JP3652995B2 - クロックデータ再生回路の識別電圧制御回路と識別電圧制御方法及び光受信装置、識別電圧制御プログラム - Google Patents

クロックデータ再生回路の識別電圧制御回路と識別電圧制御方法及び光受信装置、識別電圧制御プログラム Download PDFInfo

- Publication number

- JP3652995B2 JP3652995B2 JP2001076455A JP2001076455A JP3652995B2 JP 3652995 B2 JP3652995 B2 JP 3652995B2 JP 2001076455 A JP2001076455 A JP 2001076455A JP 2001076455 A JP2001076455 A JP 2001076455A JP 3652995 B2 JP3652995 B2 JP 3652995B2

- Authority

- JP

- Japan

- Prior art keywords

- level

- identification

- input data

- data signal

- clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/06—Dc level restoring means; Bias distortion correction ; Decision circuits providing symbol by symbol detection

- H04L25/061—Dc level restoring means; Bias distortion correction ; Decision circuits providing symbol by symbol detection providing hard decisions only; arrangements for tracking or suppressing unwanted low frequency components, e.g. removal of dc offset

- H04L25/063—Setting decision thresholds using feedback techniques only

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B10/00—Transmission systems employing electromagnetic waves other than radio-waves, e.g. infrared, visible or ultraviolet light, or employing corpuscular radiation, e.g. quantum communication

- H04B10/60—Receivers

- H04B10/66—Non-coherent receivers, e.g. using direct detection

- H04B10/69—Electrical arrangements in the receiver

- H04B10/695—Arrangements for optimizing the decision element in the receiver, e.g. by using automatic threshold control

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

Description

【発明の属する技術分野】

本発明は、識別電圧付与機能付きクロックデータ再生回路において、クロックデータ再生回路に最適な識別電圧を与える制御回路と識別電圧制御方法及び識別電圧制御プログラムに関する。

【0002】

【従来の技術】

昨今の、光アンプやWDM(波長多重伝送)を含む光伝送系においては、従来の光伝送系に比べて、光受信波形を劣化させる要因が増えてきた。例として、光ファイバアンプが発生するASE(amplified spontaneous emission)に起因する雑音の累積、光ファイバ内の光信号パワーの増大によりその影響が顕著になった光ファイバの分散や非線形効果による波形劣化、波長多重伝送における隣接チャネルからのクロストーク等が上げられる。

【0003】

送信直後の光受信波形は、図19に示すように、光入力データ信号を1又は0に確実に識別できる領域、アイ開口部が大きいが、600km伝送後の光受信波形は、図25に示すように、アイ開口部が非常に小さくなる。

【0004】

このような光受信波形の劣化があっても、受信回路の識別回路は、最適な識別を行うことが要求される。光受信波形のアイ開口部は、受光電力によって異なるので、光受信波形の1又は0を識別する識別位置の最適値は、受光電力によって異なるものであるが、従来の光伝送路では、光受信波形の劣化に対して識別位置の余裕が比較的あり、製品出荷時にメーカにより調整された値に固定されていても、実用上あまり問題とならなかった。

【0005】

【発明が解決しようとする課題】

しかしながら、光アンプやWDM(波長多重伝送)を含む光伝送系では、上述のように光受信波形を劣化させる要因が増えたため、従来のように識別位置を固定された識別回路では、エラーレート特性の曲がり(フロア)が生じ、伝送路品質を確保することが困難となる(図26上)。

【0006】

また、このような状況に鑑み、ハードウェア的に識別位置を最適に制御する識別回路が種々考えられているが、演算処理されるため回路パラメータの設計を緻密に行う必要があり、また、あまりきめこまかい制御ができないという欠点があった。

【0007】

本発明の目的は、このような欠点を克服するため、識別電圧制御回路にデジタル演算処理を用いることにより、各受光レベルで識別位置を最適に制御することができ、識別点が固定されていた従来の識別回路に比べてエラーレート特性が改善され、フロアーを生じることがなくなる識別電圧付与機能付きクロックデータ再生回路の識別電圧制御回路と識別電圧制御方法を提案することにある。

【0008】

本発明の第2の目的は、アイ開口部の内縁を検出することにより、中央識別点を最適位置に制御することができる識別電圧付与機能付きクロックデータ再生回路の識別電圧制御回路と識別電圧制御方法を提案することにある。

【0009】

本発明の第3の目的は、エラーカウント部の計測結果をもとに計測時間を調整しているので、計測精度を上げることができ、また、悪い状態からすばやく脱出することができる識別電圧付与機能付きクロックデータ再生回路の識別電圧制御回路と識別電圧制御方法を提案することにある。

【0010】

本発明の第4の目的は、計測したエラーの数に応じて、計測時間を変更するので、いたずらに大規模なカウンタを用いる必要がない識別電圧付与機能付きクロックデータ再生回路の識別電圧制御回路と識別電圧制御方法を提案することにある。

【0013】

請求項1の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0014】

請求項2の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0015】

請求項3の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程とを含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0016】

請求項4の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる過程を含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0019】

請求項5の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動し、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0020】

請求項6の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0021】

請求項7の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0022】

請求項8の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0025】

請求項9の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動し、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0026】

請求項10の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0027】

請求項11の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0028】

請求項12の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0031】

請求項13の本発明は、コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする。

【0032】

請求項14の本発明は、コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする。

【0033】

請求項15の本発明は、コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程とを含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする。

【0034】

請求項16の本発明は、コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ過程を含み、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする。

【0037】

請求項17の本発明は、光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動し、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0038】

請求項18の本発明は、光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0039】

請求項19の本発明は、光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0040】

請求項20の本発明は、光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる演算処理部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする。

【0041】

請求項21の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数に応じた電圧を生成するD/A変換部と、前記エラー数に応じた電圧に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点に対応する電圧を、各識別点の幅を変化させながら出力する演算部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0042】

請求項22の本発明の識別電圧制御回路は、前記演算部は、Hレベルエラー数に対応する電圧とLレベルエラー数に対応する電圧の差電圧に比例する電圧を中央識別点に対応する電圧として与える第1の演算増幅器と、HLレベルエラー数に対応する電圧に逆比例した電圧を上識別点に対応する電圧とし、HLレベルエラー数に対応する電圧に比例した電圧を下識別点に対応する電圧として与える第2の演算増幅器を備えることを特徴とする。

【0043】

請求項23の本発明の識別電圧制御回路は、前記演算部は、前記Hレベル近傍の上識別点に対応する電圧とLレベル近傍の下識別点に対応する電圧を任意の分圧比で分圧して前記中央識別点に対応する電圧を出力する分圧器を備えることを特徴とする。

【0044】

請求項24の本発明は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数に応じた電圧を生成するD/A変換部と、前記エラー数に応じた電圧に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点に対応する電圧を、各識別点の幅を変化させながら、前記上下各識別点及び中央識別点の間隔保持をしたままで3識別点を同時に動かして出力する演算部とを備え、前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする。

【0055】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

【0056】

図1は、本発明の第1の実施の形態による識別電圧付加機能付きCDRの識別電圧制御回路の構成を示すブロック図である。

【0057】

図1において、100は、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するCDR(clock and data recovery:クロックデータ再生回路)に識別電圧を付与する機能が追加された識別電圧付加機能付きCDRであり、10は、識別電圧付与機能付きCDR100において、制御アルゴリズムによりCDRに最適な識別電圧を与える識別電圧制御回路である。

【0058】

識別電圧付加機能付きCDR100は、従来から提供されているものであり、その構成例を図2に示す。この識別電圧付加機能付きCDR100においては、エラーの検出は、隣り合う識別点における識別結果の一致不一致を排他論理和で判定し、不一致であればエラーパルスを出力する。

【0059】

識別電圧制御回路10は、エラーカウント部20、演算処理回路31を有する演算処理部30、計測時間設定部40、D/A変換部50とで構成される。

【0060】

エラーカウント部20は、Hレベルエラーカウンタ21とLレベルエラーカウンタ22とを備えており、識別電圧付加機能付きCDR100からの、Hレベル近傍のエラーパルス(以下Hレベルエラーパルス)とLレベル近傍のエラーパルス(以下Lレベルエラーパルス)を各々Hレベルエラーカウンタ21とLレベルエラーカウンタ22で計数する。

【0061】

演算処理部30の演算処理回路31は、Hレベルエラーパルス数とLレベルエラーパルスに応じて、以下の過程を実行する。

(1)Hレベル近傍の識別点(上識別点)と中央識別点又は、Lレベル近傍の識別点(下識別点)幅を変化させる過程

(2)上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程

(3)計数したエラーの数に応じて、計数時間を変化させる過程を1つ又は複数組み合わせて実行する。

【0062】

計測時間設定部40は、Hレベルエラーパルス数とLレベルエラーパルス数に応じて、エラーカウント部の計数時間を最適な計測時間に設定する。

【0063】

D/A変換部50は、演算処理部から出力される上識別点電圧Vmと中央識別点電圧Vthと下識別点電圧Vsをそれぞれアナログ電圧に変換する。このD/A変換部50は、上識別点電圧Vmをアナログ電圧に変換するD/A変換回路51と、中央識別点Vthアナログ電圧に変換するD/A変換回路52と、下識別点Vsアナログ電圧に変換するD/A変換回路53とを備える。

【0064】

なお、上記の構成では、識別電圧制御回路を識別電圧付加機能付きCDR100と別回路として説明したが、識別電圧制御回路を識別電圧付加機能付きCDR100に内蔵する構成とすることも勿論可能である。

【0065】

図2を参照して、識別電圧付加機能付きCDR100の構成について簡単に説明する。

【0066】

図2において、識別電圧付加機能付きCDR100は、入力した入力データ信号のHレベル近傍の上識別点、中央レベル近傍の中央識別点及びLレベル近傍の下識別点を識別する3値識別回路101と、レベル変動を検出して検出結果を上記識別電圧制御回路10に出力するレベル変動検出回路102と、PLL回路103とを備えて構成される。

【0067】

ここで、3値識別回路101は、比較器110a、110b、110cとフリップフロップ120a、120b、120cとで構成され、レベル変動検出回路102は、排他的論理和回路130a、130bとで構成される。

【0068】

また、図3に、本発明による識別電圧制御回路10を適用した光受信装置の構成を示す。この光受信装置200は、光データ信号を受信して電気信号に変換し入力データ信号として出力する光/電気変換回路210、上述した識別電圧付加機能付きCDR100と識別電圧制御回路10とで構成されており、識別電圧付加機能付きCDR100から識別されたデータ信号が出力されるものである。

【0069】

図4から図10を用いて本発明の実施の形態による識別電圧制御回路の動作について説明する。

【0070】

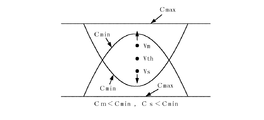

図4は、本発明の特徴である上記識別電圧制御回路10の演算処理部30における制御アルゴリズムの基本的考え方を示す図、図5は、本発明の制御アルゴリズムを用いたフローチャートの一例である。また、図6から図9は、それぞれ図5のフローチャート各過程におけるアイ開口部と上識別点電圧Vmと中央識別点Vthと下識別点Vsとの位置関係を示す図である。なお、中央識別点電圧Vthの値については、入力する光データ信号のレベルやデータ品質に応じて、すなわち識別電圧付加機能付きCDR100を使用するシステムに応じて任意に調整して設定するものとする。

【0071】

ここで、

Hレベルエラー数:Cm

Lレベルエラー数:Cs

最大計測値:Cmax(Cmax>Cmin>0)

最小計測値:Cmin(Cmin>=0)

Hレベル識別点電圧:Vm

Lレベル識別点電圧:Vs

中央識別点電圧:Vth(Vm>Vth>Vs)

エラー計測時間:Tsamp

と定義する。

【0072】

初期状態における上識別点電圧Vmと中央識別点電圧Vthと下識別点電圧Vsの各位置が、図6のようになっていると仮定する。すなわち、3点はアイ開口部内部にあるが、中央識別点電圧Vthは最適位置から若干上にずれている。

【0073】

この状態において、Hレベルエラー数CmとLレベルエラー数Csを計数すると、Cm<Cmin、Cs<Cminとなるので、ステップ401の一番目の判定がY(Yes)となり、アイ開口部の縁を検出するため、VmをΔVmだけ上にあげ、かつVsをΔVsだけ下に下げる(各識別点の幅を広げる)操作を行う(ステップ402)。この操作により、図7の状態になる。

【0074】

このとき、Hレベルエラー数Cm、Lレベルエラー数Csとも最小計測値Cminを下回っているので、計測時間内に計数するエラーパルスの数を増やして計測精度を上げるために計測時間TsampをΔTsampだけ長くする(ステップ403)。

【0075】

次に、図7において、上識別点電圧Vmと下識別点電圧Vsはアイ開口部の外側にずれているので、Hレベルエラー数CmとLレベルエラー数Csを計数すると、Cmax>Cm>Cs>Cminとなる。この結果、ステップ401の一番目の判定とステップ404の2番目の判定はN(No)となり、ステップ407の3番目の判定がY(Yes)となり、上識別点電圧Vmと中央識別点電圧Vthと下識別点電圧Vsを3点同時にΔVthだけだけ下げる制御を行うことにより(ステップ408)、図8の状態になる。

【0076】

このときも、Hレベルエラー数Cm、Lレベルエラー数Csは、最大計測値Cmaxを上回っていないので計測精度を上げるために計測時間TsampをΔTsampだけ長くする(ステップ409)。

【0077】

図8では、中央識別点電圧Vthは最適位置近傍あるが、まだ、上識別点電圧Vmと下識別点電圧Vsはアイ開口部の縁を検出しているとは言えない。このときのHレベルエラー数CmとLレベルエラー数Csの計数結果は、Cmax>Cm=Cs>Cminとなり、図5のフローチャートでは、ステップ401の一番目からステップ410の4番目の判定が全てN(No)となり、アイ開口部の縁を検出するため、上識別点電圧VmをΔVmだけ下げ、かつ下識別点電圧VsをΔVsだけ上げる(各識別点の幅を縮める)(ステップ413)。

【0078】

また同様に計測精度を上げるために計測時間TsampをΔTsampだけ長くする(ステップ414)。

【0079】

以上の操作を繰り返し行うことで、上識別点電圧Vmと下識別点電圧Vsでのエラー計測数が、Cmax>Cm=Cs≒Cminを満足する状態における中央識別点電圧Vthが最適識別点となる(図9)。

【0080】

図5において、Hレベルエラー数Cm、Lレベルエラー数Csのいずれかが最大計測値Cmaxを越えた場合は(ステップ404でYes)、上識別点電圧VmをΔVmだけ下げ、かつ下識別点電圧VsをΔVsだけ上げる(各識別点の幅を縮める)とともに(ステップ405)、計測時間TsampをΔTsampだけ短くする(ステップ406)。これにより、悪い状態からすばやく脱出することができ、またカウンタのオーバーフローを防ぐことができる。

【0081】

以上のような動作により、本実施の形態によれば、中央識別点電圧Vthが最適識別点となることで、図26に示すように、識別点固定の場合に比べてエラーレートの改善が図られるものである。

【0082】

図4における、識別点の制御とエラー計測時間の制御はそれぞれに単独で行ってもよいし、複数同時に行ってもよい。

【0083】

すなわち、上識別点電圧VmをΔVmだけ下げ、かつ下識別点電圧VsをΔVsだけ上げる(各識別点の幅を縮める)制御と、上識別点電圧Vmと中央識別点電圧Vthと下識別点Vsを3点同時にΔVthだけ下げる制御を同時に行ってもよい。

【0084】

例えば、図5においてHレベルエラー数Cm、Lレベルエラー数Csのいずれかが最大計測値Cmaxを越えた場合は、上識別点電圧VmをΔVmだけ下げ、かつ下識別点電圧VsをΔVsだけ上げる(各識別点の幅を縮める)とともに、計測時間TsampをΔTsampだけ短くする制御に加え、上識別点電圧Vmと中央識別点電圧Vthと下識別点電圧Vsを3点同時にΔVthだけ下げる制御を同時に行ったほうが、悪い状態からより早く脱出することができるであろう。

【0085】

また、計測結果において、Hレベルエラー数CmとLレベルエラー数Csが、Cmax>Cm>Cs>Cminを満たす場合は、計測数としては適切な値であるので、計測時間Tsampをかえないようにしてもよい。

【0086】

図5において一番目の判定と2番目の判定は逆の順番でもよい。同様に3番目と4番目の判定の順序が入れ替わってもよい。

【0087】

また、一番目の判定(ステップ401)、と3番目、4番目の判定(ステップ407、410)(又は4番目、3番目の判定)、2番目の判定(ステップ404)の順序で実行してもよい。あるいは、2番目の判定(ステップ404)、と3番目又は4番目の判定(ステップ407、410)(又は4番目、3番目の判定)、一番目の判定の順序で実行してもよい。

【0088】

また、ΔVmとΔVsは等しくてもよいし等しくなくてもよい。ΔVmとΔVsを等しい値に設定した場合は、中央識別点Vthは、上識別点電圧Vmと下識別点Vsの中間に位置することになる。

【0089】

上記説明において、ΔVm、ΔVs、ΔVthの値は、制御の精度をどの程度に設定するかによって変化することは言うまでもない。例えば、一般的な例では、入力データ信号の1/10〜1/1000の範囲で設定する。さらに、計測時間Tsamp及びΔTsampの値についても、制御の精度をどの程度に設定するかによって変化する。一例として、計測時間Tsampは、光受信装置が動作するエラーレートの最低値(例えば、BER=10−2〜10−3)を計測できる時間から、ほぼエラーフリーとみなされるエラーレート(例えば、BER=10−12〜10−15)を計測できる時間までの範囲で可変される。加えて、ΔTsampは、一例として、上述した時間的範囲のさらに1/10〜1/1000程度の刻みで設定する。

【0090】

次に、本発明の第2の実施の形態について説明する。図10は、本発明の第2の実施の形態による識別電圧制御回路の構成を示す図、図11は第2の実施の形態における制御アルゴリズムの基本的考え方を示す図、図12は、第2の実施の形態における制御アルゴリズムを用いたフローチャートの一例である。

【0091】

この、第2の実施の形態では、上述した第1の実施の形態をさらに簡略化したものであり、第1の実施の形態における上下各識別点電圧Vm、Vs及び中央識別点電圧Vthの間隔保持をしたままで3識別点を同時に動かす過程を省略した構成としている。その他の上下各識別点電圧Vm、Vsを移動するステップ及びエラー計測時間Tsampを変更するステップについては、図5の対応するステップと同じである。

【0092】

この第2の実施の形態による識別電圧制御回路10では、中央識別点電圧Vthは、演算処理部30により上下識別点Vm、Vsの間の任意に定められた点に設定される。アナログ電圧に変換後、分圧回路60を用いることにより、上下識別点電圧Vm、Vsの間の任意定められた点に設定する構成としている。

【0093】

次に、本発明の第3の実施の形態について説明する。図13は、本発明の第3の実施の形態による識別電圧制御回路の構成を示す図、図14は第3の実施の形態における制御アルゴリズムの基本的考え方を示す図、図15は、第3の実施の形態における制御アルゴリズムを用いたフローチャートの一例である。

【0094】

この第3の実施の形態では、第1の実施の形態による識別電圧制御回路10において、計測時間設定部40aに固定の計測時間が設定されており、エラーカウント部20における計数時間を固定し、エラー計測時間Tsampの変更を行わない構成としている。

【0095】

次に、本発明の第4の実施の形態について説明する。図16は、本発明の第4の実施の形態による識別電圧制御回路の構成を示す図、図17は第4の実施の形態における制御アルゴリズムの基本的考え方を示す図、図18は、第4の実施の形態における制御アルゴリズムを用いたフローチャートの一例である。

【0096】

この第4の実施の形態では、第2の実施の形態による識別電圧制御回路10の構成に加えて、エラーカウント部20における計数時間を固定し、エラー計測時間Tsampの変更を行わない構成としている。

【0097】

なお、第1から第4の実施の形態による識別電圧制御回路10における制御は、制御回路の各機能をハードウェア的に実現することは勿論として、各機能を備えるコンピュータプログラムである識別電圧制御プログラムを、コンピュータ処理装置のメモリにロードされることで実現することができる。この識別電圧制御プログラムは、磁気ディスク、半導体メモリその他の記録媒体600に格納される。そして、その記録媒体からコンピュータ処理装置にロードされ、コンピュータ処理装置の動作を制御することにより、上述した識別電圧制御回路10の各機能を実現する。

【0098】

上記の実施の形態では、識別電圧制御回路10をデジタル回路で実現した形態を説明したが、以下の第5から第7の実施の形態では、同様の機能を備える識別電圧制御回路をアナログ回路によって実現した形態を示す。

【0099】

まず、識別電圧制御回路をアナログ回路によって実現した第5の実施の形態について説明する。図20は、本発明の第5実施の形態による識別電圧制御回路の構成を示す図、図21は第5の実施の形態における制御アルゴリズムの基本的考え方を示す図である。この第5の実施の形態では、上識別点電圧Vm、下識別点電圧Vs、中央識別点電圧Vthの間隔が最適な位置になるようにアナログ的に制御するものである。

【0100】

この第5の実施の形態による識別電圧制御回路10Aは、HレベルエラーパルスとLレベルエラーパルスをそのレベルエラーの数に応じた直流電圧に変換するD/A変換部50Aと、演算部30Aとで構成される。また、演算部30Aは、演算増幅器301A、302Aとで構成され、D/A変換部50Aは、平均値検出回路501A〜503A及び論理和回路504Aとで構成される。

【0101】

以下、上記識別電圧制御回路10Aの動作について、図21を参照して説明する。D/A変換部50Aでは、平均値検出回路501AにおいてHレベルのエラーパルスの数に応じた直流電圧(Hレベルエラー電圧Cm)と、平均値検出回路502AにおいてLレベルのエラーパルスの数に応じた直流電圧(Lレベルエラー電圧Cs)と、HレベルとLレベルのエラーパルスの論理和のエラーパルスの数に応じた直流電圧(HLレベルエラー電圧C)とに変換して出力する。

【0102】

演算部30Aでは、演算増幅器301AがHレベルエラー電圧CmとLレベルエラー電圧Csの差電圧に比例する電圧を中央識別点電圧Vthとして与え、演算増幅器302AがHLレベルエラー電圧Cに逆比例した電圧を上識別点電圧Vmとして、HLレベルエラー電圧Cに比例した電圧を下識別点電圧Vsとして与える処理が行われる。これらの処理は同時に行われる。

【0103】

すなわち、上記において、Hレベルエラー数>Lレベルエラー数の場合、Hレベルエラー電圧Cm>Lレベルエラー電圧Csとなって中央識別点電圧Vthが下がると同時に、HLレベルエラー電圧Cも発生するので、上識別点電圧Vmが下がり、かつ下識別点電圧Vsが上がる。この結果、各識別点の間隔が狭くなる。

【0104】

また、各識別点の間隔制御において、間隔を広げる速度と狭める速度に差をつけたい場合には、HレベルとLレベルのエラーパルスの論理和のエラーパルスの数に応じた直流電圧に変換する過程において、充電時定数と放電時定数に差を設ければよい。

【0105】

上記の第5の実施の形態では、HレベルとLレベルのエラー数の計測結果に応じて、上識別点電圧Vm、下識別点電圧Vs及び中央識別点電圧Vthの3つの識別点の間隔が制御され、各識別点を最適な位置に調整することが可能となる。

【0106】

次に、識別電圧制御回路をアナログ回路によって実現した第6の実施の形態について説明する。図22は、本発明の第6の実施の形態による識別電圧制御回路の構成を示す図である。この第6の実施の形態では、上識別点電圧Vm、下識別点電圧Vs、中央識別点電圧Vthの間隔がを制御し、かつ各識別点の間隔を保持したまま3つの識別点を移動することにより、各識別点が最適な位置になるようにアナログ的に制御するものである。

【0107】

この第6の実施の形態による識別電圧制御回路10Bは、HレベルエラーパルスとLレベルエラーパルスをそのレベルエラーの数に応じた直流電圧に変換するD/A変換部50Bと、演算部30Bとで構成される。また、演算部30Bは、演算増幅器301B、302B、303Bとで構成され、D/A変換部50Aは、平均値検出回路501B〜503B及び論理和回路504Bとで構成される。ここで、演算部30B以外の構成は上記第5の実施の形態と同じである。

【0108】

演算部30Bでは、演算増幅器301BがHレベルエラー電圧CmとLレベルエラー電圧Csの差電圧に比例する電圧を中央識別点電圧Vthとして与え、演算増幅器302BがHLレベルエラー電圧Cと中央識別点電圧Vthの差電圧に比例した電圧を上識別点電圧Vmとして与え、演算増幅器303BがHLレベルエラー電圧Cと、Hレベルエラー電圧CmとLレベルエラー電圧Csの差電圧に逆比例する電圧との差電圧に比例した電圧を下識別点電圧Vsとして与える処理が行われる。

【0109】

上記ような構成により、中央識別点電圧Vthが上下に変化した場合には、上識別点電圧Vmと下識別点電圧Vsがそれに連動して上下に変化する。これにより、上記の第6の実施の形態では、HレベルとLレベルのエラー数の計測結果に応じて、上識別点電圧Vm、下識別点電圧Vs及び中央識別点電圧Vthの3つの識別点の間隔の制御がなされると共に、各識別点の間隔を保ちつつ3つの識別点を移動する制御がなされ、各識別点を最適な位置に調整することが可能となる。

【0110】

最後に、識別電圧制御回路をアナログ回路によって実現した第7の実施の形態について説明する。図23は、本発明の第7実施の形態による識別電圧制御回路の構成を示す図、図24は第7の実施の形態における制御アルゴリズムの基本的考え方を示す図である。この第7の実施の形態では、上識別点電圧Vm、下識別点電圧Vs、中央識別点電圧Vthの間隔が最適な位置になるようにアナログ的に制御するものである。

【0111】

この第7の実施の形態による識別電圧制御回路10Cは、HレベルエラーパルスとLレベルエラーパルスをそのレベルエラーの数に応じた直流電圧に変換するD/A変換部50Cと、演算部30Cとで構成される。また、演算部30Cは、演算増幅器301C、302Cと分圧器303Cとで構成され、D/A変換部50Aは、平均値検出回路501Cと502Cとで構成される。

【0112】

この識別電圧制御回路10Cでは、上識別点電圧Vmと下識別点電圧Vsの間隔制御のみを行い、中央点識別電圧Vthについては、上識別点電圧Vmと下識別点電圧Vsを分圧器303Cによって比例配分することで与えている。この分圧器303Cの分圧比にについては任意に設定することが可能である。

【0113】

上記第7の実施の形態によれば、Hレベルエラー電圧Cmが発生すると、上識別点電圧Vmが下がるように制御され、Lレベルエラー電圧Csが発生すると下識別点電圧Vsが上がるように制御される。これにより、上識別点電圧Vm、下識別点電圧Vs、中央識別点電圧Vthの間隔が最適な位置になるように制御される。

【0114】

なお、上記第5から第7の実施の形態においても、第1の実施の形態と同様に、Hレベルエラー電圧CmとLレベルエラー電圧Csの大きさによって、計測時間を設定するような構成とすることも可能である。

【0115】

以上好ましい実施の形態及び実施例をあげて本発明を説明したが、本発明は必ずしも上記実施の形態及び実施例に限定されるものではなく、その技術的思想の範囲内において様々に変形して実施することができる。

【0116】

【発明の効果】

以上説明したように本発明の識別電圧付与機能付きCDRの識別電圧制御回路と識別電圧制御方法によれば、以下のような効果が達成される。

【0117】

第1に、各受光レベルで識別位置を最適に制御することができるので、識別点が固定されていた従来の識別回路に比べてエラーレート特性が改善され、フロアーを生じることがなくなる。

【0118】

第2に、アイ開口部の内縁を検出するので識別点Vthを最適位置に制御することができる。

【0119】

第3に、エラーカウント部の計測結果をもとに、計測時間を調整しているので、計測精度を上げることができ、また、悪い状態からすばやく脱出することができる。

【0120】

第4に、計測したエラーの数に応じて、計測時間を変更するので、いたずらに大規模なカウンタを用いる必要がない。

【図面の簡単な説明】

【図1】 本発明の第1の実施の形態による識別電圧付加機能付きCDRの識別電圧制御回路の構成を示すブロック図である。

【図2】 本発明の第1の実施の形態における識別電圧付加機能付きCDRの構成を示すブロック図である。

【図3】 本発明の本発明による識別電圧制御回路を適用した光受信装置の構成を示すブロック図である。

【図4】 本発明の第1の実施の形態による識別電圧制御回路の演算処理部における制御アルゴリズムの基本的考え方を示す図である。

【図5】 本発明の第1の実施の形態による識別電圧制御回路の動作を説明するフローチャートである。

【図6】 図5のフローチャート各過程におけるアイ開口部と上識別点電圧と中央識別点と下識別点Vとの位置関係を示す図である。

【図7】 図5のフローチャート各過程におけるアイ開口部と上識別点電圧と中央識別点と下識別点Vとの位置関係を示す図である。

【図8】 図5のフローチャート各過程におけるアイ開口部と上識別点電圧と中央識別点と下識別点Vとの位置関係を示す図である。

【図9】 図5のフローチャート各過程におけるアイ開口部と上識別点電圧と中央識別点と下識別点Vとの位置関係を示す図である。

【図10】 本発明の第2の実施の形態による識別電圧付加機能付きCDRの識別電圧制御回路の構成を示すブロック図である。

【図11】 本発明の第2の実施の形態による識別電圧制御回路の演算処理部における制御アルゴリズムの基本的考え方を示す図である。

【図12】 本発明の第2の実施の形態による識別電圧制御回路の動作を説明するフローチャートである。

【図13】 本発明の第3の実施の形態による識別電圧付加機能付きCDRの識別電圧制御回路の構成を示すブロック図である。

【図14】 本発明の第3の実施の形態による識別電圧制御回路の演算処理部における制御アルゴリズムの基本的考え方を示す図である。

【図15】 本発明の第3の実施の形態による識別電圧制御回路の動作を説明するフローチャートである。

【図16】 本発明の第4の実施の形態による識別電圧付加機能付きCDRの識別電圧制御回路の構成を示すブロック図である。

【図17】 本発明の第4の実施の形態による識別電圧制御回路の演算処理部における制御アルゴリズムの基本的考え方を示す図である。

【図18】 本発明の第4の実施の形態による識別電圧制御回路の動作を説明するフローチャートである。

【図19】 送信後の光受信波形の例を示す図である。

【図20】 本発明の第5実施の形態によるアナログ的な識別電圧制御回路の構成を示すブロック図である。

【図21】 第5の実施の形態における制御アルゴリズムの基本的考え方を示す図である。

【図22】 本発明の第6の実施の形態によるアナログ的な識別電圧制御回路の構成を示すブロック図である。

【図23】 本発明の第7の実施の形態によるアナログ的な識別電圧制御回路の構成を示すブロック図である。

【図24】 第7の実施の形態における制御アルゴリズムの基本的考え方を示す図である。

【図25】 送信後の光受信波形の例を示す図である。

【図26】 エラーレートの改善効果を示す図である。

【符号の説明】

10、10A、10B、10C 識別電圧制御回路

20 エラーカウント部

30 演算処理部

40 計測時間設定部

50、50A、50B、50C D/A変換部

100 識別電圧付加機能付きCDR

200 光受信装置

210 光/電気変換回路

30A、30B、30C 演算部

301A、302A、301B、302B、303B、301C、302C 演算増幅器

501A、502A、503A、501B、502B、503B、501C、502C 平均値検出回路

504A、504B 論理和回路

303C 分圧器

Claims (24)

- 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御方法。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御方法。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程とを含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御方法。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御方法において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる過程を含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御方法。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動し、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動し、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする識別電圧付加機能付きクロックデータ再生回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする識別電圧付加機能付きクロックデータ再生回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする識別電圧付加機能付きクロックデータ再生回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする識別電圧付加機能付きクロックデータ再生回路。 - コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする識別電圧制御プログラム。 - コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる過程とを含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする識別電圧制御プログラム。 - コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす過程とを含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする識別電圧制御プログラム。 - コンピュータ装置に読み込まれて実行され、当該コンピュータ装置を制御して、光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御プログラムにおいて、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理し、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ過程を含み、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する機能を実現することを特徴とする識別電圧制御プログラム。 - 光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、

所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動し、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする光受信装置。 - 光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、エラー数の計測時間を変化させる演算処理部とを備え、 前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする光受信装置。 - 光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させ、

前記エラー計数結果に基づいて、前記上下各識別点及び中央識別点の間隔保持をしたままで、3識別点を同時に動かす演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする光受信装置。 - 光入力信号を電気信号に変換して入力データ信号として出力する光/電気変換回路と、所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路であって、識別電圧を付与する機能が追加された識別電圧付加機能付きクロックデータ再生回路とを備える光受信装置において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数を計数処理するエラーカウント部と、

前記エラー計数結果に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点との幅を変化させる演算処理部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定する識別電圧制御回路を備えたことを特徴とする光受信装置。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数に応じた電圧を生成するD/A変換部と、

前記エラー数に応じた電圧に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点に対応する電圧を、各識別点の幅を変化させながら出力する演算部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御回路。 - 前記演算部は、

Hレベルエラー数に対応する電圧とLレベルエラー数に対応する電圧の差電圧に比例する電圧を中央識別点に対応する電圧として与える第1の演算増幅器と、

HLレベルエラー数に対応する電圧に逆比例した電圧を上識別点に対応する電圧とし、HLレベルエラー数に対応する電圧に比例した電圧を下識別点に対応する電圧として与える第2の演算増幅器を備えることを特徴とする請求項21に記載の識別電圧制御回路。 - 前記演算部は、

前記Hレベル近傍の上識別点に対応する電圧とLレベル近傍の下識別点に対応する電圧を任意の分圧比で分圧して前記中央識別点に対応する電圧を出力する分圧器を備えることを特徴とする請求項21に記載の識別電圧制御回路。 - 光入力信号を電気信号に変換し所定の振幅まで増幅された入力データ信号からクロック成分を抽出し、そのクロックのタイミングで入力データ信号の1又は0を識別するクロックデータ再生回路に、最適な識別電圧を付与する識別電圧制御回路において、

入力データ信号のHレベル近傍のエラー数とLレベル近傍のエラー数に応じた電圧を生成するD/A変換部と、

前記エラー数に応じた電圧に基づいて、Hレベル近傍の上識別点と中央識別点又は、Lレベル近傍の下識別点に対応する電圧を、各識別点の幅を変化させながら、前記上下各識別点及び中央識別点の間隔保持をしたままで3識別点を同時に動かして出力する演算部とを備え、

前記入力データ信号のアイ開口部の内縁を検出しながら中央識別点を最適位置に設定することを特徴とする識別電圧制御回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001076455A JP3652995B2 (ja) | 2001-03-16 | 2001-03-16 | クロックデータ再生回路の識別電圧制御回路と識別電圧制御方法及び光受信装置、識別電圧制御プログラム |

| EP02005365A EP1241845A3 (en) | 2001-03-16 | 2002-03-14 | Control of decision thresholds in a receiver of an optical transmission system |

| US10/097,394 US7218686B2 (en) | 2001-03-16 | 2002-03-15 | Decision threshold voltage control circuit and decision threshold voltage controlling method of clock and data recovery circuit, optical receiver, and decision threshold voltage control program |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001076455A JP3652995B2 (ja) | 2001-03-16 | 2001-03-16 | クロックデータ再生回路の識別電圧制御回路と識別電圧制御方法及び光受信装置、識別電圧制御プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002281094A JP2002281094A (ja) | 2002-09-27 |

| JP3652995B2 true JP3652995B2 (ja) | 2005-05-25 |

Family

ID=18933382

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001076455A Expired - Fee Related JP3652995B2 (ja) | 2001-03-16 | 2001-03-16 | クロックデータ再生回路の識別電圧制御回路と識別電圧制御方法及び光受信装置、識別電圧制御プログラム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7218686B2 (ja) |

| EP (1) | EP1241845A3 (ja) |

| JP (1) | JP3652995B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2004098120A1 (ja) * | 2003-05-01 | 2004-11-11 | Mitsubishi Denki Kabushiki Kaisha | クロックデータリカバリー回路 |

| US7590175B2 (en) | 2003-05-20 | 2009-09-15 | Rambus Inc. | DFE margin test methods and circuits that decouple sample and feedback timing |

| US7408981B2 (en) * | 2003-05-20 | 2008-08-05 | Rambus Inc. | Methods and circuits for performing margining tests in the presence of a decision feedback equalizer |

| US7336749B2 (en) * | 2004-05-18 | 2008-02-26 | Rambus Inc. | Statistical margin test methods and circuits |

| US7627029B2 (en) | 2003-05-20 | 2009-12-01 | Rambus Inc. | Margin test methods and circuits |

| EP1630983B1 (en) * | 2003-06-03 | 2013-11-20 | Fujitsu Limited | Optical signal reception device and for-digitization discrimination point control method thereof |

| GB2402841B (en) * | 2003-06-10 | 2005-05-11 | Whereonearth Ltd | A method of providing location based information to a mobile terminal within a communications network |

| US7643759B2 (en) * | 2005-01-12 | 2010-01-05 | Sumitomo Electric Industries, Ltd. | Signal-quality evaluation device, signal adjustment method, optical-signal evaluation system, and optical transmission system |

| US8249447B2 (en) * | 2008-04-29 | 2012-08-21 | Menara Networks, Inc. | Systems and methods for optical receiver decision threshold optimization |

| WO2010067448A1 (ja) * | 2008-12-11 | 2010-06-17 | 富士通株式会社 | 受信装置、伝送装置及び伝送方法 |

| US8713380B2 (en) * | 2011-05-03 | 2014-04-29 | SanDisk Technologies, Inc. | Non-volatile memory and method having efficient on-chip block-copying with controlled error rate |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2511566A1 (fr) * | 1981-08-12 | 1983-02-18 | Thomson Csf | Recepteur optique a seuils pour systeme de transmission numerique a debit variable |

| JPS60178751A (ja) | 1984-02-24 | 1985-09-12 | Fujitsu Ltd | 信号劣化検出回路 |

| JP2571408B2 (ja) | 1987-12-11 | 1997-01-16 | 富士通株式会社 | 通信システムの試験方法 |

| US4823360A (en) | 1988-02-12 | 1989-04-18 | Northern Telecom Limited | Binary data regenerator with adaptive threshold level |

| JP2530904B2 (ja) * | 1988-02-22 | 1996-09-04 | 富士通株式会社 | 最適識別レベル制御方式 |

| JPH0454043A (ja) | 1990-06-22 | 1992-02-21 | Fujitsu Ltd | 受信データ識別回路 |

| US5521941A (en) * | 1990-11-29 | 1996-05-28 | Motorola, Inc. | Automatic threshold control for multi-level signals |

| JP2598913Y2 (ja) * | 1992-07-27 | 1999-08-23 | ミツミ電機株式会社 | データスライサ |

| JPH0810851B2 (ja) | 1993-01-11 | 1996-01-31 | 日本電気株式会社 | 波形識別装置 |

| US5425056A (en) * | 1993-03-23 | 1995-06-13 | Motorola, Inc. | Method and apparatus for generating threshold levels in a radio communication device for receiving four-level signals |

| FR2731125B1 (fr) * | 1995-02-28 | 1997-05-16 | Sgs Thomson Microelectronics | Circuit de traitement d'un signal asynchrone presentant periodiquement des salves de synchronisation |

| JP3551393B2 (ja) | 1995-03-20 | 2004-08-04 | 富士通株式会社 | 識別回路 |

| US5670951A (en) * | 1995-07-17 | 1997-09-23 | Motorola, Inc. | Radio communication device and method for generating threshold levels in a radio communication device for receiving four-level signals |

| JPH09205466A (ja) * | 1996-01-29 | 1997-08-05 | Kokusai Electric Co Ltd | シンボル判定装置 |

| JPH1093641A (ja) * | 1996-09-12 | 1998-04-10 | Nec Corp | 多値fsk復調ウィンドウコンパレータ |

| JP3863265B2 (ja) * | 1997-10-16 | 2006-12-27 | 富士通株式会社 | 光受信器およびクロック抽出回路 |

| US6188737B1 (en) * | 1999-11-24 | 2001-02-13 | Nortel Networks Limited | Method and apparatus for regenerating data |

| CA2328251C (en) * | 1999-12-15 | 2004-05-25 | Nec Corporation | Automatic identification level control circuit, identification level control method, automatic identification phase control circuit, identification phase control method, optical receiver, and optical communication system |

| JP3657209B2 (ja) | 2000-10-26 | 2005-06-08 | 三菱電機株式会社 | 光受信器用異常検出回路及び光受信器 |

| JP3731505B2 (ja) * | 2001-07-18 | 2006-01-05 | 日本電気株式会社 | 光受信装置、光データ信号の波形最適化方法及び光データ信号の波形最適化プログラム |

| JP3856101B2 (ja) * | 2001-09-03 | 2006-12-13 | 日本電気株式会社 | 受信波形整形機能を有する光受信装置 |

-

2001

- 2001-03-16 JP JP2001076455A patent/JP3652995B2/ja not_active Expired - Fee Related

-

2002

- 2002-03-14 EP EP02005365A patent/EP1241845A3/en not_active Withdrawn

- 2002-03-15 US US10/097,394 patent/US7218686B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP1241845A3 (en) | 2006-08-02 |

| US20020131531A1 (en) | 2002-09-19 |

| JP2002281094A (ja) | 2002-09-27 |

| US7218686B2 (en) | 2007-05-15 |

| EP1241845A2 (en) | 2002-09-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3731505B2 (ja) | 光受信装置、光データ信号の波形最適化方法及び光データ信号の波形最適化プログラム | |

| JP3652995B2 (ja) | クロックデータ再生回路の識別電圧制御回路と識別電圧制御方法及び光受信装置、識別電圧制御プログラム | |

| US5418660A (en) | Information processing apparatus for processing reproduction signal having nonlinear characteristics | |

| US6324144B1 (en) | Apparatus for correcting asymmetry of reproduction signals and method therefor | |

| TWI389467B (zh) | 自動增益控制方法及裝置 | |

| KR20060046531A (ko) | 자동 레벨 조정 회로 | |

| US5570335A (en) | Reproducing waveform correction circuit for optical information recording/reproducing system | |

| US20110063689A1 (en) | Image reading apparatus and image forming apparatus | |

| US20060279440A1 (en) | Frequency detector in phase locked loop circuit and frequency error detecting method | |

| US8508810B2 (en) | Image reading apparatus and image forming apparatus | |

| US7693246B2 (en) | Frequency control device and information reproduction apparatus | |

| US6324145B1 (en) | Digital data reproducing apparatus and reproduction signal binarization level correcting method | |

| US6118393A (en) | EFM signal frame period detecting circuit, and system for controlling the frequency of the bit synchronizing clock signal used for reproducing the EFM signal | |

| US7389056B2 (en) | Preamplifier circuit, clock switching circuit, and optical receiver | |

| KR102563390B1 (ko) | 지자기 센서의 자기장 측정 구간 및 범위 자동 조정 방법 | |

| US6917233B1 (en) | Limiting amplifier and method for amplifying an input signal | |

| JP4099994B2 (ja) | 位相ロック・ループ回路 | |

| US7336571B2 (en) | Method and arrangement for compensating scanning disturbances on optical recording media | |

| KR101061137B1 (ko) | 고속 적응형 등화기 및 그것의 제어 방법 | |

| JPH0736500B2 (ja) | Agc制御方式 | |

| US8068404B2 (en) | Signal value holding apparatus, signal value holding method, signal value control system, signal value control method, playback apparatus, and playback method | |

| JP2664221B2 (ja) | 情報再生装置 | |

| JP2826456B2 (ja) | 光受信器 | |

| KR100604791B1 (ko) | 광 디스크 재생 시스템의 포커스 바이어스 조정방법 및 장치 | |

| JPS6221419B2 (ja) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040212 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040408 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20041029 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041129 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20041129 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041209 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20050118 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050224 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080304 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090304 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090304 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100304 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |