JP3602011B2 - 制御回路 - Google Patents

制御回路 Download PDFInfo

- Publication number

- JP3602011B2 JP3602011B2 JP22772599A JP22772599A JP3602011B2 JP 3602011 B2 JP3602011 B2 JP 3602011B2 JP 22772599 A JP22772599 A JP 22772599A JP 22772599 A JP22772599 A JP 22772599A JP 3602011 B2 JP3602011 B2 JP 3602011B2

- Authority

- JP

- Japan

- Prior art keywords

- emitter

- voltage

- gate

- control circuit

- gate driver

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/168—Modifications for eliminating interference voltages or currents in composite switches

Landscapes

- Power Conversion In General (AREA)

- Electronic Switches (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

- Networks Using Active Elements (AREA)

- Dicing (AREA)

- Dairy Products (AREA)

- Logic Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、エミッタとコレクタとゲートとを含む半導体素子を制御する制御回路であって、ゲート・ドライバを含み、そしてこの出力を制御すべき半導体素子のゲートに接続した上記の制御回路に関するものである。

【0002】

【従来の技術】

IGBトランジスタのような現在使用されているパワー半導体は、ターンオンおよびターンオフが高速な素子であって、例えばこれらがパルス幅変調周波数コンバータに使用されたときに、ナノ秒あたり10ボルトを超える値の電圧変化率が、この周波数コンバータの出力電圧に現れることがある。このような変化率は、周波数コンバータの負荷に対しかなりの歪みを生じさせる。この周波数コンバータ負荷は、代表的には、モータであり、高い電圧変化率は、モータの巻線絶縁に歪みを生じさせ、しかもモータのケーブルに強い電圧反射を生じさせる。加えて、高い変化率は、周囲に対し電磁妨害を放射させる。

【0003】

【発明が解決しようとする課題】

パワー半導体の電圧変化率の抑制を、半導体素子を制御するゲート・ドライバの出力と制御すべき半導体素子のゲートとの間に接続したゲート抵抗器の抵抗を増大させることにより行うことが知られている。これは、パワー素子のゲート電荷の増加率を低下させ、これにより、ゲート電圧もより遅く増加するようにする。この接続方法の欠点は、これが、パワー素子の特性とこれらの配置とに依存することであり、これは、最終的な結果の精度をかなり劣化させる。さらに、その結合における抵抗は、不必要な程損失を増加させる。

本発明の目的は、制御回路であって、上記の欠点を回避でき、かつ半導体素子をこの素子に独立の方法でしかも簡単でかつ高価でない受動素子のみを使って信頼性良く制御できるようにした制御回路を提供することである。

【0004】

【課題を解決するための手段】

これは、本発明の制御回路で実現し、この制御回路は、この回路がさらに、

抵抗結合であって、ダイオードと抵抗器の2つの直列接続を逆並列接続でかつ前記半導体素子のエミッタと前記ゲート・ドライバのゼロ電位との間に接続した、前記の抵抗結合と、

前記半導体素子のコレクタと、前記ゲート・ドライバの前記ゼロ電位に接続した前記抵抗結合の端部との間に接続したフィードバック・キャパシタと、

を含むことを特徴とする。

【0005】

本発明は、半導体素子のコレクタ−エミッタ間電圧の変化がフィードバック・キャパシタC1を流れる電流を発生し、この電流がまたエミッタに結合した抵抗器を流れる、という思想に基づいたものである。電圧変化の方向は、2つの抵抗器の内のどちらをその電流が流れるかを決める。この両方の場合において、その電流は、それら抵抗器に電圧降下を発生し、この電圧降下は、ターンオン時すなわちコレクタ−エミッタ間電圧が減少するときの半導体素子の正のゲート電圧を低減させ、またターンオフ時すなわちコレクタ−エミッタ間電圧が増大するときの負のゲート電圧を低減させる。本発明の制御回路のこの構造は、かなり単純なものであり、したがってコスト的に効果がある。この簡単な構造により、制御回路は、実現することも容易であり、したがって動作上信頼性がある。さらに、適切に寸法決めした制御回路においては、損失は相当小さくなり、このため本発明の制御回路を利用したデバイスの動作効率は、本回路が提供する制限した電圧増大率により、かなり減少することはない。

本発明のその他の目的および利点については、以下の説明および特許請求の範囲の記載から明らかとなる。

【0006】

【実施の形態】

以下、本発明について、好ましい実施形態にてしかも添付図面を参照して詳細に説明する。

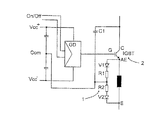

図1に示すように、半導体素子(この場合は、絶縁ゲート形バイポーラトランジスタ(IGBT)は、この素子に接続したゲート・ドライバによって制御する。ゲート・ドライバとしては、予め製作された市販の回路素子が普通使用されるが、ゲート・ドライバは、適当なディスクリートの素子を使って作ることもできる。ゲート・ドライバの主な機能は、半導体スイッチを導通状態へそしてそれに対応して導通状態からへと制御することである。加えて、この制御の後、このドライバは、この素子を制御した先の状態において信頼性良く維持しなければならない。電力消費のため、1つの状態から別の状態へ制御することは、可能な限り素早く行うことが最も有利であり、その理由は、IGBTのような半導体素子における最大の電力損失が、その制御が起きるときに発生するからである。図1のゲート・ドライバは、バイポーラ補助電圧Vcc+, Vcc−を印加する。したがって、素子は、高速に非導通状態にすることができ、そしてさらに、IGBTのエミッタと比べ負のゲートに接続した電圧によりその非導通状態に信頼性良く維持する。これは、この素子が、どのような誘起される電圧および電流パルスによってもターンオンされるのを防止する。

【0007】

補助電圧Vcc+およびVcc−並びにそれらの中間のゼロ電位Comは、ゲート・ドライバのロジック・レベル制御信号On/Offを、この半導体素子の制御を可能にする大きさまで増幅できるようにする。IGBTは、そのゲートGに対し、エミッタEと比べ正の電圧を印加することにより導通状態にすることができる。ゲート・ドライバのゼロ電位は、IGBTエミッタに接続し、したがってゲート・ドライバが、補助電圧Vcc+, Vcc−を使ってターンオンおよびターンオフのために必要な正および負の電圧をそのゲートに供給できるようにする。

本発明によれば、ゲート・ドライバGDのゼロ電位端子と半導体素子のエミッタEとの間には、抵抗器R1と、これに直列接続のダイオードV1を接続し、これら2つは、これらに並列接続した抵抗器R2と、抵抗器R2に直列接続したダイオードV2を有する。さらに、ゲート・ドライバGDのゼロ電位端子と半導体素子のコレクタとの間には、フィードバック・キャパシタC1を接続している。本発明においては、ダイオードV1とV2は、これらを設ける極性により、半導体素子のコレクタ−エミッタ間電圧の変化により生ずるキャパシタC1を通る電流が、この電流の方向に依存して、一時に1つの抵抗器のみを流れることができるようにしている。

【0008】

ターンオン時には、ゲート・ドライバは、その出力に、正の補助電圧Vcc+の大きさの電圧を供給し、この電圧は、通常は+15ボルトであってゲート電流を発生し、これが、IGBTのゲート電圧を、ターンオフ時には通常の−7ボルトの負の補助電圧Vcc−から、素子の約10ボルトのしきい値電圧に向かって増大させる。そのしきい値電圧に達すると、IGBTは、導通状態に移り、そしてそのコレクタ電圧は降下し始める。次に、これは、キャパシタC1と抵抗器R1とダイオードV1を通る電流を発生し、この電流は、抵抗器R1とダイオードV1に電圧損失を生じさせ、これがゲート・ドライバのゼロ電位端子ComをエミッタEに対し負の方向の移動させる。エミッタ電位に対し有効なゲート電圧がしきい値電圧よりも低くなると、ゲート電荷は減少し始め、そしてこれは、コレクタ電圧の変化率が減少することを意味する。このことは、キャパシタC1を通る電流が減少し、R1における電圧損失が低減することを意味する。この電圧損失の程度は、キャパシタC1のキャパシタンス、抵抗器R1の抵抗、およびコレクタ電圧の変化率とに依存する。適当な素子値では、最終的な結果は、コレクタ電圧変化率が、ターンオン・プロセス全体の間に渡ってほとんど一定に留まる。

【0009】

ターンオフ時には、類似のプロセスが生じる。ゲート電圧がしきい値電圧のレベルにまで減少すると、コレクタ電圧は、大きくなり始める。このとき、C1を通る電流は、抵抗器R2とダイオードV2を通るようにされ、そしてこれが抵抗器R2とダイオードV2において生じさせる電圧損失は、ゲート・ドライバのゼロ電位を、エミッタEに対し正の方向に移動させる。R2の抵抗は、通常はR1の抵抗の2倍または3倍の大きさであり、したがって、同じ量の電流により生じる電圧損失もまた、それに対応して大きくなる。より大きな電圧損失が必要であるが、その理由は、しきい値電圧が、正のターンオン電圧よりも負のターンオフ電圧とはより異なっているからである。

【0010】

図1に示した本発明の接続法によれば、抵抗結合1は、2つの逆並列接続した抵抗器R1,R2とダイオードV1,V2の直列接続のものから成っている。この配列により、ゲート電圧の変化を半導体素子のターンオンおよびターンオフのために別々に選択できるようになる。2つの別々の抵抗器をダイオードと一緒に使用することは有利であるが、それは、ターンオンおよびターンオフ時において、最適動作に必要な電圧が通常異なったものとなるからである。ターンオン時においては、ゲート電圧は減少して、このゲート電圧がゲート・ドライバのフルの正補助電圧Vcc+(この値は、通常は+15ボルト)に上昇する前に、素子をターンオンするのに必要なしきい値電圧以下にその電圧を瞬間的に降下させる。ターンオン時には、電流が抵抗器R1とダイオードV1を流れる(ダイオードV1のカソードはフィードバック・キャパシタC1に接続している)。

【0011】

ターンオフ時には、抵抗器R2において生じた電圧降下は、半導体素子のゲートを瞬間的にしきい値電圧よりも上に保つのに使用し、これにより、この素子を所要の変化率でターンオフされるのを可能にする。ターンオフ時において、ゲート電圧は、次にゲート・ドライバの負補助電圧Vcc−(これは通常−7ボルト)と等しくなるようにする。ターンオフにおいて、フィードバック・キャパシタにおける電流の方向は、ターンオン時におけるのと異なっており、したがってダイオードV1,V2は、異なった方向の電流により生じるゲート電圧変化を決めるのに使用することができる。

本発明は、バイポーラ補助電圧を含むゲート・ドライバに関して説明したが、本発明は、ユニポーラ補助電圧を含むゲート・ドライバで実施することも同様に行うことができる。

【0012】

図2は、本発明の1つの好ましい実施形態を示すものであって、ダイオードV1,V2と抵抗器R1,R2は、1つの直列接続をゲート・ドライバのゼロ電位Comから半導体素子の補助エミッタAEへ、そして他方の直列接続をエミッタEへ接続することにより、互いに直列接続している。これら直列接続におけるダイオードの方向は、半導体素子の補助エミッタAEにダイオードV1のアノードが接続し、しかもこれに対応してエミッタEに第2のダイオードV2のカソードが接続するような向きにしている。補助エミッタは、半導体素子の1つの電極であり、そしてこれは、IGBTのような半導体素子の電位を決定するためにのみ通常使用されて、この素子がゲートから信頼性良く制御できるようにする。エミッタは、さらに、エミッタ電流が流れるよう意図した電極である。この補助エミッタとエミッタとは、互いに電気的に直接接続状態にある。図2に示した接続においては、補助エミッタとエミッタとを接続する導体は、エミッタ回路の浮遊インダクタンスLで示している。

【0013】

図2に図示したこの接続法は、図1に示した接続法と全く同じ効果を提供する。得られる追加の利点は、短絡の場合における半導体素子を流れるおそれのある強電流の抑制にある。短絡が発生すると、IGBTのような半導体素子の飽和電圧は、強力に大きくなって、これによりフィードバック・キャパシタC1と抵抗結合1とをさらに作用させてゲート電圧を増加させるようにする。したがって、この好ましい実施形態は、半導体素子のエミッタ回路の浮遊インダクタンスLを用いることによって、短絡時のゲート電圧を減少させ、かつこれにより短絡電流の最大値を穏やかに抑制する。

パワー半導体のエミッタ回路は、常に内部浮遊インダクタンスを含み、エミッタ電流が変化するとき、このインダクタンスにある量の電圧損失が残る。この電圧降下の量は、例えばエミッタ電流の変化率に依存する。図2に示した状況においては、急速に増大する短絡電流がエミッタ回路の浮遊インダクタンスLに電圧損失を生じさせるとき、これは、補助エミッタとエミッタとの間の電圧として示され、エミッタが補助エミッタよりもより負となる。抵抗器R1とR2との間の点もまた、補助エミッタよりもより負となり、これは、半導体素子のゲート電圧に対する基準を与える。

【0014】

また、抵抗器R1とR2との間の点は、ゲート・ドライバのゼロ電位Com、あるいはゲート・ドライバの正および負の電源電圧の共通の中間点であり、これは、ゲート電圧が、補助エミッタ電圧に対し相対的に減少する傾向にあることを意味する。ゲート電圧のこの減少は、素子を流れる電流が抑制されることを意味し、これは、短絡状況においては望ましい結果となる。

当業者には明らかなように、技術の進歩につれ、本発明の基本となる思想は、種々の方法で実施することができる。したがって、本発明並びにその実施形態は、上述の例に制限されるものではなく、特許請求の範囲内で変化し得るものである。

【図面の簡単な説明】

【図1】本発明の制御回路を示す。

【図2】本発明の好ましい実施形態を示す。

【符号の説明】

GD ゲート・ドライバ

E エミッタ

AE 補助エミッタ

C コレクタ

G ゲート

V1,V2 ダイオード

R1,R2 抵抗器

C1 フィードバック・キャパシタ

Com ゼロ電位端子

L 浮遊インダクタンス

Claims (3)

- エミッタ(E)、コレクタ(C)およびゲート(G)を含む半導体素子(2)を制御する制御回路であって、ゲート・ドライバ(GD)を含み、該ゲート・ドライバの出力を制御すべき前記半導体素子のゲート(G)に接続した、前記の制御回路において、該制御回路がさらに、

抵抗結合(1)であって、ダイオード(V1,V2)と抵抗器(R1,R2)の2つの直列接続を逆並列接続でかつ前記半導体素子(2)のエミッタ(E)と前記ゲート・ドライバ(GD)のゼロ電位(Com)との間に接続した、前記の抵抗結合(1)と、

前記半導体素子(2)のコレクタ(C)と、前記ゲート・ドライバの前記ゼロ電位(Com)に接続した前記抵抗結合(1)の端部との間に接続したフィードバック・キャパシタ(C1)と、

を含むこと、を特徴とする制御回路。 - 補助エミッタも含む半導体素子をもつ請求項1記載の制御回路において、前記抵抗結合(1)は、前記ダイオード(V1,V2)と前記抵抗器(R1,R2)の2つの直列接続を含み、第1の直列接続(V1,R1)は、前記ゲート・ドライバのゼロ電位(Com)と前記半導体素子の前記補助エミッタ(AE)との間に接続し、前記ダイオード(V1)のアノードは前記半導体素子の前記補助エミッタに接続し、第2の直列接続(V2,R2)は、前記ゲート・ドライバの前記ゼロ電位(Com)と前記半導体素子の前記エミッタ(E)との間に接続し、前記ダイオード(V2)のカソードは、前記半導体素子の前記エミッタに接続したこと、を特徴とする制御回路。

- 請求項1または2に記載の制御回路であって、前記半導体素子(2)は、IGBトランジスタであること、を特徴とする制御回路。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FI981740A FI105508B (fi) | 1998-08-12 | 1998-08-12 | Ohjainpiiri |

| FI981740 | 1998-08-12 | ||

| FI982046A FI105509B (fi) | 1998-08-12 | 1998-09-23 | Ohjainpiiri |

| FI982046 | 1998-09-23 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000089838A JP2000089838A (ja) | 2000-03-31 |

| JP3602011B2 true JP3602011B2 (ja) | 2004-12-15 |

Family

ID=26160628

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP22772599A Expired - Fee Related JP3602011B2 (ja) | 1998-08-12 | 1999-08-11 | 制御回路 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6184740B1 (ja) |

| EP (1) | EP0980141B1 (ja) |

| JP (1) | JP3602011B2 (ja) |

| AT (1) | ATE249110T1 (ja) |

| DE (1) | DE69910920T2 (ja) |

| FI (1) | FI105509B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5193657B2 (ja) * | 2008-04-03 | 2013-05-08 | 日立オートモティブシステムズ株式会社 | インバータ装置 |

| KR20150140304A (ko) * | 2013-04-04 | 2015-12-15 | 티엠4 인코포레이티드 | 정류 셀 및 그 보상 회로 |

| CN105765850B (zh) * | 2013-11-01 | 2019-11-05 | Tm4股份有限公司 | 被配置用于限制切换过压的电力变换器 |

| US9882465B2 (en) * | 2013-11-14 | 2018-01-30 | Tm4 Inc. | Commutation cell, power converter and compensation circuit having dynamically controlled voltage gains |

| WO2015070344A1 (en) * | 2013-11-14 | 2015-05-21 | Tm4 Inc. | Compensation circuit, commutation cell and power converter controlling turn-on and turn-off of a power electronic switch |

| JP6819256B2 (ja) * | 2016-12-07 | 2021-01-27 | 富士電機株式会社 | 駆動回路及び該回路を含んでなる半導体モジュール |

| FR3115172B1 (fr) | 2020-10-09 | 2024-01-19 | Valeo Siemens Eautomotive Norway As | Circuit électronique de commande d’un transistor à effet de champ |

| WO2023157185A1 (ja) * | 2022-02-17 | 2023-08-24 | 三菱電機株式会社 | ゲート駆動回路及び電力変換装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01268451A (ja) * | 1988-04-15 | 1989-10-26 | Mitsubishi Electric Corp | 半導体素子の過電圧抑制回路 |

| EP0614278B1 (en) | 1988-11-16 | 1998-01-28 | Fuji Electric Co., Ltd. | Drive circuit for use with voltage-driven semiconductor device |

| FR2671241B1 (fr) | 1990-12-27 | 1997-04-30 | Peugeot | Circuit de commande d'un transistor de puissance utilise en commutation forcee. |

| JP3126565B2 (ja) * | 1993-11-01 | 2001-01-22 | 株式会社東芝 | Ac/dc変換器 |

| FR2713029B1 (fr) * | 1993-11-22 | 1995-12-29 | Gec Alsthom Transport Sa | Dispositif d'alimentation de circuit de commande de composant interrupteur de puissance. |

| JPH0829725A (ja) | 1994-05-10 | 1996-02-02 | Canon Inc | 複眼式画像表示装置 |

| SE9500761D0 (sv) | 1995-03-02 | 1995-03-02 | Abb Research Ltd | Skyddskrets för seriekopplade krafthalvledare |

| JP3125622B2 (ja) | 1995-05-16 | 2001-01-22 | 富士電機株式会社 | 半導体装置 |

| JP3373704B2 (ja) * | 1995-08-25 | 2003-02-04 | 三菱電機株式会社 | 絶縁ゲートトランジスタ駆動回路 |

| EP0814564A1 (en) | 1996-06-20 | 1997-12-29 | ANSALDO INDUSTRIA S.p.A. | Electronic switching circuit with reduction of switching transients |

| JP3356783B2 (ja) | 1996-07-05 | 2002-12-16 | 株式会社日立製作所 | 電力変換装置及びモータ制御装置 |

| SE515457C2 (sv) * | 1996-09-20 | 2001-08-06 | Abb Research Ltd | Metod och anordning vid effektransistor |

| JP3067687B2 (ja) * | 1997-05-08 | 2000-07-17 | 富士電機株式会社 | Igbt駆動回路 |

-

1998

- 1998-09-23 FI FI982046A patent/FI105509B/fi not_active IP Right Cessation

-

1999

- 1999-07-19 US US09/357,240 patent/US6184740B1/en not_active Expired - Lifetime

- 1999-07-23 DE DE69910920T patent/DE69910920T2/de not_active Expired - Lifetime

- 1999-07-23 AT AT99660126T patent/ATE249110T1/de not_active IP Right Cessation

- 1999-07-23 EP EP99660126A patent/EP0980141B1/en not_active Expired - Lifetime

- 1999-08-11 JP JP22772599A patent/JP3602011B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| FI982046A0 (fi) | 1998-09-23 |

| DE69910920D1 (de) | 2003-10-09 |

| JP2000089838A (ja) | 2000-03-31 |

| FI982046L (fi) | 2000-02-13 |

| EP0980141A1 (en) | 2000-02-16 |

| ATE249110T1 (de) | 2003-09-15 |

| US6184740B1 (en) | 2001-02-06 |

| DE69910920T2 (de) | 2004-07-22 |

| FI105509B (fi) | 2000-08-31 |

| EP0980141B1 (en) | 2003-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10164550B2 (en) | Method, circuit configuration and bridge circuit for charging a capacitance effective on main current terminals of semiconductor switch | |

| CN101079576B (zh) | 用于提供对电源调节器的开关的系统 | |

| KR0140227B1 (ko) | 전자제어회로, 전자식 정류모터 시스템, 스위칭조정식 전원공급장치 및 그 제어방법 | |

| US7830196B2 (en) | Semiconductor device alleviating or preventing surge voltage | |

| CN113098469A (zh) | 用于GaN开关的时间可编程失效安全下拉电路 | |

| US4356416A (en) | Voltage controlled non-saturating semiconductor switch and voltage converter circuit employing same | |

| US6909620B2 (en) | Inverter configurations with shoot-through immunity | |

| CN111865086B (zh) | 自供电控制电路及控制方法以及开关电源电路 | |

| US7701279B2 (en) | Driving circuit for an emitter-switching configuration | |

| US7660094B2 (en) | Inverter circuit | |

| US20170346480A1 (en) | High-Voltage Stacked Transistor Circuit | |

| US4547686A (en) | Hybrid power semiconductor switch | |

| JP2023516357A (ja) | パワーデバイスの駆動回路及び駆動システム | |

| US6229356B1 (en) | Stabilized gate drivers | |

| US5570057A (en) | Three-terminal insulated-gate power electronic device with a variable-slope saturated output characterisitic depending in a discontinuous way on the output current | |

| US7248093B2 (en) | Bipolar bootstrap top switch gate drive for half-bridge semiconductor power topologies | |

| US7019579B2 (en) | Circuit arrangement for rapidly controlling in particular inductive loads | |

| JP3602011B2 (ja) | 制御回路 | |

| JP2022135911A (ja) | バイポーラパルス電圧ゲートドライバ | |

| EP3764527B1 (en) | Switching device and method for controlling switching device | |

| JP4110052B2 (ja) | インバータ回路 | |

| US20080197904A1 (en) | Circuit Arrangement for Switching a Load | |

| GB2053606A (en) | Improvements in and relating to semiconductor switching circuits | |

| JP2001169534A (ja) | 絶縁ゲート型半導体素子のゲート回路 | |

| CN110932528B (zh) | 自供电控制电路及控制方法以及开关电源电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040907 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040921 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20071001 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081001 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091001 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101001 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101001 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111001 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111001 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121001 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131001 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |