JP3576228B2 - 表面実装型半導体装置 - Google Patents

表面実装型半導体装置 Download PDFInfo

- Publication number

- JP3576228B2 JP3576228B2 JP25730694A JP25730694A JP3576228B2 JP 3576228 B2 JP3576228 B2 JP 3576228B2 JP 25730694 A JP25730694 A JP 25730694A JP 25730694 A JP25730694 A JP 25730694A JP 3576228 B2 JP3576228 B2 JP 3576228B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor element

- semiconductor device

- resin

- wiring board

- electrode pads

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

Landscapes

- Lead Frames For Integrated Circuits (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Wire Bonding (AREA)

Description

【産業上の利用分野】

本発明は,半導体素子を搭載する樹脂封止型の表面実装型半導体装置(プラスチックパッケージ)に関し、詳しくは、高集積化、高機能化に対応できる表面実装型半導体装置に関する。

【0002】

【従来の技術】

従来より、樹脂封止型の半導体装置の組立て部材として用いられているリードフレーム(単層リードフレームと言う)は、一般に、図5に示すような形状をしており、半導体素子を搭載するためのダイパッド502とダイパッド502の周囲に設けられ、半導体素子と結線を行うためのインナーリード503と、該インナーリード503に連続し外部回路との結線を行うためのアウターリード504等を備えていた。

このような単層リードフレーム501は、通常、コバール、42合金(42%Ni−鉄)、銅系合金等の導電性に優れ、且つ強度が大きい金属板をフオトリソグラフイー技術を用いたエッチング加工方法やスタンピング法等により、図5に示すような形状に加工して作製されていた。

そしてこの単層リードフレーム501を用いた半導体装置は、図6に示すように単層リードフレーム601のダイパッド602に半導体素子605(以下単に素子とも言う)を搭載するとともに、素子のボンデイングパッド(図示せず)と、金や銀等の貴金属のメッキを施してあるインナーリード603、603aの先端部とを金等からなるワイヤ606により電気的に接続していた。

しかしながら、近年、半導体装置は、電子機器の高性能化と軽薄短小化の傾向(時流)からLSIのASICに代表されるように、ますます高集積化、高機能化になっている。このようなLSIの大規模集積化(高集積化)はウエハープロセスでの微細加工技術の進歩の上に成り立っており、より多くのゲートを1チップに収容でき、さらにチップサイズを小さくすることができるようになってきている。

【0003】

そして、この半導体チップの高集積化、高機能化は半導体チップの動作スピードの増加を招くこととなり、信号の高速処理のため、半導体チップ内の信号遅れよりパッケージ配線での信号の遅れの方が支配的になってきて、ノイズの問題も含めて半導体パッケージ内の電気的特性を改善する必要に迫られてきた。パッケージ内のインダクタンスが無視できない状況になってきたのである。

このようなパッケージ内のインダクタンスを低減するために、電源、グランドの端子数を多くし、実質的なインダクタンスを下げるようにして、ノイズの低減等電気的特性の改善をしてきた。

しかしながら、電源、グランドの接続端子数の増大は、半導体装置の総ピン数の増大にもなる。この端子数の増大は、リードフレームの加工限界から、インナーリード幅、ピッチをそのままとした場合には、インナーリード部をチップから離す傾向となり、リードフレームのインナーリード部を含むサイズは大きくなってしまい、半導体装置自体を逆に大きいものとしてしまう。

そこで、半導体装置サイズを変えずに入出力端子を増やす方法としてリードフレームのアウターリードのピッチを狭くする方法が採られてきた。

このアウターリードのピッチはこれまで1.0mmから0.8mm、0.5mmと徐々に狭くなってきているが、0.4mm、0.3mmと更にピッチが狭くなるにつれ、これら狭ピッチの実装工程が難しくなってきた。

【0004】

このような半導体装置の実装工程の難しさを回避する方法として、BGA(ボール・グリッド・アレイ)と呼ばれる半導体装置が開発されている。このBGAは、入出力端子を増やすために、BTレジン(ビスマレイミド系樹脂)を代表とする耐熱性を有する樹脂板を基材とする両面配線基板(プリント基板)の表面に半導体素子を搭載し、裏面に球状の半田を取付けた外部端子用電極を設け、スルーホールを通じて半導体素子と外部端子用電極との表裏導通をとっていた。裏面の球状の半田をアレイ状に並べることにより、端子ピッチの間隔を従来のリードフレームを用いた半導体装置より広くすることができ、この結果、半導体装置の実装工程の難しさの度合いを上げることなく入出力端子の増加に対応できた。

また、BGAでは電気特性の向上を図る場合は、基板を多層構造の多層配線基板とし、両面配線基板同様スルーホールを通じて半導体と外部端子用電極との導通をとっていた。

【0005】

【発明が解決しようとする課題】

しかしなから、従来のBGAは両面配線基板にスルーホールを設け、このスルーホールを通じて表裏の導通をとる必要があるため、半導体装置コストは従来の金属板をフオトエッチング法やスタンピング法等により製造されるリードフレームを用いたものより生産コストが高くなってしまうという問題もあった。

また、従来のBGAでは、基板樹脂の熱膨張の影響からスルーホールにて断線をおこすことがあり、信頼性の低下につながっていた。

そして、従来のBGAは両面配線基板(プリント基板)としてBTレジン(ビスマレイミド系樹脂)を代表とする耐熱性を有する樹脂板基材をコア材として用いているため熱抵抗が大きくなり、放熱性が悪くなってしまうという問題もあった。

本発明は、これらの問題を解決しようとするもので、上記のような信頼性低下を招かず、低コストで高放熱性で多端子半導体素子の実装が簡単に行える表面実装型半導体装置を提供しようとするものである。

【0006】

【課題を解決するための手段】

本発明の表面実装型半導体装置は、貫通穴を設けた片面配線基板の配線面に対向する面に絶縁層を介して、貫通穴を塞ぐ金属等からなる放熱板を設け、放熱板の貫通穴部側面に半導体素子を搭載した樹脂封止型の半導体装置であって、半導体素子は、半導体素子の端子が片面配線基板の配線面側に向くように搭載されており、片面配線基板の配線面には、半導体素子とワイヤにて電気的に結線された電極パッドと、外部端子用電極パッドと、前記半導体素子と電気的に結線された電極パッドと外部端子用電極パッドとを電気的に結線した配線とを、同一平面上に配し、上記半導体素子と、半導体素子と電気的結線された電極パッドと、外部端子用電極パッドとの領域以外はソルダーレジスト等の絶縁物によってマスキングされ、片面配線基板の配線面側の半導体素子全体と、半導体素子と電気的結線された電極パッドと、該半導体素子と電気的結線された電極パッドと半導体素子との結線部、とは樹脂封止され、放熱板は外部に露出しており、前記マスキングされていない外部端子用電極パッドから略球状に、樹脂部より外側に突出した半田部が設けられていることを特徴とするものである。

【0007】

【作用】

本発明の表面実装型半導体装置は、上記のような構成にすることにより、多端子半導体素子の実装ができ、且つ、高放熱性を可能としている。

詳しくは、金属等からなる放熱板を外部へ露出させて、ヒートシンク型としていることにより、放熱(熱放散性)に優れたものとしている。

そして、半導体素子の端子、半導体素子と電気的に結線した電極、外部端子用電極を全て配線基板の一面側に形成することにより、従来のBGAのように、スルホールを介して半導体素子と外部端子を結線する必要がないものとしている。BTレジン(ビスマレイミド系樹脂)を代表と耐熱性を有する樹脂材を基材とする片面配線基板を用いていることによりその作製を容易なものとしており、且つ、低コストの作製を可能としている。

【0008】

【実施例】

本発明の表面実装半導体装置の実施例を以下、図にそって説明する。

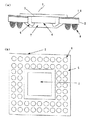

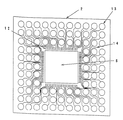

図1(a)は本発明の実施例表面実装半導体装置の断面図であり、図1(b)は本発明の実施例表面実装半導体装置の平面図で、図3〜5は本実施例表面実装半導体装置の内部構造を示した概略平面図である。

図中、1は表面実装半導体装置、2は片面配線基板、3は金属板、4は半導体素子、4Aは半導体素子端子、5は半導体素子搭載部、6はワイヤ、7は樹脂、8は半田、9はソルダーレジスト、12は半導体素子との結線用電極パッド、13は外部端子用電極パッド、14は配線、15は絶縁層、16は貫通穴である。本実施例表面実装半導体装置は、図1に示すように半導体素子3の厚みに略相当する片面配線基板2に貫通穴16を設け、この貫通穴16部に半導体素子を、金属板3を介して搭載したものである。

片面配線基板2の配線面側には、半導体素子と電気的結線された電極パッド12と、外部端子用電極パッド13と、前記半導体素子と電気的に結線された電極パッド12と外部端子用電極パッド13とを電気的結線した配線14とを配している。

半導体素子4と、半導体素子と電気的結線された電極パッド12と、外部端子電極パッド13との領域以外はソルダーレジスト等の絶縁物によってマスキングされている。

又、片面配線基板2の配線面側の半導体素子全体と、半導体素子と電気的結線された電極パッドと、該半導体素子と電気的結線された電極パッドと半導体素子との結線部、とは樹脂封止されており、片面配線基板2の配線面側でない面に設けられた金属板3は外部に露出している。

ソルダーレジスト等の絶縁物によってマスキングされていない外部端子用電極パッド13から略球状に、樹脂部8より外側に突出した半田8が設けられている。

そして、半導体素子3の端子3Aと半導体素子3との結線用電極パッド12はワイヤ5により結線され、半導体素子との結線用電極パッド12と外部端子用電極パッド13とは配線部14により結線されている。

【0009】

片面配線基板2は、基材(コア材)としてBTレジン(ビスマレイミド系樹脂)を用いたが、これに限定されるものでなく、他に、紙基材フエノール樹脂や紙基材エポキシ樹脂などの積層板の片側に銅(Cu)箔を接着した基板を用いても良い。

金属板3は、ヒートシンク型の放熱板であり、実施例ではCu材であるが、これに限定はされない。放熱性のものであれば、特に金属である必要もない。

【0010】

次いで、上記実施例の表面実装半導体装置の製造方法を挙げ、図2に沿って説明する。図2は製造工程を説明するため要部の概略図である。

先ず、略半導体素子の厚みに相当するBTレジン(ビスマレイミド系樹脂)を基材2Aとし、Cu箔2Bを片面に覆ったからなる片面配線基板用基材2を用意し(図2(a))、片面配線基板用基材2に、半導体素子を収納できるスペースでドリル等により貫通穴16をあけた後に、片面配線基板用基材2のCu箔2Bがある面とは反対側の面に絶縁層(樹脂層)15を形成する(図2(b))。この絶縁層15の形成方法としては、スクリーン印刷法でも、フイルム上の絶縁性樹脂を熱圧着しても良い。

次いで、Cu箔2B上に、Cu箔からなる半導体素子との結線用電極パッド12、外部端子用電極パッド13と、前記半導体素子と電気的に結線された電極であるパッド12と外部端子用電極パッド13とを電気的結線した配線14を作製する為、耐腐蝕性膜としてのレジストパターンを所定の形状に作製する(図2(c)。レジストパターンの作製方法としては、スクリーン印刷方法あるいはリソグラフイー法が挙げられる。リソグラフイー法の場合は液状レジストあるいはドライフイルムレジストが用いられる。

この後、所定のパターンに形成されたレジストを耐腐蝕性膜として、Cu箔を腐蝕液によりエッチングして(図2(d))、レジストを剥離して所定のパターンに対応したCU箔のパターンを作製した(図2(e))。このとき状態を示したものが図3である。

次いで、片面配線基板用基材2Aの、配線面に対向する側の面より、絶縁層を介して、貫通穴16を塞ぐように金属板3を接着する。(図2(f))

この後、半導体素子領域(貫通穴16部)や半導体素子との結線用電極パッド12領域、外部端子用電極パッド13領域のみを露出させた状態にソルダーレジスト9を覆った後、ソルダーレジスト9から露出した、ワイヤボンデイングを後に行う半導体素子と電気的に結線される電極パッド12と外部端子用の電極パッド13に電解金メッキを施しておく。(図2(g))

次いで、貫通穴16側の金属3の面上に、半導体素子4を端子4Aが、片面配線基板の配線面側に向くように、にして搭載した。(図2(h))

半導体素子を搭載した後、半導体素子4の端子4A部と電気的に結線される電極パッド12とを金線からなるワイヤ408にてボンデイング結線した(図2(i))。このときの状態を示したものが図4である。

ボンデイング結線後、半導体素子4、ワイヤ6、半導体素子4との結線用の電極パッド12を含む所定領域をイオン性不純物の含有量が少ないエポキシからなる樹脂7にて樹脂封止した(図2(j))。樹脂封止は、モールド樹脂封止、ポッテイング樹脂封止のいずれの方法でも可能である。

次いで、ソルダーレジスト9から露出した外部端子用電極パッド13部上の金メッキ20部上に球状に半田8を作製して(図2(k))、表面実装半導体装置を得た。この状態に相当するものが図1である。

球状の半田8の作製は、金メッキされている外部端子用電極パッド404にフラックスを供給した後、0.8mmφ程度の半田ボールを搭載し、リフローすることにより行う。

【0011】

【発明の効果】

本発明の表面実装型半導体装置は、以上のように、従来のBGA(ボール・グリッド・アレイ)のように、スルホールを設けた複雑な構造ではないため、製造コストを大幅に削減でき、信頼性も高くしている。

そして、半導体素子を金属等からなる放熱板上に搭載して、且つ、金属板が半導体装置の外側表面にでた、ヒートシンク型となっていることにより、放熱性に優れたものとしており、従来のBGAよりも格段と放熱性の面ではすぐれた構造としている。

【図面の簡単な説明】

【図1】実施例表面実装型半導体装置の平面図および断面図

【図2】本発明の表面実装型半導体装置の製造方法実施例の工程図

【図3】本発明の表面実装型半導体装置の製造工程における状態を示した図

【図4】本発明の表面実装型半導体装置の製造工程における状態を示した図

【図5】従来の単層リードフレームを示す図

【図6】従来の単層リードフレームを用いた半導体装置の要部を示す図

【符号の説明】

1 表面実装半導体装置

2 片面配線基板

2A 基材

2B Cu箔

3 金属板

4 半導体素子

4A 半導体素子端子

5 半導体素子搭載部

6 ワイヤ

7 樹脂

8 半田

9 ソルダーレジスト

12 半導体素子との結線用電極パッド

13 外部端子用電極パッド

14 配線

15 絶縁層

16 貫通穴

17 レジストパターン

501 単層リードフレーム

502 ダイパッド

503 インナーリード

504 アウターリード

601 単層リードフレーム

602 ダイパッド

603、603a インナーリード

605 半導体素子

606 ワイヤ

Claims (1)

- 貫通穴を設けた片面配線基板の配線面に対向する面に絶縁層を介して、貫通穴を塞ぐ金属等からなる放熱板を設け、放熱板の貫通穴部側面に半導体素子を搭載した樹脂封止型の半導体装置であって、半導体素子は、半導体素子の端子が片面配線基板の配線面側に向くように搭載されており、片面配線基板の配線面には、半導体素子とワイヤにて電気的に結線された電極パッドと、外部端子用電極パッドと、前記半導体素子と電気的に結線された電極パッドと外部端子用電極パッドとを電気的に結線した配線とを、同一平面上に配し、上記半導体素子と、半導体素子と電気的結線された電極パッドと、外部端子用電極パッドとの領域以外はソルダーレジスト等の絶縁物によってマスキングされ、片面配線基板の配線面側の半導体素子全体と、半導体素子と電気的結線された電極パッドと、該半導体素子と電気的結線された電極パッドと半導体素子との結線部、とは樹脂封止され、放熱板は外部に露出しており、前記マスキングされていない外部端子用電極パッドから略球状に、樹脂部より外側に突出した半田部が設けられていることを特徴とする表面実装型半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP25730694A JP3576228B2 (ja) | 1994-09-28 | 1994-09-28 | 表面実装型半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP25730694A JP3576228B2 (ja) | 1994-09-28 | 1994-09-28 | 表面実装型半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH0897315A JPH0897315A (ja) | 1996-04-12 |

| JP3576228B2 true JP3576228B2 (ja) | 2004-10-13 |

Family

ID=17304531

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP25730694A Expired - Fee Related JP3576228B2 (ja) | 1994-09-28 | 1994-09-28 | 表面実装型半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3576228B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6881611B1 (en) | 1996-07-12 | 2005-04-19 | Fujitsu Limited | Method and mold for manufacturing semiconductor device, semiconductor device and method for mounting the device |

| WO1999065076A1 (fr) * | 1998-06-05 | 1999-12-16 | Hitachi, Ltd. | Dispositif a semiconducteur et procede de fabrication |

| JP3269815B2 (ja) | 1999-12-13 | 2002-04-02 | 富士通株式会社 | 半導体装置及びその製造方法 |

-

1994

- 1994-09-28 JP JP25730694A patent/JP3576228B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH0897315A (ja) | 1996-04-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6025640A (en) | Resin-sealed semiconductor device, circuit member for use therein and method of manufacturing resin-sealed semiconductor device | |

| JP3947292B2 (ja) | 樹脂封止型半導体装置の製造方法 | |

| JPH06283650A (ja) | 半導体装置 | |

| JPH10294418A (ja) | 半導体装置 | |

| JPH0883865A (ja) | 樹脂封止型半導体装置 | |

| JPH09246427A (ja) | 表面実装型半導体装置の製造方法および表面実装型半導体装置 | |

| JP3576228B2 (ja) | 表面実装型半導体装置 | |

| KR100280083B1 (ko) | 인쇄회로기판 및 인쇄회로기판의 제조 방법과 이를 이용한 반도체패키지 | |

| JP2620611B2 (ja) | 電子部品搭載用基板 | |

| KR20020010489A (ko) | 집적 회로 패키지 | |

| JPH09116045A (ja) | リードフレームを用いたbgaタイプの樹脂封止型半導体装置およびその製造方法 | |

| JP2798108B2 (ja) | 混成集積回路装置 | |

| JP3297959B2 (ja) | 半導体装置 | |

| JP3585660B2 (ja) | 表面実装型半導体装置の製造方法 | |

| JPH08139259A (ja) | リードフレームとリードフレーム部材、およびそれらを用いた表面実装型半導体装置 | |

| JP3030605B2 (ja) | 半導体装置 | |

| JPH03120851A (ja) | 半導体搭載用基板 | |

| JPH118260A (ja) | 樹脂封止型半導体装置の製造方法 | |

| JPH03161957A (ja) | 半導体装置 | |

| JPH09199631A (ja) | 半導体装置の構造と製造方法 | |

| JP3475310B2 (ja) | リードフレーム、リードフレーム部材および半導体装置 | |

| JP2784209B2 (ja) | 半導体装置 | |

| JPH04119653A (ja) | 集積回路素子 | |

| JPH0855931A (ja) | 面実装半導体搭載装置及び面実装半導体搭載装置用基板 | |

| JPH05166971A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20040302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040427 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20040510 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040622 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040707 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080716 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090716 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090716 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100716 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100716 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110716 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120716 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120716 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |