JP2018113414A - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP2018113414A JP2018113414A JP2017004445A JP2017004445A JP2018113414A JP 2018113414 A JP2018113414 A JP 2018113414A JP 2017004445 A JP2017004445 A JP 2017004445A JP 2017004445 A JP2017004445 A JP 2017004445A JP 2018113414 A JP2018113414 A JP 2018113414A

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- resin layer

- resin

- semiconductor device

- semiconductor element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/562—Protection against mechanical damage

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5383—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/921—Connecting a surface with connectors of different types

- H01L2224/9212—Sequential connecting processes

- H01L2224/92122—Sequential connecting processes the first connecting process involving a bump connector

- H01L2224/92125—Sequential connecting processes the first connecting process involving a bump connector the second connecting process involving a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5385—Assembly of a plurality of insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

Landscapes

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Wire Bonding (AREA)

Abstract

Description

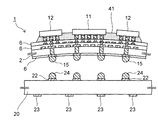

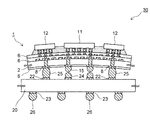

本実施形態に係る半導体装置について、その製造工程を追いながら説明する。

図13は、第1例に係る樹脂層40の平面レイアウトについて示す平面図である。

図14は、第2例に係る樹脂層40の平面レイアウトについて示す平面図である。

図15は、第3例に係る樹脂層40の平面レイアウトについて示す平面図である。

図16は、第4例に係る樹脂層40の平面レイアウトについて示す平面図である。

第1実施形態では、図7(b)に示したように、リフローによりはんだバンプ13を溶融し、回路基板1と各半導体素子11、12とを接続した。

第2実施形態では、図19(b)〜図20(b)に示したように、TCB法で回路基板1に各半導体素子11、12を搭載した後に、回路基板1と各半導体素子11、12との間にアンダーフィル樹脂41を充填した。

Claims (10)

- 無機材料の基板と、前記基板の上に形成された樹脂絶縁層とを備えた回路基板と、

前記回路基板の主面にバンプを介して搭載された半導体素子と、

前記半導体素子の横の前記主面に形成され、前記回路基板の縁と対角線の少なくとも一方に沿って延び、かつ前記基板よりも熱膨張率が大きな樹脂層と、

を有することを特徴とする半導体装置。 - 前記樹脂層は、平面視において、前記回路基板の四辺の縁に沿って延びるリング状であることを特徴とする請求項1に記載の半導体装置。

- 前記樹脂層は、平面視において、前記回路基板の相対する二辺に沿って帯状に延びることを特徴とする請求項1に記載の半導体装置。

- 前記樹脂層の端部に、前記二辺とは異なる前記回路基板の残りの二辺に沿って延びる延長部を設けたことを特徴とする請求項3に記載の半導体装置。

- 前記樹脂層の上面の高さは、前記半導体素子の上面の高さよりも低いことを特徴とする請求項1に記載の半導体装置。

- 前記樹脂層は、前記樹脂絶縁層よりも厚いことを特徴とする請求項1に記載の半導体装置。

- 無機材料の基板と、前記基板の上に形成された樹脂絶縁層とを備えた回路基板の主面に、前記回路基板の縁と対角線の少なくとも一方に沿って延びる樹脂層を形成する工程と、

前記回路基板の前記主面に、バンプを備えた半導体素子を搭載する工程と、

前記樹脂層を形成する工程の後に、前記バンプを加熱して溶融することにより、前記バンプを介して前記回路基板と前記半導体素子とを接続する工程と、

を有することを特徴とする半導体装置の製造方法。 - 前記樹脂層の材料として熱硬化性樹脂を採用すると共に、

前記バンプを加熱する工程において前記樹脂層を熱硬化させることを特徴とする請求項7に記載の半導体装置の製造方法。 - 前記回路基板の前記主面と前記半導体素子との間にアンダーフィル樹脂を充填する工程を更に有し、

前記樹脂層を形成する工程において、前記アンダーフィル樹脂よりも粘度が高い樹脂を前記樹脂層の材料として使用することを特徴とする請求項7に記載の半導体装置の製造方法。 - 前記樹脂層の材料として熱硬化性樹脂を採用すると共に、

前記回路基板の前記主面にアンダーフィル樹脂を塗布する工程を更に有し、

前記回路基板の前記主面に前記半導体素子を搭載する工程において、前記主面と前記半導体素子との間に前記アンダーフィル樹脂を介在させ、

前記バンプを加熱する工程において、前記樹脂層と前記アンダーフィル樹脂とを同時に熱硬化させることを特徴とする請求項7に記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017004445A JP2018113414A (ja) | 2017-01-13 | 2017-01-13 | 半導体装置とその製造方法 |

| US15/866,725 US20180204807A1 (en) | 2017-01-13 | 2018-01-10 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017004445A JP2018113414A (ja) | 2017-01-13 | 2017-01-13 | 半導体装置とその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018113414A true JP2018113414A (ja) | 2018-07-19 |

| JP2018113414A5 JP2018113414A5 (ja) | 2019-10-10 |

Family

ID=62841024

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017004445A Pending JP2018113414A (ja) | 2017-01-13 | 2017-01-13 | 半導体装置とその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20180204807A1 (ja) |

| JP (1) | JP2018113414A (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11387176B2 (en) * | 2017-03-14 | 2022-07-12 | Mediatek Inc. | Semiconductor package structure |

| US10784211B2 (en) | 2017-03-14 | 2020-09-22 | Mediatek Inc. | Semiconductor package structure |

| US11171113B2 (en) | 2017-03-14 | 2021-11-09 | Mediatek Inc. | Semiconductor package structure having an annular frame with truncated corners |

| US11264337B2 (en) | 2017-03-14 | 2022-03-01 | Mediatek Inc. | Semiconductor package structure |

| US11362044B2 (en) | 2017-03-14 | 2022-06-14 | Mediatek Inc. | Semiconductor package structure |

| EP3671831B1 (en) * | 2018-12-18 | 2024-09-18 | MediaTek Inc. | Semiconductor package structure |

| JP7069082B2 (ja) * | 2019-05-08 | 2022-05-17 | 三菱電機株式会社 | 電力用半導体装置およびその製造方法 |

| US11570903B2 (en) * | 2019-10-16 | 2023-01-31 | Advanced Micro Devices, Inc. | Process for conformal coating of multi-row surface-mount components in a lidless BGA package and product made thereby |

| KR20220029987A (ko) * | 2020-09-02 | 2022-03-10 | 에스케이하이닉스 주식회사 | 3차원 구조의 반도체 장치 |

| US11538760B2 (en) | 2020-12-17 | 2022-12-27 | Advanced Semiconductor Engineering, Inc. | Semiconductor package structure and method for manufacturing the same |

| US11694941B2 (en) * | 2021-05-12 | 2023-07-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor die package with multi-lid structures and method for forming the same |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11260960A (ja) * | 1998-03-11 | 1999-09-24 | Sony Corp | 半導体パッケージおよびその製造方法 |

| JP2005039206A (ja) * | 2003-07-18 | 2005-02-10 | Samsung Electronics Co Ltd | 半導体チップ表面実装方法 |

| JP2005252286A (ja) * | 2005-04-01 | 2005-09-15 | Hitachi Ltd | 自動車用制御コントロールユニットおよびその製造方法並びにicチップパッケージ |

| JP2007173862A (ja) * | 2003-06-24 | 2007-07-05 | Ngk Spark Plug Co Ltd | 中継基板、半導体素子付き中継基板、中継基板付き基板、半導体素子と中継基板と基板とからなる構造体 |

| JP2009027109A (ja) * | 2007-07-24 | 2009-02-05 | Taiyo Yuden Co Ltd | 電子部品の実装方法及び回路基板 |

| JP2011146519A (ja) * | 2010-01-14 | 2011-07-28 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2013106031A (ja) * | 2011-11-16 | 2013-05-30 | Samsung Electro-Mechanics Co Ltd | 半導体パッケージ及びその製造方法 |

| US8986806B1 (en) * | 2012-04-20 | 2015-03-24 | Amkor Technology, Inc. | Warpage control stiffener ring package and fabrication method |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20060051889A1 (en) * | 2004-09-08 | 2006-03-09 | Vinu Yamunan | Chip assembly reinforcement |

| JP5211493B2 (ja) * | 2007-01-30 | 2013-06-12 | 富士通セミコンダクター株式会社 | 配線基板及び半導体装置 |

| TW200950014A (en) * | 2008-05-23 | 2009-12-01 | Advanced Semiconductor Eng | Semiconductor package and method for manufacturing the same |

| JP5250524B2 (ja) * | 2009-10-14 | 2013-07-31 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US8143110B2 (en) * | 2009-12-23 | 2012-03-27 | Intel Corporation | Methods and apparatuses to stiffen integrated circuit package |

| KR101678539B1 (ko) * | 2010-07-21 | 2016-11-23 | 삼성전자 주식회사 | 적층 패키지, 반도체 패키지 및 적층 패키지의 제조 방법 |

| US8580683B2 (en) * | 2011-09-27 | 2013-11-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Apparatus and methods for molding die on wafer interposers |

| US9287194B2 (en) * | 2013-03-06 | 2016-03-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Packaging devices and methods for semiconductor devices |

| PL3058566T3 (pl) * | 2013-10-18 | 2018-07-31 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Kodowanie współczynników widmowych widma sygnału audio |

| US9627329B1 (en) * | 2014-02-07 | 2017-04-18 | Xilinx, Inc. | Interposer with edge reinforcement and method for manufacturing same |

| KR101676916B1 (ko) * | 2014-08-20 | 2016-11-16 | 앰코 테크놀로지 코리아 주식회사 | 반도체 디바이스의 제조 방법 및 이에 따른 반도체 디바이스 |

| US9379032B2 (en) * | 2014-09-15 | 2016-06-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor packaging having warpage control and methods of forming same |

| TWI641087B (zh) * | 2015-12-28 | 2018-11-11 | 矽品精密工業股份有限公司 | 電子封裝件及封裝用之基板 |

| JP6524003B2 (ja) * | 2016-03-17 | 2019-06-05 | 東芝メモリ株式会社 | 半導体装置 |

| US9899305B1 (en) * | 2017-04-28 | 2018-02-20 | Taiwan Semiconductor Manufacturing Company Ltd. | Semiconductor package structure |

-

2017

- 2017-01-13 JP JP2017004445A patent/JP2018113414A/ja active Pending

-

2018

- 2018-01-10 US US15/866,725 patent/US20180204807A1/en not_active Abandoned

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11260960A (ja) * | 1998-03-11 | 1999-09-24 | Sony Corp | 半導体パッケージおよびその製造方法 |

| JP2007173862A (ja) * | 2003-06-24 | 2007-07-05 | Ngk Spark Plug Co Ltd | 中継基板、半導体素子付き中継基板、中継基板付き基板、半導体素子と中継基板と基板とからなる構造体 |

| JP2005039206A (ja) * | 2003-07-18 | 2005-02-10 | Samsung Electronics Co Ltd | 半導体チップ表面実装方法 |

| JP2005252286A (ja) * | 2005-04-01 | 2005-09-15 | Hitachi Ltd | 自動車用制御コントロールユニットおよびその製造方法並びにicチップパッケージ |

| JP2009027109A (ja) * | 2007-07-24 | 2009-02-05 | Taiyo Yuden Co Ltd | 電子部品の実装方法及び回路基板 |

| JP2011146519A (ja) * | 2010-01-14 | 2011-07-28 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2013106031A (ja) * | 2011-11-16 | 2013-05-30 | Samsung Electro-Mechanics Co Ltd | 半導体パッケージ及びその製造方法 |

| US8986806B1 (en) * | 2012-04-20 | 2015-03-24 | Amkor Technology, Inc. | Warpage control stiffener ring package and fabrication method |

Also Published As

| Publication number | Publication date |

|---|---|

| US20180204807A1 (en) | 2018-07-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2018113414A (ja) | 半導体装置とその製造方法 | |

| JP3813797B2 (ja) | 半導体装置の製造方法 | |

| US9462693B2 (en) | Electronic device and method of manufacturing electronic device | |

| JP4899406B2 (ja) | フリップチップ型半導体装置 | |

| KR101655926B1 (ko) | 반도체장치 및 반도체장치의 제조방법 | |

| JP2006502587A (ja) | マルチチップパッケージ用のコンポーネント、方法およびアセンブリ | |

| US8811031B2 (en) | Multichip module and method for manufacturing the same | |

| JP6064705B2 (ja) | 半導体装置の製造方法および半導体実装基板 | |

| KR100858456B1 (ko) | 회로 기판 및 반도체 장치 | |

| KR20130129100A (ko) | 반도체 장치 및 그 제조 방법 | |

| JP5644264B2 (ja) | 半導体装置 | |

| US20200212019A1 (en) | Method for fabricating electronic package | |

| JP2009238854A (ja) | 半導体デバイスの実装構造体及び実装構造体を用いた電子機器 | |

| KR20080031107A (ko) | 반도체 장치 | |

| KR20070051165A (ko) | 프리 솔더 범프를 갖는 반도체 패키지와, 그를 이용한 적층패키지 및 그의 제조 방법 | |

| US9799596B2 (en) | Wiring substrate and semiconductor device | |

| KR101374144B1 (ko) | 워피지 방지 구조를 갖는 반도체 장치 | |

| JP6592977B2 (ja) | 半導体パッケージ基板、半導体パッケージおよびその製造方法 | |

| JP6464762B2 (ja) | 半導体パッケージ基板、および半導体パッケージと、半導体パッケージ基板の製造方法、および半導体パッケージの製造方法 | |

| JP6323672B2 (ja) | 半導体装置及びその製造方法 | |

| JP5284125B2 (ja) | 半導体装置およびその製造方法 | |

| JP2015220291A (ja) | 半導体装置及びその製造方法 | |

| US20230005830A1 (en) | Semiconductor apparatus | |

| JP5577734B2 (ja) | 電子装置および電子装置の製造方法 | |

| US20160029486A1 (en) | Solder joint structure and electronic component module including the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20180209 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20180215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190829 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190829 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200722 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200825 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201005 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20201104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210104 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20210104 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20210113 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20210119 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20210312 |

|

| C211 | Notice of termination of reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C211 Effective date: 20210316 |

|

| C22 | Notice of designation (change) of administrative judge |

Free format text: JAPANESE INTERMEDIATE CODE: C22 Effective date: 20210518 |

|

| C13 | Notice of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: C13 Effective date: 20210720 |

|

| C23 | Notice of termination of proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C23 Effective date: 20211019 |

|

| C03 | Trial/appeal decision taken |

Free format text: JAPANESE INTERMEDIATE CODE: C03 Effective date: 20211124 |

|

| C30A | Notification sent |

Free format text: JAPANESE INTERMEDIATE CODE: C3012 Effective date: 20211124 |