本発明の知見は、例示として示された添付図面を参照して以下の詳細な記述を考慮することによって容易に理解できる。引き続いて、添付図面を参照しながら、本発明の一形態であるA/D変換器の実施の形態を説明する。可能な場合には、同一の部分には同一の符号を付し、重複する説明を省略する。

図1は、本発明の一形態に係るA/D変換器の回路図である。A/D変換器11は、いわゆるフォールディング積分型のA/D変換である第1のA/D変換動作と、巡回型A/D変換である第2のA/D変換動作を、同一の回路構成を用いて実施する。A/D変換器11は、当該A/D変換器11が有するスイッチの時系列の制御パターンの変更により、第1のA/D変換動作及び第2のA/D変換動作を実現する。

図1に示されるように、A/D変換器11は、ゲインステージ15と、A/D変換回路17と、論理回路19と、D/A変換回路21と、クロック発生器61と、参照電圧発生部70と、を含む。

<ゲインステージ>

ゲインステージ15は、ディジタル値に変換されるアナログ信号である入力値VINを受ける入力15aと、演算値VOPを送出する出力15bと、を含む。また、ゲインステージ15は、シングルエンド型の演算増幅回路23と、第1のキャパシタ25と、第2のキャパシタ27と、第3のキャパシタ29と、を含む。

演算増幅回路23は、第1の入力23aと、出力23bと、第2の入力23cと、を含む。出力23bから送出される信号の位相は、第1の入力23aに与えられた信号の位相に対して反転する。例えば、第1の入力23aは反転入力端子である。第2の入力23cは、非反転入力端子である。例えば、演算増幅回路23の第2の入力23cは、基準電位線LCOMに接続される。従って、第2の入力23cは、基準電位VCOMを受ける。

第1のキャパシタ25、第2のキャパシタ27及び第3のキャパシタ29は、各種の信号値の格納及び演算のための容量である。第3のキャパシタ29の容量C2は、第1のキャパシタ25の容量C1aより大きい。また、第3のキャパシタ29の容量C2は、第2のキャパシタ27の容量C1bより大きい。これら容量C1a及び容量C1bによれば、フォールディング積分型A/D変換である第1のA/D変換動作において入力される入力値VINは、容量比(C1a/C2,C1b/C2)に従って減衰される。従って、フォールディング積分型A/D変換において出力される入力値VINの電圧範囲は、キャパシタの容量比に従って小さくなる。このような構成により、シングルエンド構成の当該A/D変換器11を構成できる。

より詳細には、第3のキャパシタ29の容量C2は、第1のキャパシタ25の容量C1aの2倍である。また、第3のキャパシタ29の容量C2は、第2のキャパシタ27の容量C1bの2倍である。すなわち、C1a=1/2×C2及びC1b=1/2×C2といった関係が成立する。このようなキャパシタを有するA/D変換器11によれば、フォールディング積分型A/D変換において入力される入力値VINは、1/2に減衰される。そして、減衰された入力値VINがサンプリング及び積分される。従って、フォールディング積分型A/D変換において出力されるアナログ信号である演算値VOPの電圧範囲は、キャパシタの容量比に従って1/2となる。これにより、巡回型A/D変換である第2のA/D変換動作において、シングルエンド構成のA/D変換器に適した入力電圧が提供される。

ゲインステージ15は、複数のスイッチ43,47,49,51,53を含む。複数のスイッチ43,47,49,51,53は、第1のキャパシタ25、第2のキャパシタ27及び第3のキャパシタ29を、演算増幅回路23に接続する。なお、図1に示されるスイッチ43,47,49,51,53の配置は一例である。スイッチ43,47,49,51,53は、クロック発生器61において生成される制御信号により制御される。

<A/D変換回路>

A/D変換回路17は、ゲインステージ15の出力15bからの演算値VOPに基づき、第1の変換参照電圧VRCH及び/又は第2の変換参照電圧VRCLに応じてディジタル値Dを生成する。

A/D変換回路17は、例えば2個のコンパレータ17a,17b(比較器)を含む。A/D変換器17は、コンパレータ17a,17bのいずれか一方を用いて1ビットのディジタル値Dを生成する。また、A/D変換器17は、コンパレータ17a,17bの両方を用いて2ビットのディジタル値Dを生成する。

コンパレータ17aは、アナログ信号と第1の変換参照電圧VRCHと比較することにより、比較結果信号であるビット(B1)を生成する。コンパレータ17bは、アナログ信号を第2の変換参照電圧VRCLと比較することにより、比較結果信号であるビット(B0)を生成する。第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLは、後述する参照電圧発生部70から提供される。ディジタル値Dは、A/D変換値を示す。ディジタル値Dは、例えば1ビット(B0)又は2ビット(B0,B1)である。各ビット(B0,B1)は、「1」又は「0」を取り得る。1ビットのディジタル値Dは、(B1)である。2ビットのディジタル値Dは、(B0+B1)である。

なお、コンパレータ17aにおいて、第1の変換参照電圧VRCHが提供される入力は、キャパシタ(不図示)を介して基準電位VCOMに接続されてもよい。この構成によれば、高周波ノイズのためのフィルタリングを行うことが可能になる。

A/D変換回路17が1ビットのディジタル値Dを生成するとき、ビット(B1)の値により1回の積分動作又は一巡回毎のディジタル値Dは、2値(D=0又はD=1)を取り得る。このとき、A/D変換回路17では、コンパレータ17aが動作する。従って、1ビットのディジタル値Dを生成するときに基準として用いられる信号は、第1の変換参照電圧VRCHである。この場合には、コンパレータ17aは、以下のように動作する。

VOP≧VRCHのとき B1=1

VOP<VRCHのとき B1=0

A/D変換回路17が2ビットのディジタル値Dを生成するとき、ビット(B0,B1)の組み合わせにより1回の積分動作又は一巡回毎のディジタル値Dが(D=0,D=1,D=2)を取り得る。この場合、コンパレータ17a,17bは、以下のように動作する。

VOP>VRCHのとき B1=1,B0=1

VRCL<VOP≦VRCHのとき B1=0,B0=1

VOP≦VRCLのとき B1=0,B0=0

<参照電圧発生部>

図2は、図1に示された参照電圧発生部70の構成を示す回路図である。図2に示されるように、参照電圧発生部70は、A/D変換回路17に提供される第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLを生成する。参照電圧発生部70は、基準電圧源33,35,36,37,38と接続される。基準電圧源33は参照電圧発生部70に第1の基準参照電圧VRHを提供する。基準電圧源35は参照電圧発生部70に第2の基準参照電圧VRLを提供する。基準電圧源36は参照電圧発生部70に電圧(VC+ΔVT)を提供する。基準電圧源37は参照電圧発生部70に電圧(VC)を提供する。基準電圧源38は参照電圧発生部70に電圧(VC−ΔVT)を提供する。また、参照電圧発生部70は、ゲインステージ15の出力15bと接続される。ゲインステージ15の出力15bは参照電圧発生部70に演算値VOPを提供する。さらに、参照電圧発生部70は、コンパレータ17aに第1の変換参照電圧VRCHを提供する。参照電圧発生部70は、コンパレータ17bに第2の変換参照電圧VRCLを提供する。

参照電圧発生部70は、第1の論理回路71と、第2の論理回路72と、第1の参照電圧発生回路73と、第2の参照電圧発生回路74と、スイッチ75,76と、を含む。第1の参照電圧発生回路73は、第1の論理回路71から提供される制御信号φHL,φML,φLLに基づいて、第1の変換参照電圧VRCHを生成する。第2の参照電圧発生回路74は、制御信号SI,SAに基づいて、第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLを生成する。スイッチ75,76は、第2の論理回路72から提供される制御信号φCH1,φCH2に基づいて、第1の参照電圧発生回路73と第2の参照電圧発生回路74とを選択的にコンパレータ17aに接続する。従って、第1の参照電圧発生回路73で生成された第1の変換参照電圧VRCH及び第2の参照電圧発生回路74で生成された第1の変換参照電圧VRCHの一方がコンパレータ17aに提供される。

第1の論理回路71は、ゲインステージ15の出力15bと、基準電圧源37と、に接続される。第1の論理回路71は、基準電圧源37から提供された電圧(VC)に対する演算値VOPの大小関係を取得し、制御信号φHL,φML,φLLを生成する。第1の論理回路71は、以下のように動作する。

n=1,2であるとき、φHL=0,φML=1,φLL=0

n≧3であるとき、

VOP≧VC(n≧3):φHL=0,φML=0,φLL=1

VOP<VC(n≧3):φHL=1,φML=0,φLL=0

なお、制御信号φMLは、第1の論理回路71とは別の論理回路において生成されてもよい。すなわち、制御信号φMLは、演算値VOPに基づくことなく生成されてもよい。

ここで、nはゲインステージ15におけるフォールディング積分動作の数を示す。例えば、n=2とは、ゲインステージ15における2回目のフォールディング積分動作であることを示す。上記の動作によれば、1回目及び2回目のフォールディング積分動作であるとき、制御信号(φHL=0,φML=1,φLL=0)により、スイッチ73bは導通とされ、スイッチ73a,73cは非導通とされる。また、3回目以降のフォールディング積分動作であって、2回目のフォールディング積分動作の結果がVC≧VOPであるとき、制御信号(φHL=0,φML=0,φLL=1)により、スイッチ73aが導通とされ、スイッチ73b,73cが非導通とされる。一方、3回目以降のフォールディング積分動作であって、2回目のフォールディング積分動作の結果がVC<VOPであるとき、制御信号(φHL=1,φML=0,φLL=0)により、スイッチ73cは導通とされ、スイッチ73a,73bは非導通とされる。

なお、第1の論理回路71における比較動作は、コンパレータ17aの出力を利用して行われてもよい。この場合には、参照電圧発生部70は、A/D変換回路17と接続される。

第2の論理回路72は、制御信号φCH1,φCH2を生成する。制御信号φCH1は、スイッチ75の開閉動作を制御する。制御信号φCH2は、スイッチ76の開閉動作を制御する。第2の論理回路72は、以下のように動作する。

第1のA/D変換動作であるとき:φCH1=1,φCH2=0

第2のA/D変換動作であるとき:φCH1=0,φCH2=1

第1の参照電圧発生回路73は、第1のA/D変換動作のための第1の変換参照電圧V

RCHを生成する。第1の参照電圧発生回路73には、電圧(V

C,V

C+ΔV

T,V

C−ΔV

T)が提供される。第1の参照電圧発生回路73は、スイッチ73a,73b,73cを含む。スイッチ73aは、制御信号φ

LLにより開閉動作が制御される。スイッチ73bは、制御信号φ

MLにより開閉動作が制御される。スイッチ73cは、制御信号φ

HLにより開閉動作が制御される。第1の参照電圧発生回路73は、制御信号φ

HL,φ

ML,φ

LLに基づき、第1の変換参照電圧V

RCHとして、電圧(V

C,V

C+ΔV

T,V

C−ΔV

T)のうちいずれか一つを選択的に出力する。それぞれの電圧(V

C)及び電圧(ΔV

T)は、下記式(1A),(1B),(1C)により示される。

ここで、式(1B)におけるdは、演算値V

OPと演算値V

OPの上限値との間の余裕、及び、演算値V

OPと演算値V

OPの下限値との間の余裕を設定する値であり、0<d<1の範囲における所定の数値に設定される。例えば、d=0.25とされる。

図3は、図2に示された第2の参照電圧発生回路74の構成を示す回路図である。図3に示されるように、第2の参照電圧発生回路74は、第2のA/D変換動作のための第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLを生成する。第2の参照電圧発生回路74は、第1の基準参照電圧VRH及び第2の基準参照電圧VRLに基づき、第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLを生成する。第1の基準参照電圧VRH及び第2の基準参照電圧VRLは、基準電圧源33,35から提供される。第2の参照電圧発生回路74は、第1の基準参照電圧VRH及び第2の基準参照電圧VRLに基づき、所定の抵抗値を有する抵抗R1〜R5に応じて、電圧(VRC1H,VRC2H,VRC2L,VRC1L)を生成する。第2のA/D変換動作では、制御信号SAによって制御されるスイッチの動作により、第1の変換参照電圧VRCHとして電圧(VRC2H)が提供され、第2の変換参照電圧VRCLとして電圧(VRC2L)が提供される。

この第2の参照電圧発生回路74によれば、第1の変換参照電圧VRCHは、第1の基準参照電圧VRHと第2の基準参照電圧VRLとの間の中央値より高く且つ第1の基準参照電圧VRHより低い。また、第2の変換参照電圧VRCLは、第1の基準参照電圧VRHと第2の基準参照電圧VRLとの間の中央値より低く且つ第2の基準参照電圧VRLより高い。このように第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLが生成されるので、第1のA/D変換動作及び第2のA/D変換動作が適切に実施される。

例えば、抵抗R1,R2,R3,R4,R5の抵抗値を、抵抗R1=2R、抵抗R2=R、抵抗R3=2R、抵抗R4=R、抵抗R5=2R(Rは所定の抵抗値)といった値に設定することにより、第2のA/D変換動作における第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLとして、以下の式により表される電圧(VRC2H,VRC2L)が提供される。

VRC2H=(5VRH+3VRL)/8

VRC2L=(3VRH+5VRL)/8

このように第1の変換参照電圧VRCH及び第2の変換参照電圧VRCLが生成されるので、より適切に第2のA/D変換動作が実施される。

再び図1に示されるように、論理回路19は、ディジタル値Dに応じた制御信号VCONT(例えばφDH、φDL、φDS)を生成する。

D/A変換回路21は、第1の出力21aと、第2の出力21bとを含む。D/A変換回路21は、第1の基準参照電圧VRH及び第2の基準参照電圧VRLの少なくともいずれか一方を、制御信号VCONTに応じて第1の出力21a及び第2の出力21bを介してゲインステージ15に提供する。第1の基準参照電圧VRH及び第2の基準参照電圧VRLは、基準電圧源33,35から提供される。

D/A変換回路21は、制御信号に応じて動作するスイッチ回路31を含む。スイッチ回路31は、第1の基準参照電圧VRH及び第2の基準参照電圧VRLのいずれかを、D/A変換回路21が第1の出力21aに提供するように動作する。スイッチ回路31は、第1の基準参照電圧VRH及び第2の基準参照電圧VRLのいずれかを、D/A変換回路21が第2の出力21bに提供するように動作する。

スイッチ回路31は、スイッチ31a,31b,31cを含む。スイッチ回路31は、スイッチ31a,31bを動作させることにより、第1の基準参照電圧VRHを第1の出力21aに提供すると共に、第2の基準参照電圧VRLを第2の出力21bに提供する。また、スイッチ回路31は、スイッチ31a,31cを動作させることにより、第1の基準参照電圧VRHを第1の出力21a及び第2の21bに提供する。さらに、スイッチ回路31は、スイッチ31b,31cを動作させることにより、第2の基準参照電圧VRLを第1の出力21a及び第2の21bに提供する。

D/A変換回路21の第1の出力21aは、第1のキャパシタ25の一端に接続される。D/A変換回路21の第2の出力21bは、第2のキャパシタ27の一端に接続される。スイッチ31a,31b,31cの開閉は、それぞれ、論理回路19からの制御信号φDH,φDS,φDLによって制御される。従って、ディジタル値Dは、動作させるべき制御信号φDH,φDS,φDLを決定する。

ここで、第1の出力21aに提供される電圧をVDA1とし、第2の出力21bに提供される電圧をVDA2とする。そして、A/D変換回路17が1つのコンパレータ17aを用いてディジタル値Dを生成する場合には、D/A変換回路21は、A/D変換回路17からのディジタル値Dに基づく制御信号VCONTに応じて、以下のように動作する。

条件(D=1)が満たされるとき:VDA1=VRH、VDA2=VRL

条件(D=0)が満たされるとき:VDA1=VDA2=VRL

一方、A/D変換回路17が2つのコンパレータ17a,17bを用いてディジタル値Dを生成する場合には、D/A変換回路21は、A/D変換回路17からのディジタル値Dに基づく制御信号VCONTに応じて、以下のように動作する。

条件(D=2)が満たされるとき:VDA1=VDA2=VRH

条件(D=1)が満たされるとき:VDA1=VRH、VDA2=VRL

条件(D=0)が満たされるとき:VDA1=VDA2=VRL

本発明の別の側面は、イメージセンサデバイスである。図4は、イメージセンサの画素を示す図面である。イメージセンサデバイスは、セルアレイと、変換器アレイとを備える。セルアレイは、二次元状に配置された複数のイメージセンサセル2aを含む。変換器アレイは、セルアレイに接続されており複数のA/D変換器11を含む。A/D変換器11は、セルアレイのカラム線8を介してイメージセンサセル2aに接続される。

イメージセンサセル2aは、例えばCMOSイメージセンサセルである。フォトダイオードDFは、イメージに関連する一画素分の光Lを受ける。選択トランジスタMSのゲートは、行方向に伸びるロウ選択線Sに接続される。リセットトランジスタMRのゲートはリセット線Rに接続される。転送トランジスタMTのゲートは、行方向に伸びる転送選択線に接続される。フォトダイオードDFの一端は転送トランジスタMTを介して浮遊拡散層FDに接続される。浮遊拡散層FDは、リセットトランジスタMRを介してリセット電位線Resetに接続されると共に、トランジスタMAのゲートに接続される。トランジスタMAの一電流端子(例えばドレイン)は、選択トランジスタMSを介してカラム線8に接続される。トランジスタMAは、浮遊拡散層FDの電荷量に応じて電位を選択トランジスタMSを介してカラム線に提供する。

この構造のイメージセンサセル2aは、リセットレベルを示す第1の信号と該リセットレベルに重畳された信号レベルを示す第2の信号とを生成する。すなわち、イメージセンサセル2aでは、まず、リセット線Rに提供される制御信号がリセットトランジスタMRに提供され、浮遊拡散層FDがリセットされる。トランジスタMAを介して、このリセットレベルが読み出される。次に、電荷転送制御信号TXが転送トランジスタMTに提供され、フォトダイオードDFから光誘起信号電荷が浮遊拡散層に転送される。そして、トランジスタMAを介して、この信号レベルが読み出される。このように、イメージセンサセル2aは、リセットレベルを示す第1の信号S1と該リセットレベルに重畳された信号レベルを示す第2の信号S2とを生成可能である。

<フォールディング積分型A/D変換動作>

次に、図1に示されたA/D変換器11における第1のA/D変換動作を説明する。第1のA/D変換動作は、入力信号の標本化及び標本値の積分を繰り返し行うことによりアナログ値である入力値VINからディジタル値Dである出力値を得るためのフォールディング積分型の動作である。

図5の(a)部、(b)部、(c)部及び(d)部は、第1のA/D変換動作を説明するための回路図である。第1のA/D変換動作では、前述したように、A/D変換回路17が1つのコンパレータ17aを用いてディジタル値Dを生成する。

図5の(a)部に示されるように、ゲインステージ15は、第1の初期格納ステップとしての第1の格納動作を行う。このステップでは、ゲインステージ15の入力15aを介して受けた入力値VINを第1のキャパシタ25に格納する。また、ゲインステージ15の出力23bと第1の入力23aとを接続する。そして、第2のキャパシタ27は、第2の出力21bから提供される第2の基準参照電圧VRLを格納する。さらに、第3のキャパシタ29は、演算増幅回路23の出力23bと第1の入力23aとの間に接続される。

第1の初期格納ステップ及び以下に説明する各ステップにおける格納及び接続は、スイッチ回路31及びスイッチ43,47,49,51,53により実現される。第1の初期格納ステップでは、制御信号(φDH=0,φDS=0,φDL=1)及び制御信号(φ1=1,φ2=0,φ3=0,φR=1,φS=1)により、スイッチ31b,47,53,43は導通とされ、スイッチ31a,31c,49,51は非導通とされる。

このとき、容量C

1a,C

1bに蓄積される電荷(Q

1a,Q

1b)は、下記式(2A),(2B)により示される。

第1の初期格納動作ステップに引き続き、A/D変換器11は、図5の(b)部又は図5の(c)部に示される、第1の演算ステップとしての第1の演算動作を行う。

第1の演算ステップでは、制御信号(φ1=0,φ2=1,φ3=0,φR=0,φS=0)により、スイッチ49は導通とされ、スイッチ47,51,53,43は非導通とされる。この回路構成によれば、第1のキャパシタ25が第1の出力21aと第1の入力23aとの間に接続され、第2のキャパシタ27が第2の出力21bと第1の入力23aとの間に接続され、第3のキャパシタ29が演算増幅回路23の出力23bと第1の入力23aとの間に接続される。

D/A変換回路21の第1の出力21a及び第2の出力21bには、コンパレータ17aからのディジタル値D(n)(=B1)に従ったスイッチ回路31の制御により、第1の基準参照電圧VRH又は第2の基準参照電圧VRLが提供される。

1回目及び2回目の第1の演算動作が行われるとき、参照電圧発生部70は、第1の変換参照電圧VRCHとして第1の閾値をA/D変換回路17に提供する。この場合、参照電圧発生部70では、制御信号(φHL=0,φML=1,φLL=0,φCH1=1,φCH2=0)により、スイッチ73b,75は導通とされ、スイッチ73a,73c,76は非導通とされる。

ここで、参照電圧発生部70は、2回目の第1の演算動作の結果を利用して、制御値Eである第1の制御値または第2の制御値を生成する。制御値Eは、3回目以降の第1の演算動作に利用される閾値である第1の変換参照電圧VRCHを生成するための値である。この動作は、参照電圧発生部70の第1の論理回路71において行われる。第1の論理回路71は、以下のように動作する。VOP(2)は、2回目の第1の演算動作により生成された演算値である。

条件(VOP(2)≧VC)が満たされるとき、E=1

条件(VOP(2)<VC)が満たされるとき、E=0

具体的には、演算値VOP(2)が第1の閾値(VC)以上であるとき、制御値Eは第1の制御値(E=1)である。一方、演算値VOP(2)が第1の閾値(VC)未満であるとき、制御値Eは第2の制御値(E=0)である。なお、この制御値は、2回目の第1の演算動作の結果(演算値VOP(2))に基づくコンパレータ17aのディジタル出力(D(2)=0又は1)を利用してもよい。

1回目及び2回目の第1の演算動作が行われるとき、A/D変換回路17のコンパレータ17aは、式(3)に示されるように動作する。式(3)において、D(n)=(B

1)はn回目の演算動作おけるディジタル値Dが(B

1)であることを示す。nはゲインステージ15におけるフォールディング積分動作の数を示す。例えば、D(1)=1は1回目のフォールディング演算動作におけるディジタル値Dが「1」であることを示す。

3回目以降の第1の演算動作が行われるとき、参照電圧発生部70及びA/D変換回路17のコンパレータ17aは、式(4)に示されるように動作する。ただし、3≦n<Mである。Mは、最大繰り返し数(積分の回数)である。

式(4)によれば、参照電圧発生部70は、第1の変換参照電圧VRCHとして電圧[VC−d×ΔVR×(2×E−1)]をA/D変換回路17に提供する。そして、A/D変換回路17は、演算値VOP(n)(3≦n<M)に基づき、第1の変換参照電圧VRCHを参照して、ディジタル値Dを生成する。

式(4)において、[VC−d×ΔVR×(2×E−1)]は、コンパレータ17aに提供される第2の閾値又は第3の閾値である。制御値Eは、第2の閾値又は第3の閾値を決定する。第2の閾値又は第3の閾値を示す数式[VC−d×ΔVR×(2×E−1)]を参照すると、制御値Eが含まれている。制御値Eは、2回目の第1の演算動作の結果に基づいて生成される値である。すなわち、3回目以降の演算動作においては、2回目の演算動作で得られた結果(制御値E)を用いて閾値(第1の変換参照電圧VRCH)を決定している。既に述べたように、式(4)におけるdは、演算値VOPと演算値VOPの上限値との間の余裕、及び、演算値VOPと演算値VOPの下限値との間の余裕を設定する値であり、0<d<1の範囲における所定の数値に設定される。例えば、d=0.25とされる。

例えば、第1の制御値(E=1)であるとき、第1の制御値(E=1)を式(4)に代入すると、式(5)に示される第2の閾値(V

C−d×ΔV

R)が得られる。第2の閾値は、第1の閾値V

Cより[d×ΔV

R]だけ小さい。この場合、参照電圧発生部70では、制御信号(φ

HL=0,φ

ML=0,φ

LL=1,φ

CH1=1,φ

CH2=0)により、スイッチ73a,75が導通とされ、スイッチ73b,73c,76が非導通とされる。

一方、第2の制御値(E=0)であるとき、第2の制御値(E=0)を式(4)に代入すると、式(6)に示される第3の閾値(V

C+d×ΔV

R)が得られる。第3の閾値は、第1の閾値V

Cより[d×ΔV

R]だけ大きい。この場合、参照電圧発生部70では、制御信号(φ

HL=1,φ

ML=0,φ

LL=0,φ

CH1=1,φ

CH2=0)により、スイッチ73c,75が導通とされ、スイッチ73a,73b,76が非導通とされる。

要するに、1回目及び2回目の演算動作では、第1の変換参照電圧VRCHとして電圧(VC)がコンパレータ17aに提供される。そして、2回目の演算動作の結果に基づいて第1の制御値(E=1)が生成された場合には、第1の変換参照電圧VRCHとして電圧(VC−d×ΔVR)がコンパレータ17aに提供される。一方、2回目の演算動作の結果に基づいて、第2の制御値(E=2)が生成された場合には、第1の変換参照電圧VRCHとして電圧(VC+d×ΔVR)がコンパレータ17aに提供される。

続いて、ゲインステージ15は、図5(d)に示される第1の格納動作を第1の格納ステップとして行う。第1の格納ステップでは、第3のキャパシタ29を演算増幅回路23の出力23bと第1の入力23aとの間に接続することで演算値VOPを容量C2に保持したままで、ゲインステージ15の入力15aからの入力値VINを第1のキャパシタ25に格納し、第2の出力21bから提供される第2の基準参照電圧VRLを第2のキャパシタ27に格納する。第1の格納ステップでは、制御信号(φDH=0,φDS=0、φDL=1)及び制御信号(φ1=1,φ2=0,φ3=0,φR=0,φS=1)により、スイッチ31b,47,43は導通とされ、スイッチ31a,31c,49,51,53は非導通とされる。

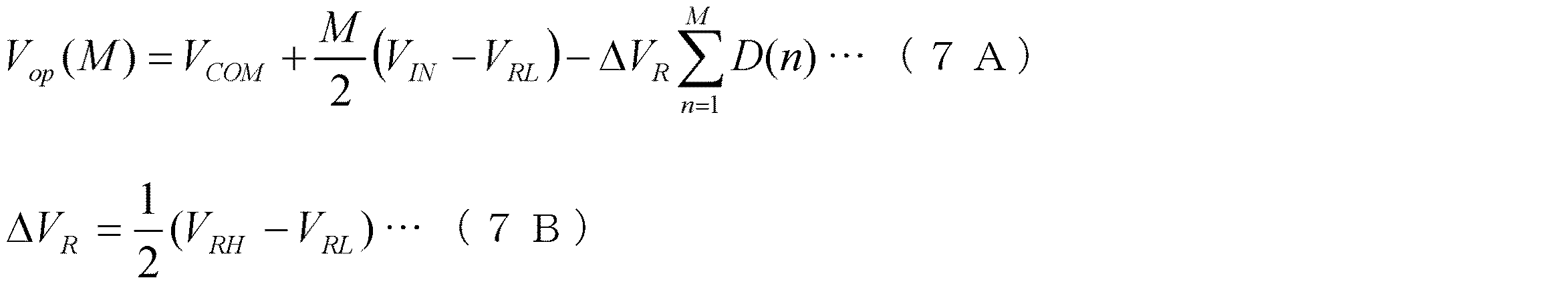

次いで、ゲインステージ15は、ディジタル値D(n−1)に基づき、図5の(b)部及び図5の(c)部に示される第1の演算動作のいずれかを選択しながら、n回目の第1の演算ステップ及び第1の格納ステップを行うフォールディング積分型A/D変換ステップを所定回数繰り返して実施する。フォールディング積分型A/D変換ステップにおいて、第1の演算ステップ及び第1の格納ステップをM回繰り返して、サンプリング及び積分を行ったときの演算値V

OPは、式(7A),(7B)により示される。式(7A)において、ディジタル値D(n)は、上記式(5)又は式(6)により示される。

式(7A)の右辺第2項に示されるように、入力信号である入力値VINに1/2のゲインをかけて、M回のサンプリングを行い、フォールディング積分型のA/D変換を行うと、その出力(演算値VOP)の振幅範囲は、入力信号の振幅範囲と同じになる。

<巡回型A/D変換動作>

次に、図1に示されたA/D変換器11における第2のA/D変換動作を説明する。第2のA/D変換動作は、巡回型A/D変換動作である。以下、A/D変換器11における、巡回型A/D変換ステップとしての巡回型A/D変換の動作を説明する。

図6の(a)部、(b)部及び(c)部は、第2のA/D変換動作を説明するための回路図である。第2のA/D変換動作では、A/D変換回路17が2つのコンパレータ17a,17bを用いてディジタル値Dを生成する。

まず、ゲインステージ15は、図6の(a)部に示されるように、第2の初期格納ステップとしての第2の格納動作を実施する。このステップでは、フォールディング積分型A/D変換ステップにおける演算値VOPである残差アナログ信号を第1のキャパシタ25、第2のキャパシタ27及び第3のキャパシタ29に格納する。このステップでは、制御信号(φDH=0,φDS=1、φDL=0)及び制御信号(φ1=1,φ2=0,φ3=1,φR=0,φS=0)により、スイッチ31c,47,51は導通とされ、スイッチ31a,31b,43,49,53は非導通とされる。また、このステップでは、フォールディング積分型A/D変換ステップにおける演算値VOPがコンパレータ17a,17bに提供される。コンパレータ17a,17bは、提供された演算値VOPに基づき、ディジタル値Dを生成する。

続いて、ゲインステージ15は、第2の初期格納ステップに引き続き、ディジタル値D(=B1+B0)の値に従って、図6の(b)部又は図6の(c)部に示されるように、第2の演算ステップとしての第2の演算動作を行う。第2の演算動作では、ゲインステージ15は、演算増幅回路23、第1のキャパシタ25、第2のキャパシタ27及び第3のキャパシタ29により演算値VOPを生成する。第2の演算動作では、第3のキャパシタ29が演算増幅回路23の出力23bと第1の入力23aとの間に接続されると共に、第1のキャパシタ25が第1の出力21aと第1の入力23aとの間に接続され、第2のキャパシタ27が第2の出力21bと第1の入力23aとの間に接続される。第2の演算ステップでは、制御信号(φ1=0,φ2=1,φ3=0,φR=0,φS=0)により、スイッチ49は導通とされ、スイッチ47,51,53,43は非導通とされる。

D/A変換回路21の第1の出力21a及び第2の出力21bには、コンパレータ17a,17bからのディジタル値D(=B1+B0)に従ってスイッチ回路31が制御され、第1の基準参照電圧VRH又は第2の基準参照電圧VRLが提供される。

コンパレータ17a,17bは、以下のように動作する。

VOP>VRCHのとき D=2(B1=1,B0=1)

VRCL<VOP≦VRCHのとき D=1(B1=0,B0=1)

VOP≦VRCLのとき D=0(B1=0,B0=0)

D=2のときには、D/A変換回路21の第1の出力21a及び第2の出力21bから第1の基準参照電圧VRHが提供されるように制御されながら図6の(b)部の動作が行われる。一方、D=0のときには、D/A変換回路21の第1の出力21a及び第2の出力21bから第2の基準参照電圧VRLが提供されるように制御されながら図6の(b)部の動作が行われる。さらに、D=1のときには、D/A変換回路21の第1の出力21a及び第2の出力21bからそれぞれ第1の基準参照電圧VRH及び第2の基準参照電圧VRLが提供されるように制御されながら図6の(c)部の動作が行われる。

続いて、ゲインステージ15は、第2の演算ステップに引き続き、図6の(a)部に示されるように、第2の格納ステップとしての第2の格納動作を行う。

第2の格納ステップでは、第2の演算ステップにおける演算値VOPを第1のキャパシタ25、第2のキャパシタ27及び第3のキャパシタ29に格納する点において、第2の初期格納ステップと相違する。

そして、ゲインステージ15は、巡回型A/D変換ステップとして、第2の演算ステップ及び第2の格納ステップを所定回数繰り返して行う。M回の積分動作後の演算値V

OP(M)の残差に対するj回目の巡回動作後に得られるディジタル値をD(j)で表すと、残差V

OP(M)−V

COMとディジタル値D(j)の関係は式(8)により示される。

式(7A)のD(M)と、式(8)のD(1)〜D(N)より、アナログ値である入力値からディジタル値である出力値が得られる。

以下、本実施形態に係るA/D変換器11の作用効果について説明する。

このA/D変換器11では、ゲインステージ15の出力15bから送出される演算値VOPに基づいて第1の変換参照電圧VRCHを生成する。そして、第1の変換参照電圧VRCHを参照して、ゲインステージ15からの演算値VOPがディジタル値Dに変換される。これにより、第1の変換参照電圧VRCHは、唯一の値ではなく可変値であるので、積分動作の繰り返しによってもゲインステージ15の出力15bから送出される演算値VOPが所望の範囲を超えないようにすることが可能になる。従って、このA/D変換器11は、積分演算の結果を所望の範囲に収めることができる。

このゲインステージ15では、第3のキャパシタ29の容量C2が、第1のキャパシタ25の容量C1a及び第2のキャパシタ27の容量C1bに対して2倍である。換言すると、第1のキャパシタ25及び第2のキャパシタ27と、第3のキャパシタ29との容量比が1/2である。従って、演算増幅回路23における電圧の出力範囲は、入力範囲の1/2になる。このため、このゲインステージ15によれば、1回目の積分動作によって入力信号の大きさが1/2となる。次に、2回目の積分動作では1回目の積分動作の結果と、1/2とされる演算増幅回路23の演算値VOPとが足し合される。従って、2回目の積分動作の出力の大きさは、入力値VINの大きさに対応する。これにより、第1の変換参照電圧VRCHの生成において、2回目の積分動作の出力を参照することは、入力を参照することと同じ意味である。従って、ゲインステージ15の演算値VOPを利用して、積分演算の結果を所望の範囲に収めることが可能な第1の変換参照電圧VRCHを生成することができる。

図7及び図8を参照しつつ、参照電圧発生部70の作用につきさらに説明する。図7及び図8は、ゲインステージ15のフォールディング積分型A/D変換器としての動作時における入出力特性を概略的に示す図である。参照電圧発生部70は、2回目の積分動作で得られたゲインステージ15の出力に基づいて、第1の制御値又は第2の制御値を生成する。そして、参照電圧発生部70は、3回目の積分動作で得られたゲインステージ15の出力をA/D変換するための第1の変換参照電圧VRCHを、第2の閾値(VC−ΔVT)又は第3の閾値(VC+ΔVT)に基づいて生成する。そして、第1の閾値(VC)及び第1の制御値に基づいて生成された第2の閾値(VC−ΔVT)は、第1の閾値(VC)より小さい。一方、第1の閾値(VC)及び第2の制御値に基づいて生成された第3の閾値(VC+ΔVT)は、第1の閾値(VC)より大きい。その結果、ゲインステージ15の出力が大きい場合には閾値が小さくなり、ゲインステージ15の出力が小さい場合には閾値が大きくなる。

ここで、閾値は、ゲインステージ15の出力を所定の範囲に収めるために、演算値VOPから所定の値(ΔVR)を減じる動作(いわゆる折り返し動作)を行うか否かを判断するための値である。そうすると、第2の閾値が第1の閾値(VC)より小さい場合(VC−ΔVT)には、ゲインステージ15の出力が小さい段階で折り返し動作が実行されることになる(図7参照)。従って、ゲインステージ15の出力から上限値(Vmax)までの間の余裕をΔVm1からΔVm2へ拡大させることが可能になる。また、第3の閾値が第1の閾値(VC)より大きい場合(VC+ΔVT)には、ゲインステージ15の出力が大きい段階で折り返し動作が実行されることになる(図8参照)。従って、ゲインステージ15の出力から下限値(Vmin)までの間の余裕をΔVm3からΔVm4へ拡大させることが可能になる。

このA/D変換器11では、コンパレータ17aの比較動作における誤差耐性を高めることが可能になる。従って、精密な参照電圧を提供するために高精度の電源を用いる必要がなくなる。

また、第1の閾値(VC)は、第1の基準参照電圧VRHと、第2の基準参照電圧VRLとの中間値である(式(1A)参照)。この構成によれば、ゲインステージ15に入力される入力値VINの許容範囲において、第1の閾値(VC)よりも小さい第2の閾値(VC−ΔVT)を用いてA/D変換される範囲と、第1の閾値(VC)よりも大きい第2の閾値(VC+ΔVT)を用いてA/D変換される範囲と、の境界を、当該許容範囲の中間に設定することができる。

<比較例1>

図9の(a)部〜(d)部は、シミュレーションにより求めたゲインステージのフォールディング積分型A/D変換器としての動作時における入出力特性を示す図面である。縦軸は、A/D変換前の入力値VIN(アナログ値)であり、横軸は、入力値VINをA/D変換後の値(14ビットディジタル値)である。すなわち、横軸は、入力値VIN(ディジタル値)であり、14ビットでA/D変換した結果出力されると期待されるディジタル値に換算して示している。図9の(a)部〜(d)部に示される入出力特性は、比較例に係る参照電圧発生部から提供される基準参照電圧に基づいている。比較例に係る参照電圧発生部は、基準参照電圧を生成するための閾値が一定値(第1の閾値(VC))として動作する。また、シミュレーションのための条件として、(VC=0.5V、VRH=1.0V、VRL=0V、VCOM=0V)が設定された。

図9の(a)部及び図9の(b)部は、積分回数(M=16)とした場合のシミュレーション結果である。また、図9の(a)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図9の(b)部は、実際のフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含む。図9の(a)部に示された入出力特性によれば、上限値(又は下限値)までの余裕(ΔVm)は、0.036Vであることがわかった。従って、図9の(b)部に示されるように、電圧バイアス等の誤差に対して0.036Vの余裕があることがわかった。

図9の(c)部及び図9の(d)部は、積分回数(M=64)とした場合のシミュレーション結果である。また、図9の(c)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図9の(d)部は、実際のフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含む。図9の(c)部に示された入出力特性によれば、上限値(又は下限値)までの余裕(ΔVm)は、0.0077Vであることがわかった。従って、図9の(d)部に示されるように、電圧バイアス等の誤差に対して0.0077Vの余裕があることがわかった。

<実施例1>

図10の(a)部〜(d)部は、シミュレーションにより求めたゲインステージ15のフォールディング積分型A/D変換器としての動作時における入出力特性を示す図面である。縦軸は、A/D変換前の入力値VIN(アナログ値)であり、横軸は、入力値VINをA/D変換後の値(14ビットディジタル値)である。図10の(a)部〜(d)部に示される入出力特性は、参照電圧発生部70から提供される基準参照電圧に基づいている。また、シミュレーションのための条件として、(VC=0.5V、ΔVT=0.125V、VRH=1.0V、VRL=0V、VCOM=0V)が設定された。

図10の(a)部及び図10の(b)部は、積分回数(M=16)とした場合のシミュレーション結果である。また、図10の(a)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図10の(b)部は、実際のフォールディング積分型A/D変換回路として、コンパレータ17aの電圧バイアス等の誤差要因を含む。図10の(a)部に示された入出力特性によれば、上限値(又は下限値)までの余裕(ΔVm)は、0.125Vであることがわかった。従って、図10の(b)部に示されるように、電圧バイアス等の誤差に対して0.125Vの余裕があることがわかった。また、比較例の余裕(0.036V)と比較すると、誤差耐性は3倍程度(0.125/0.036)向上することがわかった。

図10の(c)部及び図10の(d)部は、積分回数(M=64)とした場合のシミュレーション結果である。また、図10の(c)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図10の(d)部は、実際のフォールディング積分型A/D変換回路として、コンパレータ17aの電圧バイアス等の誤差要因を含む。図10の(c)部に示された入出力特性によれば、上限値(又は下限値)までの余裕(ΔVm)は、0.125Vであることがわかった。従って、図10の(d)部に示されるように、電圧バイアス等の誤差に対して0.125Vの余裕があることがわかった。また、比較例の余裕(0.0077V)と比較すると、誤差耐性は16倍程度(0.125/0.0077)向上することがわかった。

<実施例2>

図11の(a)部〜(d)部は、シミュレーションにより求めたゲインステージ15のフォールディング積分型A/D変換器としての動作時における入出力特性を示す図面である。縦軸は、A/D変換前の入力値VIN(アナログ値)であり、横軸は、入力値VINをA/D変換後の値(14ビットディジタル値)である。図11の(a)部〜(d)部に示される入出力特性は、参照電圧発生部70から提供される基準参照電圧に基づいている。また、シミュレーションのための条件として、(VC=0.375V、ΔVT=0.125V、VRH=1.0V、VRL=0V、VCOM=0V)が設定された。

さらに、実施例2では、2回目の演算値VOPをディジタル値Dに変換するための第1の閾値として、第1の閾値(VC+ΔVR/4)を設定した。ΔVRは、上記式(1C)に示される。即ち、第1の閾値は、第1の基準参照電圧VRHと、第2の基準参照電圧VRLとの中間値(VC)よりも小さく、第2の基準参照電圧よりも大きい。

図11の(a)部及び図11の(b)部は、積分回数(M=16)とした場合のシミュレーション結果である。また、図11の(a)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図11の(b)部は、実際のフォールディング積分型A/D変換回路として、コンパレータ17aの電圧バイアス等の誤差要因を含む。図11の(a)部に示された入出力特性によれば、下限値までの余裕(ΔVm)は、0.09Vであることがわかった。従って、図11の(b)部に示されるように、電圧バイアス等の誤差に対して0.09Vの余裕があることがわかった。また、比較例の余裕(0.036V)と比較すると、誤差耐性は2.5倍程度(0.09/0.036)向上することがわかった。

図11の(c)部及び図11の(d)部は、積分回数(M=64)とした場合のシミュレーション結果である。また、図11の(c)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図11の(d)部は、実際のフォールディング積分型A/D変換回路として、コンパレータ17aの電圧バイアス等の誤差要因を含む。図11の(c)部に示された入出力特性によれば、下限値までの余裕(ΔVm)は、0.072Vであることがわかった。従って、図11の(d)部に示されるように、電圧バイアス等の誤差に対して0.072Vの余裕があることがわかった。また、比較例の余裕(0.0077V)と比較すると、誤差耐性は10倍程度(0.072/0.0077)向上することがわかった。

実施例2のように、閾値(VC+ΔVR/4)とする設定によれば、入力の大きさが小さい領域(換言すると暗い領域)における余裕を拡大することができる。即ち、この構成によれば、入力の許容範囲における中間値を境界点として、第1の閾値よりも小さい第2の閾値を用いてA/D変換される範囲と、第1の閾値よりも大きい第2の閾値を用いてA/D変換される範囲と、の境界を、入力の許容範囲における下限寄りに設定することができる。

<実施例3>

図12の(a)部〜(d)部は、シミュレーションにより求めたゲインステージ15のフォールディング積分型A/D変換器としての動作時における入出力特性を示す図面である。縦軸は、A/D変換前の入力値VIN(アナログ値)であり、横軸は、入力値VINをA/D変換後の値(14ビットディジタル値)である。図12の(a)部〜(d)部に示される入出力特性は、参照電圧発生部70から提供される基準参照電圧に基づいている。また、シミュレーションのための条件として、(VC=0.625V、ΔVT=0.125V、VRH=1.0V、VRL=0V、VCOM=0V)が設定された。

さらに、実施例3では、2回目の演算値VOPをディジタル値Dに変換するための第1の閾値として、第1の閾値(VC−ΔVR/4)を設定した。ΔVRは、上記式(1C)に示される。第1の閾値は、第1の基準参照電圧VRHと、第2の基準参照電圧VRLとの中間値(VC)よりも大きく、第1の基準参照電圧VRHよりも小さい。

図12の(a)部及び図12の(b)部は、積分回数(M=16)とした場合のシミュレーション結果である。また、図12の(a)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図12の(b)部は、実際のフォールディング積分型A/D変換回路として、コンパレータ17aの電圧バイアス等の誤差要因を含む。図12の(a)部に示された入出力特性によれば、上限値までの余裕(ΔVm)は、0.09Vであることがわかった。従って、図12の(b)部に示されるように、電圧バイアス等の誤差に対して0.09Vの余裕があることがわかった。また、比較例の余裕(0.036V)と比較すると、誤差耐性は2.5倍程度(0.09/0.036)向上することがわかった。

図12の(c)部及び図12の(d)部は、積分回数(M=64)とした場合のシミュレーション結果である。また、図12の(c)部は、理想的なフォールディング積分型A/D変換回路として、コンパレータの電圧バイアス等の誤差要因を含んでいない。一方、図12の(d)部は、実際のフォールディング積分型A/D変換回路として、コンパレータ17aの電圧バイアス等の誤差要因を含む。図12の(c)部に示された入出力特性によれば、上限値までの余裕(ΔVm)は、0.072Vであることがわかった。従って、図12の(d)部に示されるように、電圧バイアス等の誤差に対して0.072Vの余裕があることがわかった。また、比較例の余裕(0.0077V)と比較すると、誤差耐性は10倍程度(0.072/0.0077)向上することがわかった。

実施例3のように、閾値(VC−ΔVR/4)とする設定によれば、入力の大きさが大きい領域(換言すると明るい領域)における余裕を拡大することができる。即ち、この構成によれば、入力の許容範囲における中間値を境界点として、第1の閾値よりも小さい第2の閾値を用いてA/D変換される範囲と、第1の閾値よりも大きい第2の閾値を用いてA/D変換される範囲と、の境界を、入力の許容範囲における上限寄りに設定することができる。

<実施例4>

実施例4では、式(4)における係数dの効果を確認した。図13の(a)部〜(c)部は、シミュレーションにより求めたゲインステージ15のフォールディング積分型A/D変換器としての動作時における入出力特性を示す図面である。縦軸は、A/D変換前の入力値VIN(アナログ値)であり、横軸は、入力値VINをA/D変換後の値(14ビットディジタル値)である。図13の(a)部〜(c)部に示される入出力特性は、参照電圧発生部70から提供される基準参照電圧に基づいている。また、シミュレーションのための条件として、(VC=0.5V、ΔVT=d×0.5V、VRH=1.0V、VRL=0V、VCOM=0V)が設定された。

さらに、実施例4では、式(4)における係数dの値を、d=0、d=0.25、d=0.5のように変化させた。

図13の(a)部は、d=0であるときの入出力特性を示す図面であり、図13の(b)部は、d=0.25であるときの入出力特性を示す図面であり、図13の(c)部は、d=0.5であるときの入出力特性を示す図面である。図13の(a)部、(b)部及び(c)部に示されるように、dの数値を変化させることにより、余裕(ΔVm)の大きさを調整できることがわかった。

以上、本発明をその実施形態に基づいて詳細に説明した。しかし、本発明は上記実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲で様々な変形が可能である。

例えば、上記実施形態では、参照電圧発生部70は、ゲインステージ15の演算値VOPを利用して、変換参照電圧を生成したが、この構成に限定されることはない。参照電圧発生部70は、ゲインステージ15の入力15a提供される入力値VINを利用して、変換参照電圧を生成してもよい。このような構成は、図1に示された回路に対して、スイッチを追加すると共に、入力値VINを閾値と比較するためのコンパレータ(不図示)を追加することにより実現できる。例えば、スイッチ43,51を閉鎖することにより、入力15aと参照電圧発生部70が接続される。そして、スイッチ51と出力15bとの間に演算増幅回路23の出力23bが接続されないように新たなスイッチ(不図示)を設ける。このような構成によっても、上記実施形態と同様の効果を得ることができる。

また、上記実施形態では、2回目の積分動作の演算結果を利用して、3回目以降の変換参照電圧を生成した。すなわち、4回目や5回目の演算に利用される変換参照電圧は、2回目の積分動作の演算結果を利用している。例えば、n回目(nは3以上の整数)の演算に利用される変換参照電圧は、(n−1)回目の積分動作の演算結果を利用して生成されてもよい。例えば、4回目の演算に利用される変換参照電圧は、3回目の積分動作の演算結果を利用して生成されてもよい。

また、第1の閾値(VC+ΔVR/4)又は第1の閾値(VC−ΔVR/4)は、A/D変換回路17が備えるコンパレータのオフセット機能を利用して実現されてもよい。すなわち、コンパレータには電圧VCが提供され、電圧ΔVR/4はコンパレータが有するオフセット機能により提供されてもよい。