JP2017123732A - 半導体素子の駆動回路 - Google Patents

半導体素子の駆動回路 Download PDFInfo

- Publication number

- JP2017123732A JP2017123732A JP2016001772A JP2016001772A JP2017123732A JP 2017123732 A JP2017123732 A JP 2017123732A JP 2016001772 A JP2016001772 A JP 2016001772A JP 2016001772 A JP2016001772 A JP 2016001772A JP 2017123732 A JP2017123732 A JP 2017123732A

- Authority

- JP

- Japan

- Prior art keywords

- gate

- semiconductor element

- circuit

- resistor

- delay circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 137

- 230000003111 delayed effect Effects 0.000 claims abstract description 13

- 239000003990 capacitor Substances 0.000 claims description 22

- 238000010586 diagram Methods 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 238000010248 power generation Methods 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 230000001133 acceleration Effects 0.000 description 3

- 238000007599 discharging Methods 0.000 description 3

- 229910002601 GaN Inorganic materials 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

Images

Landscapes

- Power Conversion In General (AREA)

Abstract

Description

本発明の第1の態様による半導体素子の駆動回路は、前記第2スイッチ素子が、前記遅延回路で遅延された前記指令信号がゲートに入力されるpチャネルMOSFETであり、前記指令信号の論理を反転させて前記遅延回路に出力する反転回路(12)を備える。

また、本発明の第1の態様による半導体素子の駆動回路は、前記遅延回路が、前記反転回路と前記pチャネルMOSFETのゲートとの間に直列接続された抵抗(R1)と、前記pチャネルMOSFETのゲートとソースとの間に接続されたコンデンサ(C1)と、を備える。

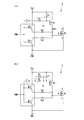

本発明の第2の態様による半導体素子の駆動回路は、前記第2スイッチ素子が、前記遅延回路で遅延された前記指令信号がゲートに入力されるnチャネルMOSFETである。

本発明の第2の態様による半導体素子の駆動回路は、前記遅延回路が、一端が前記nチャネルMOSFETのゲートに接続され、他端に前記指令信号が入力される抵抗(R2)と、一端が前記nチャネルMOSFETのゲートに接続され、他端が接地されたコンデンサ(C2)と、を備える。

また、本発明の半導体素子の駆動回路は、前記第2スイッチ素子と前記制御電極との間に直列接続された第2抵抗部(Rg3、Rg4)を備える。

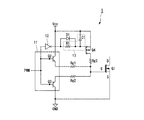

図1は、本発明の第1実施形態による半導体素子の駆動回路の構成を示す回路図である。図1に示す通り、本実施形態の駆動回路1は、増幅部11、ゲート抵抗Rg1(第1抵抗部)、ゲート抵抗Rg2、ゲート抵抗Rg3(第2抵抗部)、スイッチング用MOSFETQ4(第2スイッチ素子)、反転回路12、遅延回路13、及びダイオードD1を備えており、外部から入力されるPWM(Pulse Width Modulation:パルス幅変調)信号に基づいて半導体素子Q1を駆動する回路である。

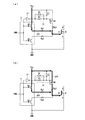

図5は、本発明の第2実施形態による半導体素子の駆動回路の構成を示す回路図である。図5に示す通り、本実施形態の駆動回路2は、図1に示す駆動回路1の反転回路12を省略し、ゲート抵抗Rg3、スイッチング用MOSFETQ4、遅延回路13、及びダイオードD1を、それぞれゲート抵抗Rg4(第2抵抗部)、スイッチング用MOSFETQ5(第2スイッチ素子)、遅延回路23、及びダイオードD3に代えた構成である。

Claims (6)

- 半導体素子の制御電極に一端が接続された第1抵抗部と、半導体素子のオン状態を指令する指令信号に基づいてオン状態になり、電源と前記第1抵抗部の他端とを接続する第1スイッチ素子とを備える半導体素子の駆動回路において、

前記指令信号を予め規定された時間だけ遅延させる遅延回路と、

前記遅延回路で遅延された前記指令信号に基づいて、前記電源と前記制御電極とを接続する第2スイッチ素子と、

を備える半導体素子の駆動回路。 - 前記第2スイッチ素子は、前記遅延回路で遅延された前記指令信号がゲートに入力されるpチャネルMOSFETであり、

前記指令信号の論理を反転させて前記遅延回路に出力する反転回路を備える、

請求項1記載の半導体素子の駆動回路。 - 前記遅延回路は、前記反転回路と前記pチャネルMOSFETのゲートとの間に直列接続された抵抗と、

前記pチャネルMOSFETのゲートとソースとの間に接続されたコンデンサと、

を備える請求項2記載の半導体素子の駆動回路。 - 前記第2スイッチ素子は、前記遅延回路で遅延された前記指令信号がゲートに入力されるnチャネルMOSFETである請求項1記載の半導体素子の駆動回路。

- 前記遅延回路は、一端が前記nチャネルMOSFETのゲートに接続され、他端に前記指令信号が入力される抵抗と、

一端が前記nチャネルMOSFETのゲートに接続され、他端が接地されたコンデンサと、

を備える請求項4記載の半導体素子の駆動回路。 - 前記第2スイッチ素子と前記制御電極との間に直列接続された第2抵抗部を備える請求項1から請求項5の何れか一項に記載の半導体素子の駆動回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016001772A JP2017123732A (ja) | 2016-01-07 | 2016-01-07 | 半導体素子の駆動回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016001772A JP2017123732A (ja) | 2016-01-07 | 2016-01-07 | 半導体素子の駆動回路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2017123732A true JP2017123732A (ja) | 2017-07-13 |

Family

ID=59305869

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016001772A Pending JP2017123732A (ja) | 2016-01-07 | 2016-01-07 | 半導体素子の駆動回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2017123732A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112714988A (zh) * | 2018-09-19 | 2021-04-27 | 松下知识产权经营株式会社 | 浪涌电流抑制装置和马达驱动装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004088892A (ja) * | 2002-08-26 | 2004-03-18 | Toshiba Corp | 絶縁ゲート型半導体素子のゲート回路 |

| JP2006340579A (ja) * | 2005-06-06 | 2006-12-14 | Toshiba Mitsubishi-Electric Industrial System Corp | 絶縁ゲート型半導体素子のゲート回路 |

| JP2015177694A (ja) * | 2014-03-17 | 2015-10-05 | 株式会社Ihi | 電圧駆動型電力用半導体素子の駆動回路 |

-

2016

- 2016-01-07 JP JP2016001772A patent/JP2017123732A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004088892A (ja) * | 2002-08-26 | 2004-03-18 | Toshiba Corp | 絶縁ゲート型半導体素子のゲート回路 |

| JP2006340579A (ja) * | 2005-06-06 | 2006-12-14 | Toshiba Mitsubishi-Electric Industrial System Corp | 絶縁ゲート型半導体素子のゲート回路 |

| JP2015177694A (ja) * | 2014-03-17 | 2015-10-05 | 株式会社Ihi | 電圧駆動型電力用半導体素子の駆動回路 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112714988A (zh) * | 2018-09-19 | 2021-04-27 | 松下知识产权经营株式会社 | 浪涌电流抑制装置和马达驱动装置 |

| CN112714988B (zh) * | 2018-09-19 | 2023-07-25 | 松下知识产权经营株式会社 | 浪涌电流抑制装置和马达驱动装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9083343B1 (en) | Cascode switching circuit | |

| JP5629386B2 (ja) | 半導体駆動回路およびそれを用いた電力変換装置 | |

| CN107615664B (zh) | 功率晶体管驱动装置 | |

| US8773177B2 (en) | Drive circuit | |

| JP4512671B1 (ja) | 電力変換回路 | |

| JP5993749B2 (ja) | 半導体装置のゲート駆動回路およびそれを用いた電力変換装置 | |

| CN102208864A (zh) | 开关设备驱动装置和半导体装置 | |

| CN105471417B (zh) | 用于反向导通的igbt的控制电路 | |

| JP6303663B2 (ja) | 電圧駆動型電力用半導体素子の駆動回路 | |

| JP6458552B2 (ja) | スイッチング方式の降圧型dc−dcコンバータ、及び電力変換回路 | |

| CN105099417A (zh) | 用于功率半导体开关的布置和方法 | |

| JP2013081137A (ja) | 半導体装置 | |

| KR102026929B1 (ko) | 전력 스위치용 게이트 구동회로 | |

| JP2018098849A (ja) | パワーモジュール | |

| JP6456524B2 (ja) | バッファ回路及び半導体装置 | |

| JP2017123732A (ja) | 半導体素子の駆動回路 | |

| JP2009017723A (ja) | 電流増幅半導体素子の駆動回路 | |

| CN116683752A (zh) | 一种驱动控制电路及控制方法 | |

| Bayerer et al. | Low impedance gate drive for full control of voltage controlled power devices | |

| JP5780489B2 (ja) | ゲート駆動回路 | |

| CN114362729A (zh) | 适应高结温环境的门极驱动电路及其开通方法、关断方法 | |

| WO2016192799A1 (en) | Parallel-coupled switching devices and switch-mode power converter | |

| JP5791758B1 (ja) | ゲート駆動回路 | |

| JP6312946B1 (ja) | 電力用半導体素子の駆動回路およびモータ駆動装置 | |

| JP5950961B2 (ja) | ゲート駆動回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20160108 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20181109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190924 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190925 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191009 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200107 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200406 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20200406 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20200414 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20200421 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20200619 |

|

| C211 | Notice of termination of reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C211 Effective date: 20200623 |

|

| C22 | Notice of designation (change) of administrative judge |

Free format text: JAPANESE INTERMEDIATE CODE: C22 Effective date: 20201006 |

|

| C23 | Notice of termination of proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C23 Effective date: 20201124 |

|

| C03 | Trial/appeal decision taken |

Free format text: JAPANESE INTERMEDIATE CODE: C03 Effective date: 20210105 |

|

| C30A | Notification sent |

Free format text: JAPANESE INTERMEDIATE CODE: C3012 Effective date: 20210105 |