JP2017108176A - 半導体装置、固体撮像装置、および撮像システム - Google Patents

半導体装置、固体撮像装置、および撮像システム Download PDFInfo

- Publication number

- JP2017108176A JP2017108176A JP2017043543A JP2017043543A JP2017108176A JP 2017108176 A JP2017108176 A JP 2017108176A JP 2017043543 A JP2017043543 A JP 2017043543A JP 2017043543 A JP2017043543 A JP 2017043543A JP 2017108176 A JP2017108176 A JP 2017108176A

- Authority

- JP

- Japan

- Prior art keywords

- metal member

- voltage

- electrode

- signal

- capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

【解決手段】第1段アンプおよび第2段アンプと、第1電極および第2電極を備える結合コンデンサと、前記第1段アンプの出力端子および前記第1電極を接続する第1金属部材と、前記第2段アンプの入力端子および前記第2電極を接続する第2金属部材とを有し、前記第2電極から前記第2段アンプの入力端子への方向に対して垂直な断面において、前記第2金属部材の上下左右のそれぞれの方向のうちの少なくとも2つの方向に前記第1金属部材が配置された半導体装置を提供する。

【選択図】 図3

Description

図1は第1実施形態に係る半導体装置の一例としての固体撮像装置100のブロック図である。個体撮像装置100はCMOSエリアセンサであって、画素アレイ10、垂直走査回路11、タイミングジェネレータ(TG)12、定電流回路13、列信号線14、増幅回路15、信号蓄積部16、水平走査回路17、水平転送回路18、出力回路19、出力パッド20を備える。画素アレイ10は、行方向及び列方向に沿って2次元マトリクス状に配列された複数の画素(PIX)101を備えている。図1においては、図面の簡略化のために4行4列の画素アレイ10が示されているが、画素101の数は特に限定されるものではない。なお、本明細書において、行方向とは図面において横方向を示し、列方向とは図面において縦方向を示すものとする。一例では、行方向が撮像装置における水平方向に対応し、列方向が撮像装置における垂直方向に対応する。

図4は、第2実施形態に係る半導体装置の一例としての固体撮像装置の回路図である。固体撮像装置はCMOSエリアセンサであって、画素アレイ2、周辺回路部5を備えている。図示されていないが、固体撮像装置は制御信号を生成するタイミングジェネレータ、画素アレイ2の各行を走査する垂直走査回路を備える。画素アレイ2は行方向及び列方向に沿って2次元マトリクス状に配列された複数の画素単位3を備える。

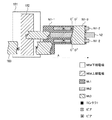

図6は、第3実施形態の出力回路のレイアウト断面図であり、図3の破線C−C’の領域の断面図に相当する。半導体基板110上には、第1の金属配線層Mt1、第2の金属配線層Mt2、第3の金属配線層Mt3が、それぞれ絶縁層を挟んで順に形成されている。第1の金属配線層Mt1にはGND163が形成され、第2の金属配線層Mt2にはノードN1の一部を構成する第1金属部材N1−2が形成されている。第3の金属配線層Mt3にはノードN1の一部を構成する2つの第1金属部材N1−3と、ノードN2を構成する第2金属部材N2が形成されている。第1金属部材N1−2と第1金属部材N1−3とはビア161、162によって接続されている。これらの第1金属部材N1−2、N1−3、第2金属部材N2は平面視において、結合コンデンサCmの電極から第2段ソースフォロア回路M2の入力への方向に延在している。図6の断面視において、第2金属部材N2の下方には第1金属部材N1−2が位置し、両側には2つの第1金属部材N1−3が位置している。すなわち、第2金属部材N2は下方と左右の3方向から第1金属部材N1に囲まれている。

図7は、第4実施形態の出力回路の断面図であり、図3の破線C−C’の領域の断面図に相当する。本実施形態においては、第1の金属配線層Mt1からなるGND171、第2の金属配線層Mt2からなるGND172および第1金属部材N1−2と、第3の金属配線層Mt3からなるGND173、第1金属部材N1−3、第2金属部材N2とが形成されている。GND171、172、173はビア174、175によって接続され、第1金属部材N1−2、N1−3はビア176によって接続されている。

第5実施形態においては、結合コンデンサCmがMIM(Metal Insulator Metal)コンデンサで構成されている。図8は第5実施形態の出力回路の平面レイアウト図である。結合コンデンサCmは、第1電極としてのMIM下部電極181、第2電極としてのMIM上部電極182を備える。MIM下部電極は第3の金属配線層Mt3(183)を介して第1段ソースフォロアMOSトランジスタM1のソース出力に接続され、MIM上部電極182は第2段ソースフォロアMOSトランジスタM2のゲート入力に接続される。図中、破線C−C’の領域の断面図、破線D−D’の部分の断面図は、それぞれ図3(b)、(c)で示される。第5実施形態で示すように、本発明の結合コンデンサCmはMIMコンデンサにも適用することができる。

図9は第6実施形態に係る出力回路の回路図である。第5実施形態に係る出力回路は3段のソースフォロア回路を備えて構成されている。図9において、図2の出力回路19と同一の構成は同一符号で表されている。出力回路は第1〜3段ソースフォロアのMOSトランジスタM1〜M3、結合コンデンサCm、Cm2、定電流源If1〜If3、スイッチSC、SC1を備える。ノードN3は第2段ソースフォロアMOSトランジスタM2の出力端子と結合コンデンサCm2の第1電極を接続する第3金属部材からなる。ノードN4は第3段ソースフォロアMOSトランジスタM3の入力端子と結合コンデンサCm2の電極を接続する第4金属部材からなる。スイッチSC2は基準電圧Vref1とノードN4を接続する。定電流源If3は第3段ソースフォロアMOSトランジスタM3の負荷定電流源である。

第7実施形態は、本発明を入力部に結合コンデンサを使ったゲインアンプに適用する例である。その一例として図4のゲインアンプGAへの適応例を説明する。第2実施形態の出力回路図とそのレイアウトの符号を利用して説明する。

図10は、本発明の第8実施形態による撮像システムの構成例を示す図である。撮像システム800は、例えば、光学部810、固体撮像装置100、映像信号処理部830、記録・通信部840、タイミング制御部850、システム制御部860、及び再生・表示部870を含む。撮像システム820は、撮像装置100及び映像信号処理部830を有する。撮像装置100は、先の実施形態で説明した固体撮像装置が用いられる。撮像システムはデジタルカメラ、ビデオカメラ、スマートフォンの他、撮影機能を有する様々な装置を含み得る。

本発明は、固体撮像装置、撮像システムに限定されることなく、第1段アンプの出力と第2段アンプの入力とが結合コンデンサによって接続された半導体装置に広く適用可能である。また、第1段アンプ、第2段アンプのソースフォロアMOSトランジスタはn型、p型を問わず、また、差動増幅器を用いたボルテージフォロアであっても良い。さらに、第1段アンプ、第2段アンプは電流増幅器に限定されず、電圧増幅器であっても良い。

5 周辺回路部

19 出力回路

20 出力パッド

Cm 結合コンデンサ

M1 第1段ソースフォロアMOSトランジスタ

M2 第2段ソースフォロアMOSトランジスタ

BR リセット電圧用出力回路

BV 輝度電圧用出力回路

GA ゲインアンプ

Claims (1)

- 第1段アンプおよび第2段アンプと、

第1電極および第2電極を備える結合コンデンサと、

前記第1段アンプの出力端子および前記第1電極を接続する第1金属部材と、

前記第2段アンプの入力端子および前記第2電極を接続する第2金属部材とを有し、

前記第2電極から前記第2段アンプの入力端子への方向に対して垂直な断面において、前記第2金属部材の上下左右のそれぞれの方向のうちの少なくとも2つの方向に前記第1金属部材が配置された半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017043543A JP2017108176A (ja) | 2017-03-08 | 2017-03-08 | 半導体装置、固体撮像装置、および撮像システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017043543A JP2017108176A (ja) | 2017-03-08 | 2017-03-08 | 半導体装置、固体撮像装置、および撮像システム |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014167227A Division JP6109125B2 (ja) | 2014-08-20 | 2014-08-20 | 半導体装置、固体撮像装置、および撮像システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017108176A true JP2017108176A (ja) | 2017-06-15 |

| JP2017108176A5 JP2017108176A5 (ja) | 2017-10-05 |

Family

ID=59060006

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017043543A Pending JP2017108176A (ja) | 2017-03-08 | 2017-03-08 | 半導体装置、固体撮像装置、および撮像システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2017108176A (ja) |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05291499A (ja) * | 1992-04-13 | 1993-11-05 | Ricoh Co Ltd | 半導体装置とその製造方法 |

| JP2000269211A (ja) * | 1999-03-15 | 2000-09-29 | Nec Corp | 半導体装置 |

| JP2001078093A (ja) * | 1999-09-02 | 2001-03-23 | Matsushita Electronics Industry Corp | 固体撮像装置 |

| JP2002299340A (ja) * | 2001-03-28 | 2002-10-11 | Sanyo Electric Co Ltd | 半導体装置の配線構造 |

| JP2006262388A (ja) * | 2005-03-18 | 2006-09-28 | Canon Inc | 固体撮像装置及びカメラ |

| JP2011205230A (ja) * | 2010-03-24 | 2011-10-13 | Fujitsu Semiconductor Ltd | A/d変換器 |

| JP2012010266A (ja) * | 2010-06-28 | 2012-01-12 | Sony Corp | 半導体装置、固体撮像装置、電子機器、および撮像装置 |

| JP2012156448A (ja) * | 2011-01-28 | 2012-08-16 | Oki Data Corp | 演算増幅器、駆動回路、駆動装置、および画像形成装置 |

| JP2012253818A (ja) * | 2012-09-10 | 2012-12-20 | Canon Inc | 撮像装置、及び撮像システム |

| JP2012257095A (ja) * | 2011-06-09 | 2012-12-27 | Olympus Corp | 固体撮像装置、撮像装置、および信号読み出し方法 |

| JP2014022414A (ja) * | 2012-07-12 | 2014-02-03 | Mitsumi Electric Co Ltd | 半導体集積回路 |

| JP2016046284A (ja) * | 2014-08-20 | 2016-04-04 | キヤノン株式会社 | 半導体装置、固体撮像装置、および撮像システム |

-

2017

- 2017-03-08 JP JP2017043543A patent/JP2017108176A/ja active Pending

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05291499A (ja) * | 1992-04-13 | 1993-11-05 | Ricoh Co Ltd | 半導体装置とその製造方法 |

| JP2000269211A (ja) * | 1999-03-15 | 2000-09-29 | Nec Corp | 半導体装置 |

| JP2001078093A (ja) * | 1999-09-02 | 2001-03-23 | Matsushita Electronics Industry Corp | 固体撮像装置 |

| JP2002299340A (ja) * | 2001-03-28 | 2002-10-11 | Sanyo Electric Co Ltd | 半導体装置の配線構造 |

| JP2006262388A (ja) * | 2005-03-18 | 2006-09-28 | Canon Inc | 固体撮像装置及びカメラ |

| JP2011205230A (ja) * | 2010-03-24 | 2011-10-13 | Fujitsu Semiconductor Ltd | A/d変換器 |

| JP2012010266A (ja) * | 2010-06-28 | 2012-01-12 | Sony Corp | 半導体装置、固体撮像装置、電子機器、および撮像装置 |

| JP2012156448A (ja) * | 2011-01-28 | 2012-08-16 | Oki Data Corp | 演算増幅器、駆動回路、駆動装置、および画像形成装置 |

| JP2012257095A (ja) * | 2011-06-09 | 2012-12-27 | Olympus Corp | 固体撮像装置、撮像装置、および信号読み出し方法 |

| JP2014022414A (ja) * | 2012-07-12 | 2014-02-03 | Mitsumi Electric Co Ltd | 半導体集積回路 |

| JP2012253818A (ja) * | 2012-09-10 | 2012-12-20 | Canon Inc | 撮像装置、及び撮像システム |

| JP2016046284A (ja) * | 2014-08-20 | 2016-04-04 | キヤノン株式会社 | 半導体装置、固体撮像装置、および撮像システム |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6109125B2 (ja) | 半導体装置、固体撮像装置、および撮像システム | |

| US7511275B2 (en) | Semiconductor device, and control method and device for driving unit component of semiconductor device | |

| US8023025B2 (en) | Photoelectric conversion apparatus and image pickup system using the same | |

| US9924121B2 (en) | Solid-state imaging device and method of driving the same transferring other part of charges to a combined capacitor | |

| US20120026371A1 (en) | Image capturing device, image capturing system, and method of driving image capturing device | |

| JP5813047B2 (ja) | 撮像装置、および、撮像システム。 | |

| US7486320B2 (en) | Photoelectric conversion device and image pickup system using the photoelectric conversion device | |

| CN107888853B (zh) | 固体摄像装置 | |

| JP2010178173A (ja) | 固体撮像装置 | |

| JP2001230974A (ja) | 固体撮像装置及び撮像システム | |

| JP6238558B2 (ja) | 撮像装置、および、撮像システム。 | |

| JP2012114838A (ja) | 固体撮像装置およびカメラシステム | |

| JP2011035787A (ja) | 固体撮像装置 | |

| JP2003051989A (ja) | 光電変換装置、固体撮像装置及びシステム | |

| US9426391B2 (en) | Solid-state imaging apparatus, method of controlling the same, and imaging system | |

| WO2013084408A1 (ja) | 固体撮像装置及びそれを備える撮像装置 | |

| JP6532224B2 (ja) | 撮像装置、撮像システム、及び撮像装置の駆動方法 | |

| JP5300292B2 (ja) | 光電変換装置の駆動方法 | |

| JP2017108176A (ja) | 半導体装置、固体撮像装置、および撮像システム | |

| US7030915B2 (en) | Signal processing apparatus | |

| JP2004274229A (ja) | 撮像装置 | |

| JP2021028989A (ja) | 撮像装置、撮像システム、および撮像装置の駆動方法 | |

| WO2011064921A1 (ja) | 固体撮像装置、その駆動方法、及び撮像装置 | |

| WO2023171133A1 (ja) | 固体撮像素子、および電子機器 | |

| JP2000223688A (ja) | 固体撮像装置およびカメラシステム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170821 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170821 |

|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20171214 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20180126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180411 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180524 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190311 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20190829 |