JP2017097633A - 車両制御装置 - Google Patents

車両制御装置 Download PDFInfo

- Publication number

- JP2017097633A JP2017097633A JP2015229375A JP2015229375A JP2017097633A JP 2017097633 A JP2017097633 A JP 2017097633A JP 2015229375 A JP2015229375 A JP 2015229375A JP 2015229375 A JP2015229375 A JP 2015229375A JP 2017097633 A JP2017097633 A JP 2017097633A

- Authority

- JP

- Japan

- Prior art keywords

- unit

- diagnosis

- area

- storage area

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1652—Handling requests for interconnection or transfer for access to memory bus based on arbitration in a multiprocessor architecture

- G06F13/1663—Access to shared memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/22—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing

- G06F11/2205—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested

- G06F11/2236—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested to test CPU or processors

- G06F11/2242—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested to test CPU or processors in multi-processor systems, e.g. one processor becoming the test master

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

- G06F11/34—Recording or statistical evaluation of computer activity, e.g. of down time, of input/output operation ; Recording or statistical evaluation of user activity, e.g. usability assessment

- G06F11/3466—Performance evaluation by tracing or monitoring

- G06F11/3495—Performance evaluation by tracing or monitoring for systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/061—Improving I/O performance

- G06F3/0613—Improving I/O performance in relation to throughput

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Quality & Reliability (AREA)

- Human Computer Interaction (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Abstract

【解決手段】車両制御装置1は、記憶装置5が有する共有記憶領域51を診断する間は当該記憶装置5に対する演算装置2または演算装置3のアクセス先を、診断対象領域内に格納されているデータに代えて、補助記憶領域52内に格納されている複製データに変更することにより制御演算を実行することにより、演算効率の低下を抑制する。

【選択図】図1

Description

図1は、本発明の実施形態1に係る車両制御装置(ECU)1の構成図である。ECU1は、例えばエンジン制御装置などのような車両の動作を制御する装置であり、第1演算装置2、第2演算装置3、プログラム領域4、記憶装置5、入出力回路6を備える。ここではECU1が接続されている機器としてスロットルセンサ7とアクチュエータ8を例示するがこれに限られるものではない。

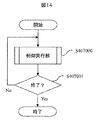

第1演算装置制御部401は、記憶装置5が管理する各テーブル(フラグ管理テーブル51100、診断進捗管理テーブル51300、共有領域管理テーブル51400、補助記憶領域管理テーブル52100)を初期化する。

第1演算装置制御部401は、診断判定部402を呼び出す。診断判定部402の動作については後述の図9で説明する。診断判定部402は、メモリ診断を実施すべきタイミングであるか否かを判定する役割を有する。

第1演算装置制御部401は、診断管理部403を呼び出す。診断管理部403の動作については後述の図10で説明する。診断管理部403は、メモリ診断の全体動作を制御する役割を有する。

第1演算装置制御部401は、終了条件が満たされているか否かを判定する。満たされていれば本フローチャートを終了し、満たされていなければステップS401001へ戻る。終了条件は、例えばECU1の電源をOFFする命令が入力されていることなどである。

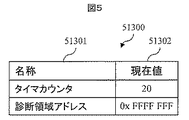

診断判定部402は、診断進捗管理テーブル51300からタイマカウンタの現在値フィールド51302を取得する。診断判定部402は、タイマカウンタの値をインクリメントし、診断進捗管理テーブル51300の対応するフィールドにインクリメントした値を格納する。

診断判定部402は、診断パラメータテーブル51200から診断実行周期の値フィールド51202(図示する例においては200)を取得する。診断判定部402は、取得したタイマカウンタを取得した診断実行周期により除算した余りを算出する。算出した余りが0であればステップS402001に進み、その他の場合は本フローチャートを終了する。

診断判定部402は、フラグ管理テーブル51100が格納している診断開始フラグの現在値フィールド51102に1(メモリ診断を開始することを示す値)を格納する。診断管理部403は、後述するステップS403000においてこの診断開始フラグの値を確認することにより、メモリ診断を開始すべきタイミングに到達しているか否かを判定することができる。

診断管理部403は、フラグ管理テーブル51100から診断開始フラグの現在値フィールド51102を取得する。診断開始フラグが1であればステップS403001に進み、その他の場合は本フローチャートを終了する。

診断管理部403は、コンテキスト管理部404を呼び出す。コンテキスト管理部404の動作については後述の図11で説明する。コンテキスト管理部404は、共有領域51が格納しているデータを補助記憶領域52へ退避し、または退避したデータを補助記憶領域52から共有領域51へ戻す役割を有する。本ステップにおいてはデータを補助記憶領域52へ退避することになる。

診断管理部403は、通知部405を呼び出す。通知部405の動作については後述の図12で説明する。通知部405は、いずれかの演算装置が共有領域51に対するメモリ診断を実施するとき他の演算装置に対してその旨を割り込み処理により通知し、または診断完了後にその旨を通知する役割を有する。本ステップにおいては診断開始を通知することになる。

診断管理部403は、診断実行部406を呼び出す。診断実行部406の動作については後述の図13で説明する。診断実行部406は、共有領域51に対するメモリ診断を実際に実施する役割を有する。

診断管理部403は、改めてコンテキスト管理部404を呼び出す。本ステップにおいては補助記憶領域52へ退避したデータを共有領域51へ書き戻すことになる。

診断管理部403は、通知部405を呼び出す。本ステップにおいては診断完了を通知することになる。

コンテキスト管理部404は、診断進捗管理テーブル51300から診断領域アドレスの現在値フィールド51302を取得する。診断領域アドレスは、現在メモリ診断を実施する対象となっている診断対象領域のアドレスを示す値である。診断領域アドレスがセットされていない場合は、診断パラメータテーブル51200から開始アドレスの値フィールド51202を取得し、これを診断領域アドレスの現在値フィールド51302として格納する。開始アドレスは、診断すべき記憶領域の先頭アドレスを指定する値であり、例えば共有領域51の先頭アドレスが指定される。

コンテキスト管理部404は、フラグ管理テーブル51100から診断完了フラグの現在値フィールド51102を取得する。診断完了フラグが0であればステップS404002へ進み、0でない場合はステップS404006に進む。診断完了フラグは、共有領域51全体に対するメモリ診断を完了したか否かを示すフラグである。

コンテキスト管理部404は、診断パラメータテーブル51200から終了アドレスの値フィールド51202を取得する。終了アドレスは、診断すべき記憶領域の終端アドレスを指定する値であり、例えば共有領域51の終端アドレスが指定される。コンテキスト管理部404は、現在の診断領域アドレスと終了アドレスを比較する。一致した場合はステップS404003に進み、一致しない場合はステップS404004に進む。

コンテキスト管理部404は、診断パラメータテーブル51200から開始アドレスの値フィールド51202を取得し、診断進捗管理テーブル51300の診断領域アドレスの現在値フィールド51302として格納する。本ステップは、メモリ診断を完了した後に開始アドレスを先頭まで戻すためのものである。

コンテキスト管理部404は、診断領域アドレスの現在値フィールド51302を次の診断対象領域のアドレスへ更新する。例えば、後述する診断実行部406が一度に診断することができる記憶領域の個数に対して各記憶領域のサイズを乗算した数値を用いて、診断領域アドレスをインクリメントする。診断実行部406が一度に診断することができる記憶領域の個数は、診断パラメータテーブル51200の診断可能アドレス数の値フィールド51202によって指定することができる。補助記憶領域52に対してデータを退避することを考慮すると、診断実行部406が一度に診断することができる記憶領域の個数は、退避先のデータサイズが補助記憶領域52の最大サイズ以下となるようにすることが望ましい。

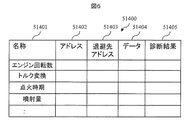

コンテキスト管理部404は、診断領域アドレスが格納しているデータを、補助記憶領域52に対して退避する。具体的には、診断領域アドレスの現在値から開始して、診断可能アドレス数に対して各記憶領域のサイズを乗算した数値のアドレスに至るまでの間の記憶領域に格納されているデータを、補助記憶領域52へコピーする。コンテキスト管理部404は、データを退避する補助記憶領域52上のアドレスを退避先アドレスフィールド51403に格納するとともに、退避前における共有領域51上のアドレスと退避したデータをそれぞれ退避元アドレスフィールド52103と退避元データ52104に格納する。

コンテキスト管理部404は、退避先アドレスフィールド51403と退避元アドレスフィールド52103をそれぞれコピー元アドレスとコピー先アドレスとして用いることにより、補助記憶領域52に退避したデータを共有領域51に対してコピーする。これにより、退避したデータを復帰することができる。ただし後述するように制御実行部410が補助記憶領域52上のデータを上書きする場合もあるので、コピー前後に係るデータ値が同一であるとは限らない。

コンテキスト管理部404は、フラグ管理テーブル51100の診断完了フラグの現在値フィールド51102に対して0を格納する。

通知部405は、第2演算装置3に対して、共有領域51の診断を開始した旨を知らせる割り込み処理を発生させる。通知が遅延しないようにするためには割り込み処理を用いることが望ましいが、遅延が許容範囲内に収まると見込まれるのであれば、その他手法を用いて通知してもよい。

診断実行部406は、診断パラメータテーブル51200から診断用テストデータの値フィールド51202を取得する。診断実行部406は、取得した診断用テストデータを診断領域アドレスに対して書き込む。

診断実行部406は、診断領域アドレスからデータを読み出す。

診断実行部406は、ステップS406001において読み出したデータと、ステップS406000において書き込んだ診断用テストデータとを比較する(S406002)。両者が一致する場合はステップS406005に進み、不一致だった場合ステップS406004に進む。

診断実行部406は、共有領域管理テーブル51400の診断結果フィールド51405に対して、当該領域が異常である旨を示す値(例えば0は正常、1は異常など)を記録する。

診断実行部406は、診断可能アドレス数が指定する個数だけ、これらステップを並列して実施することができる。例えば診断開始アドレスから開始して、32個の記憶領域に対して並列的にこれらステップを実施することができる。これにより診断可能アドレス数の個数分だけ一括してメモリ診断を実施することができる。並列的に実施することに代えて、対象アドレスを内部的にインクリメントしながらこれらステップを繰り返し実施することにより、同様に一括診断することもできる。

診断実行部406は、フラグ管理テーブル51100の診断完了フラグの現在値フィールド51102に対して1を格納する。

第2演算装置制御部407は、制御実行部410を呼び出す。制御実行部410の動作については後述の図17で説明する。制御実行部410は、制御演算を実施する役割を有する。

第2演算装置制御部407は、終了条件が満たされているか否かを判定する。満たされていれば本フローチャートを終了し、満たされていなければステップS407000へ戻る。終了条件は、例えばECU1の電源をOFFする命令が入力されていることなどである。

割り込み実行部408は、アクセス先設定部409を呼び出す。アクセス先設定部409の動作については後述の図16で説明する。アクセス先設定部409は、共有領域51が格納しているデータを用いて制御演算を実施するのか、それとも補助記憶領域52が格納しているデータを用いて制御演算を実施するのかを切り替える役割を有する。

アクセス先設定部409は、フラグ管理テーブル51100からアクセス先変更フラグの現在値フィールド51102を取得する。アクセス先変更フラグの値が0であればステップS409001へ進み、1であればステップS409003へ進む。

アクセス先設定部409は、診断進捗管理テーブル51300から診断領域アドレスの現在値フィールド51302を取得するとともに、診断パラメータテーブル51200から診断可能アドレス数の値フィールド51202を取得する。アクセス先設定部409は、共有領域管理テーブル51400が管理している記憶領域のうち、取得した診断領域アドレスと診断可能アドレス数に対応する分については、制御実行部410が補助記憶領域52の対応する記憶領域に対してデータを読み書きするようにアクセス先を変更する。本フローチャートを実行するのは第2演算装置3なので、第2演算装置3自身がアクセス先を変更してもよいし、いずれの記憶領域に対してアクセスすべきかを示すフラグなどのデータを適当な記憶領域上に保持してもよい。

アクセス先設定部409は、フラグ管理テーブル51100のアクセス先変更フラグの現在値フィールド51102を1に更新する。

アクセス先設定部409は、診断進捗管理テーブル51300から診断領域アドレスの現在値フィールド51302を取得するとともに、診断パラメータテーブル51200から診断可能アドレス数の値フィールド51202を取得する。アクセス先設定部409は、共有領域管理テーブル51400が管理している記憶領域のうち、取得した診断領域アドレスと診断可能アドレス数に対応する分については、制御実行部410が共有領域51の対応する記憶領域に対してデータを読み書きするようにアクセス先を変更する。具体的手段はステップS409001と同様である。

アクセス先設定部409は、フラグ管理テーブル51100のアクセス先変更フラグの現在値フィールド51102を0に更新する。

制御実行部410は、制御演算において必要になるデータを、共有領域51または補助記憶領域52から取得する。いずれの記憶領域から取得するかについては、ステップS409001またはS409003において指定される。補助記憶領域52へデータを退避している間のアクセス先アドレスは、退避先アドレスフィールド51403から取得することができる。

制御実行部410は、ステップS410000において取得したデータを用いて、制御演算を実施する。

制御実行部410は、制御演算の結果を、ステップS410000においてデータを取得した記憶領域に対して書き込む。補助記憶領域52に対して演算結果を書き込んだ場合であっても、ステップS404006により共有領域51に対してその書き込まれたデータが反映されるので、制御演算の整合性を保つことができる。

本実施形態1に係るECU1は、共有領域51に対してメモリ診断を実施している間は診断対象領域内のデータを補助記憶領域52へ退避し、演算装置は退避されたデータを用いて制御演算を実施する。これにより、メモリ診断中においても演算装置の利用効率を高めることができる。

実施形態1において、共有領域51と補助記憶領域52は記憶装置5の一部として構成されているが、これら記憶領域を互いに異なる記憶装置上に構成することもできる。例えば共有領域51をRAM上に構築するとともに、補助記憶領域52はRAMよりも信頼性の高いメモリ装置上に構築することができる。この別メモリ装置はECU1内に配置してもよいしECU1の外部に設けてECU1からアクセスするようにしてもよい。

実施形態1〜2においては、第1演算装置2が共有領域51に対するメモリ診断を実施し、第2演算装置3が制御演算を実施することを説明したが、双方の演算装置がいずれもメモリ診断と制御演算を実施してもよいし、いずれかの演算装置はメモリ診断のみを実施するとともに他の演算装置はメモリ診断と制御演算をともに実施してもよい。

本発明は上記実施形態に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施形態は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施形態の構成の一部を他の実施形態の構成に置き換える事が可能であり、また、ある実施形態の構成に他の実施形態の構成を加えることも可能である。また、各実施形態の構成の一部について他の構成の追加・削除・置換をすることができる。

Claims (12)

- 車両の動作を制御する車両制御装置であって、

前記車両の動作を制御する制御演算を実行する第1および第2演算装置、

前記第1および第2演算装置が共有する共有記憶領域を診断するメモリ診断部、

前記メモリ診断部が診断する診断対象領域が格納しているデータの複製を記憶する補助記憶部、

前記メモリ診断部が前記診断対象領域を診断する間は前記第1および第2演算装置が前記診断対象領域内に格納されているデータに代えて前記補助記憶部内に格納されている前記複製を用いて前記制御演算を実行するようにアクセス先アドレスを設定するアクセス先設定部、

を備えることを特徴とする車両制御装置。 - 前記メモリ診断部は、前記共有記憶領域を診断する処理を実装したメモリ診断プログラムとして構成されており、

前記第1演算装置は、前記メモリ診断部を実行することにより前記共有記憶領域を診断し、

前記車両制御装置はさらに、前記第1演算装置が前記メモリ診断部を実行開始すると前記共有記憶領域が診断中である旨を前記アクセス先設定部に対して通知する通知部を備えており、

前記アクセス先設定部は、前記通知部から前記共有記憶領域が診断中である旨の通知を受け取ると、前記第2演算装置が前記診断対象領域に代えて前記補助記憶部に対してアクセスするようにアクセス先アドレスを設定する

ことを特徴とする請求項1記載の車両制御装置。 - 前記車両制御装置は、前記第1および第2演算装置がアクセスするメモリ装置を備え、

前記共有記憶領域と前記補助記憶部はともに、前記メモリ装置が有する記憶領域として構成されている

ことを特徴とする請求項1記載の車両制御装置。 - 前記車両制御装置は、前記共有記憶領域を有する共有記憶装置を備え、

前記補助記憶部は、前記複製を記憶する補助記憶領域として構成されており、

前記車両制御装置はさらに、前記共有記憶装置とは異なる記憶装置であって前記補助記憶領域を有する補助記憶装置を備える

ことを特徴とする請求項1記載の車両制御装置。 - 前記補助記憶装置は、前記共有記憶装置よりも信頼性の高い記憶装置によって構成されている

ことを特徴とする請求項4記載の車両制御装置。 - 前記補助記憶装置は、いずれかの演算装置がデータを書き込む間は他の演算装置からのアクセスを排除する排他的記憶装置として構成されることにより、前記共有記憶装置よりも高い信頼性を有する記憶装置として構成されている

ことを特徴とする請求項5記載の車両制御装置。 - 前記通知部は、前記第1演算装置が前記メモリ診断部を実行完了すると前記共有記憶領域の診断が完了した旨を前記アクセス先設定部に対して通知し、

前記アクセス先設定部は、前記通知部から前記共有記憶領域の診断が完了した旨の通知を受け取ると、前記第2演算装置が前記補助記憶部に代えて前記診断対象領域に対してアクセスするようにアクセス先アドレスを設定する

ことを特徴とする請求項2記載の車両制御装置。 - 前記共有記憶領域は、前記メモリ診断部が一括して診断する前記診断対象領域の個数を指定する診断個数データを格納しており、

前記補助記憶部は、前記診断個数データが指定する前記個数以上の前記診断対象領域の複製を記憶することができる記憶容量を備え、

前記メモリ診断部は、前記診断個数データが指定する前記個数の前記診断対象領域を一括して診断し、

前記アクセス先アドレス設定部は、前記メモリ診断部が前記共有記憶領域の診断を開始してから前記診断個数データが指定する前記個数の前記診断対象領域を診断し終えるまでの間は、前記第1および第2演算装置が前記診断対象領域内に格納されているデータに代えて前記補助記憶部内に格納されている前記複製を用いて前記制御演算を実行するようにアクセス先アドレスを設定する

ことを特徴とする請求項1記載の車両制御装置。 - 前記共有記憶領域は、前記複製を記憶している前記補助記憶部上のアドレスを記述する退避先アドレスデータを格納し、

前記第1および第2演算装置は、前記退避先アドレスデータが記述している前記補助記憶部上のアドレスから前記複製を取得する

ことを特徴とする請求項1記載の車両制御装置。 - 前記補助記憶部は、前記診断対象領域を格納している前記共有記憶領域上のアドレスを記述する退避元アドレスデータを格納し、

前記第1演算装置は、前記共有記憶領域の診断が完了した後、前記退避先アドレスデータが記述している前記補助記憶部上のアドレスが格納しているデータを取得し、前記退避元アドレスデータが記述しているアドレスに対してその取得したデータを書き戻す

ことを特徴とする請求項9記載の車両制御装置。 - 前記メモリ診断部は、前記共有領域を診断する処理を実装したメモリ診断プログラムとして構成されており、

前記第1および第2演算装置は、前記共有記憶領域のうち自身がデータを書き込む領域に対して、前記メモリ診断部を実行することにより前記診断を実施する

ことを特徴とする請求項1記載の車両制御装置。 - 前記メモリ診断部は、前記共有記憶領域を診断する処理を実装したメモリ診断プログラムとして構成されており、

前記第1および第2演算装置は、前記共有記憶領域のうち自身がデータを書き込む割合が他の演算装置よりも高い領域に対して、前記メモリ診断部を実行することにより前記診断を実施する

ことを特徴とする請求項1記載の車両制御装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015229375A JP2017097633A (ja) | 2015-11-25 | 2015-11-25 | 車両制御装置 |

| US15/761,972 US10789184B2 (en) | 2015-11-25 | 2016-10-26 | Vehicle control device |

| EP16868313.4A EP3382562B1 (en) | 2015-11-25 | 2016-10-26 | Vehicle control device |

| PCT/JP2016/081655 WO2017090364A1 (ja) | 2015-11-25 | 2016-10-26 | 車両制御装置 |

| CN201680055509.3A CN108351840B (zh) | 2015-11-25 | 2016-10-26 | 车辆控制装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015229375A JP2017097633A (ja) | 2015-11-25 | 2015-11-25 | 車両制御装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018181912A Division JP6654230B2 (ja) | 2018-09-27 | 2018-09-27 | 車両制御装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017097633A true JP2017097633A (ja) | 2017-06-01 |

| JP2017097633A5 JP2017097633A5 (ja) | 2018-04-19 |

Family

ID=58764185

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015229375A Pending JP2017097633A (ja) | 2015-11-25 | 2015-11-25 | 車両制御装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10789184B2 (ja) |

| EP (1) | EP3382562B1 (ja) |

| JP (1) | JP2017097633A (ja) |

| CN (1) | CN108351840B (ja) |

| WO (1) | WO2017090364A1 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020060928A (ja) * | 2018-10-10 | 2020-04-16 | トヨタ自動車株式会社 | モータ制御用の情報処理装置 |

| JP2020194357A (ja) * | 2019-05-28 | 2020-12-03 | 株式会社東芝 | 情報処理回路及び情報処理方法 |

| JP2021046799A (ja) * | 2019-09-17 | 2021-03-25 | 株式会社デンソー | 車載制御装置 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11197136B2 (en) * | 2018-09-26 | 2021-12-07 | Micron Technology, Inc. | Accessing a memory resource at one or more physically remote entities |

| JP2022065218A (ja) * | 2019-03-05 | 2022-04-27 | 日立Astemo株式会社 | 車両制御装置 |

| EP3822786A1 (en) * | 2019-11-12 | 2021-05-19 | Visteon Global Technologies, Inc. | A data processing system and a method for controlling a data processing system |

| CN113742795A (zh) * | 2020-05-27 | 2021-12-03 | 台湾积体电路制造股份有限公司 | 对集成电路中的半导体存储器的安全级别进行认证的方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04125753A (ja) * | 1990-09-17 | 1992-04-27 | Fujitsu Ltd | メモリのオンライン診断方式 |

| JP2007066246A (ja) * | 2005-09-02 | 2007-03-15 | Hitachi Ltd | コントローラの自己診断システム及び方法 |

| JP2007226640A (ja) * | 2006-02-24 | 2007-09-06 | Nec Corp | メモリ診断処理回路およびメモリ診断処理方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100230454B1 (ko) * | 1997-05-28 | 1999-11-15 | 윤종용 | 다중처리 시스템의 캐시메모리 검사방법 |

| JP2001167005A (ja) * | 1999-12-08 | 2001-06-22 | Nec Corp | メモリ診断方法とメモリ診断回路および半導体記憶装置 |

| US6763432B1 (en) * | 2000-06-09 | 2004-07-13 | International Business Machines Corporation | Cache memory system for selectively storing directory information for a higher level cache in portions of a lower level cache |

| US8219762B1 (en) * | 2004-08-13 | 2012-07-10 | Oracle America, Inc. | Computer system and method for leasing memory location to allow predictable access to memory location |

| FR2884629B1 (fr) * | 2005-04-15 | 2007-06-22 | Atmel Corp | Dispositif d'amelioration de la bande passante pour des circuits munis de controleurs memoires multiples |

| JP4979060B2 (ja) * | 2006-03-03 | 2012-07-18 | ルネサスエレクトロニクス株式会社 | 表示制御用半導体集積回路 |

| JP4458119B2 (ja) * | 2007-06-11 | 2010-04-28 | トヨタ自動車株式会社 | マルチプロセッサシステム及びその制御方法 |

| US8549208B2 (en) * | 2008-12-08 | 2013-10-01 | Teleputers, Llc | Cache memory having enhanced performance and security features |

| US9037928B2 (en) * | 2012-01-01 | 2015-05-19 | Mosys, Inc. | Memory device with background built-in self-testing and background built-in self-repair |

| JP5725040B2 (ja) * | 2011-01-13 | 2015-05-27 | 富士通株式会社 | マルチコアプロセッサシステム、およびスケジューリング方法 |

| JP5745868B2 (ja) * | 2011-01-18 | 2015-07-08 | トヨタ自動車株式会社 | マルチプロセッサシステム |

| US20180107591A1 (en) * | 2011-04-06 | 2018-04-19 | P4tents1, LLC | System, method and computer program product for fetching data between an execution of a plurality of threads |

| JP5816572B2 (ja) * | 2012-02-23 | 2015-11-18 | 日立オートモティブシステムズ株式会社 | 車両用制御装置 |

| US20140310488A1 (en) * | 2013-04-11 | 2014-10-16 | Transparent Io, Inc. | Logical Unit Management using Differencing |

| JP6145345B2 (ja) | 2013-07-22 | 2017-06-07 | 日立オートモティブシステムズ株式会社 | 自動車用電子制御装置 |

| US9213634B2 (en) * | 2013-11-22 | 2015-12-15 | Apple Inc. | Efficient reuse of segments in nonoverwrite storage systems |

| JP6243266B2 (ja) * | 2014-03-20 | 2017-12-06 | 日立オートモティブシステムズ株式会社 | 電子制御装置及びメモリ診断方法 |

| US9449717B2 (en) * | 2014-06-20 | 2016-09-20 | Arm Limited | Memory built-in self-test for a data processing apparatus |

-

2015

- 2015-11-25 JP JP2015229375A patent/JP2017097633A/ja active Pending

-

2016

- 2016-10-26 EP EP16868313.4A patent/EP3382562B1/en active Active

- 2016-10-26 US US15/761,972 patent/US10789184B2/en active Active

- 2016-10-26 WO PCT/JP2016/081655 patent/WO2017090364A1/ja active Application Filing

- 2016-10-26 CN CN201680055509.3A patent/CN108351840B/zh active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04125753A (ja) * | 1990-09-17 | 1992-04-27 | Fujitsu Ltd | メモリのオンライン診断方式 |

| JP2007066246A (ja) * | 2005-09-02 | 2007-03-15 | Hitachi Ltd | コントローラの自己診断システム及び方法 |

| JP2007226640A (ja) * | 2006-02-24 | 2007-09-06 | Nec Corp | メモリ診断処理回路およびメモリ診断処理方法 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020060928A (ja) * | 2018-10-10 | 2020-04-16 | トヨタ自動車株式会社 | モータ制御用の情報処理装置 |

| JP7176341B2 (ja) | 2018-10-10 | 2022-11-22 | 株式会社デンソー | モータ制御用の情報処理装置 |

| JP2020194357A (ja) * | 2019-05-28 | 2020-12-03 | 株式会社東芝 | 情報処理回路及び情報処理方法 |

| JP7235591B2 (ja) | 2019-05-28 | 2023-03-08 | 株式会社東芝 | 情報処理回路及び情報処理方法 |

| JP2021046799A (ja) * | 2019-09-17 | 2021-03-25 | 株式会社デンソー | 車載制御装置 |

| JP7259666B2 (ja) | 2019-09-17 | 2023-04-18 | 株式会社デンソー | 車載制御装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3382562A1 (en) | 2018-10-03 |

| WO2017090364A1 (ja) | 2017-06-01 |

| US20180253390A1 (en) | 2018-09-06 |

| EP3382562B1 (en) | 2022-12-07 |

| US10789184B2 (en) | 2020-09-29 |

| CN108351840A (zh) | 2018-07-31 |

| EP3382562A4 (en) | 2019-09-04 |

| CN108351840B (zh) | 2022-06-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| WO2017090364A1 (ja) | 車両制御装置 | |

| JP6800850B2 (ja) | 中央処理装置(cpu)と補助プロセッサとの間の改善した関数コールバック機構 | |

| JP5776688B2 (ja) | 情報処理装置及びタスク切り替え方法 | |

| WO2020177577A1 (zh) | 一种控制器加载多核固件的方法、装置及计算机设备 | |

| JP6654230B2 (ja) | 車両制御装置 | |

| JP2013225208A (ja) | 情報処理装置、情報処理方法、及びプログラム | |

| EP2643576B1 (en) | Method for enabling calibration during start-up of a micro controller unit and integrated circuit therefor | |

| US10705993B2 (en) | Programming and controlling compute units in an integrated circuit | |

| CN112667442A (zh) | 基于非易失内存器件启动系统的控制方法、装置及设备 | |

| JP2015035007A (ja) | コンピュータ、制御プログラム、及びダンプ制御方法 | |

| JP6243266B2 (ja) | 電子制御装置及びメモリ診断方法 | |

| JP5644380B2 (ja) | 情報処理装置 | |

| JP6365387B2 (ja) | 電子制御装置 | |

| CN109358903B (zh) | 数据访问设备和访问错误通知方法 | |

| JP2013061783A (ja) | マルチコア・プロセッサ | |

| TW202119215A (zh) | 共用代碼之系統與代碼共用方法 | |

| US11003474B2 (en) | Semiconductor device for providing a virtualization technique | |

| JP2020030507A (ja) | マルチコア制御装置 | |

| US10007624B2 (en) | Electronic device for blocking interrupt requests | |

| JP2007172519A (ja) | 情報処理装置、ソフトウェアモジュールのリンク管理方法及びプログラム | |

| JP2001256055A (ja) | プログラムダウンロード方式 | |

| JP2016154001A (ja) | 画像処理装置、画像処理用データ転送制御方法、及び画像処理用データ転送制御プログラム | |

| WO2016117102A1 (ja) | 計算機システム | |

| JP2019020896A (ja) | プロセッサ及びメモリモジュール | |

| CN115993994A (zh) | 系统加速方法、装置、电子设备及存储介质 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180305 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180305 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180528 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20180710 |