JP2016012713A - 樹脂フィルム、半導体装置および半導体装置の製造方法 - Google Patents

樹脂フィルム、半導体装置および半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2016012713A JP2016012713A JP2015004623A JP2015004623A JP2016012713A JP 2016012713 A JP2016012713 A JP 2016012713A JP 2015004623 A JP2015004623 A JP 2015004623A JP 2015004623 A JP2015004623 A JP 2015004623A JP 2016012713 A JP2016012713 A JP 2016012713A

- Authority

- JP

- Japan

- Prior art keywords

- resin film

- film layer

- resin

- resin layer

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

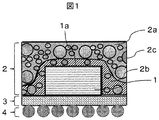

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

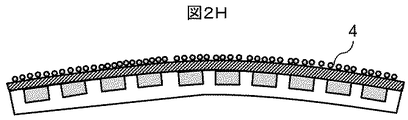

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/293—Organic, e.g. plastic

- H01L23/295—Organic, e.g. plastic containing a filler

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3135—Double encapsulation or coating and encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/96—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being encapsulated in a common layer, e.g. neo-wafer or pseudo-wafer, said common layer being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/568—Temporary substrate used as encapsulation process aid

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/12105—Bump connectors formed on an encapsulation of the semiconductor or solid-state body, e.g. bumps on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

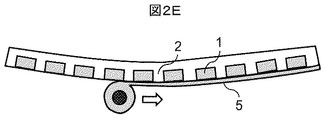

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Laminated Bodies (AREA)

- Sealing Material Composition (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015004623A JP2016012713A (ja) | 2014-06-05 | 2015-01-14 | 樹脂フィルム、半導体装置および半導体装置の製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014116766 | 2014-06-05 | ||

| JP2014116766 | 2014-06-05 | ||

| JP2015004623A JP2016012713A (ja) | 2014-06-05 | 2015-01-14 | 樹脂フィルム、半導体装置および半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016012713A true JP2016012713A (ja) | 2016-01-21 |

| JP2016012713A5 JP2016012713A5 (enExample) | 2017-04-13 |

Family

ID=55229218

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015004623A Pending JP2016012713A (ja) | 2014-06-05 | 2015-01-14 | 樹脂フィルム、半導体装置および半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2016012713A (enExample) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017117842A (ja) * | 2015-12-21 | 2017-06-29 | 京セラ株式会社 | 電子部品及び電子部品の製造方法 |

| WO2018181761A1 (ja) * | 2017-03-31 | 2018-10-04 | 日立化成株式会社 | 封止フィルム、電子部品装置の製造方法及び電子部品装置 |

| JP2020068237A (ja) * | 2018-10-22 | 2020-04-30 | 新光電気工業株式会社 | 配線基板 |

| CN111370337A (zh) * | 2020-03-18 | 2020-07-03 | 深圳杰微芯片科技有限公司 | 降低封装翘曲方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0823005A (ja) * | 1993-09-14 | 1996-01-23 | Toshiba Corp | 樹脂封止型半導体装置の製造方法、樹脂封止型半導体装置及び封止用樹脂シート |

| JP2011187877A (ja) * | 2010-03-11 | 2011-09-22 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2014056924A (ja) * | 2012-09-12 | 2014-03-27 | Hitachi Chemical Co Ltd | 半導体装置の製造方法及びそれに用いる熱硬化性樹脂組成物並びにそれらにより得られる半導体装置 |

-

2015

- 2015-01-14 JP JP2015004623A patent/JP2016012713A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0823005A (ja) * | 1993-09-14 | 1996-01-23 | Toshiba Corp | 樹脂封止型半導体装置の製造方法、樹脂封止型半導体装置及び封止用樹脂シート |

| JP2011187877A (ja) * | 2010-03-11 | 2011-09-22 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2014056924A (ja) * | 2012-09-12 | 2014-03-27 | Hitachi Chemical Co Ltd | 半導体装置の製造方法及びそれに用いる熱硬化性樹脂組成物並びにそれらにより得られる半導体装置 |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017117842A (ja) * | 2015-12-21 | 2017-06-29 | 京セラ株式会社 | 電子部品及び電子部品の製造方法 |

| WO2018181761A1 (ja) * | 2017-03-31 | 2018-10-04 | 日立化成株式会社 | 封止フィルム、電子部品装置の製造方法及び電子部品装置 |

| CN110462818A (zh) * | 2017-03-31 | 2019-11-15 | 日立化成株式会社 | 密封膜、电子部件装置的制造方法及电子部件装置 |

| KR20190132401A (ko) * | 2017-03-31 | 2019-11-27 | 히타치가세이가부시끼가이샤 | 봉지 필름, 전자 부품 장치의 제조 방법 및 전자 부품 장치 |

| JPWO2018181761A1 (ja) * | 2017-03-31 | 2020-02-20 | 日立化成株式会社 | 封止フィルム、電子部品装置の製造方法及び電子部品装置 |

| JP7115469B2 (ja) | 2017-03-31 | 2022-08-09 | 昭和電工マテリアルズ株式会社 | 封止フィルム、電子部品装置の製造方法及び電子部品装置 |

| KR102440947B1 (ko) * | 2017-03-31 | 2022-09-05 | 쇼와덴코머티리얼즈가부시끼가이샤 | 봉지 필름, 전자 부품 장치의 제조 방법 및 전자 부품 장치 |

| CN110462818B (zh) * | 2017-03-31 | 2023-12-26 | 株式会社力森诺科 | 密封膜、电子部件装置的制造方法及电子部件装置 |

| JP2020068237A (ja) * | 2018-10-22 | 2020-04-30 | 新光電気工業株式会社 | 配線基板 |

| JP7211757B2 (ja) | 2018-10-22 | 2023-01-24 | 新光電気工業株式会社 | 配線基板 |

| CN111370337A (zh) * | 2020-03-18 | 2020-07-03 | 深圳杰微芯片科技有限公司 | 降低封装翘曲方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7843058B2 (en) | Flip chip packages with spacers separating heat sinks and substrates | |

| KR101476883B1 (ko) | 3차원 패키징을 위한 응력 보상층 | |

| US10410969B2 (en) | Semiconductor package assembly | |

| JP2022009941A (ja) | 電子部品装置の製造方法及び電子部品装置 | |

| CN104037136B (zh) | 加强结构以及用于控制安装在衬底上的芯片翘曲的方法 | |

| KR20140026570A (ko) | 범플리스 빌드업층 패키지 휨 감소 | |

| CN101533785A (zh) | 薄tim无核高密度无凸点封装的形成方法和由此形成的结构 | |

| US11894317B2 (en) | Package structure and method for manufacturing the same | |

| CN102468245A (zh) | 半导体装置及其制造方法 | |

| JP2016012713A (ja) | 樹脂フィルム、半導体装置および半導体装置の製造方法 | |

| CN107768322A (zh) | 半导体封装结构及制造其之方法 | |

| KR102520917B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| US12033907B2 (en) | Semiconductor encapsulation material and semiconductor device | |

| TWI751331B (zh) | 半導體裝置的製造方法以及半導體裝置的中間體 | |

| JP7434794B2 (ja) | 半導体装置の製造方法及び封止用エポキシ樹脂組成物 | |

| US8906749B2 (en) | Method for fabricating a semiconductor device | |

| US20250174580A1 (en) | Semiconductor package | |

| US10410942B2 (en) | Semiconductor device package and method for manufacturing the same | |

| CN107946280B (zh) | 半导体封装 | |

| JP6461031B2 (ja) | 半導体装置の製造方法 | |

| CN222300665U (zh) | 半导体封装体 | |

| JP2012054487A (ja) | 電子装置 | |

| CN115732338A (zh) | 半导体装置的制造方法 | |

| KR101563163B1 (ko) | 내장형 기판 및 그 제조방법 | |

| JP7172022B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170313 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170313 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171004 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171017 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180410 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180611 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20181106 |