JP2016004792A - 半導体装置とその製造方法および機器 - Google Patents

半導体装置とその製造方法および機器 Download PDFInfo

- Publication number

- JP2016004792A JP2016004792A JP2014121934A JP2014121934A JP2016004792A JP 2016004792 A JP2016004792 A JP 2016004792A JP 2014121934 A JP2014121934 A JP 2014121934A JP 2014121934 A JP2014121934 A JP 2014121934A JP 2016004792 A JP2016004792 A JP 2016004792A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- electrode

- sealing resin

- lead frame

- semiconductor element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W72/884—

-

- H10W90/736—

-

- H10W90/753—

-

- H10W90/756—

Landscapes

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Lead Frames For Integrated Circuits (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Abstract

【課題】寄生インダクタンスを低減することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体装置の封止樹脂301の外縁部に段差部301bを有する凹部を形成し、封止樹脂301から露出する電極104,105を2度曲げて電極104,105の先端部を凹部内に内包させ、電極104,105を凹部から突出させないことにより、容易に、基板に実装した時の半導体装置とその他の部品との配線長を短くし、寄生インダクタンスを低減する。

【選択図】図2

【解決手段】半導体装置の封止樹脂301の外縁部に段差部301bを有する凹部を形成し、封止樹脂301から露出する電極104,105を2度曲げて電極104,105の先端部を凹部内に内包させ、電極104,105を凹部から突出させないことにより、容易に、基板に実装した時の半導体装置とその他の部品との配線長を短くし、寄生インダクタンスを低減する。

【選択図】図2

Description

本発明は、電極を備える半導体装置とその製造方法、半導体装置を搭載した機器に関する。

従来の電力変換装置に利用される半導体装置としては、リードフレームと絶縁層、放熱板を組み合わせたものがある(例えば、特許文献1参照)。図9は、特許文献1に記載された従来の半導体装置を示す図である。

図9において、リードフレーム901には複数の半導体素子903が搭載されており、これらはアルミ線904によって電気的に接続されている。リードフレーム901の半導体素子903が搭載されていない方の面には絶縁層905が形成され、放熱板906とリードフレーム901とを接着している。半導体装置全体は、封止樹脂908で覆われているが、放熱板906の一部を露出させることで良好な放熱性能を持たせている。外部との電気的な接続は、パワー系入出力リード907と、制御信号入力リード902によって行われる。

また、従来の半導体装置として、金属ブロックを使用したものもある(例えば、特許文献2参照)。図10は、特許文献2に記載された従来の半導体装置を示す図である。

図10において、半導体素子1002は、ベース部1001に搭載されて、金属ブロック1003を介してソース端子1004に接続されている。ゲート端子1005はアルミ線などを用いて半導体素子1002に接続されている。

図10において、半導体素子1002は、ベース部1001に搭載されて、金属ブロック1003を介してソース端子1004に接続されている。ゲート端子1005はアルミ線などを用いて半導体素子1002に接続されている。

しかしながら、図9の構成では、半導体装置の直上にプリント配線板を配置する際、半導体装置の側面から出て上側に突出する制御信号入力リード902とプリント配線板とを接続するために、プリント配線板にスルーホールが必要である。また、スルーホールに制御信号入力リード902を通して接続する構成のため、制御用ICやノイズ抑制用スナバコンデンサをスルーホールの直近に配置することは困難である。そのため、図9の構成では、半導体素子903から制御用ICやノイズ抑制用スナバコンデンサまでの配線は、ある程度長くなってしまうことが多い。配線が長くなると配線上の寄生インダクタンスが大きくなるため、半導体装置を高速動作させた際に、半導体装置自身に誤動作が発生する可能性や、大きなノイズが発生する可能性がある。

ここで、図9の構成の代わりに、制御信号入力リード902をJの形状に曲げるなどの構成を採用すれば、スルーホールなしに制御信号入力リード902をプリント配線板に接続することも可能である。だが、この構成では、半導体装置をヒートシンクなどの冷却装置に取り付けた際に、リードとプリント配線板との接合部に過大な力がかかり、信頼性が低下する可能性がある。

また、図10の構成では、ソース端子1004が平坦な形状であることからソース側の配線の寄生インダクタンスを小さくすることができるが、ゲート端子1005のリードが半導体装置の側面から出ているため、ゲート側の配線をスルーホール実装工法で実装する必要があり、制御用ICまでのゲート側の配線は長いままである。

本発明は、これら前記従来の課題を解決するもので、寄生インダクタンスを容易に低減することが可能な半導体装置および製造方法、機器を提供することを目的とする。

上記目的を達成するために、本発明の半導体装置は、半導体素子搭載領域および電極を備えるリードフレームと、前記半導体素子搭載領域に搭載された半導体素子と、前記半導体素子と前記電極とを電気的に接続する電気配線部と、前記半導体素子および前記電気配線部を樹脂封止する封止樹脂と、を有し、前記電極には、前記封止樹脂から露出する部分に設けられた曲げ部により前記封止樹脂の表面にその先端のはんだ接合部が露出したはんだ接合部が設けられ、前記封止樹脂には、その一面に形成されると共に前記電極の前記はんだ接合部を収容する凹部が設けられ、前記電極の先端の前記はんだ接合部の厚みは、前記凹部の深さより薄いことを特徴とする。

また、本発明の半導体装置の製造方法は、電極を備えるリードフレームに半導体素子を搭載する工程と、前記電極と前記半導体素子とを電気配線部で電気的に接続する工程と、前記半導体素子および前記電気配線部を封止樹脂で樹脂封止すると共に前記封止樹脂の一面に凹部を形成する工程と、前記封止樹脂から露出する前記電極に曲げ部を形成して前記電極の先端を前記凹部内に収容する工程と、を有することを特徴とする。

以上のように、本発明によれば、寄生インダクタンスを容易に低減することが可能な半導体装置および製造方法、機器を提供することができる。

以下、本発明の実施の形態について、図面を参照しながら説明する。なお、以下の説明において、同じ構成には同じ符号を付けて、適宜説明を省略している。

(実施の形態1)

図1は本発明の実施の形態1における半導体装置の構成を示す図である。図1(a)は本発明の実施の形態1における半導体装置の上面図を、図1(b)は同じく底面図を、図1(c)は側面図を、それぞれ示している。

(実施の形態1)

図1は本発明の実施の形態1における半導体装置の構成を示す図である。図1(a)は本発明の実施の形態1における半導体装置の上面図を、図1(b)は同じく底面図を、図1(c)は側面図を、それぞれ示している。

本実施の形態の半導体装置1104は、図1(a)および図1(c)で示すように、平板状であり、その一面(上面)に正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105が露出している。正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105は、銅もしくは銅を主体とした合金であることが望ましいが、他の材料でもよい。

図1(b)に示すように、他面(底面)には放熱板201が露出しており、封止樹脂301と共に、平面を成している。

半導体装置全体は封止樹脂301で封止されているが、半導体装置1104の上面において、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105は、封止樹脂301に覆われておらず露出している。封止樹脂301は、エポキシ樹脂、シリコーン樹脂から選択でき、必要に応じてフィラーを含有していてもよい。

半導体装置全体は封止樹脂301で封止されているが、半導体装置1104の上面において、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105は、封止樹脂301に覆われておらず露出している。封止樹脂301は、エポキシ樹脂、シリコーン樹脂から選択でき、必要に応じてフィラーを含有していてもよい。

正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105は、封止樹脂301の側面から突き出ていて、封止樹脂301の外部において90°の曲げが2箇所に施されて、封止樹脂301の一方の面である上面(放熱板201が露出する面に対する反対の面)を部分的に覆うように配置されている。なお、各曲げは、曲げる角度が90°ずつである場合に限らず、100°と80°等、2回に分けて合計180°になるように曲げても良いが、90°で2回曲げた場合が最も実装面積を小さくすることができ、好ましい。

図1(a),図1(c)に示すように、封止樹脂301には、一方の面である上面に、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105が覆うエリアのみが部分的に凹構造となるように、段差部301bが設けられている。段差部301bは、凹部の一例である。つまり、本実施の形態の半導体装置は、一方の面である封止樹脂301の上面の外周周辺に、電極の配置位置に応じて凹構造である段差部301bが形成されている。この段差部301bによる部分的な凹構造内に各電極101〜105の先端であるはんだ接合部106を収容することによって、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105を、封止樹脂301の凹部周辺の表面から突出させずに配置することができる。

なお、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105の厚みは例えば0.4〜1mmであるため、封止樹脂301の段差部301bの深さ301cは、電極101〜105の厚みに加えて、隙間50μm以上かつ500μm以下の範囲で深くすることが好ましい。例えば、図1(c)に示す段差部301bの深さ301cは、電極の厚み600μmに隙間200μmを加えた800μmである。

段差部301bにおける50μm以上かつ500μm以下の隙間は、後述する電力変換装置等の機器を組み立てる工程において、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105上の各はんだ接合部106の上に形成されるはんだ接合層の厚みを一定程度に確保するために有効である。それと共に、段差部301bにおける隙間は、後述のように、半導体装置の固定のために加えられる応力の大半を、封止樹脂301の最も大きな面積を占める段差部301b以外の部分に逃がすことで、はんだ接合層に加わる応力を低減するために有効である。

なお、ここでの説明では、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105を用いて説明したが、電極は半導体装置に応じて様々なものを用いることができ、その個数も任意である。

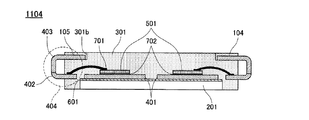

図2は本発明の実施の形態1における半導体装置の断面図であり、図1(a)の一点鎖線で示したA−A’断面図である。図2は、図1(a)における、正極側制御電極104と負極側制御電極105を通る平面を示している。

図2に示すように、半導体装置の内部において、半導体素子501は、リードフレーム401の一方の面の半導体素子搭載部に、半導体素子接合材料702を介して搭載されている。半導体素子接合材料702は、例えば、はんだなどの金属材料、または、銀ペーストなどの樹脂材料である。リードフレーム401の半導体素子搭載部の反対側の面には、絶縁樹脂601を介して放熱板201が接着されている。半導体素子501は、電気配線部701によって、リードフレーム401に電気的に接続されている。電気配線部701は、例えば、アルミニウム、銅、金もしくはそれらの合金材料でできたワイヤーや、銅クリップである。電気配線部701がワイヤーの場合は、超音波接合もしくは熱圧着によって電気配線部701を接合する。電気配線部701が銅クリップの場合は、はんだか導電性ペーストによって電気配線部701を接合する。

封止樹脂301は、少なくとも半導体素子501と電気配線部701を封止し、リードフレーム401の電極部のリードフレーム曲げ部404より先および放熱板201の裏面を露出するように、リードフレーム401および放熱板201を保持する。前述のように、封止樹脂301には、正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105の近傍に、封止樹脂301の段差部301bが設けられている。段差部301bは、上述した正極電極101、負極電極102、出力電極103、正極側制御電極104、負極側制御電極105が覆うエリアのみが部分的に凹となる構造を形成するために設けられている。

リードフレーム401は、複数のリードフレーム曲げ部404を有している。リードフレーム曲げ部404は、リードフレーム401の一部であり、それぞれ封止樹脂301の側面から外部に突き出している。リードフレーム曲げ部404は、半導体素子501が搭載された面側に180°折り返されており、図2に示すように、リードフレーム401自身の一部を覆うように曲げられている。リードフレーム曲げ部404は、第1のリードフレーム曲げ部402と、第2のリードフレーム曲げ部403を有しており、2度の曲げにより、合計して180°折り曲げられる。これにより、封止樹脂301から露出したリードフレーム401の一部は、正極側制御電極104と負極側制御電極105をなしている。なお、正極電極101、負極電極102、出力電極103も、正極側制御電極104および負極側制御電極105と同様の構造である。

図3は、本発明の実施の形態1における半導体装置の正極側制御電極104(図2参照)に係るリードフレーム曲げ部の構成を示す要部概略斜視図である。

図2,図3に示すように、リードフレーム曲げ部404は、第1のリードフレーム曲げ部402と、第2のリードフレーム曲げ部403を有しており、それぞれの曲げ部で90°曲げられている。図3に示すように、第1のリードフレーム曲げ部402と第2のリードフレーム曲げ部403は、平面的には、ずれた位置に配置される。つまり、リードフレーム曲げ部404を伸ばした際に、電気配線部701が接続される部分から第1のリードフレーム曲げ部402に至る部分と、はんだ接合部106から第2のリードフレーム曲げ部403に至る部分とは、直線状に連続せず、ずれて配置されている。言い換えれば、正極側制御電極104のはんだ接合部106は、第1のリードフレーム曲げ部402の上部以外の位置に形成されている。このような構成とすることで、それぞれの曲げ部で90°以上の曲げを行っても、電気配線部701と正極側制御電極104が接触しない構成を実現できる。

図2,図3に示すように、リードフレーム曲げ部404は、第1のリードフレーム曲げ部402と、第2のリードフレーム曲げ部403を有しており、それぞれの曲げ部で90°曲げられている。図3に示すように、第1のリードフレーム曲げ部402と第2のリードフレーム曲げ部403は、平面的には、ずれた位置に配置される。つまり、リードフレーム曲げ部404を伸ばした際に、電気配線部701が接続される部分から第1のリードフレーム曲げ部402に至る部分と、はんだ接合部106から第2のリードフレーム曲げ部403に至る部分とは、直線状に連続せず、ずれて配置されている。言い換えれば、正極側制御電極104のはんだ接合部106は、第1のリードフレーム曲げ部402の上部以外の位置に形成されている。このような構成とすることで、それぞれの曲げ部で90°以上の曲げを行っても、電気配線部701と正極側制御電極104が接触しない構成を実現できる。

図8は本発明の半導体装置の製造工程に係るフローチャートを示す図である。図4,図5は本発明の半導体装置の製造工程を順に示す断面図である。

まず、図4(a)に示すとおり、リードフレーム401を準備する。

まず、図4(a)に示すとおり、リードフレーム401を準備する。

次に、図4(b)に示すとおり、図8のダイボンド工程(ステップ1)を行う。このダイボンド工程では、半導体素子501を搭載する。ここでは、半導体素子501としてトランジスターとダイオードを1対として、正極側、負極側にそれぞれ1つずつ配置しているが、個数、種類を限定するものではない。

次に、図4(c)に示すとおり、図8のワイヤリング工程(ステップ2)を行う。このワイヤリング工程では、電気配線部701によって、半導体素子501とリードフレーム401を電気的に接続する。

次に、図4(d),図5(a),図5(b)に示すとおり、図8の封止工程(ステップ3)を行う。図4(d)に示すように、まず、封止金型801の中に、ワイヤリング工程(ステップ2)までの工程で組み立てた物と、あらかじめ絶縁樹脂601を貼り付けた放熱板201を配置する。次に、図5(a)に示すように、封止金型801を閉じ、未硬化状態の封止樹脂301aを圧入する。次に、図5(b)に示すように、封止金型801を開き、一定温度で封止樹脂301を硬化させる。このとき、封止金型801の表面形状に合わせて、封止樹脂301には段差部301bが形成されている。

次に、図5(c)に示すとおり、図8のカット工程(ステップ4)およびリードフレーム曲げ工程1(ステップ5)を行う。これらの工程では、余分なリードフレームをカット(切断)して、残ったリードフレームを曲げて第1のリードフレーム曲げ部402を形成する。

次に、図5(d)に示すとおり、図8のリードフレーム曲げ工程2(ステップ6)を行う。この工程では、さらにリードフレームを曲げて第2のリードフレーム曲げ部403を形成する。本実施の形態では、このように第1のリードフレーム曲げ部402および第2のリードフレーム曲げ部403を形成することで、半導体装置1104を製造する。

従来、リードフレームは、90°を超えた曲げ部を形成することが困難で、SOJパッケージなどに見られるように、リードフレームの先端をJ形状にして封止樹脂をごく一部覆う程度の曲げしかできなかった。そこで、本発明では、リードフレーム401を曲げる箇所を、第1のリードフレーム曲げ部402および第2のリードフレーム曲げ部403の2箇所に分けることで、リードフレームを180°折り返すことを可能とした。

図6は本発明の半導体装置を利用した電力変換装置の組立工程を順に示す断面図、図7は本発明の半導体装置を利用した電力変換装置の組立工程を示す平面図である。

図6(a)に、第1の工程であるはんだペースト印刷工程を示す。本工程では、予めスナバコンデンサ1103などの周辺部品を実装しておいたプリント配線板1101を準備し、はんだペースト1102を印刷する。はんだペースト1102の印刷にはメタルマスクを用いた印刷工法、ディスペンサを用いた塗布工法などが選択できる。

図6(a)に、第1の工程であるはんだペースト印刷工程を示す。本工程では、予めスナバコンデンサ1103などの周辺部品を実装しておいたプリント配線板1101を準備し、はんだペースト1102を印刷する。はんだペースト1102の印刷にはメタルマスクを用いた印刷工法、ディスペンサを用いた塗布工法などが選択できる。

図6(b)に、第2の工程である半導体装置搭載工程を示す。第1の工程で印刷したはんだペースト1102の上に、本発明の半導体装置1104を搭載する。このとき、段差部301bには前述の隙間が設けられており、半導体装置1104の電極101〜105は封止樹脂301の表面よりもやや凹となっているために、はんだが過剰につぶれることなく、適切な厚みを確保できる。

その後、第3の工程であるリフロー工程によって、はんだペースト1102を溶融させ、プリント配線板1101と半導体装置1104との接続は完了する。このとき、第2の工程でも述べたように、段差部301bの隙間により、半導体装置1104の電極101〜105は封止樹脂301の表面よりもやや凹となっているために、はんだが溶融した際に、半導体装置1104の重みによってはんだがつぶれ過ぎるのを抑制することができる。また、封止樹脂301の表面より凹んだはんだ接合部106において接合されることで、プリント配線板1101と半導体装置1104の封止樹脂301とが、直接、接した状態とすることもできる。

図6(c)に、第4の工程であるヒートシンク取付工程を示す。図6(c)に示すように、固定板1105およびボルト1106、ヒートシンク1107を準備し、第3の工程までで組み立てた半導体装置1104およびプリント配線板1101を、ヒートシンク1107上に載置し、ボルト1106等の固定具で固定し、スナバコンデンサ1103を配置する。このとき、第3の工程でプリント配線板1101と半導体装置1104の封止樹脂とが、直接、接した状態となっているため、ボルト1106と固定板1105によって半導体装置1104に加えられる応力は、半導体装置1104の封止樹脂301が受ける形となり、はんだ接合部106に過剰な負荷がかからない。このように、段差部301bに隙間を設けることで、はんだのクラック発生などの信頼性に対する影響を抑えることができる。

図7に、組み立て後の平面図を示す。図7は、半導体装置1104の搭載面に対する裏面側から見た図である。図7により、本実施の形態では、スナバコンデンサ1103が半導体装置1104の直上に配置可能であることがわかる。このように、本実施の形態は、半導体装置1104とスナバコンデンサ1103との配線長を短くすることができ、配線上の寄生インダクタンスが小さくなり、ノイズ抑制を効果的に行うことができる。

なお、以上の説明においては、インバータ等の半導体装置とスナバコンデンサを搭載した電力変換装置を例に説明したが、様々な半導体装置と電子部品等の部品を基板に実装し、ヒートシンクを搭載した電子機器等の機器に用いることも可能である。

本発明は、容易に、寄生インダクタンスを低減することができ、電極を備える半導体装置とその製造方法、半導体装置を搭載した機器等に有用である。

101 正極電極

102 負極電極

103 出力電極

104 正極側制御電極

105 負極側制御電極

106 はんだ接合部

201、906 放熱板

301、301a、908 封止樹脂

301b 段差部

301c 深さ

401、901 リードフレーム

402 第1のリードフレーム曲げ部

403 第2のリードフレーム曲げ部

404 リードフレーム曲げ部

501、903、1002 半導体素子

601 絶縁樹脂

701 電気配線部

702 半導体素子接合材料

801 封止金型

902 制御信号入力リード

904 アルミ線

905 絶縁層

907 パワー系入出力リード

1001 ベース部

1003 金属ブロック

1004 ソース端子

1005 ゲート端子

1101 プリント配線板

1102 はんだペースト

1103 スナバコンデンサ

1104 半導体装置

1105 固定板

1106 ボルト

1107 ヒートシンク

102 負極電極

103 出力電極

104 正極側制御電極

105 負極側制御電極

106 はんだ接合部

201、906 放熱板

301、301a、908 封止樹脂

301b 段差部

301c 深さ

401、901 リードフレーム

402 第1のリードフレーム曲げ部

403 第2のリードフレーム曲げ部

404 リードフレーム曲げ部

501、903、1002 半導体素子

601 絶縁樹脂

701 電気配線部

702 半導体素子接合材料

801 封止金型

902 制御信号入力リード

904 アルミ線

905 絶縁層

907 パワー系入出力リード

1001 ベース部

1003 金属ブロック

1004 ソース端子

1005 ゲート端子

1101 プリント配線板

1102 はんだペースト

1103 スナバコンデンサ

1104 半導体装置

1105 固定板

1106 ボルト

1107 ヒートシンク

Claims (7)

- 半導体素子搭載領域および電極を備えるリードフレームと、

前記半導体素子搭載領域に搭載された半導体素子と、

前記半導体素子と前記電極とを電気的に接続する電気配線部と、

前記半導体素子および前記電気配線部を樹脂封止する封止樹脂と、を有し、

前記電極には、前記封止樹脂から露出する部分に設けられた曲げ部により前記封止樹脂の表面にその先端のはんだ接合部が露出したはんだ接合部が設けられ、

前記封止樹脂には、その一面に形成されると共に前記電極の前記はんだ接合部を収容する凹部が設けられ、

前記電極の先端の前記はんだ接合部の厚みは、前記凹部の深さより薄い、

半導体装置。 - 前記封止樹脂の他面にその一部が露出した放熱板をさらに有し、

前記凹部と、2つの前記曲げ部による前記電極の先端の前記はんだ接合部とは、前記放熱板が露出する面の反対の面に配置された、

請求項1記載の半導体装置。 - 前記曲げ部が2つである、

請求項1又は2記載の半導体装置。 - 2つの前記曲げ部が、それぞれ90°曲げられた、

請求項3記載の半導体装置。 - 1つの前記電極における2つの前記曲げ部は、前記封止樹脂の一面の前記曲げ部に最も近い外周辺と平行な方向にずれて設けられた、

請求項4記載の半導体装置。 - 基板と、前記基板の表面に実装された請求項1から5の何れか記載の半導体装置と、を有し、

前記半導体装置は、前記電極において前記基板にはんだで表面実装され、

前記凹部の周辺の前記封止樹脂は、前記基板と接する、

機器。 - 電極を備えるリードフレームに半導体素子を搭載する工程と、

前記電極と前記半導体素子とを電気配線部で電気的に接続する工程と、

前記半導体素子および前記電気配線部を封止樹脂で樹脂封止すると共に前記封止樹脂の一面に凹部を形成する工程と、

前記封止樹脂から露出する前記電極に曲げ部を形成して前記電極の先端を前記凹部内に収容する工程と、を有する、

半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014121934A JP2016004792A (ja) | 2014-06-13 | 2014-06-13 | 半導体装置とその製造方法および機器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014121934A JP2016004792A (ja) | 2014-06-13 | 2014-06-13 | 半導体装置とその製造方法および機器 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2016004792A true JP2016004792A (ja) | 2016-01-12 |

Family

ID=55223908

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014121934A Pending JP2016004792A (ja) | 2014-06-13 | 2014-06-13 | 半導体装置とその製造方法および機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2016004792A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110137087A (zh) * | 2018-02-08 | 2019-08-16 | 浙江清华柔性电子技术研究院 | 导热封装结构的制作方法及可穿戴设备 |

| CN112514058A (zh) * | 2018-08-02 | 2021-03-16 | 三菱电机株式会社 | 半导体模块 |

| JP7609615B2 (ja) | 2020-11-30 | 2025-01-07 | 新電元工業株式会社 | 電子モジュール |

-

2014

- 2014-06-13 JP JP2014121934A patent/JP2016004792A/ja active Pending

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110137087A (zh) * | 2018-02-08 | 2019-08-16 | 浙江清华柔性电子技术研究院 | 导热封装结构的制作方法及可穿戴设备 |

| CN110137142A (zh) * | 2018-02-08 | 2019-08-16 | 浙江清华柔性电子技术研究院 | 导热封装结构、制作方法及具有其的可穿戴设备 |

| CN112514058A (zh) * | 2018-08-02 | 2021-03-16 | 三菱电机株式会社 | 半导体模块 |

| CN112514058B (zh) * | 2018-08-02 | 2024-04-09 | 三菱电机株式会社 | 半导体模块 |

| JP7609615B2 (ja) | 2020-11-30 | 2025-01-07 | 新電元工業株式会社 | 電子モジュール |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7441287B2 (ja) | 半導体装置 | |

| JP5802695B2 (ja) | 半導体装置、半導体装置の製造方法 | |

| US20180233439A1 (en) | Semiconductor chip package having heat dissipating structure | |

| KR101388857B1 (ko) | 반도체 패키지 및 반도체 패키지 제조 방법 | |

| TW201546914A (zh) | 基板及其製造方法 | |

| WO2012108011A1 (ja) | パワー半導体モジュール | |

| JP7210868B2 (ja) | 半導体装置 | |

| JPH09260550A (ja) | 半導体装置 | |

| KR102228945B1 (ko) | 반도체 패키지 및 이의 제조방법 | |

| CN103972277B (zh) | 半导体装置及其制造方法 | |

| JP2012199436A (ja) | 半導体装置及びその製造方法 | |

| JP6129355B2 (ja) | 電力半導体装置 | |

| JP2016004792A (ja) | 半導体装置とその製造方法および機器 | |

| JP5172290B2 (ja) | 半導体装置 | |

| JP2010245468A (ja) | モールドパッケージの実装構造および実装方法 | |

| JP2021082794A (ja) | 電子部品および電子装置 | |

| JP2019050297A (ja) | 半導体装置 | |

| JP2016092261A (ja) | 電子制御装置およびその製造方法 | |

| KR20150039402A (ko) | 외부접속단자부, 이를 이용한 반도체 패키지 및 그 제조 방법 | |

| JP2007027404A (ja) | 半導体装置 | |

| JP2012227229A (ja) | 半導体装置 | |

| JP4435050B2 (ja) | 半導体装置 | |

| JP2017069351A (ja) | 半導体装置 | |

| WO2015052880A1 (ja) | 半導体装置及びその製造方法 | |

| JP2005228811A (ja) | 半導体装置 |