JP2014505909A - 電源、メモリ、相互接続、及びledに関連する小型化技法、システム、及び装置 - Google Patents

電源、メモリ、相互接続、及びledに関連する小型化技法、システム、及び装置 Download PDFInfo

- Publication number

- JP2014505909A JP2014505909A JP2013514252A JP2013514252A JP2014505909A JP 2014505909 A JP2014505909 A JP 2014505909A JP 2013514252 A JP2013514252 A JP 2013514252A JP 2013514252 A JP2013514252 A JP 2013514252A JP 2014505909 A JP2014505909 A JP 2014505909A

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- memory

- led

- active component

- color

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000015654 memory Effects 0.000 title claims abstract description 180

- 238000000034 method Methods 0.000 title abstract description 64

- 230000007334 memory performance Effects 0.000 claims abstract description 8

- 230000008878 coupling Effects 0.000 claims description 10

- 238000010168 coupling process Methods 0.000 claims description 10

- 238000005859 coupling reaction Methods 0.000 claims description 10

- 239000000758 substrate Substances 0.000 claims description 10

- 239000004020 conductor Substances 0.000 claims description 8

- 229910000679 solder Inorganic materials 0.000 claims description 6

- 239000003365 glass fiber Substances 0.000 claims description 4

- 238000009413 insulation Methods 0.000 claims 1

- 238000012545 processing Methods 0.000 description 43

- 230000000670 limiting effect Effects 0.000 description 38

- 238000013461 design Methods 0.000 description 35

- 239000003990 capacitor Substances 0.000 description 28

- 239000000463 material Substances 0.000 description 28

- 230000006870 function Effects 0.000 description 22

- 239000003086 colorant Substances 0.000 description 20

- 239000004065 semiconductor Substances 0.000 description 20

- 230000002829 reductive effect Effects 0.000 description 15

- 230000008901 benefit Effects 0.000 description 13

- 238000003860 storage Methods 0.000 description 13

- 230000003071 parasitic effect Effects 0.000 description 12

- 238000004519 manufacturing process Methods 0.000 description 10

- 230000004397 blinking Effects 0.000 description 8

- WBTMFEPLVQOWFI-UHFFFAOYSA-N 1,3-dichloro-5-(2,5-dichlorophenyl)benzene Chemical compound ClC1=CC=C(Cl)C(C=2C=C(Cl)C=C(Cl)C=2)=C1 WBTMFEPLVQOWFI-UHFFFAOYSA-N 0.000 description 7

- 238000004891 communication Methods 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 230000002093 peripheral effect Effects 0.000 description 6

- 238000005476 soldering Methods 0.000 description 6

- RPPNJBZNXQNKNM-UHFFFAOYSA-N 1,2,4-trichloro-3-(2,4,6-trichlorophenyl)benzene Chemical compound ClC1=CC(Cl)=CC(Cl)=C1C1=C(Cl)C=CC(Cl)=C1Cl RPPNJBZNXQNKNM-UHFFFAOYSA-N 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 230000035939 shock Effects 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 238000005286 illumination Methods 0.000 description 4

- 230000000007 visual effect Effects 0.000 description 4

- 229910001369 Brass Inorganic materials 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 238000001994 activation Methods 0.000 description 3

- 239000010951 brass Substances 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- HCWZEPKLWVAEOV-UHFFFAOYSA-N 2,2',5,5'-tetrachlorobiphenyl Chemical compound ClC1=CC=C(Cl)C(C=2C(=CC=C(Cl)C=2)Cl)=C1 HCWZEPKLWVAEOV-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- FTWRSWRBSVXQPI-UHFFFAOYSA-N alumanylidynearsane;gallanylidynearsane Chemical compound [As]#[Al].[As]#[Ga] FTWRSWRBSVXQPI-UHFFFAOYSA-N 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 150000003071 polychlorinated biphenyls Chemical class 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- CRCBRZBVCDKPGA-UHFFFAOYSA-N 1,2,5-trichloro-3-(2,5-dichlorophenyl)benzene Chemical compound ClC1=CC=C(Cl)C(C=2C(=C(Cl)C=C(Cl)C=2)Cl)=C1 CRCBRZBVCDKPGA-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 230000003044 adaptive effect Effects 0.000 description 1

- 230000004075 alteration Effects 0.000 description 1

- RNQKDQAVIXDKAG-UHFFFAOYSA-N aluminum gallium Chemical compound [Al].[Ga] RNQKDQAVIXDKAG-UHFFFAOYSA-N 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000011960 computer-aided design Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000001627 detrimental effect Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005672 electromagnetic field Effects 0.000 description 1

- 238000005265 energy consumption Methods 0.000 description 1

- 238000004146 energy storage Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000005755 formation reaction Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000006855 networking Effects 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 230000001902 propagating effect Effects 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000012163 sequencing technique Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 230000011664 signaling Effects 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 238000001429 visible spectrum Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/10—Distribution of clock signals, e.g. skew

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/18—Packaging or power distribution

- G06F1/183—Internal mounting support structures, e.g. for printed circuit boards, internal connecting means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/18—Packaging or power distribution

- G06F1/183—Internal mounting support structures, e.g. for printed circuit boards, internal connecting means

- G06F1/188—Mounting of power supply units

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B47/00—Circuit arrangements for operating light sources in general, i.e. where the type of light source is not relevant

- H05B47/10—Controlling the light source

- H05B47/175—Controlling the light source by remote control

- H05B47/18—Controlling the light source by remote control via data-bus transmission

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/181—Printed circuits structurally associated with non-printed electric components associated with surface mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

- H05K1/113—Via provided in pad; Pad over filled via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10431—Details of mounted components

- H05K2201/10507—Involving several components

- H05K2201/10545—Related components mounted on both sides of the PCB

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Human Computer Interaction (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Sources (AREA)

- Led Device Packages (AREA)

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

- Details Of Connecting Devices For Male And Female Coupling (AREA)

- Combinations Of Printed Boards (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

Abstract

Description

本願は、「MINITURIZATION TECHNIQUES,SYSTEMS,AND APPARATUS RELATING TO POWER SUPPLIES,MEMORY,INTERCONNECTIONS,AND LEDS」という名称で2011年6月3日に出願された米国特許出願第13/153,224号明細書並びに以下の仮特許出願:「MINITURIZED POWER SUPPLY」という名称で2010年6月7日に出願された米国仮出願第61/352,359号明細書、「SYSTEMS AND METHODS FOR OPTIMIZING MEMORY PERFORMANCE」という名称で2010年6月7日に出願された米国仮出願第61/352,349号明細書、「SYSTEMS AND METHODS FOR PROVIDING A PIN GRID ARRAY TO BALL GRID ARRAY ADAPTOR」という名称で2010年6月7日に出願された米国仮出願第61/352,369号明細書、「SYSTEMS AND METHODS FOR ACTIVATING MULTI−COLOR LIGHT EMITTING DIODES」という名称で2010年6月7日に出願された米国仮出願第61/352,378号明細書の利益を主張するものであり、これらの特許出願及び仮特許出願を参照により本明細書に援用する。

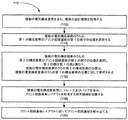

図1及び対応する考察は、本発明の実施形態による適した動作環境の概説を提供することを目的とする。さらに後述するように、本発明の実施形態は、後述するように、ネットワーク化された構成又は結合構成を含め、様々なカスタマイズ可能な企業構成での1つ又は複数の動的モジュラー処理ユニットの使用を含む。

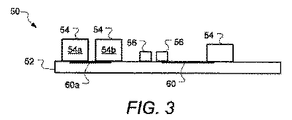

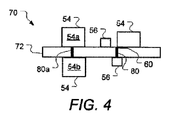

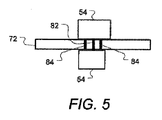

本発明のいくつかの態様は電源に関する。上述したように、多くの従来の電源設計は多くの場合、あまり空間効率的ではない。電源は、複数の電子構成要素を含むことができ、これらの電子構成要素は能動的構成要素及び受動的構成要素を含むことができる。能動的構成要素は、スイッチ(例えば、双極トランジスタ、電界効果トランジスタ等)、調整器、比較器等の部品を含む。受動的構成要素は、抵抗、インダクタ、コンデンサ等の部品を含む。電子構成要素は通常PCBに搭載され、PCB上のトレースを通して相互接続される。通常、電子構成要素はPCBの片側のみに搭載される。これは、電子産業ではコスト考慮事項から望ましいと見られている。いくつかの場合、受動的構成要素(例えば、小型コンデンサ又は小型抵抗)は往々にして、基板の逆側に配置される。例えば、図3は、全体的に50で示される電源を示し、PCB52は、PCB(又は他の回路基板)の片側58に搭載された複数の構成要素54及び56を有する。構成要素は、能動的構成要素54及び受動的構成要素56を含むことができる。構成要素の相互接続はトレース60(例えば、非導電基板に取り付けられるか、又は堆積した導電材料)により提供される。PCBは、例えば、複数層のトレース(図示せず)を提供する多層PCBであることができる。

本発明のいくつかの態様は、コンピュータ装置又はシステムでのメモリ性能を最適化するシステム及び方法に関する。さらに、本発明のいくつかの態様は、回路基板上のメモリレイアウトを小型化し最適化するシステム及び方法に関する。

本発明のいくつかの態様はICコネクタに関する。特に、本発明のいくつかの態様は、IC(例えば、CPU)を回路基板(例えば、PCB)に取り付けることができるPGA−BGAアダプタに関する。記載されるPGA−BGAアダプタは、はんだBGAを使用して、PGAを備えたIC素子を回路基板に電気的且つ物理的に接続できるようにする任意の適した構成要素を備えることができる。非限定的な例として、図13は、PGA−BGAアダプタ210がケース212と、機械加工ピンソケット216の配列214とを備える代表的な実施形態を示す。記載されるアダプタのよりよい理解を提供するために、上述した各構成要素について以下により詳細に説明する。

上述したように、本発明の少なくともいくつかの態様はLED回路に関する。実際には、本発明のいくつかの実施形態は、LEDがLEDの構成要素材料によって決まる別個の各色を、ユーザが望む情報又はユーザにより定義される状態の視覚的表現又は表示として発することが可能なように電気的に接続された2色LED又は3色LED等の少なくとも1つのマルチカラーLEDに関連して行われる。少なくとも1つの実施形態では、2色LED電気インジケータシステムは2色LEDを含む。そのような実施形態では、LEDは2つの色:一方向での電流の流れによる第1の色及び逆方向での電流の流れによる第2の色を発することが可能である。すべてのダイオードと同様に、2色LEDは2つのリード又は電気端子を含む。しかし、電流が一方向に流れる場合、適切なダイオードに対して、一方のリードは陰極として挙動し、その間、他方のリードは陽極として挙動する。電流が逆になると、他方のダイオードに対して、前は陰極であったリードは陽極として挙動し、前は陽極であったリードは陰極として挙動する。

Claims (20)

- 小型化された電源であって、

プリント回路基板と、

前記プリント回路基板の第1の側に配置される第1の能動的構成要素と、

前記プリント回路基板の第2の側に配置される第2の能動的構成要素であって、前記第2の側は前記第1の側と異なり、前記第2の能動的構成要素は前記第1の能動的構成要素に電気的に接続される、第2の能動的構成要素と、

を備える、電源。 - 前記第1の能動的構成要素及び前記第2の能動的構成要素は、互いの(each other)真逆(directly opposite)に配置される、請求項1に記載の電源。

- 前記第1の能動的構成要素及び前記第2の能動的構成要素は、互いの真逆に配置されて、互いに部分的にのみ重なる、請求項1に記載の電源。

- 前記第1の能動的構成要素及び前記第2の能動的構成要素は、バイアを用いて(with a via)互いに電気的に接続される、請求項1に記載の電源。

- 前記第1の能動的構成要素と前記第2の能動的構成要素との間のトレース長(trace length)は、前記プリント回路基板の厚さにほぼ等しい、請求項1に記載の電源。

- 前記第1の能動的構成要素及び前記第2の能動的構成要素は、遮蔽接続(shielded connection)を通して互いに電気的に接続される、請求項1に記載の電源。

- 前記遮蔽接続は、信号導体(signal conductor)及び複数の遮蔽構造を備える、請求項6に記載の電源。

- 前記プリント回路基板の前記第1及び第2の側のそれぞれで約2.5cm2未満を占める、請求項1に記載の電源。

- 最適化されたメモリ性能を有するシステムであって、

上側及び下側を有する回路基板と、

前記回路基板に結合されるメモリコントローラと、

前記回路基板に直接はんだ付けされる(soldered)複数のメモリ素子であって、前記メモリ素子のそれぞれは、前記メモリコントローラの約6.4cm以内に配置され、前記メモリ素子の第1の部分は前記回路基板の前記上側に配置され、前記メモリ素子の第2の部分は前記回路基板の前記下側に配置される、複数のメモリ素子と、

システムクロックと、

前記複数のメモリ素子を前記システムクロックに結合する、ほぼ等距離の2つ以上のクロック線と、

前記メモリ素子のそれぞれを前記メモリコントローラに結合する複数のデータ線と、

を備える、システム。 - 前記メモリ素子のそれぞれの部分は、前記メモリコントローラの約6.4cm以内である、請求項9に記載のシステム。

- 前記メモリ素子のそれぞれは全体的に、前記メモリコントローラの約6.4cm以内である、請求項9に記載のシステム。

- インタポーザであって、

剛性絶縁ケースと、

前記絶縁ケース内に配置される機械加工ピンソケット(pin socket)配列(array)であって、前記機械加工ピンソケット配列内の複数のソケットのそれぞれは、前記絶縁ケースの第1の表面から開くピンレセプタクルを備え、前記複数のソケットのそれぞれは、前記ケースの第2の表面に配置されるはんだ玉を備える、機械加工ピンソケット配列と、

を備える、インタポーザ。 - 前記複数のソケットのそれぞれは、少なくとも2つの内部フィンガ接点を備える、請求項12に記載のインタポーザ。

- 前記複数のソケットのそれぞれは3〜10個のフィンガ接点を備える、請求項12に記載のインタポーザ。

- 前記内部フィンガ接点は弾性を有する、請求項13に記載のインタポーザ。

- 前記絶縁ケースは、約1mm〜約8mmの厚さを有するガラス繊維基板を備える、請求項12に記載のインタポーザ。

- 前記機械加工ピンソケット配列は、適切な向きで集積回路を受けるように適合される、請求項12に記載のインタポーザ。

- 前記インタポーザのフットプリントのサイズは、前記インタポーザに接続する集積回路のフットプリントのサイズにほぼ等しい、請求項12に記載のインタポーザ。

- 前記インタポーザは、プリント回路基板の第1の側に電気的に結合され、前記インタポーザに直接電気的に接続しない電気回路が、前記プリント回路基板の第2の側の真逆に配置される、請求項12に記載のインタポーザ。

- 2色LED電気インジケータシステムであって、

第1の電流方向に従って第1の色を発し、前記第1の電流方向とは逆の第2の電流方向に従って第2の色を発することが可能な2色LEDであって、前記2色LEDは第1のリード及び第2のリードも有する、2色LEDと、

単一の独立単色LEDに接続され、前記単一の独立単色LEDのみをアクティブ化させることが意図される第1の電気接地出力を提供する第1の電気線であって、前記第1の電気線は、前記2色LEDの前記第1のリード及び第1のプルアップ抵抗に接続され、前記第1のプルアップ抵抗は、電流を前記第1の電流方向に提供して、前記第1の色をアクティブ化させる、第1の電気線と、

単一の独立単色LEDに接続され、前記単一の独立単色LEDのみをアクティブ化させることが意図される第2の電気接地出力を提供する第2の電気線であって、前記第2の電気線は、前記2色LEDの前記第2のリード及び第2のプルアップ抵抗に接続され、前記第2のプルアップ抵抗は、電流を前記第2の電流方向に提供して、前記第2の色をアクティブ化させる、第2の電気線と、

を備える、2色LED電気インジケータシステム。

Applications Claiming Priority (11)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US35237810P | 2010-06-07 | 2010-06-07 | |

| US35234910P | 2010-06-07 | 2010-06-07 | |

| US35235910P | 2010-06-07 | 2010-06-07 | |

| US35236910P | 2010-06-07 | 2010-06-07 | |

| US61/352,349 | 2010-06-07 | ||

| US61/352,359 | 2010-06-07 | ||

| US61/352,378 | 2010-06-07 | ||

| US61/352,369 | 2010-06-07 | ||

| US13/153,224 | 2011-06-03 | ||

| US13/153,224 US20120002455A1 (en) | 2010-06-07 | 2011-06-03 | Miniturization techniques, systems, and apparatus relatng to power supplies, memory, interconnections, and leds |

| PCT/US2011/039292 WO2011156277A2 (en) | 2010-06-07 | 2011-06-06 | Miniturization techniques, systems, and apparatus relating to power supplies, memory, interconnections, and leds |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014505909A true JP2014505909A (ja) | 2014-03-06 |

| JP2014505909A5 JP2014505909A5 (ja) | 2014-08-14 |

Family

ID=45098601

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013514252A Pending JP2014505909A (ja) | 2010-06-07 | 2011-06-06 | 電源、メモリ、相互接続、及びledに関連する小型化技法、システム、及び装置 |

Country Status (12)

| Country | Link |

|---|---|

| US (1) | US20120002455A1 (ja) |

| EP (1) | EP2577421A4 (ja) |

| JP (1) | JP2014505909A (ja) |

| KR (1) | KR20130088825A (ja) |

| CN (1) | CN103069358A (ja) |

| AU (1) | AU2011265095A1 (ja) |

| BR (1) | BR112012031326A2 (ja) |

| CA (1) | CA2838678A1 (ja) |

| MX (1) | MX2012014355A (ja) |

| RU (1) | RU2013100003A (ja) |

| WO (1) | WO2011156277A2 (ja) |

| ZA (1) | ZA201300116B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7242574B2 (en) | 2002-10-22 | 2007-07-10 | Sullivan Jason A | Robust customizable computer processing system |

| US7256991B2 (en) | 2002-10-22 | 2007-08-14 | Sullivan Jason A | Non-peripherals processing control module having improved heat dissipating properties |

| KR101259706B1 (ko) * | 2002-10-22 | 2013-05-06 | 제이슨 에이. 설리반 | 향상된 방열 특성을 갖는 비주변 처리 제어 모듈 |

| JP2011170616A (ja) * | 2010-02-18 | 2011-09-01 | On Semiconductor Trading Ltd | 静電容量型タッチセンサ |

| US8314571B2 (en) * | 2010-12-14 | 2012-11-20 | Greenwave Reality, Pte, Ltd. | Light with changeable color temperature |

| US20140185214A1 (en) * | 2012-12-31 | 2014-07-03 | Zhen Jia | Stacked power module for graphics processing unit |

| RU2530725C2 (ru) * | 2013-01-10 | 2014-10-10 | Открытое акционерное общество "Завод им. В.А. Дегтярева" | Кронштейн |

| US20140292488A1 (en) * | 2013-03-29 | 2014-10-02 | Jerome Joseph Trohak | InSight |

| JP2015154544A (ja) * | 2014-02-13 | 2015-08-24 | アイシン・エィ・ダブリュ株式会社 | 電力変換器用のコントローラ |

| US10379591B2 (en) * | 2014-09-23 | 2019-08-13 | Hewlett Packard Enterprise Development Lp | Dual in-line memory module (DIMM) form factor backup power supply |

| US9832876B2 (en) * | 2014-12-18 | 2017-11-28 | Intel Corporation | CPU package substrates with removable memory mechanical interfaces |

| US10178786B2 (en) | 2015-05-04 | 2019-01-08 | Honeywell International Inc. | Circuit packages including modules that include at least one integrated circuit |

| US9548551B1 (en) | 2015-08-24 | 2017-01-17 | International Business Machines Corporation | DIMM connector region vias and routing |

| US10631410B2 (en) * | 2016-09-24 | 2020-04-21 | Apple Inc. | Stacked printed circuit board packages |

| CN108008764A (zh) * | 2016-10-31 | 2018-05-08 | 鸿富锦精密工业(武汉)有限公司 | 电路板组合 |

| US10361631B2 (en) * | 2017-10-05 | 2019-07-23 | Monolithic Power Systems, Inc. | Symmetrical power stages for high power integrated circuits |

| CN108766489B (zh) * | 2018-08-01 | 2023-08-08 | 灿芯半导体(上海)股份有限公司 | 一种用于倒装封装的ddr接口 |

| US10700046B2 (en) * | 2018-08-07 | 2020-06-30 | Bae Systems Information And Electronic Systems Integration Inc. | Multi-chip hybrid system-in-package for providing interoperability and other enhanced features to high complexity integrated circuits |

| DE102018127075B4 (de) * | 2018-10-30 | 2021-12-30 | Auto-Kabel Management Gmbh | Hochstromschaltung |

| CN113126714B (zh) * | 2021-04-08 | 2022-08-02 | 山东英信计算机技术有限公司 | 一种服务器内存连接装置、服务器内存测试系统及方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05206678A (ja) * | 1992-01-28 | 1993-08-13 | Nec Corp | 多層配線基板 |

| JPH0637416A (ja) * | 1992-07-14 | 1994-02-10 | Fujitsu Ltd | プリント配線板 |

| JPH06260361A (ja) * | 1993-03-03 | 1994-09-16 | Nippon Steel Corp | 薄型電源用インダクタの製造方法 |

| JP2002290087A (ja) * | 2001-03-28 | 2002-10-04 | Densei Lambda Kk | オンボード実装型電子機器およびオンボード実装型電源装置 |

| JP2003100480A (ja) * | 2001-09-25 | 2003-04-04 | Matsushita Electric Works Ltd | 放電灯点灯装置 |

| JP2007189801A (ja) * | 2006-01-12 | 2007-07-26 | Denso Corp | インバータ装置用配線基板 |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5131140A (en) * | 1991-02-26 | 1992-07-21 | Hewlett-Packard Company | Method for evaluating plane splits in printed circuit boards |

| US5076794A (en) * | 1991-04-29 | 1991-12-31 | Compaq Computer Corporation | Space-saving mounting interconnection between electrical components and a printed circuit board |

| US5539616A (en) * | 1992-06-29 | 1996-07-23 | Elonex Technologies, Inc. | Modular portable computer |

| US5736796A (en) * | 1995-05-01 | 1998-04-07 | Apple Computer, Inc. | Printed circuit board having split voltage planes |

| DE19536848A1 (de) * | 1995-10-02 | 1997-04-03 | Bosch Gmbh Robert | Baugruppenträger für ein elektronisches Steuergerät mit signalverarbeitenden Bauelementen und schnell arbeitenden digitalen Bauelementen |

| US5801072A (en) * | 1996-03-14 | 1998-09-01 | Lsi Logic Corporation | Method of packaging integrated circuits |

| SE511426C2 (sv) * | 1996-10-28 | 1999-09-27 | Ericsson Telefon Ab L M | Anordning och förfarande vid avskärmning av elektronik |

| US6043987A (en) * | 1997-08-25 | 2000-03-28 | Compaq Computer Corporation | Printed circuit board having a well structure accommodating one or more capacitor components |

| US6037846A (en) * | 1998-10-09 | 2000-03-14 | Nortel Networks Corporation | Surface mount EMI gasket filter |

| US6388206B2 (en) * | 1998-10-29 | 2002-05-14 | Agilent Technologies, Inc. | Microcircuit shielded, controlled impedance “Gatling gun”via |

| US6349038B1 (en) * | 1999-09-21 | 2002-02-19 | Dell Usa, L.P. | EMC characteristics of a printed circuit board |

| CA2299572C (en) * | 1999-11-18 | 2004-05-04 | Xybernaut Corporation | Personal communicator |

| US6373715B1 (en) * | 1999-12-17 | 2002-04-16 | Intel Corporation | Orienting multiple processors on two sides of a printed circuit board |

| US6727774B1 (en) * | 2000-06-19 | 2004-04-27 | Sun Microsystems, Inc. | Bypass capacitor methods for achieving a desired value of electrical impedance between parallel planar conductors of an electrical power distribution structure, and associated electrical power distribution structures |

| US20020099513A1 (en) * | 2001-01-25 | 2002-07-25 | Keezer David Clark | Systems and methods for testing multi-gigahertz digital systems and components |

| US6900383B2 (en) * | 2001-03-19 | 2005-05-31 | Hewlett-Packard Development Company, L.P. | Board-level EMI shield that adheres to and conforms with printed circuit board component and board surfaces |

| US6567254B2 (en) * | 2001-03-20 | 2003-05-20 | Northern Technologies, Inc. | Methods and systems for reducing clamp voltages in surge protection circuitry |

| US6639309B2 (en) * | 2002-03-28 | 2003-10-28 | Sandisk Corporation | Memory package with a controller on one side of a printed circuit board and memory on another side of the circuit board |

| CN100367645C (zh) * | 2003-08-20 | 2008-02-06 | 松下电器产业株式会社 | 开关电源装置 |

| US7619683B2 (en) * | 2003-08-29 | 2009-11-17 | Aptina Imaging Corporation | Apparatus including a dual camera module and method of using the same |

| US7286436B2 (en) * | 2004-03-05 | 2007-10-23 | Netlist, Inc. | High-density memory module utilizing low-density memory components |

| US20050205292A1 (en) * | 2004-03-18 | 2005-09-22 | Etenna Corporation. | Circuit and method for broadband switching noise suppression in multilayer printed circuit boards using localized lattice structures |

| US7230437B2 (en) * | 2004-06-15 | 2007-06-12 | Formfactor, Inc. | Mechanically reconfigurable vertical tester interface for IC probing |

| US20060065431A1 (en) * | 2004-09-29 | 2006-03-30 | Trucco Horacio A | Self-reflowing printed circuit board and application methods |

| US20060256533A1 (en) * | 2005-05-13 | 2006-11-16 | Lear Corporation | Thermally dissipating and power dispersing adhesively bonded metal-printed circuit board structure |

| US7414312B2 (en) * | 2005-05-24 | 2008-08-19 | Kingston Technology Corp. | Memory-module board layout for use with memory chips of different data widths |

| KR100656751B1 (ko) * | 2005-12-13 | 2006-12-13 | 삼성전기주식회사 | 전자소자 내장 인쇄회로기판 및 그 제조방법 |

| US7539023B2 (en) * | 2005-12-15 | 2009-05-26 | Andrei Bulucea | Monolithic plug-in power supply |

| US7895540B2 (en) * | 2006-08-02 | 2011-02-22 | Georgia Tech Research Corporation | Multilayer finite difference methods for electrical modeling of packages and printed circuit boards |

| US8174106B2 (en) * | 2006-08-29 | 2012-05-08 | International Business Machines Corporation | Through board stacking of multiple LGA-connected components |

| US7683460B2 (en) * | 2006-09-22 | 2010-03-23 | Infineon Technologies Ag | Module with a shielding and/or heat dissipating element |

| CN101868815B (zh) * | 2007-09-17 | 2014-08-20 | 照明有限责任公司 | 用于柜式标牌的led照明系统 |

| US20100007293A1 (en) * | 2008-07-09 | 2010-01-14 | Ives Burr Meadors | Programmable power-control circuit and methods of operation |

| US8582298B2 (en) * | 2009-06-22 | 2013-11-12 | Xyber Technologies | Passive cooling enclosure system and method for electronics devices |

| US9048112B2 (en) * | 2010-06-29 | 2015-06-02 | Qualcomm Incorporated | Integrated voltage regulator with embedded passive device(s) for a stacked IC |

-

2011

- 2011-06-03 US US13/153,224 patent/US20120002455A1/en not_active Abandoned

- 2011-06-06 WO PCT/US2011/039292 patent/WO2011156277A2/en active Application Filing

- 2011-06-06 JP JP2013514252A patent/JP2014505909A/ja active Pending

- 2011-06-06 AU AU2011265095A patent/AU2011265095A1/en not_active Abandoned

- 2011-06-06 MX MX2012014355A patent/MX2012014355A/es active IP Right Grant

- 2011-06-06 BR BR112012031326A patent/BR112012031326A2/pt not_active IP Right Cessation

- 2011-06-06 EP EP11792959.6A patent/EP2577421A4/en not_active Withdrawn

- 2011-06-06 CA CA2838678A patent/CA2838678A1/en not_active Abandoned

- 2011-06-06 CN CN2011800391781A patent/CN103069358A/zh active Pending

- 2011-06-06 RU RU2013100003/08A patent/RU2013100003A/ru not_active Application Discontinuation

- 2011-06-06 KR KR1020137000423A patent/KR20130088825A/ko not_active Application Discontinuation

-

2013

- 2013-01-04 ZA ZA2013/00116A patent/ZA201300116B/en unknown

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05206678A (ja) * | 1992-01-28 | 1993-08-13 | Nec Corp | 多層配線基板 |

| JPH0637416A (ja) * | 1992-07-14 | 1994-02-10 | Fujitsu Ltd | プリント配線板 |

| JPH06260361A (ja) * | 1993-03-03 | 1994-09-16 | Nippon Steel Corp | 薄型電源用インダクタの製造方法 |

| JP2002290087A (ja) * | 2001-03-28 | 2002-10-04 | Densei Lambda Kk | オンボード実装型電子機器およびオンボード実装型電源装置 |

| JP2003100480A (ja) * | 2001-09-25 | 2003-04-04 | Matsushita Electric Works Ltd | 放電灯点灯装置 |

| JP2007189801A (ja) * | 2006-01-12 | 2007-07-26 | Denso Corp | インバータ装置用配線基板 |

Also Published As

| Publication number | Publication date |

|---|---|

| MX2012014355A (es) | 2013-03-05 |

| KR20130088825A (ko) | 2013-08-08 |

| WO2011156277A3 (en) | 2012-04-26 |

| ZA201300116B (en) | 2013-09-25 |

| AU2011265095A1 (en) | 2013-01-24 |

| WO2011156277A2 (en) | 2011-12-15 |

| EP2577421A4 (en) | 2016-07-20 |

| CA2838678A1 (en) | 2011-12-15 |

| BR112012031326A2 (pt) | 2019-09-24 |

| CN103069358A (zh) | 2013-04-24 |

| RU2013100003A (ru) | 2014-07-20 |

| EP2577421A2 (en) | 2013-04-10 |

| US20120002455A1 (en) | 2012-01-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2014505909A (ja) | 電源、メモリ、相互接続、及びledに関連する小型化技法、システム、及び装置 | |

| US6744635B2 (en) | Removable visual indication structure for a printed circuit board | |

| US20150378958A1 (en) | Arbitrating usage of serial port in node card of scalable and modular servers | |

| US20070167073A1 (en) | Electricity output device with a power supply | |

| CN201083918Y (zh) | 背光模块的光源装置 | |

| US20120274474A1 (en) | Indicator light circuit and electronic device employing the same | |

| JP2007172580A (ja) | 電子装置用コネクタ、システムおよび取り付け方法(pciエクスプレス・コネクタ) | |

| US8432278B2 (en) | Network-enabled device with improved status indication of said device's network state and device state using a single light indicator or a set thereof | |

| TWI592057B (zh) | 發光裝置及其控制方法 | |

| TW201312342A (zh) | 電腦及其主機板、測試卡 | |

| CN101521982B (zh) | Pcb板、模具、led显示装置及其制作方法 | |

| US20110271025A1 (en) | Computer motherboard | |

| US20050099812A1 (en) | Conduction state indicating connector | |

| CN108811314B (zh) | 一种基于高厚径比深孔电镀技术高频高速电子线路板 | |

| TWM445791U (zh) | 萬用電路板模組及使用該萬用電路板模組的連接器 | |

| US11028974B1 (en) | LED tube with built-in driving power module | |

| CN210740100U (zh) | 一种led照明系统 | |

| US7404734B2 (en) | Jumper installation feedback | |

| TWI708182B (zh) | 具有螢幕的記憶體模組與主機板模組 | |

| CN107221285A (zh) | 一种电子显示电路 | |

| CN214098321U (zh) | 一种电脑内部连接散热和灯光的控制装置 | |

| CN2924916Y (zh) | 电源供应器的出线结构改良 | |

| CN101521983A (zh) | Pcb板、模具、led显示装置及其制作方法 | |

| CN208461117U (zh) | 一种防短路u盘 | |

| US20230262919A1 (en) | Daughter card plug detection |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140606 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140606 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140610 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150422 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150427 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20150715 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160224 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160524 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20161031 |