JP2014107383A - マスクおよびその製造方法、ならびに半導体装置 - Google Patents

マスクおよびその製造方法、ならびに半導体装置 Download PDFInfo

- Publication number

- JP2014107383A JP2014107383A JP2012258646A JP2012258646A JP2014107383A JP 2014107383 A JP2014107383 A JP 2014107383A JP 2012258646 A JP2012258646 A JP 2012258646A JP 2012258646 A JP2012258646 A JP 2012258646A JP 2014107383 A JP2014107383 A JP 2014107383A

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- pattern

- region

- data

- formation region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 45

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 37

- 230000015572 biosynthetic process Effects 0.000 claims abstract description 114

- 239000000758 substrate Substances 0.000 claims abstract description 65

- 230000007261 regionalization Effects 0.000 claims abstract description 36

- 239000000470 constituent Substances 0.000 claims description 44

- 238000000034 method Methods 0.000 claims description 32

- 230000002093 peripheral effect Effects 0.000 claims description 16

- 238000006073 displacement reaction Methods 0.000 abstract description 5

- 239000010410 layer Substances 0.000 description 47

- 230000000694 effects Effects 0.000 description 17

- 239000010408 film Substances 0.000 description 16

- 238000013461 design Methods 0.000 description 9

- 239000002356 single layer Substances 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 4

- 239000000463 material Substances 0.000 description 3

- 238000013480 data collection Methods 0.000 description 2

- QNRATNLHPGXHMA-XZHTYLCXSA-N (r)-(6-ethoxyquinolin-4-yl)-[(2s,4s,5r)-5-ethyl-1-azabicyclo[2.2.2]octan-2-yl]methanol;hydrochloride Chemical compound Cl.C([C@H]([C@H](C1)CC)C2)CN1[C@@H]2[C@H](O)C1=CC=NC2=CC=C(OCC)C=C21 QNRATNLHPGXHMA-XZHTYLCXSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000014509 gene expression Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

- H01L27/14685—Process for coatings or optical elements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/392—Floor-planning or layout, e.g. partitioning or placement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/20—Sequence of activities consisting of a plurality of measurements, corrections, marking or sorting steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/30—Structural arrangements specially adapted for testing or measuring during manufacture or treatment, or specially adapted for reliability measurements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14603—Special geometry or disposition of pixel-elements, address-lines or gate-electrodes

- H01L27/14605—Structural or functional details relating to the position of the pixel elements, e.g. smaller pixel elements in the center of the imager compared to pixel elements at the periphery

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14683—Processes or apparatus peculiar to the manufacture or treatment of these devices or parts thereof

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2119/00—Details relating to the type or aim of the analysis or the optimisation

- G06F2119/18—Manufacturability analysis or optimisation for manufacturability

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24802—Discontinuous or differential coating, impregnation or bond [e.g., artwork, printing, retouched photograph, etc.]

Abstract

【解決手段】マスクMSKは、基板SBと、有効画素形成用領域と、基準用パターン形成用領域とを備える。有効画素形成用領域には、画素を構成する画素構成部材を形成するための画素用パターンPTN1mが配置される。基準用パターン形成用領域には、有効画素形成用領域において画素用パターンPTN1mが本来配置される基準位置を示すための基準用パターンPTN21m〜PTN28mが配置される。画素用パターンPTN1mは、基準位置よりも有効画素形成用領域の中央側にずれるように配置される。

【選択図】図1

Description

(実施の形態1)

まず一実施の形態の半導体装置の加工に用いられるマスクの構成について、図1、図2を用いて説明する。

なおここでは画素用パターンPTN1mおよび非画素用パターンPTN2m(基準用パターンPTN21m〜PTN28mおよびダミー形成用パターンDMm)は図を簡略化するために矩形の平面形状を有しているが、これに限らず、これらのパターンは任意の平面形状を取り得る。

本実施の形態は、実施の形態1と比較して、基準用パターンおよび基準部の平面形状において異なっている。まず本実施の形態のマスクの構成について、図5、図6を用いて説明する。

本実施の形態のマスクMSKの非画素用パターンPTN2mは、境界線BL1m〜BL4mに対して垂直に延びる仮想の直線lを対称線とする対称な平面形状を有する。すなわち非画素用パターンPTN2mは、仮想の直線lに垂直な方向について、仮想の直線lの左側および右側の双方において同じ距離だけパターンが配置された態様となっている。したがって本実施の形態の非画素用パターンPTN2mには、仮想の直線lの左側と右側との双方に、光近接効果およびマイクロローディング効果がほぼ同様に加わる。このため本実施の形態の非画素用パターンPTN2mには、仮想の直線lの左側と右側との双方において、光近接効果およびマイクロローディング効果に起因する変形などが互いに逆方向に発生する。

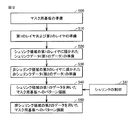

実施の形態1〜2のマスクMSKの第1の製造方法は以下のとおりである。ここでは特に、CAD上における設計(レイアウト)の手法について述べる。

実施の形態1〜2のマスクMSKの第2の製造方法は以下のとおりである。ここでも特に、CAD上における設計(レイアウト)の手法について述べる。

次に図13および図14に示すように、有効画素形成用領域(シュリンク領域)に画素用パターンPTN1mを描画するための第1のデータと、基準用パターン形成用領域(非シュリンク領域)に非画素用パターンPTN2mを描画するための第2のデータとが描かれるための、たとえば単一のレイヤが準備される(S10)。

実施の形態1〜2のマスクMSKの第3の製造方法は以下のとおりである。ここでも特に、CAD上における設計(レイアウト)の手法について述べる。

次に、図16および図17に示すように、有効画素形成用領域(シュリンク領域)に画素用パターンPTN1mを描画するための第1のデータと、基準用パターン形成用領域(非シュリンク領域)に基準用パターンPTN2mを描画するための第2のデータとが描かれるための、たとえば単一のレイヤが準備される(S10)。この工程は図15の工程(S10)と同様である。

実施の形態1〜2のマスクMSKの第4の製造方法は以下のとおりである。ここでも特に、CAD上における設計(レイアウト)の手法について述べる。

次に図21に示すように、マスク用の基板SBにおいて、有効画素形成用領域(シュリンク領域)と基準用パターン形成用領域(非シュリンク領域)との座標の範囲が特定される(S10)。ここでは上記のように、x1≦x≦x2でありかつy1≦y≦y2である座標範囲内がシュリンク領域であり、それ以外の座標範囲が非シュリンク領域であると特定される。

Claims (12)

- 主表面を有する基板と、

前記基板の前記主表面に配置された有効画素形成用領域と、

前記主表面において前記有効画素形成用領域を取り囲む基準用パターン形成用領域とを備え、

前記有効画素形成用領域には、画素を構成する画素構成部材を形成するための画素用パターンが配置され、

前記基準用パターン形成用領域には、前記有効画素形成用領域において前記画素用パターンが本来配置される基準位置を示すための基準用パターンが配置され、

前記画素用パターンは、前記基準位置よりも前記有効画素形成用領域の中央側にずれるように配置される、マスク。 - 前記基準用パターンは、前記有効画素形成用領域の外周線を介在して、前記画素用パターンと対向するように配置され、

前記基準用パターンは、前記基準用パターンに対向する前記画素用パターンが本来配置される、前記外周線に沿う方向に関する前記基準位置を示すように配置される、請求項1に記載のマスク。 - 前記基準用パターン形成用領域において、前記基準用パターンの周囲に、前記基準用パターンと間隔をあけてダミー形成用パターンが形成されている、請求項1に記載のマスク。

- 前記基準用パターンは、前記主表面において前記外周線に対して垂直に延びる仮想の直線を対称線とする対称な平面形状を有する、請求項2に記載のマスク。

- 主表面を有する半導体基板と、

前記半導体基板の前記主表面に配置された有効画素領域と、

前記主表面において前記有効画素領域を取り囲む基準部配置領域とを備え、

前記有効画素領域には、画素を構成する画素構成部材が配置され、

前記基準部配置領域には、前記有効画素領域において前記画素構成部材が本来配置される基準位置を示すための基準部が配置され、

前記画素構成部材は、前記基準位置よりも前記有効画素領域の中央側にずれるように配置される、半導体装置。 - 前記基準部は、前記有効画素領域の外周線を介在して、前記画素構成部材と対向するように配置され、

前記基準部は、前記基準部に対向する前記画素構成部材が本来配置される、前記外周線に沿う方向に関する前記基準位置を示すように配置される、請求項5に記載の半導体装置。 - 前記基準部配置領域において、前記基準部の周囲に、前記基準部と間隔をあけてダミー構造が形成されている、請求項5に記載の半導体装置。

- 前記基準部は、前記主表面において前記外周線に対して垂直に延びる仮想の直線を対称線とする対称な平面形状を有する、請求項6に記載の半導体装置。

- 主表面を有する基板を準備する工程と、

前記基板の前記主表面のうち、画素を構成する画素構成部材を形成するための画素用パターンが形成される有効画素形成用領域に前記画素用パターンを描画するための、第1のレイヤに描かれた第1のデータを準備する工程と、

前記基板の前記主表面のうち、前記有効画素形成用領域を取り囲み、前記有効画素形成用領域において前記画素用パターンが本来配置される基準位置を示すための基準用パターンが形成される基準用パターン形成用領域に前記基準用パターンを描画するための、前記第1のレイヤとは異なる第2のレイヤに描かれた第2のデータを準備する工程と、

前記第1のデータを用いて前記有効画素形成用領域に前記画素用パターンを、前記基準位置よりも前記有効画素形成用領域の中央側にずれるように描画する工程と、

前記第2のデータを用いて前記基準用パターン形成用領域に前記基準用パターンを描画する工程とを備える、マスクの製造方法。 - 主表面を有する基板を準備する工程と、

前記基板の前記主表面のうち、画素を構成する画素構成部材を形成するための画素用パターンが形成される有効画素形成用領域に前記画素用パターンを描画するための第1のデータと、前記基板の前記主表面のうち、前記有効画素形成用領域を取り囲み、前記有効画素形成用領域において前記画素用パターンが本来配置される基準位置を示すための基準用パターンが形成される基準用パターン形成用領域に前記基準用パターンを描画するための第2のデータとを準備する工程と、

前記有効画素形成用領域と、前記基準用パターン形成用領域とを識別するための識別データを準備する工程と、

前記第1のデータに前記識別データを重畳させた状態で、前記第1のデータを用いて前記有効画素形成用領域に前記画素用パターンを、前記基準位置よりも前記有効画素形成用領域の中央側にずれるように描画する工程と、

前記第2のデータを用いて前記基準用パターン形成用領域に前記基準用パターンを描画する工程とを備える、マスクの製造方法。 - 主表面を有する基板を準備する工程と、

前記基板の前記主表面のうち、画素を構成する画素構成部材を形成するための画素用パターンが形成される有効画素形成用領域に前記画素用パターンを描画するための、第1のセルに描かれた第1のデータを準備する工程と、

前記基板の前記主表面のうち、前記有効画素形成用領域を取り囲み、前記有効画素形成用領域において前記画素用パターンが本来配置される基準位置を示すための基準用パターンが形成される基準用パターン形成用領域に前記基準用パターンを描画するための、前記第1のセルとは異なる第2のセルに描かれた第2のデータを準備する工程と、

前記第1のデータを用いて前記有効画素形成用領域に前記画素用パターンを、前記基準位置よりも前記有効画素形成用領域の中央側にずれるように描画する工程と、

前記第2のデータを用いて前記基準用パターン形成用領域に前記基準用パターンを描画する工程とを備え、

前記第1のセルと前記第2のセルとは同一のレイヤで描かれる、マスクの製造方法。 - 主表面を有する基板を準備する工程と、

前記基板の前記主表面のうち、画素を構成する画素構成部材を形成するための画素用パターンが形成される有効画素形成用領域と、前記基板の前記主表面のうち、前記有効画素形成用領域を取り囲み、前記有効画素形成用領域において前記画素用パターンが本来配置される基準位置を示すための基準用パターンが形成される基準用パターン形成用領域との、前記基板の前記主表面における座標の範囲を特定する工程と、

前記有効画素形成用領域に前記画素用パターンを描画するための第1のデータと、前記基準用パターン形成用領域に前記基準用パターンを描画するための第2のデータとを準備する工程と、

前記座標の範囲を識別しながら、前記第1のデータを用いて前記有効画素形成用領域に前記画素用パターンを、前記基準位置よりも前記有効画素形成用領域の中央側にずれるように描画する工程と、

前記座標の範囲を識別しながら、前記第2のデータを用いて前記基準用パターン形成用領域に前記基準用パターンを描画する工程とを備える、マスクの製造方法。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012258646A JP2014107383A (ja) | 2012-11-27 | 2012-11-27 | マスクおよびその製造方法、ならびに半導体装置 |

| TW102141035A TWI618972B (zh) | 2012-11-27 | 2013-11-12 | 光罩及其製造方法以及半導體裝置 |

| US14/079,709 US9054011B2 (en) | 2012-11-27 | 2013-11-14 | Mask and method for manufacturing the same, and semiconductor device |

| CN201310611389.9A CN103839782B (zh) | 2012-11-27 | 2013-11-26 | 掩模及其制造方法、半导体装置 |

| CN201810179971.5A CN108321143B (zh) | 2012-11-27 | 2013-11-26 | 掩模及其制造方法、半导体装置 |

| US14/702,878 US9524915B2 (en) | 2012-11-27 | 2015-05-04 | Semiconductor device |

| US15/293,805 US9825084B2 (en) | 2012-11-27 | 2016-10-14 | Semiconductor device |

| US15/797,547 US10199425B2 (en) | 2012-11-27 | 2017-10-30 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012258646A JP2014107383A (ja) | 2012-11-27 | 2012-11-27 | マスクおよびその製造方法、ならびに半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017018261A Division JP6362716B2 (ja) | 2017-02-03 | 2017-02-03 | マスクおよび半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014107383A true JP2014107383A (ja) | 2014-06-09 |

| JP2014107383A5 JP2014107383A5 (ja) | 2015-10-15 |

Family

ID=50772470

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012258646A Pending JP2014107383A (ja) | 2012-11-27 | 2012-11-27 | マスクおよびその製造方法、ならびに半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (4) | US9054011B2 (ja) |

| JP (1) | JP2014107383A (ja) |

| CN (2) | CN103839782B (ja) |

| TW (1) | TWI618972B (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6246076B2 (ja) * | 2014-06-05 | 2017-12-13 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法および半導体装置 |

| CN104297989B (zh) * | 2014-10-22 | 2017-06-27 | 京东方科技集团股份有限公司 | 基板、掩膜板及液晶显示装置 |

| US9558545B2 (en) * | 2014-12-03 | 2017-01-31 | Kla-Tencor Corporation | Predicting and controlling critical dimension issues and pattern defectivity in wafers using interferometry |

| JP2017032365A (ja) * | 2015-07-31 | 2017-02-09 | 株式会社日立ハイテクノロジーズ | パターンの計測方法および計測装置 |

| US20180130845A1 (en) * | 2016-11-04 | 2018-05-10 | Dpix, Llc | Flat panel array with the alignment marks in active area |

| CN108241230B (zh) * | 2016-12-23 | 2020-11-13 | 上海仪电显示材料有限公司 | 彩色滤光基板的制作方法 |

| KR20200093583A (ko) * | 2017-11-29 | 2020-08-05 | 다이니폰 인사츠 가부시키가이샤 | 배선 기판 및 배선 기판의 제조 방법 |

| FR3099297B1 (fr) | 2019-07-24 | 2022-08-12 | Accumulateurs Fixes | Composition d’electrolyte pour element electrochimique comprenant une anode de lithium |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01186617A (ja) * | 1988-01-14 | 1989-07-26 | Seiko Epson Corp | 半導体装置 |

| JP2000131826A (ja) * | 1998-10-27 | 2000-05-12 | Hitachi Ltd | マスク及びそれを用いた半導体装置の製造方法 |

| JP2006134356A (ja) * | 2000-06-13 | 2006-05-25 | Mentor Graphics Corp | 集積化検証および製造適応ツール |

| JP2006145563A (ja) * | 2004-11-16 | 2006-06-08 | Sony Corp | パターン形成方法及び装置 |

| JP2006173314A (ja) * | 2004-12-15 | 2006-06-29 | Matsushita Electric Ind Co Ltd | 固体撮像装置およびマスク描画方法 |

| JP2008103472A (ja) * | 2006-10-18 | 2008-05-01 | Sony Corp | 固体撮像素子及び撮像装置 |

| JP2009026045A (ja) * | 2007-07-19 | 2009-02-05 | Toshiba Corp | 半導体集積回路のレイアウト作成装置および半導体集積回路の製造方法 |

| JP2010060937A (ja) * | 2008-09-04 | 2010-03-18 | Nikon Corp | フォトマスクセット、フォトマスク、デバイスの製造方法、並びに、測定方法及びその装置 |

| JP2012155081A (ja) * | 2011-01-25 | 2012-08-16 | Toshiba Corp | 露光マスクのパタン配置方法 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0917715A (ja) | 1995-06-29 | 1997-01-17 | Nec Corp | 半導体装置のパターン合わせノギス |

| JPH10335205A (ja) | 1997-05-29 | 1998-12-18 | Nec Yamagata Ltd | 半導体集積回路のパターン設計方法 |

| JP3948084B2 (ja) | 1997-11-14 | 2007-07-25 | ソニー株式会社 | 電子線描画用精度測定方法 |

| JP4326088B2 (ja) * | 1999-11-05 | 2009-09-02 | 富士通マイクロエレクトロニクス株式会社 | 描画パターン検査方法 |

| US6425113B1 (en) * | 2000-06-13 | 2002-07-23 | Leigh C. Anderson | Integrated verification and manufacturability tool |

| JP2002278517A (ja) * | 2001-03-15 | 2002-09-27 | Hitachi Ltd | 液晶表示装置 |

| US6664011B2 (en) * | 2001-12-05 | 2003-12-16 | Taiwan Semiconductor Manufacturing Company | Hole printing by packing and unpacking using alternating phase-shifting masks |

| JP3689698B2 (ja) * | 2003-01-31 | 2005-08-31 | キヤノン株式会社 | 投影露光装置、投影露光方法および被露光部材の製造方法 |

| JP3977285B2 (ja) * | 2003-05-15 | 2007-09-19 | キヤノン株式会社 | 固体撮像素子の製造方法 |

| JP4018642B2 (ja) * | 2004-01-05 | 2007-12-05 | 株式会社東芝 | 参照データ生成方法、パターン欠陥検査装置、パターン欠陥検査方法、及び参照データ生成プログラム |

| US7266803B2 (en) * | 2005-07-29 | 2007-09-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Layout generation and optimization to improve photolithographic performance |

| JP2008205312A (ja) | 2007-02-21 | 2008-09-04 | Denso Corp | 露光方法 |

| US7945873B2 (en) * | 2007-04-17 | 2011-05-17 | Canon Kabushiki Kaisha | Mask pattern data generating method, information processing apparatus, photomask fabrication system, and image sensing apparatus |

| JP5593602B2 (ja) * | 2008-09-24 | 2014-09-24 | ソニー株式会社 | 撮像素子および撮像装置 |

| JP5330019B2 (ja) * | 2009-02-18 | 2013-10-30 | ルネサスエレクトロニクス株式会社 | マスクパターンの検査方法およびマスクパターン検査装置 |

| JP5493461B2 (ja) * | 2009-05-12 | 2014-05-14 | ソニー株式会社 | 固体撮像装置、電子機器及び固体撮像装置の製造方法 |

| NL2005804A (en) * | 2010-01-14 | 2011-07-18 | Asml Netherlands Bv | Method and apparatus for enhancing signal strength for improved generation and placement of model-based sub-resolution assist features (mb-sraf). |

| JP5758727B2 (ja) * | 2011-07-15 | 2015-08-05 | ルネサスエレクトロニクス株式会社 | マスク検査方法、およびマスク検査装置 |

| JP2014027123A (ja) * | 2012-07-27 | 2014-02-06 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| CN102776473B (zh) * | 2012-08-10 | 2014-10-29 | 深圳市华星光电技术有限公司 | 有机电致发光二极管有机材料蒸镀用掩模装置 |

-

2012

- 2012-11-27 JP JP2012258646A patent/JP2014107383A/ja active Pending

-

2013

- 2013-11-12 TW TW102141035A patent/TWI618972B/zh active

- 2013-11-14 US US14/079,709 patent/US9054011B2/en active Active

- 2013-11-26 CN CN201310611389.9A patent/CN103839782B/zh not_active Expired - Fee Related

- 2013-11-26 CN CN201810179971.5A patent/CN108321143B/zh active Active

-

2015

- 2015-05-04 US US14/702,878 patent/US9524915B2/en active Active

-

2016

- 2016-10-14 US US15/293,805 patent/US9825084B2/en active Active

-

2017

- 2017-10-30 US US15/797,547 patent/US10199425B2/en active Active

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01186617A (ja) * | 1988-01-14 | 1989-07-26 | Seiko Epson Corp | 半導体装置 |

| JP2000131826A (ja) * | 1998-10-27 | 2000-05-12 | Hitachi Ltd | マスク及びそれを用いた半導体装置の製造方法 |

| JP2006134356A (ja) * | 2000-06-13 | 2006-05-25 | Mentor Graphics Corp | 集積化検証および製造適応ツール |

| JP2006145563A (ja) * | 2004-11-16 | 2006-06-08 | Sony Corp | パターン形成方法及び装置 |

| JP2006173314A (ja) * | 2004-12-15 | 2006-06-29 | Matsushita Electric Ind Co Ltd | 固体撮像装置およびマスク描画方法 |

| JP2008103472A (ja) * | 2006-10-18 | 2008-05-01 | Sony Corp | 固体撮像素子及び撮像装置 |

| JP2009026045A (ja) * | 2007-07-19 | 2009-02-05 | Toshiba Corp | 半導体集積回路のレイアウト作成装置および半導体集積回路の製造方法 |

| JP2010060937A (ja) * | 2008-09-04 | 2010-03-18 | Nikon Corp | フォトマスクセット、フォトマスク、デバイスの製造方法、並びに、測定方法及びその装置 |

| JP2012155081A (ja) * | 2011-01-25 | 2012-08-16 | Toshiba Corp | 露光マスクのパタン配置方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140145192A1 (en) | 2014-05-29 |

| US20180053807A1 (en) | 2018-02-22 |

| US20170033152A1 (en) | 2017-02-02 |

| US9524915B2 (en) | 2016-12-20 |

| TW201437738A (zh) | 2014-10-01 |

| TWI618972B (zh) | 2018-03-21 |

| US9054011B2 (en) | 2015-06-09 |

| CN108321143B (zh) | 2021-07-16 |

| US10199425B2 (en) | 2019-02-05 |

| US9825084B2 (en) | 2017-11-21 |

| CN108321143A (zh) | 2018-07-24 |

| CN103839782A (zh) | 2014-06-04 |

| CN103839782B (zh) | 2018-03-30 |

| US20150235912A1 (en) | 2015-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2014107383A (ja) | マスクおよびその製造方法、ならびに半導体装置 | |

| WO2013021985A1 (ja) | 露光装置用のアライメント装置及びアライメントマーク | |

| US20160071255A1 (en) | Methods for measuring overlays | |

| KR20150108356A (ko) | 터치 패널 및 표시 장치 | |

| CN104570170A (zh) | 光学元件阵列、光电转换装置以及图像拾取系统 | |

| CN105319622A (zh) | 光学元件阵列和包括该阵列的固态成像装置 | |

| TWI432815B (zh) | 鏡頭模組 | |

| TWI484236B (zh) | 影像感測器 | |

| TWI547918B (zh) | 面板裝置及其檢測方法 | |

| JP6362716B2 (ja) | マスクおよび半導体装置 | |

| JP2013207053A5 (ja) | ||

| KR20220012360A (ko) | 지문 감지 장치 및 전자 디바이스 | |

| CN106959557B (zh) | 一种显示基板及其制作方法、显示装置 | |

| JP6222989B2 (ja) | 電子装置の製造方法 | |

| CN105301677A (zh) | 光掩模、光学元件阵列的制造方法、光学元件阵列 | |

| US10495892B2 (en) | Display assembly, driving method thereof, and display device | |

| JP2012114270A (ja) | 半導体チップの製造方法 | |

| CN110232298B (zh) | 光学指纹传感器模组 | |

| JP2002334974A (ja) | 固体撮像装置及びその製造方法 | |

| US8780315B2 (en) | LCD panel, color filter substrate, and method of manufacturing the color filter substrate | |

| CN102034736B (zh) | 接触孔的光刻方法 | |

| WO2023032851A1 (ja) | マーカ、検出装置、及び、検出方法 | |

| WO2016002730A1 (ja) | 光学表示デバイスの検査方法および光学部材のパターン認識方法 | |

| TWI446013B (zh) | 鏡頭與鏡頭單元片 | |

| JP2016170212A (ja) | 固体撮像装置およびカメラ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150827 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150827 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160623 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160719 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160914 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20161108 |