以下、図面を参照しつつ、実施の形態について説明する。実施の形態の説明において、個数、量などに言及する場合、特に記載ある場合を除き、必ずしもその個数、量などに限定されない。実施の形態の図面において、同一の参照符号や参照番号は、同一部分または相当部分を表わすものとする。また、実施の形態の説明において、同一の参照符号等を付した部分等に対しては、重複する説明は繰り返さない場合がある。

<実施の形態1>

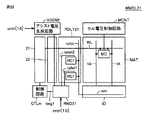

図1を参照して、実施の形態1に係る半導体装置LSI_1のブロック構成図を説明する。

半導体装置LSI_1(以下、単に、チップと記載する場合もある。)は、IPモジュール2およびメモリモジュールMMDL1を備える、所謂、SOC(Silicon On a Chip)である。IPモジュール2は、例えば、中央処理装置(CPU)である。IPモジュール2およびメモリモジュールMMDL1間は、バス3を介して、アドレス、データ、および各種制御信号を送受信する。レギュレータ回路1は、印加された電源電圧vdd_exに基づき、IPモジュール2およびメモリモジュールMMDL1へ、各々、電源電圧vdd_cpuおよび電源電圧vddを供給する。図1において、レギュレータ回路1は、半導体装置LSI_1とは別チップで構成される例を示す。必要に応じ、レギュレータ回路1は、半導体装置LSI_1に内蔵されても良い。

メモリモジュールMMDL1は、ワードデコーダ21、ワードドライバ22、メモリセルアレイMAT、IO部IO、アシスト電圧生成回路VGEN、セル電圧制御回路MCNT、制御回路CTLm、および遅延回路DLY1を有する。制御回路CTLmは、基準タイミング信号tmg1を遅延回路DLY1へ出力する。遅延回路DLY1は、基準タイミング信号tmg1を所定時間遅延させたセンスアンプ起動信号saeを生成する。この遅延時間は、アシスト電圧生成回路VGENが生成するワード線アシスト電圧wdrv_vddに応答して、変化する。

図2を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の回路図を説明する。

メモリモジュールMMDL1は、ワード線WLj(j=0〜m:mは正の整数)およびビット線対bt/bbと接続されたメモリセルMCが行列状に配置されたメモリセルアレイMATを有する。各ワード線WLjは、ワードドライバ22が有するp型トランジスタMp21およびn型トランジスタMn21で構成されるインバータの出力ノードと接続される。p型トランジスタMp21のソースには、ワード線アシスト電圧wdrv_vddが印加される。n型トランジスタMn21のソースには、電源電圧vssが印加される。

アシスト電圧生成回路VGENは、電源電圧vddを降圧して、ワード線アシスト電圧wdrv_vddを生成する。このワード線アシスト電圧wdrv_vddは、ワードドライバ22が有するp型トランジスタ21を経由して、選択ワード線WLjに印加される。選択ワード線WLjの電圧を、メモリセルMCに印加される電源電圧vddより低下させることで、メモリセルのSNM(スタティック・ノイズ・マージン)が確保される。

ワードデコーダ21は、制御回路CTLmが出力するアドレス信号adr[x:0]に基づき、ワードドライバ22が有する複数のインバータ(Mp21/Mn21)のいずれか一つを選択する。ワードデコーダ21におけるアドレス信号adr[x:0]の取込み、および制御回路CTLmにおける基準タイミング信号tmg1の生成は、クロックCLKに同期して行われる。制御回路CTLmは、IPモジュール2からバス3を経由して送信されるアドレス信号A[k:0]をクロックCLKに同期して取り込み、アドレス信号adr[x:0]を生成する。

セル電圧制御回路MCNTには、電源電圧vddが印加される。セル電圧制御回路MCNTは、制御回路CTLmが出力する信号colselおよび信号rwselに応答して、書込み時における選択カラム(選択列)のメモリセルMCに印加する電圧を制御する。即ち、セル電圧制御回路MCNTは、書込み対象となる選択カラムのメモリセルMCに印加される電圧mvdd[0]または電圧mvdd[1]を、非選択カラムに印加される電圧より低く設定する。この設定により、メモリセルMCのライトマージンが確保される。

カラムセレクタ23は、信号colselに基づき、2つのビット線対bt/bbのいずれか一方を選択する。図2は、1つのカラムセレクタ23には2つのビット線対bt/bbが接続されている例を示す。適宜、カラムセレクタ23に接続するビット線対bt/bbの本数を増加しても良い。この信号colselは、制御回路CTLmに入力されるアドレス信号A[k:0]に基づき生成される。

カラムセレクタ23は、さらに、信号rwselに基づき、選択されたビット線対bt/bbをセンスアンプ(SA)24およびライトアンプ(WA)25のいずれか一方に接続する。この信号rwselは、制御回路CTLmに入力されるライトイネーブル信号WEに応答して生成される。

センスアンプ24には、選択されたメモリセルMCがビット線対bt/bbに出力する微小振幅の電圧が入力される。センスアンプ24は、センスアンプ起動信号saeに応答して起動される。即ち、センスアンプ起動信号saeがロウレベル(電源電圧vss)からハイレベル(電源電圧vdd)に変化すると、センスアンプ24は、入力された微小振幅の電圧を増幅し、2値の値を有する出力データQ[p](p=0〜n:nは正の整数)を出力する。センスアンプ起動信号saeの2値の値と、センスアンプ24の起動との対応付けは、上述と逆相に設定しても良い。なお、図2のメモリモジュールMMDL1は、n+1ビット幅である。

上述の通り、メモリモジュールMMDL1には、レギュレータ回路1が生成する電源電圧vddが印加される。この電源電圧vddは、ワードドライバ22を除いて、メモリモジュールMMDL1が有する各回路に印加される。ワードドライバ22には、アシスト電圧生成回路VGENが生成するワード線アシスト電圧wdrv_vddが印加される。

遅延回路DLY1は、基準タイミング信号tmg1を所定時間遅延させたセンスアンプ起動信号saeを生成する。遅延回路DLY1は、センスアンプ24が、アドレス信号adr[x:0]で選択されるメモリセルMCのデータに応じて、ビット線対bt/bbの電位差がセンスアンプ24で増幅可能な値に開くタイミングと、センスアンプ起動信号saeの生成タイミングと、を整合させる。遅延回路DLY1の遅延時間をワード線アシスト電圧wdrv_vddで調整することにより、ワード線アシスト電圧wdrv_vddが印加される選択メモリセルMCにおける遅延時間と整合させたセンスアンプ起動信号saeの生成が実現される。

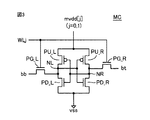

図3を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリセルアレイMATが有するメモリセルMCの回路図を説明する。

p型トランジスタPU_Lのソースには電圧mvdd[j]が印加され、そのドレインはノードNLと接続される。n型トランジスタPD_LのドレインはノードNLと接続され、そのソースには電源電圧vssが印加される。p型トランジスタPU_Rのソースには電圧mvdd[j]が印加され、そのドレインはノードNRと接続される。n型トランジスタPD_RのドレインはノードNRと接続され、そのソースには電源電圧vssが印加される。p型トランジスタPU_Lおよびn型トランジスタPD_LのゲートはノードNRと接続され、p型トランジスタPU_Rおよびn型トランジスタPD_Rのゲートは、ノードNLと接続される。

n型トランジスタPG_Lのソース/ドレインのいずれか一方はノードNLと接続され、ソース/ドレインのいずれか他方はビット線bbと接続される。n型トランジスタPG_Rのソース/ドレインのいずれか一方はノードNRと接続され、ソース/ドレインのいずれか他方はビット線btと接続される。n型トランジスタPG_Lおよびn型トランジスタPG_Rのゲートは、ワード線WLjと接続される。なお、n型トランジスタPG_Lおよびn型トランジスタPG_Rのソースおよびドレインは、導通電流の方向により変化する。本明細書では、n型トランジスタPG_L等のソースおよびドレインは、”ソース/ドレイン”と記載される。

図4を参照して、実施の形態1に係る半導体装置LSI_1が備えるIO部IOが有するカラムセレクタ23の回路図を説明する。

カラムセレクタ23は、信号colselおよび信号rwselで動作が制御されるスイッチ51〜スイッチ54を有する。カラムセレクタ23は、信号colselおよび信号rwselに基づき、ビット線対bt/bbの接続先を、センスアンプ24、ライトアンプ25、および電源電圧vddのいずれかに切り替える。図4は、カラムセレクタ23と接続される2組のビット線対bt/bbのうち、左側のビット線対bt/bbおよび右側の選択ビット線対bt/bbが、各々、読出し時における選択ビット線対および非選択ビット線対として設定された場合の接続を示す。

左側の選択ビット線対bt/bbは、スイッチ51およびスイッチ52を介して、センスアンプ24の入力端子と接続される。右側の非選択ビット線対bt/bbは、スイッチ53およびスイッチ54を介して、電源電圧vddにプリチャージされる。ライトアンプ25に入力された書込みデータD[0]をビット線対bt/bbに印加する場合、選択ビット線対bt/bbとライトアンプ25の出力とが接続されるようにスイッチ51〜スイッチ54の開閉状態が制御される。なお、図4は、メモリセルアレイMATのn+1ビットのデータ幅のうち、0ビットのセンスアンプ24およびライトアンプ25と接続されるカラムセレクタ23の構成を示すが、他のビットも同様である。

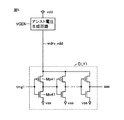

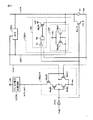

図5を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1が有する遅延回路DLY1の回路図を説明する。

遅延回路DLY1は、p型トランジスタMp41およびn型トランジスタMn41で構成されるインバータを所定段数直列接続した構成を有する。p型トランジスタMp41のソースには、アシスト電圧生成回路VGENが生成するワード線アシスト電圧wdrv_vddが印加され、そのドレインはn型トランジスタMn41のドレインと接続される。n型トランジスタMn41のソースには、電源電圧vssが印加される。

直列接続されたインバータの初段におけるp型トランジスタMp41およびn型トランジスタMn41のゲートには、基準タイミング信号tmg1が入力される。最終段のインバータは、基準タイミング信号tmg1を所定時間遅延させたセンスアンプ起動信号saeを出力する。遅延回路DLY1の遅延時間は、各インバータに印加されるワード線アシスト電圧wdrv_vddに依存する。

ワード線アシスト電圧wdrv_vddは、メモリセルのSNMを所定値維持可能な値に設定される。その結果、選択ワード線WLj(図2参照)に電源電圧vddを印加する場合と比べて、選択ワード線WLjにワード線アシスト電圧wdrv_vddを印加した場合、メモリセルの読出し速度は低下する。図3に示されるメモリセルMCの回路図において、ワード線WLjに印加される電圧が電源電圧vddからワード線アシスト電圧wdrv_vddに低下した場合、n型トランジスタPG_Lおよびn型トランジスタPG_Rの駆動能力が低下する。その結果、ビット線対bt/bb間の電位差がセンスアンプ24で増幅可能な値まで増加する時間は、ワード線WLjに電源電圧vddを印加した場合と比較して、ワード線WLjにワード線アシスト電圧wdrv_vddを印加した場合、増大する。

一方、図2に示されるメモリモジュールMMDL1において、ワードドライバ22以外の回路には電源電圧vddが印加される。その結果、制御回路CTLm、ワードデコーダ21、ワードドライバ22、メモリセルMC、およびカラムセレクタ23を経由して、ビット線対bt/bbのデータがセンスアンプ24に入力されるタイミングと、電源電圧vddが印加される回路で生成されるセンスアンプ起動信号saeでセンスアンプ24を起動するタイミングが整合しなくなる。

図5に示される遅延回路DLY1には、アシスト電圧生成回路VGENが生成するワード線アシスト電圧wdrv_vddが印加される。従って、センスアンプ起動信号saeを生成するパスは、電源電圧vddが印加される制御回路CTLmおよび遅延回路DLY1で構成される。その結果、ワード線アシスト電圧wdrv_vddが印加されるメモリセルMCがビット線対bt/bbを駆動する時間の変化を、遅延回路DLY1の遅延時間に反映することが可能となる。

図6を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の動作タイミングを説明する。

最初のクロックCLKの立ち上がり期間は読出しサイクル、2番目のクロックCLKの立ち上がり期間は書込みサイクルである。図6では省略しているが、読出しサイクルおよび書込みサイクルは、制御回路CTLmに入力されるライトイネーブル信号WEにより設定される(図2参照)。

読出しサイクルにおいて、セル電圧制御回路MCNTは、選択カラムのメモリセルMCに印加する電圧mvdd[0]および非選択カラムのメモリセルMCに印加する電圧mvdd[1]を、ともに電源電圧vddとする。

制御回路CTLmは、クロックCLKの立ち上がりエッジに同期して、アドレスA[k:0]を取り込み、アドレス信号adr[x:0]を生成する。アドレス信号adr[x:0]に基づき、ワードドライバ22は、選択ワード線WLjの電圧を電源電圧vssからワード線アシスト電圧wdrv_vddに立ち上げる。ワード線アシスト電圧wdrv_vddは、電源電圧vddをΔvdd_wl降下させた電圧に設定される。

制御回路CTLmは、クロックCLKの立ち上がりエッジに同期して、さらに、基準タイミング信号tmg1を生成する。図6では、基準タイミング信号の一例として、所定のパルス幅を有するワンショットパルスが示される。

選択ワード線WLjおよび選択カラム(選択ビット線対bt/bb)と接続されるメモリセルMCは、ビット線対bt/bb間の電圧を増大させ、センスアンプ24の入力信号を生成する。

遅延回路DLY1は、基準タイミング信号tmg1の立ち上がりエッジを所定時間遅延させ、センスアンプ起動信号saeの立ち上がりエッジを生成する。図6では、センスアンプ起動信号saeの一例として、立ち上がりエッジから所定時間経過後に立ち下がるワンショットパルスが示される。センスアンプ起動信号saeの立ち上がりに応答して、センスアンプ24は、選択メモリセルMCと接続されるビット線対bt/bb間の電圧の増幅動作を開始する。

センスアンプ起動信号saeの立ち上がりエッジに基づくセンスアンプ24の起動タイミングは、基準タイミング信号tmg1の立ち上がりエッジに応答して決定される。また、選択メモリセルMCがビット線対bt/bb間に電圧を出力するタイミングは、ワード線WLjの立ち上がりエッジに応答して決定される。ワード線WLjの立ち上がりエッジおよび基準タイミング信号tmg1の立ち上がりエッジは、いずれもクロックCLKの立ち上がりエッジに応答して生成される。

書込みサイクルにおいて、セル電圧制御回路MCNTは、選択カラムのメモリセルMCに印加する電圧mvdd[0]を、電源電圧vddからΔvdd_write降下させた値に設定する。一方、非選択カラムのメモリセルMCに印加する電圧mvdd[1]は、電源電圧vddに設定される。選択ワード線WLjには、読出しサイクル時と同様に、電源電圧vddをΔvdd_wl降下させた電圧が印加される。この電圧設定により、選択ワード線WLjおよび選択ビット線対bt/bbと接続されたメモリセルMCの書込みマージンが確保され、一方で、選択ワード線WLjおよび非選択ビット線対bt/bbと接続されたメモリセルMCが保持するデータ破壊は防止される。

遅延回路DLY1は、センスアンプ起動信号saeの立ち上がりタイミングを、選択メモリセルMCがビット線対bt/bb間にセンスアンプ24が増幅可能な電位差を出力するタイミングと整合するように基準タイミング信号tmg1の遅延時間を調整する。ワード線アシスト電圧wdrv_vddをワード線WLjに印加するメモリモジュールMMDL1において、この遅延回路DLY1により、センスアンプ24の起動タイミングを最適化することが可能となる。この結果、メモリモジュールMMDL1のアクセス時間短縮および消費電力低減が実現される。

図7を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1が有する遅延回路DLY1の変形例1および変形例2の回路図を説明する。

図7(a)は、遅延回路DLY1の変形例1である遅延回路DLY11の回路図である。遅延回路DLY11は、遅延時間が電源電圧vddに依存するサブ遅延回路DLY11aおよび遅延時間がワード線アシスト電圧wdrv_vddに依存するサブ遅延回路DLY11bで構成される。サブ遅延回路DLY11aおよびサブ遅延回路DLY11bは、p型トランジスタMp71およびn型トランジスタMn71で構成されるインバータを、各々、所定段数、直列接続した遅延回路である。

サブ遅延回路DLY11aにおいて、p型トランジスタMp71のソースには電源電圧vddが印加され、そのドレインは、n型トランジスタMn71のドレインと接続される。n型トランジスタMn71のソースには電源電圧vssが印加される。初段のインバータを構成するp型トランジスタMp71およびn型トランジスタMn71のゲートには、基準タイミング信号tmg1が印加される。最終段のインバータは、電源電圧vddに依存する遅延時間経過後、基準タイミング信号tmg1を出力する。

サブ遅延回路DLY11bにおいて、p型トランジスタMp71のソースにはワード線アシスト電圧wdrv_vddが印加され、そのドレインは、n型トランジスタMn71のドレインと接続される。n型トランジスタMn71のソースには電源電圧vssが印加される。初段のインバータを構成するp型トランジスタMp71およびn型トランジスタMn71のゲートには、サブ遅延回路DLY11aの出力信号が印加される。最終段のインバータは、ワード線アシスト電圧wdrv_vddに依存する遅延時間経過後、遅延回路DLY11の出力信号として、センスアンプ起動信号saeを出力する。

ビット線対bt/bbにセンスアンプ24で増幅可能な電位差が発生するまでの時間は、セル電流に依存する。トランジスタの閾値電圧はランダムにばらつくため、各メモリセルMCのセル電流は異なる。ビット線対bt/bb間の電位差不足による読出し不良を防ぐためには、最もセル電流が少ないメモリセルMC(ワーストセル)に合わせてセンスアンプ24の起動タイミングを設計する必要がある。また、閾値電圧が異なると、セル電流のワード線アシスト電圧wdrv_vdd依存性が異なる。従って、遅延回路DLY1の遅延量のワード線アシスト電圧wdrv_vddの依存性は、ワーストセルのワード線アシスト電圧wdrv_vdd依存性と同じであることが望ましい。

遅延回路DLY11が有するサブ遅延回路DLY11aおよびサブ遅延回路DLY11bの段数を調整することで、遅延回路DLY11のワード線アシスト電圧wdrv_vdd依存性の調整が可能になる。これにより、プロセス、温度、電圧条件等に応じて、ワード線アシスト電圧wdrv_vddの電圧を変更した場合でも、センスアンプ起動タイミングを、より最適化することが可能となる。

図7(b)は、遅延回路DLY1の変形例2である遅延回路DLY12の回路図である。サブ遅延回路DLY12bは、p型トランジスタMp72、n型トランジスタMn72、およびn型トランジスタMn73で構成されるインバータを、所定段数、直列接続した遅延回路である。

サブ遅延回路DLY12bにおいて、p型トランジスタMp72のソースには電源電圧vddが印加され、そのドレインはn型トランジスタMn72のドレインと接続される。n型トランジスタMn72のソースは、n型トランジスタMn73のドレインと接続される。n型トランジスタMn73のソースには、電源電圧vssが印加される。

サブ遅延回路DLY12bにおいて、初段のインバータが有するp型トランジスタMn72のゲートおよびn型トランジスタMn73のゲートには、サブ遅延回路DLY12aの出力信号が印加される。最終段のインバータは、電源電圧vddおよびワード線アシスト電圧wdrv_vddに依存する遅延時間経過後、サブ遅延回路DLY12aの出力信号として、センスアンプ起動信号saeを出力する。

図7(a)に示されるサブ遅延回路DLY11bにおいて、ワード線アシスト電圧wdrv_vddは、インバータが有するp型トランジスタMp71のソースに印加される。p型トランジスタMp71およびn型トランジスタMn71で構成されるインバータの動作電流により、ワード線アシスト電圧wdrv_vddにノイズが発生する危険性が懸念される。このノイズにより、ワード線WLjの電圧が変動し、メモリセルMCの動作マージン悪化が懸念される。

それに対し、サブ遅延回路DLY12bにおいて、インバータが有するp型トランジスタMp72のソースには電源電圧vddが印加されるとともに、n型トランジスタMn72のゲートには、ワード線アシスト電圧wdrv_vddが印加される。この構成により、ワード線アシスト電圧wdrv_vddに、インバータの動作電流に起因するノイズが抑制される。この結果、ワード線アシスト電圧wdrv_vddに発生するノイズを吸収する容量に起因するチップ面積増大や消費電力増加を抑制することが可能となる。なお、サブ遅延回路DLY12bにおいて、センスアンプ起動信号saeの立ち上がりタイミングに影響を及ぼすのは、インバータの偶数段または奇数段のいずれか一方である。従って、偶数段または奇数段どちらかのインバータにおいて、n型トランジスタだけを縦積み構成とすることで、チップ面積を削減することが可能である。

<実施の形態1の変形例1>

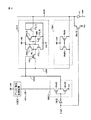

図8を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の変形例1であるメモリモジュールMMDL11のブロック構成を説明する。

メモリモジュールMMDL11は、メモリモジュールMMDL1と以下の点が相違する。即ち、メモリモジュールMMDL1が備えていた遅延回路DLY1に代えて、レプリカセル駆動回路RWD1およびレプリカセル遅延回路RDLY11を備える。メモリモジュールMMDL11において、メモリモジュールMMDL1と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

図9を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL11の構成を説明する。

メモリモジュールMMDL11は、ワードデコーダ21、ワードドライバ22、メモリセルアレイMAT、IO部IO、アシスト電圧生成回路VGEN、セル電圧制御回路MCNT、および制御回路CTLmと、レプリカセル駆動回路RWD1、レプリカセル遅延回路RDLY11、インバータINV1、およびインバータINV2と、を有する。

レプリカセル駆動回路RWD1には、アシスト電圧生成回路VGENが生成するワード線アシスト電圧wdrv_vddが印加される。レプリカセル駆動回路RWD1には、基準タイミング信号tmg1の論理レベルをインバータINV2で反転させた信号が印加される。

レプリカセル遅延回路RDLY11は、レプリカセル選択線rplwlおよびレプリカビット線rplbtに接続された複数のレプリカセルRC1と、レプリカビット線rplbtに接続された複数のダミーセルDCと、を有する。レプリカセルRC1およびダミーセルDCを構成する各トランジスタは、メモリセルアレイMATが有するメモリセルMCを構成する対応する各トランジスタと同一の形状および配置を有することが好ましい。

レプリカセルRC1およびダミーセルDCの合計数は、メモリセルアレイMATのビット線対bt/bbと接続されるメモリセルMCの総数m+1と等しいことが好ましい。これは、レプリカビット線rplbtの寄生容量をビット線btおよびビット線bbの寄生容量と等しくするためである。レプリカセル選択線rplwlは、レプリカビット線rplbtと並行に、換言すれば、ワード線WLjと垂直に配置される。

インバータINV2は、基準タイミング信号tmg1の論理レベルを反転させた信号をレプリカセル駆動回路RWD1に出力する。レプリカセル駆動回路RWD1は、インバータINV2の出力に応答して、レプリカセル選択線rplwlを駆動する。レプリカセル選択線rplwlで選択されたレプリカセルRC1は、レプリカビット線rplbtにデータを出力する。レプリカビット線のデータに応答して、インバータINV1は、センスアンプ起動信号saeを出力する。

図10を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL11が有するダミーセルDCの回路構成を説明する。

p型トランジスタPU_Lのソースには電源電圧vddが印加され、そのドレインは、電源電圧vddに設定されたノードNLと接続される。n型トランジスタPD_LのドレインはノードNLと接続され、そのソースには電源電圧vssが印加される。p型トランジスタPU_Rのソースには電源電圧vddが印加され、そのドレインは、ノードNRと接続される。n型トランジスタPD_RのドレインはノードNRと接続され、そのソースには電源電圧vssが印加される。p型トランジスタPU_Lおよびn型トランジスタPD_LのゲートはノードNRと接続される。一方、p型トランジスタPU_Rおよびn型トランジスタPD_Rのゲートは、電源電圧vddに設定されたノードNLと接続される。即ち、ダミーセルDCのノードNLおよびノードNRは、各々、電源電圧vddおよび電源電圧vssに設定される。

n型トランジスタPG_LのソースおよびドレインはノードNLと接続される。n型トランジスタPG_Rのソース/ドレインのいずれか一方はノードNRと接続され、ソース/ドレインのいずれか他方はレプリカビット線rplbtと接続される。n型トランジスタPG_Lおよびn型トランジスタPG_Rのゲートには、電源電圧vssが印加される。即ち、ダミーセルDCは、ワード線WLjが非選択状態のメモリセルMCが、ビット線btまたはビット線bbに与える寄生容量を模擬する。

図10において、ノードNRおよびノードNLを、各々、電源電圧vddおよび電源電圧vssに設定しても良い。ノードNRを電源電圧vddとすることで、非選択メモリセルMCのリーク電流に起因する、選択メモリセルMCによるビット線対bt/bbへのセンスアンプ24で増幅可能な電位差が発生までの増加時間を反映させることが可能となる。

図11を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL11が有するレプリカセル駆動回路RWD1およびレプリカセルRC1の回路図を説明する。

レプリカセル駆動回路RWD1の回路図を説明する。

レプリカセル駆動回路RWD1は、p型トランジスタMp92およびn型トランジスタMn92で構成されるインバータである。p型トランジスタMp92のソースには、ワード線アシスト電圧wdrv_vddが印加され、そのドレインは、n型トランジスタMn92のドレインと接続される。n型トランジスタMn92のソースには、電源電圧vssが印加される。p型トランジスタMp92およびn型トランジスタMn92のゲートには、基準タイミング信号tmg1の論理レベルをインバータINV2で反転させた信号が印加される。レプリカセル駆動回路RWD1の出力は、レプリカセル選択線rplwlと接続される。

即ち、レプリカセル駆動回路RWD1は、ワードドライバ22が有するインバータと同様に、ハイレベルおよびロウレベルが、各々、ワード線アシスト電圧wdrv_vddおよび電源電圧vssである信号を出力する。

レプリカセルRC1の回路構成を説明する。

レプリカセルRC1の回路構成は、図10に示されるダミーセルDCの回路構成と、以下の点を除いて、同一である。即ち、ダミーセルDCが有するn型トランジスタPG_Rのゲートには、電源電圧vssが印加されているのに対し、レプリカセルRC1が有するp型トランジスタPG_Rのゲートは、レプリカセル選択線rplwlと接続される。

レプリカセル駆動回路RWD1およびレプリカセルRC1の動作を説明する。

制御回路CTLmが生成する基準タイミング信号tmg1がロウレベル(電源電圧vss)からハイレベル(電源電圧vdd)に変化すると、インバータINV2はレプリカセル駆動回路RWD1にロウレベルの信号を出力する。この出力信号に応答して、レプリカセル駆動回路RWD1は、レプリカセル選択線rplwlを電源電圧vssからワード線アシスト電圧wdrv_vddまで引き上げる。

レプリカセルRC1が有するp型トランジスタPG_Rのゲートには、ワード線アシスト電圧wdrv_vddが印加される。その結果、導通状態にあるn型トランジスタPG_Rおよびn型トランジスタPD_Rは、レプリカビット線rplbtの電荷を引き抜き、レプリカビット線rplbtの電圧は、電源電圧vddから電源電圧vssに向けて低下する。なお、レプリカセルRC1と接続されるレプリカビット線rplbtの電圧は、レプリカセル選択線rplwlが電源電圧vssからワード線アシスト電圧wdrv_vddに変化する前に、あらかじめ、図示しないプリチャージ回路で電源電圧vddに設定される。

レプリカビット線rplbtの電圧がインバータINV1の入力閾値より低くなると、インバータINV1は、センスアンプ起動信号saeの電圧をロウレベルからハイレベルに変化させる。このセンスアンプ起動信号saeに応答して、センスアンプ24は、選択メモリセルMCが選択ビット線対bt/bb間に出力する電圧の増幅動作を開始する。

レプリカセル遅延回路RDLY11のレプリカセルRC1は、メモリセルアレイMATに隣接させて、メモリセルMCと同一形状に配置することが可能である。従って、チップ面積の増加を抑制しつつ、選択メモリセルMCと接続されるビット線対bt/bbのデータがセンスアンプ24に入力されるタイミングと、センスアンプ24の起動タイミングとを整合させることが可能となる。

<実施の形態1の変形例2>

図12を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の変形例2であるメモリモジュールMMDL12の回路図を説明する。

メモリモジュールMMDL12は、メモリモジュールMMDL1と以下の点で相違する。即ち、メモリモジュールMMDL1が備えていた遅延回路DLY1に代えて、インバータINV2、レプリカセル駆動回路RWD1、レプリカセル遅延回路RDLY12、n型トランジスタMn12、およびバッファA1を備える。メモリモジュールMMDL12において、メモリモジュールMMDL1と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

メモリモジュールMMDL12は、ワードデコーダ21、ワードドライバ22、メモリセルアレイMAT、IO部IO、アシスト電圧生成回路VGEN、セル電圧制御回路MCNT、および制御回路CTLmと、レプリカセル駆動回路RWD1、レプリカセル遅延回路RDLY12、インバータINV2、n型トランジスタMn12、およびバッファA1と、を有する。

レプリカセル駆動回路RWD1には、アシスト電圧生成回路VGENが生成するワード線アシスト電圧wdrv_vddが印加される。レプリカセル駆動回路RWD1には、基準タイミング信号tmg1の論理レベルをインバータINV2で反転させた信号が印加される。

レプリカセル遅延回路RDLY12は、レプリカセル選択線rplwl、レプリカビット線rplbt、およびレプリカビット線rplbbに接続された複数のレプリカセルRC2と、レプリカビット線rplbtに接続された複数のダミーセルDCと、レプリカビット線rplbtおよびレプリカビット線rplbbに接続されたカレントミラー回路CM1と、を有する。レプリカセルRC2およびダミーセルDCを構成する各トランジスタは、メモリセルアレイMATが有するメモリセルMCを構成する対応する各トランジスタと同一の形状および配置を有することが好ましい。

レプリカセルRC2およびダミーセルDCの合計数は、メモリセルアレイMATのビット線対bt/bbと接続されるメモリセルMCの総数m+1と等しいことが好ましい。これは、レプリカビット線rplbtおよびレプリカビット線rplbbの寄生容量を、ビット線btおよびビット線bbの寄生容量と等しくするためである。レプリカセル選択線rplwlは、レプリカビット線rplbtおよびレプリカビット線rplbbと並行に、換言すれば、ワード線WLjと垂直に配置される。

インバータINV2は、基準タイミング信号tmg1の論理レベルを反転させた信号をレプリカセル駆動回路RWD1に出力する。レプリカセル駆動回路RWD1は、インバータINV2の出力に応答して、レプリカセル選択線rplwlを駆動する。レプリカセル選択線rplwlで選択されたレプリカセルRC2には、レプリカビット線rplbbを経由して、カレントミラー回路CM1から電流が供給される。同時に、カレントミラー回路CM1は、n型トランジスタMn12であらかじめ電源電圧vssに引き下げられていたレプリカビット線rplbtの電圧を上昇させる。レプリカビット線rplbtの電圧が論理閾値電圧より高くなると、バッファA1はセンスアンプ起動信号saeを出力する。

図13を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL12が有するレプリカセル駆動回路RWD1、レプリカセルRC2、およびカレントミラー回路CM1の回路構成を説明する。

レプリカセル駆動回路RWD1の回路構成は、図11に示される同一の符号が付されたものと同一であり、説明は省略する。

レプリカセルRC2の回路構成は、図3に示されるメモリセルMCの回路構成と、以下の点を除いて、同一である。即ち、p型トランジスタPU_Lおよびn型トランジスタPD_Lのゲートには、電源電圧vddが印加される。さらに、n型トランジスタPG_Rのゲートには電源電圧vssが印加される。

カレントミラー回路CM1は、ソースに電源電圧vddが印加されるとともに、互いのゲートが接続されたp型トランジスタMpbbおよびp型トランジスタMpbtを有する。p型トランジスタMpbbのドレインおよびゲートは、レプリカビット線rplbbと接続される。p型トランジスタMpbtのドレインは、レプリカビット線rplbtと接続される。即ち、カレントミラー回路CM1は、レプリカビット線rplbbに流出する電流に対して、p型トランジスタMpbbのゲート幅に対するp型トランジスタMpbtのゲート幅の比率(ミラー比)で決定される電流を、レプリカビット線rplbtに供給する。

図14および図13を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL12が有するレプリカセルRC2およびカレントミラー回路CM1の動作を説明する。

制御回路CTLmが生成する基準タイミング信号tmg1がロウレベル(電源電圧vss)からハイレベル(電源電圧vdd)に変化すると、インバータINV2はレプリカセル駆動回路RWD1にロウレベルの信号を出力する。この出力信号に応答して、レプリカセル駆動回路RWD1は、レプリカセル選択線rplwlを電源電圧vssからワード線アシスト電圧wdrv_vddまで引き上げる(図14)。

ノードNLおよびノードNRを、各々、ロウレベルおよびハイレベルに保持するレプリカセルRC2のn型トランジスタPG_Lのゲートには、ワード線アシスト電圧wdrv_vddが印加される。その結果、カレントミラー回路CM1のp型トランジスタMpbbは、レプリカビット線rplbbを経由して、レプリカセルRC2に電流を供給する。レプリカビット線rplbbの電圧は、レプリカセルRC2のn型トランジスタPG_Lおよびn型トランジスタPD_Lの導通抵抗に依存する値を維持する(図14)。

一方、レプリカセルRC2のn型トランジスタPG_Rは非導通状態を維持する。n型トランジスタMn12は、レプリカセル選択線rplwlでレプリカセルRC2を起動する前に、レプリカビット線rplbtの電圧を電源電圧vssに設定する。カレントミラー回路CM1のp型トランジスタMpbbがレプリカビット線rplbbに電流供給を開始すると、カレントミラー回路CM1のp型トランジスタMpbtは、レプリカビット線rplbtに充電電流の供給を開始する。レプリカビット線rplbtの電圧は、電源電圧vssから電源電圧vddへ上昇する(図14)。

バッファA1は、レプリカビット線rplbtの電圧が論理閾値電圧を超えると、センスアンプ起動信号saeの電圧をロウレベルからハイレベルに変化させる(図14)。このセンスアンプ起動信号saeに応答して、センスアンプ24は、選択メモリセルMCが選択ビット線対bt/bb間に出力する電圧の増幅動作を開始する。

レプリカビット線rplbtの電圧が電源電圧vssから電源電圧vddまで上昇する速度は、レプリカビット線rplbtと接続されるレプリカセルRC2に起因する寄生容量およびレプリカビット線rplbtの寄生容量の値と、カレントミラー回路CM1の電流駆動能力に依存する。従って、メモリモジュールMMDL12が有するレプリカセル遅延回路RDLY12によれば、レプリカセルRC2の数を増やすことで、ランダムにばらつく各トランジスタの閾値電圧による遅延量のばらつきを抑制しつつ、さらに、カレントミラー回路MC1を構成するp型トランジスタMpbtおよびp型トランジスタMpbbのトランジスタ幅Wの比を調整することで、センスアンプ24の起動タイミングを最適化することが可能となる。

従来のレプリカセル遅延回路において、レプリカセルの数を増やしつつセンスアンプの起動タイミングを調整するには、レプリカビット線の寄生容量を増やす必要があった。その結果、チップの面積と消費電力が増加するという問題を有していた。

<実施の形態1の変形例3>

図15を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の変形例3であるメモリモジュールMMDL13のブロック構成を説明する。

メモリモジュールMMDL13は、図9に示されるメモリモジュールMMDL11と以下に点で相違する。即ち、メモリモジュールMMDL13は、メモリモジュールMMDL11が備えていたアシスト電圧生成回路VGENを省略した構成を有する。メモリモジュールMMDL13において、メモリモジュールMMDL11と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

制御回路CTLmが生成するアドレス信号adr[x:0]に基づき、ワードデコーダ21およびワードドライバ22はメモリセルMCを選択する。この選択されたメモリセルMCが、ビット線対bt/bbを介して、センスアンプ24に入力電圧を印加するタイミングと、センスアンプ起動信号saeによるセンスアンプ24の起動タイミングの不整合は、選択ワード線WLjに電源電圧vddを印加するメモリセルモジュールでも懸念される。

図15に示されるレプリカセル駆動回路RDW1は、ワードドライバ22と同様に、電源電圧vddが印加される。メモリセルMCの出力データがセンスアンプ24に印加されるタイミングと、センスアンプ起動信号saeによるセンスアンプ24の起動タイミングが、メモリセルMCの特性ばらつき等が原因で整合しない場合、レプリカセル遅延回路RDLY11が有するレプリカセルRC1の個数を調整することで両タイミングを整合させることが可能である。

<実施の形態1の変形例4>

図16を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の変形例4であるメモリモジュールMMDL14の回路図を説明する。

メモリモジュールMMDL14は、図12に示されるメモリモジュールMMDL12と以下の点で相違する。即ち、メモリモジュールMMDL14は、メモリモジュールMMDL12が備えていたレプリカセル駆動回路RWD1に代えて、レプリカセル駆動回路RWD14を備える。さらに、レプリカセル遅延回路RDLY12に代えて、レプリカセル遅延回路RDLY14を備える。メモリモジュールMMDL14において、メモリモジュールMMDL12と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

レプリカセル遅延回路RDLY14は、レプリカセル選択線rplwl、レプリカビット線rplbt、レプリカビット線rplbb、ダミーセルDC、レプリカセルRC2、およびカレントミラー回路CM14を有する。

図17を参照して、実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールMMDL1の変形例4であるメモリモジュールMMDL14が有するレプリカセル駆動回路RWD14およびカレントミラー回路CM14の回路図を説明する。

レプリカセル駆動回路RWD14は、ワード線アシスト電圧wdrv_vddを電源電圧とする2入力NAND回路である。レプリカセル駆動回路RWD14は、p型トランジスタMp92、p型トランジスタMp93、n型トランジスタMn92、およびn型トランジスタMn93を有する。p型トランジスタMp93のソースにはワード線アシスト電圧wdrv_vddが印加され、そのドレインは、p型トランジスタMp92のソースと接続される。p型トランジスタMp92のドレインは、n型トランジスタMn92およびn型トランジスタMn93のドレインと接続される。n型トランジスタMn92およびn型トランジスタMn93のソースには、電源電圧vssが印加される。

p型トランジスタMp92およびn型トランジスタMn92のゲートには、基準タイミング信号tmg1の論理レベルをインバータINV2で反転させた信号が印加される。p型トランジスタMp93およびn型トランジスタMn93のゲートには、センスアンプ起動信号saeが印加される。p型トランジスタMp92のドレインは、レプリカセル選択線rplwlと接続される。

カレントミラー回路CM14は、カレントミラー回路CM1および制御回路180を有する。カレントミラー回路CM1は、ソースに電源電圧vddが印加されたp型トランジスタMpbbおよびp型トランジスタMpbtを有する。p型トランジスタMpbbのゲートおよびドレインはレプリカビット線rplbbと接続される。p型トランジスタMpbtのゲートはp型トランジスタMpbbのゲートと接続される。p型トランジスタMpbtのドレインは、レプリカビット線rplbtと接続される。

制御回路180は、p型トランジスタMp94、NANDゲート94、およびインバータ93を有する。p型トランジスタMp94のソースには電源電圧vddが印加され、ドレインはレプリカビット線rplbtと接続される。インバータ93は、インバータINV2の出力の論理レベルを反転させた信号(基準タイミング信号tmg1と同相)を、NANDゲート94の一方の入力端子へ出力する。NANDゲート94の他方の入力端子には、センスアンプ起動信号saeが印加される。NANDゲート94の出力は、p型トランジスタMp94のゲートに印加される。

レプリカビット線rplbtおよびレプリカビット線rplbb間には、レプリカセルRC2が接続される。レプリカセルRC2は、レプリカセル選択線rplwlで起動される。このレプリカセルRC2の具体的構成は、図13に示される。

バッファA1は、レプリカビット線rplbtの立ち上がりに応じて、センスアンプ起動信号saeを生成する。このセンスアンプ起動信号saeは、センスアンプ24に印加されるとともに、レプリカセル駆動回路RWD14のn型トランジスタMn93およびp型トランジスタMp93のゲートと、制御回路180のNANDゲート94の入力端子と、に印加される。n型トランジスタMn12は、基準タイミング信号tmg1に応答して、レプリカビット線rplbtの電圧を電源電圧vssに初期設定する。

レプリカセル駆動回路RWD14およびカレントミラー回路CM14の動作を説明する。

基準タイミング信号tmg1がロウレベルに設定されている場合、n型トランジスタMn12は、レプリカビット線rplbtの電圧をロウレベル(電源電圧vss)に設定する。また、レプリカセル駆動回路RWD14は、レプリカセル選択線rplwlの電圧をロウレベルに設定する。一方、レプリカセルRC2のn型トランジスタPG_Lは非導通状態にあるため(図13参照)、レプリカビット線rplbbの電圧は、ほぼ電源電圧vddに設定される。

基準タイミング信号tmg1がロウレベルからハイレベルに変化すると、レプリカセル駆動回路RWD14は、レプリカセル選択線rplwlをロウレベルからハイレベルに立ち上げる。このレプリカセル選択線rplwlの変化に基づき、レプリカセルRC2のn型トランジスタPG_Lは、導通状態に変化する。レプリカビット線rplbtは、n型トランジスタMn12による電源電圧vssの印加から解放される。

カレントミラー回路CM1のp型トランジスタMpbbは、レプリカビット線rplbbを介して、レプリカセルRC2へ電流を供給する。p型トランジスタMpbtは、p型トランジスタMpbbに流れる電流に対して、p型トランジスタMpbtとp型トランジスタMpbbのトランジスタ幅Wの比に応じた電流で、レプリカビット線rplbtをロウレベルからハイレベルに引き上げる。バッファA1は、レプリカビット線rplbtの立ち上がりに応じて、センスアンプ起動信号saeを生成する。センスアンプ起動信号saeのロウレベルからハイレベルへの立ち上がりエッジに応答して、センスアンプ24は起動される。起動されたセンスアンプ24は、ビット線対bt/bb間電圧の増幅動作を開始する。

センスアンプ起動信号saeがロウレベルからハイレベルに変化すると、レプリカセル駆動回路RWD14は、レプリカセル選択線rplwlをハイレベルからロウレベルに変化させる。この変化に応答して、カレントミラー回路CM1のレプリカセルRC2への電流供給、さらには、レプリカビット線rplbtへの充電電流の供給は停止する。一方、NANDゲート94への両入力信号は共にハイレベルとなるので、p型トランジスタMp92のゲートにはロウレベルが印加される。その結果、レプリカビット線rplbtは、基準タイミング信号tmg1がロウレベルになるまで、ハイレベルに維持される。

メモリモジュールMMDL14によれば、カレントミラー回路CM1によるレプリカビット線対rplbt/rplbbへの電流供給は、センスアンプ起動信号saeによりセンスアンプ24が起動された後、停止される。従って、カレントミラー回路でセンスアンプ起動信号saeを生成する場合であっても、カレントミラー回路の電流は必要な期間のみ発生する。その結果、半導体装置LSI_1の消費電力は低減される。

<実施の形態2>

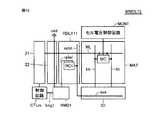

図18を参照して、実施の形態2に係る半導体装置LSI_2のブロック構成を説明する。

半導体装置LSI_2(チップ記載する場合もある)は、DVFS(Dynamic Voltage and Frequency Scaling)機能を備える、SOCである。

半導体装置LSI_2は、IPモジュール2、メモリモジュールMMDL2、および制御回路CTL_IPを備える。IPモジュール2およびメモリモジュールMMDL2間は、バス3を介して、アドレス、データ、および各種制御信号を送受信する。レギュレータ回路1は、印加された電源電圧vdd_exに基づき、IPモジュール2およびメモリモジュールMMDL2へ、各々、電源電圧vdd_cpuおよび電源電圧vddを印加する。図1において、レギュレータ回路1は、半導体装置LSI_1とは別チップで構成される例を示す。必要に応じ、レギュレータ回路1は、半導体装置LSI_1に内蔵されても良い。

制御回路CTL_IPは、制御信号cntrl_vおよび制御信号cntrl_ipを、各々、レギュレータ回路1およびIPモジュール2へ出力する。制御回路CTL_IPは、IPモジュール2の使用状況に応じ、制御信号cntrl_vに基づき、レギュレータ回路1が生成する電源電圧vdd_cpuの値を変更する。制御回路CTL_IPは、さらに、レギュレータ回路1の制御に合わせて、制御信号cntrl_ipに基づき、IPモジュール2の動作条件を制御する。IPモジュール2は、IPモジュール2の動作条件に応じて、制御信号cntrl[1:0]に基づき、メモリモジュールMMDL2の動作条件を制御する。

メモリモジュールMMDL2は、ワードデコーダ21、ワードドライバ22、メモリセルアレイMAT、IO部IO、アシスト電圧生成回路VGEN2、セル電圧制御回路MCNT、制御回路CTLm、および遅延回路DLY2を有する。制御回路CTLmは、基準タイミング信号tmg1を遅延回路DLY2へ出力する。遅延回路DLY2は、アシスト電圧生成回路VGEN2の出力電圧に応答して、基準タイミング信号を所定時間遅延させたセンスアンプ起動信号saeを生成する。

IPモジュール2は、IPモジュール2の動作条件に適合するように、制御信号cntrl[1:0]に基づき、アシスト電圧生成回路VGEN2および遅延回路DLY2の特性を制御する。なお、この制御信号cntrl[1:0]によるメモリモジュールMMDL2の動作条件の制御は、DVFS機能に限られない。例えば、チップの製造プロセスに起因するトランジスタ等の回路素子の特性変動に応じて、制御信号cntrl[1:0]に基づき、メモリモジュールMMDL2の動作条件を設定しても良い。

図19を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2の回路図を説明する。

メモリモジュールMMDL2は、図2に示される実施の形態1に係るメモリモジュールMMDL1と、以下の点で相違する。即ち、メモリモジュールMMDL1が備えていたアシスト電圧生成回路VGENに代えて、アシスト電圧生成回路VGEN2を備える。さらに、メモリモジュールMMD1Lが備えていた遅延回路DLY1に代えて、遅延回路DLY2を備える。アシスト電圧生成回路VGEN2および遅延回路DLY2は、制御信号cntrl[1:0]に基づき、その特性が制御される。メモリモジュールMMDL2において、メモリモジュールMMDL1と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

図20を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2が有する遅延回路DLY2の回路図を説明する。

遅延回路DLY2は、サブ遅延回路DLY21a、サブ遅延回路DLY21b、セレクタ200、およびセレクタ201を有する。

サブ遅延回路DLY21aおよびサブ遅延回路DLY21bは、p型トランジスタMp81およびn型トランジスタMn81で構成されるインバータを、各々、所定段数、直列接続した遅延回路である。

サブ遅延回路DLY21aにおいて、p型トランジスタMp81のソースにはワード線アシスト電圧wdrv_vddが印加され、n型トランジスタMn81のソースには電源電圧vssが印加される。初段のインバータを構成するp型トランジスタMp81およびn型トランジスタMn81のゲートには、基準タイミング信号tmg1が印加される。最終段のインバータは、ワード線アシスト電圧wdrv_vddに依存する遅延時間経過後、基準タイミング信号tmg1を出力する。

セレクタ200は、制御信号cntrl[0]に基づき、基準タイミング信号tmg1またはサブ遅延回路DLY21aで所定時間遅延させた基準タイミング信号tmg1のいずれか一方を選択して出力する。

サブ遅延回路DLY21bにおいて、p型トランジスタMp81のソースにはワード線アシスト電圧wdrv_vddが印加され、n型トランジスタMn81のソースには電源電圧vssが印加される。初段のインバータを構成するp型トランジスタMp81およびn型トランジスタMn81のゲートには、セレクタ200の出力信号が印加される。最終段のインバータは、ワード線アシスト電圧wdrv_vddに依存する遅延時間経過後、サブ遅延回路DLY21aの出力信号を出力する。

セレクタ201は、制御信号cntrl[1]に基づき、サブ遅延回路DLY21bの出力信号またはセレクタ200の出力信号のいずれか一方を選択して、センスアンプ起動信号saeとして出力する。

上記回路動作から理解される通り、遅延回路DLY2は、2値の値を有する制御信号cntrl[0]および制御信号cntrl[1]に基づき、4つの異なる遅延時間が設定可能な遅延回路として機能する。例えば、制御信号cntrl[0]をロウレベルおよびハイレベルに設定した場合、セレクタ200は、各々、基準タイミング信号tmg1およびサブ遅延回路DLY21aの出力信号を出力する。また、制御信号cntrl[1]をロウレベルおよびハイレベルに設定した場合、セレクタ201は、各々、セレクタ200の出力信号およびサブ遅延回路DLY21bの出力信号を出力する。

半導体装置LSI_2の動作状態に応じて、メモリモジュールMMDL2に印加される電源電圧vddを低下させた場合、SNMを確保するため、電源電圧vddとワード線アシスト電圧wdrv_vddとの電圧差は、電源電圧vddを低下させる前よりも大きく設定する必要がある。また、電源電圧vddが十分高い場合、ワード線アシスト電圧wdrv_vddと電源電圧vddとを、同程度に設定し得ることも考えられる。

そのように電源電圧vddの設定値に応じてワード線アシスト電圧wdrv_vddの電圧値を変更した場合、ワーストセルがセンスアンプ24で増幅可能な電位差をビット線対bt/bbに発生するまでの遅延時間および遅延回路DLY2の遅延量の、ワード線アシスト電圧wdrv_vdd依存性が異なる場合もある。その場合、遅延回路DLY2の遅延段数を制御信号cntrl[1:0]で切り替えることで、遅延量の最適化、即ち、センスアンプ24の起動タイミングの最適化を行うことが可能となる。

なお、図20に示される遅延回路DLY2が有するサブ遅延回路DLY21aおよびサブ遅延回路DLY21bのインバータへ印加する電源電圧を、ワード線アシスト電圧wdrv_vddに代えて、図7(b)のサブ遅延回路DLY12bのように、電源電圧vddに変更しても良い。その結果、遅延回路DLY2の遅延時間を制御するワード線アシスト電圧wdrv_vddにおけるインバータの動作電流に起因するノイズが抑制される。

図21を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2が有するアシスト電圧生成回路VGEN2の動作タイミングを説明する。

アシスト電圧生成回路VGEN2は、電源電圧vddを降圧して、ワード線アシスト電圧wdrv_vddを生成する。電源電圧vddの値は、制御回路CTL_IPが出力する制御信号cntrl_vに基づき、レギュレータ回路1が設定する(図18参照)。一方、アシスト電圧生成回路VGEN2が生成するワード線アシスト電圧wdrv_vddの値は、制御信号cntrl[1:0]に基づき設定される。

期間T00において、制御信号cntrl[1]および制御信号cntrl[0]は、ともにロウレベル(電源電圧vss)に設定される。この期間T00において、電源電圧vddは、例えば、1.0Vに設定され、ワード線アシスト電圧wdrv_vddは1.0Vより降下した値に設定される。

期間T01において、制御信号cntrl[1]および制御信号cntrl[0]は、各々、ロウレベルおよびハイレベルに設定される。期間T10において制御信号cntrl[1]および制御信号cntrl[0]は、各々、ハイレベルおよびロウレベルに設定される。期間T11において、制御信号cntrl[1]および制御信号cntrl[0]は、いずれもハイレベルに設定される。期間T00〜期間T11に変化するに従い、電源電圧vddは、1.0Vから、適宜設定された値に順次低下する。同様に、ワード線アシスト電圧wdrv_vddも、期間T00〜期間T11に変化するに従い、期間T00で設定された値から、適宜設定された値に順次低下する。

各期間T00〜期間T11における電源電圧vddとワード線アシスト電圧wdrv_vddの差、即ち、電源電圧vddに対するワード線アシスト電圧wdrv_vddの降下電圧値は、電源電圧vddの低下とともに、増加するように設定される。これは、メモリセルMCに印加される電源電圧vddの低下に伴うSNMの悪化を軽減するため、ワード線アシスト電圧wdrv_vddの低下量を、電源電圧vddの低下量より大きく設定するためである。

メモリモジュールMMDL2が有するアシスト電圧生成回路VGEN2は、制御信号cntrl[1:0]に応答して、ワード線アシスト電圧wdrv_vddの値を変化させる。遅延回路DLY2は、この制御信号cntrl[1:0]に応答して、設定されたワード線アシスト電圧wdrv_vddの値に最適なタイミングでセンスアンプ起動信号saeを生成する。この結果、メモリモジュールMMDL2のアクセス時間短縮および消費電力低減が実現される。

<実施の形態2の変形例1>

図22を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2の変形例1であるメモリモジュールMMDL21のブロック構成を説明する。

メモリモジュールMMDL21は、メモリモジュールMMDL2と以下の点で相違する。即ち、メモリモジュールMMDL2が備えていた遅延回路DLY2に代えて、レプリカセル駆動回路RWD21およびレプリカセル遅延回路RDLY21を備える。メモリモジュールMMDL21において、メモリモジュールMMDL2と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

図23を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL21の回路図を説明する。

メモリモジュールMMDL21は、セレクタSEL、レプリカセル駆動回路RWD21、レプリカセル遅延回路RDLY21、およびインバータINV1を有する。

ワード線アシスト電圧wdrv_vddが印加されるレプリカセル駆動回路RWD21は、レプリカセル選択線rplwl1またはレプリカセル選択線rplwl2を駆動する。セレクタSELは、制御信号cntrl[1:0]に基づき、レプリカセル駆動回路RWD21が駆動するレプリカセル選択線rplwl1またはレプリカセル選択線rplwl2を選択する。

レプリカセル遅延回路RDLY21は、レプリカビット線rplbtおよびレプリカセル選択線rplwl1と接続されたレプリカセルRC1と、レプリカビット線rplbtおよびレプリカセル選択線rplwl2と接続されたレプリカセルRC1と、レプリカビット線rplbtと接続されたダミーセルDCと、を有する。インバータINV1は、レプリカビット線rplbtの論理レベルを反転させて、センスアンプ起動信号saeを生成する。

図24を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2が有するセレクタSELおよびレプリカセル駆動回路RWD21の回路図を説明する。

セレクタSELおよびレプリカセル駆動回路RWD21の構成を説明する。

セレクタSELは、NANDゲート101およびNANDゲート102を有する。NANDゲート101およびNANDゲート102の一方の入力端子には、基準タイミング信号tmg1が印加される。NANDゲート101の他方の入力端子には、制御信号cntrl[1]が印加される。NANDゲート102の他方の入力端子には、制御信号cntrl[0]が印加される。

レプリカセル駆動回路RWD21は、p型トランジスタMp101およびn型トランジスタMn101で構成されるインバータを2つ有する。p型トランジスタMp101のソースにはワード線アシスト電圧wdrv_vddが印加され、そのドレインは、n型トランジスタMn101のドレインが接続される。n型トランジスタMn101のソースには電源電圧vssが印加される。一方のインバータが有するp型トランジスタMp101およびn型トランジスタMn101のゲートには、NANDゲート101の出力が印加される。他方のインバータが有するp型トランジスタMp101およびn型トランジスタMn101のゲートには、NANDゲート102の出力が印加される。一方のインバータの出力はレプリカセル選択線rplwl2と接続され、他方のインバータの出力はレプリカセル選択線rplwl1と接続される。

セレクタSELおよびレプリカセル駆動回路RWD21の動作を説明する。

セレクタSELは、制御信号cntrl[1]および制御信号cntrl[0]に基づき、基準タイミング信号tmg1を、レプリカセル駆動回路RWD21が有する2つのインバータのいずれか一方または両方に伝達するか否かを選択する。レプリカセル駆動回路RWD21が有する1つのインバータは、ハイレベルに設定された制御信号cntrl[0]に応答して、レプリカセル選択線rplwl1をハイレベルに引き上げる。レプリカセル選択線rplwl1がハイレベルに変化すると、グループG2のレプリカセルRC1は、レプリカビット線rplbtの電圧を電源電圧vddから電源電圧vssに引き下げる。同様に、ハイレベルに設定された制御信号cntrl[1]に応答して、グループG1のレプリカセルRC1は、レプリカビット線rplbtの電圧を電源電圧vssに引き下げる。

電源電圧vddが低下するに従い、メモリセルMCの電流駆動能力は低下する。この電流駆動能力の低下は、メモリセルMCが有するトランジスタの閾値電圧が高い場合、特に顕著となる。ワードドライバ22が、その高い閾値電圧を有するメモリセルMCを選択した場合を想定する。この場合、メモリセルMCがセンスアンプ24へデータを出力するタイミングは、他のメモリセルMCを選択した場合と比較して、一番遅くなる。従って、センスアンプ起動信号saeを生成するタイミングも、それに合わせる必要がある。

レプリカビット線rplbtの電圧を引き下げるグループG1およびグループG2は、複数のレプリカセルRC1で構成される。従って、グループG1またはグループG2を有するレプリカセル遅延回路RDLY21は、平均的な閾値電圧を有するメモリセルがセンスアンプ24へデータを出力するタイミングを模擬するものと考えられる。このレプリカセル遅延回路RDLY21が有するグループG1またはグループG2を、電源電圧vddの違いに応じて選択することにより、センスアンプ起動信号saeの生成タイミングを最適化することが可能となる。なお、図24には示されていないが、制御信号cntrl[1:0]の設定値に関係なく、基準タイミング信号tmg1がハイレベルになると、常にレプリカビット線rplbtの電圧を引き下げるレプリカセルのグループを設けても良い。

<実施の形態2の変形例2>

図25を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2の変形例2であるメモリモジュールMMDL22の回路図を説明する。

メモリモジュールMMDL22は、メモリモジュールMMDL2と以下の点で相違する。即ち、メモリモジュールMMDL2が備えていた遅延回路DLY2に代えて、レプリカセル駆動回路RWD1、レプリカセル遅延回路RDLY22、インバータINV1、およびインバータINV2を備える。メモリモジュールMMDL22において、メモリモジュールMMDL2と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

インバータINV2は、基準タイミング信号tmg1の論理レベルを反転させた信号をレプリカセル駆動回路RWD1へ出力する。ワード線アシスト電圧wdrv_vddが印加されるレプリカセル駆動回路RWD1は、レプリカセル選択線rplwlを駆動する。アシスト電圧生成回路VGEN2は、2値の値を有する制御信号cntrl[0]および制御信号cntrl[1]の組合わせに基づき、出力するワード線アシスト電圧wdrv_vddの電圧値を変更する。

レプリカセル遅延回路RDLY22は、レプリカセル選択線rplwlおよびレプリカビット線rplbtと接続された複数のレプリカセルRC3と、レプリカビット線rplbtと接続された複数のダミーセルDCを有する。インバータINV1は、レプリカビット線rplbtの論理レベルを反転させ、センスアンプ起動信号saeを生成する。

図26を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL22が有するレプリカセル駆動回路RWD1およびレプリカセルRC3の回路図を説明する。

レプリカセル駆動回路RWD1は、p型トランジスタMp92およびn型トランジスタMn92で構成されるインバータであり、レプリカセル選択線rplwlを駆動する。p型トランジスタMp92のソースにはワード線アシスト電圧wdrv_vddが印加され、そのドレインはn型トランジスタMn92のドレインと接続される。n型トランジスタMn92のソースには電源電圧vssが印加される。p型トランジスタMp92およびn型トランジスタMn92のゲートには、インバータINV2で論理レベルを反転された基準タイミング信号tmg1が印加される。

レプリカセルRC3の回路構成を説明する。

レプリカセルRC3は、p型トランジスタPU_L、p型トランジスタPU_R、n型トランジスタPD_L、n型トランジスタPD_R、n型トランジスタPG_L、およびn型トランジスタPG_Rを有する。p型トランジスタPU_Lのソースには電源電圧vddが印加され、そのゲートおよびドレインは、各々、ノードNLおよびノードNRと接続される。p型トランジスタPU_Rのソースには電源電圧vddが印加され、そのゲートおよびドレインは、各々、ノードNRおよびノードNLと接続される。

n型トランジスタPD_Lのソースには電源電圧vssが印加され、そのゲートはノードNLと接続される。n型トランジスタPD_Lのドレインは、n型トランジスタPG_Lのソース/ドレインの一方と接続される。n型トランジスタPG_Lのソース/ドレインの他方およびゲートには、電源電圧vssが印加される。n型トランジスタPD_Rのソースには電源電圧vssが印加され、そのゲートはノードNRと接続される。n型トランジスタPD_Rのドレインは、n型トランジスタPG_Rのソース/ドレインの一方と接続される。n型トランジスタPG_Rのソース/ドレインの他方はレプリカビット線rplbtと接続される。n型トランジスタPG_Rのゲートには、制御信号cntrl[0]または制御信号cntrl[1]のいずれか一方が印加される。

レプリカセル遅延回路RDLY22が有するレプリカセルRC3は、第1グループおよび第2グループに分けられる。第1グループに属するレプリカセルRC3のノードNRには、制御信号cntrl[0]が印加される。第2のグループに属するレプリカセルRC3のノードNRには、制御信号cntrl[1]が印加される。両グループに属するレプリカセルRC3は、レプリカビット線rplbtと接続される。

レプリカセルRC3の動作を説明する。

レプリカセル駆動回路RWD1は、基準タイミング信号tmg1がロウレベルからハイレベルに変化すると、レプリカセル選択線rplwlをハイレベルに引き上げる。その結果、第1グループおよび第2グループのレプリカセルRC3が有するn型トランジスタPG_Rは導通状態となる。制御信号cntrl[0]がハイレベルに設定されている場合、第1グループに属する複数のレプリカセルRC3のn型トランジスタPG_Rおよびn型トランジスタPD_Rは、あらかじめ電源電圧vddにプリチャージされているレプリカビット線rplbtを電源電圧vssに向けて降下させる。一方、制御信号cntrl[1]がロウレベルに設定されている場合、第2グループの属する複数のレプリカセルRC3は、n型トランジスタPD_Rが非導通状態にあるため、レプリカビット線rplbtの電圧に影響を及ぼさない。

アシスト電圧生成回路VGEN2は、レギュレータ回路1による電源電圧vddの設定値、制御信号cntrl[0]、および制御信号cntrl[1]に基づき、ワードドライバ22およびレプリカセル駆動回路RWD1に印加するワード線アシスト電圧wdrv_vddの値を調整する。レプリカセル遅延回路RDLY22は、制御信号cntrl[0]および制御信号cntrl[1]に基づき、レプリカビット線rplbtを駆動するレプリカセルRC3の数を、セレクタ等の制御回路を介さずに、制御信号cntrl[0]および制御信号cntrl[1]により、直接調整する。その結果、レプリカセル遅延回路RDLY22を駆動するレプリカセル駆動回路RWD1の構成を簡略しつつ、かつ、トランジスタの閾値電圧のバラツキに対して最適なセンスアンプ起動信号saeを生成するメモリモジュールMMDL22を有する半導体装置LSI_2を実現することが可能となる。

<実施の形態2の変形例3>

図27を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL2の変形例3であるメモリモジュールMMDL23の回路図を説明する。

メモリモジュールMMDL23は、メモリモジュールMMDL2と以下の点で相違する。即ち、メモリモジュールMMDL2が備えていた遅延回路DLY2に代えて、レプリカセル駆動回路RWD1、レプリカセル遅延回路RDLY23、インバータINV2、バッファA1、およびn型トランジスタMn12を備える。メモリモジュールMMDL23において、メモリモジュールMMDL2と同一の符号が付されたものは、同一の構成を有し、それらの重複説明は行わない。

インバータINV2は、基準タイミング信号tmg1の論理レベルを反転させた信号をレプリカセル駆動回路RWD1へ出力する。ワード線アシスト電圧wdrv_vddが印加されるレプリカセル駆動回路RWD1は、レプリカセル選択線rplwlを駆動する。アシスト電圧生成回路VGEN2は、制御信号cntrl[0]および信号cntrl[1]に基づき、出力するワード線アシスト電圧wdrv_vddの電圧値を変更する。

レプリカセル遅延回路RDLY23は、レプリカセル選択線rplwl、レプリカビット線rplbt、およびレプリカビット線rplbbと接続された複数のレプリカセルRC2と、レプリカビット線rplbtと接続された複数のダミーセルDCを有する。レプリカセル遅延回路RDLY23は、さらに、カレントミラー回路CM3を有する。カレントミラー回路CM3は、制御信号cntrl[0]および制御信号cntrl[1]が印加されるとともに、レプリカビット線rplbbと接続される。

バッファA1は、レプリカビット線rplbtの電圧の立ち上がりに応じて、センスアンプ起動信号saeを生成する。n型トランジスタMn12は、基準タイミング信号tmg1に応答して、レプリカビット線rplbtの電圧を電源電圧vssに設定する。

図28を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL23が有するカレントミラー回路CM3の回路図を説明する。

レプリカセル駆動回路RWD1の構成は、図26に示されるものと同一である。さらに、レプリカセルRC2の構成は、図13に示されるものと同一である。

カレントミラー回路CM3の構成を説明する。

カレントミラー回路CM3は、p型トランジスタMp111〜Mp116を有する。

p型トランジスタMp111のソースには電源電圧vddが印加され、ゲートにはセンスアンプ起動信号saeが印加され、ドレインはp型トランジスタMp114のソースと接続される。p型トランジスタMp114のゲートおよびドレインはレプリカビット線rplbbと接続される。p型トランジスタMp112のソースには電源電圧vddが印加され、ゲートには制御信号cntrl[1]が印加され、ドレインはp型トランジスタMp115のソースと接続される。p型トランジスタMp115のゲートはレプリカビット線rplbbと接続され、ドレインはレプリカビット線rplbtと接続される。即ち、p型トランジスタMp111、p型トランジスタMp114、p型トランジスタMp112、およびp型トランジスタMp115は、第1のカレントミラー回路を構成する。

p型トランジスタMp113のソースには電源電圧vddが印加され、ゲートには制御信号cntrl[0]が印加され、ドレインはp型トランジスタMp116のソースと接続される。p型トランジスタMp116のゲートはレプリカビット線rplbbと接続され、ドレインはレプリカビット線rplbtと接続される。即ち、p型トランジスタMp111、p型トランジスタMp114、p型トランジスタMp113、およびp型トランジスタMp116は、第2のカレントミラー回路を構成する。

カレントミラー回路CM3の動作を説明する。

基準タイミング信号tmg1がロウレベルに設定されているとき、レプリカセル駆動回路RWD1は、レプリカセル選択線rplwlをロウレベル(電源電圧vss)に設定する。レプリカビット線rplbtは、n型トランジスタMn12によりロウレベルに設定される。バッファA1は、レプリカビット線rplbtの設定電圧(ロウレベル)に基づき、センスアンプ起動信号saeをロウレベルに設定する。このとき、レプリカセルRC2のn型トランジスタPG_Lは非導通状態にあるため、p型トランジスタMp111およびp型トランジスタMp114は、レプリカビット線rplbbに電流を供給しない。その結果、第1のカレントミラー回路および第2のカレントミラー回路は、いずれも、レプリカビット線rplbtに電流を供給しない。

基準タイミング信号tmg1がロウレベルからハイレベルに変化すると、レプリカセル駆動回路RWD1は、レプリカセル選択線rplwlをハイレベル(電源電圧vdd)に引き上げる。すると、レプリカセルRC2のn型トランジスタPG_Lが導通状態になるため、カレントミラー回路CM3のp型トランジスタMp111およびp型トランジスタMp114は、レプリカビット線rplbbを介して、レプリカセルRC2へ電流供給を開始する。このレプリカセルRC2による電流供給により、電源電圧vssに設定されていたレプリカビット線rplbbの電圧は、電源電圧vddに向けて上昇を開始する。

一方、電源電圧vssに設定されていたレプリカビット線rplbtは、制御信号cntrl[0]/cntrl[1]に基づき選択される第1のカレントミラー回路または第2のカレントミラー回路のいずれか一方、または両方により、電源電圧vddに向けて上昇を開始する。制御信号cntrl[1]をロウレベル、制御信号cntrl[0]をハイレベルに設定すると、p型トランジスタMp112は導通状態となる。すると、第1のカレントミラー回路は、レプリカビット線rplbtへの電流供給を開始する。第1のカレントミラー回路によりレプリカビット線rplbtの電圧が電源電圧vddに向けて上昇を開始すると、バッファA1は、センスアンプ起動信号saeをロウレベルからハイレベルに変化させる。

制御信号cntrl[1]をハイレベル、制御信号cntrl[0]をロウレベルに設定すると、p型トランジスタMp113は導通状態となる。すると、第2のカレントミラー回路は、レプリカビット線rplbtへの電流供給を開始する。レプリカビット線rplbtの電圧が上昇すると、バッファA1は、センスアンプ起動信号saeをロウレベルからハイレベルに変化させる。

バッファA1がセンスアンプ起動信号saeをロウレベルからハイレベルに変化させると、カレントミラー回路CM3のp型トランジスタMp111は導通状態から非導通状態に変化する。このp型トランジスタMp111の導通状態の変化に基づき、カレントミラー回路CM3は、レプリカビット線rplbtおよびレプリカビット線rplbbへの電流供給を停止する。

図29を参照して、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールMMDL23が有するカレントミラー回路CM3の変形例であるカレントミラー回路CM31の回路図を説明する。

カレントミラー回路CM31は、図28に示されるカレントミラー回路CM3と以下の点で相違する。即ち、p型トランジスタMp111のゲートにセンスアンプ起動信号saeを印加する代わりに、電源電圧vssが印加される。その他の構成は同一である。

カレントミラー回路CM3では、カレントミラー回路のリファレンス電流側の電流パスを構成するp型トランジスタMp111のゲートには、センスアンプ起動信号saeが印加されていた。センスアンプ起動信号saeの電圧が電源電圧vssから電源電圧vddに向けて上昇を開始すると、p型トランジスタMp111の電流駆動能力が低下する。カレントミラー回路のリファレンス電流に相当するp型トランジスタMp111の電流が減少すると、各々所定のトランジスタのゲート幅Wに設定されているp型トランジスタMp112およびp型トランジスタMp115と、p型トランジスタMp113およびp型トランジスタMp116に流れる電流が減少する。この電流減少は、電源電圧vddが低く設定されるほど、顕著となる。

一方、図29に示されるカレントミラー回路CM31は、p型トランジスタMp111のゲートに電源電圧vssを印加する構成を有する。この構成により、p型トランジスタMp111の駆動電流の変化は、センスアンプ起動信号saeの影響が軽減される。その結果、センスアンプ起動信号saeがロウレベルからハイレベルに変化するタイミングは、レプリカセルRC2に起因する遅延時間が正しく反映され、センスアンプ24の起動タイミングの精度が向上する。

メモリモジュールMMDL23によれば、メモリモジュールMMDL23へ印加する電源電圧vddの値を制御する制御信号cntrl[1:0]に基づいて、アシスト電圧生成回路VGEN2およびレプリカセル遅延回路RDLY23が有するカレントミラー回路CM3を制御することで、設定された電源電圧vddに最適なタイミングで、センスアンプ起動信号saeを生成することが可能となる。

さらに、センスアンプ起動信号saeの生成タイミングは、異なるミラー比を有するカレントミラー回路を制御信号cntrl[1:0]で切り替えることで調整可能である。その結果、レプリカセル遅延回路RDLY23が有するレプリカセルRC2の個数を固定した場合であっても、センスアンプ起動信号saeの生成タイミングの調整が可能となる。

<実施の形態3>

図30を参照して、実施の形態3に係る半導体装置LSI_3のブロック構成を説明する。

半導体装置LSI_3は、デュアルレール(Dual Rail)方式のSOCである。半導体装置LSI_3は、IPモジュール2、メモリモジュールMMDL3を備える。IPモジュール2およびメモリモジュールMMDL3間は、バス3を介して、アドレス、データ、および各種制御信号を送受信する。レギュレータ回路1は、印加された電源電圧vdd_exに基づき、IPモジュール2へ電源電圧vdd_cpuを供給し、メモリモジュールMMDL3へ電源電圧vddおよび電源電圧vdd2を供給する。図30において、レギュレータ回路1は、半導体装置LSI_1とは別チップで構成される例を示す。必要に応じ、レギュレータ回路1は、半導体装置LSI_1に内蔵されても良い。

メモリモジュールMMDL3は、ワードデコーダ21、ワードドライバ22、メモリセルアレイMAT、IO部IO、セル電圧制御回路MCNT、制御回路CTLm、および遅延回路DLY3を有する。制御回路CTLmは、基準タイミング信号tmg1を遅延回路DLY3へ出力する。遅延回路DLY3は、基準タイミング信号を所定時間遅延させたセンスアンプ起動信号saeを生成する。

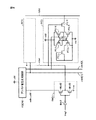

図31を参照して、実施の形態3に係る半導体装置LSI_3が備えるメモリモジュールMMDL3の回路図を説明する。

デュアルレール方式の半導体装置LSI_3において、メモリモジュールMMDL3には、電源電圧vddおよび電源電圧vdd2が印加される。電源電圧vddは、ワードデコーダ21、制御回路CTLm、カラムセレクタ23、センスアンプ24、およびライトアンプ25に印加される。電源電圧vddが印加されるこれら回路領域を、”周辺回路部PERI”、と定義する。電源電圧vdd2は、ワードドライバ22、セル電圧制御回路MCNT、メモリセルアレイMAT、および遅延回路DLY1に印加される。電源電圧vdd2が印加されるこれら回路領域を、”メモリコア部MRC”、と定義する。

電源電圧vdd2の値は、電源電圧vddの値より大きく設定される。これは、メモリセルMCの動作マージンを確保するためである。周辺回路部PERIとメモリコア部MRC間の信号は、レベルシフト回路LSFでレベル変換される。レベルシフト回路の入力部には電源電圧vddが印加され、その出力部には電源電圧vdd2が印加される。

メモリセルアレイMATは、ワード線WLj(j=0〜m:mは正の整数)およびビット線対bt/bbと接続され、行列状に配置されたメモリセルMCを有する。各ワード線WLjは、ワードドライバ22が有するp型トランジスタMp21およびn型トランジスタMn21で構成されるインバータの出力ノードと接続される。p型トランジスタMp21のソースには、電源電圧vdd2が印加される。n型トランジスタMn21のソースには、電源電圧vssが印加される。

ワードデコーダ21は、制御回路CTLmが出力するアドレス信号adr[x:0](アドレス信号adr0〜adrxを示す。)に基づき、ワードドライバ22が有する複数のインバータ(Mp21/Mn21)のいずれか一つを選択する。ワードデコーダ21におけるアドレス信号adr[x:0]の取込み、および制御回路CTLmにおける基準タイミング信号tmg1の生成は、クロックCLKに同期して行われる。制御回路CTLmは、IPモジュール2からバス3を経由して送信されるアドレス信号A[k:0]をクロックCLKに同期して取り込み、アドレス信号adr[x:0]を生成する。

ワードデコーダ21の出力信号は、電源電圧vdd(ハイレベル)と電源電圧vss(ロウレベル)間で変化する。一方、ワードドライバ22が有するインバータには、電源電圧vdd2および電源電圧vssが印加される。レベルシフト回路LSFは、ワードデコーダ21の出力信号をレベル変換して、ワードドライバに出力する。

セル電圧制御回路MCNTは、制御回路CTLmが出力する信号colselおよび信号rwselに基づき、電源電圧vdd2から、電圧mvdd[0]および電圧mvdd[1]を生成する。

カラムセレクタ23は、信号colselに基づき、2つのビット線対bt/bbのいずれか一方を選択する。図31では、1つのカラムセレクタ23には2つのビット線対bt/bbが接続されている例を示すが、適宜、接続するビット線対bt/bbの本数を増加しても良い。この信号colselは、制御回路CTLmに入力されるアドレス信号A[k:0]に基づき生成される。

カラムセレクタ23は、さらに、信号rwselに基づき、選択されたビット線対bt/bbをセンスアンプ(SA)24およびライトアンプ(WA)25のいずれか一方に接続する。この信号rwselは、制御回路CTLmに入力されるライトイネーブル信号WEに応答して生成される。

センスアンプ24には、選択されたメモリセルMCがビット線対bt/bbに出力する微小振幅の電圧が入力される。センスアンプ24は、センスアンプ起動信号saeに応答して起動される。即ち、センスアンプ起動信号saeがロウレベル(電源電圧vss)からハイレベル(電源電圧vdd)に変化すると、センスアンプ24は、入力された微小振幅の電圧を増幅し、2値の値を有する出力データQ[p](p=0〜n:nは正の整数)を出力する。センスアンプ起動信号saeの2値の値と、センスアンプ24の起動との対応付けは、上述と逆相に設定しても良い。なお、図31のメモリモジュールMMDL3は、n+1ビット幅である。

遅延回路DLY1は、基準タイミング信号tmg1を所定時間遅延させたセンスアンプ起動信号saeを生成する。遅延回路DLY1は、センスアンプ24が、アドレス信号adr[x:0]で選択されるメモリセルMCのデータの増幅動作を開始するタイミングと、基準タイミング信号tmg1に基づき生成されるセンスアンプ起動信号saeの生成タイミングとを整合させる。

遅延回路DLY1の回路構成は、図5に示される遅延回路DLY1と同一である。但し、図5に示される遅延回路DLY1には、電源電圧vddが印加されるが、図31に示される遅延回路DLY1には、電源電圧vdd2が印加される。遅延回路DLY1は、p型トランジスタMp41およびn型トランジスタMn41で構成されるインバータを所定段数直列接続した構成を有する。

図32を参照して、実施の形態3に係る半導体装置LSI_3が備えるメモリモジュールMMDL3が有するメモリコア部MRCおよび周辺回路部PERIに印加される電源電圧の設定値を説明する。

クロックCLKを生成する制御回路CTLmは、周辺回路部PERIに属する。従って、クロックCLKの波形は、電源電圧vss(ロウレベル)と電源電圧vdd(ハイレベル)間で変化する。メモリコア部MRCには、電源電圧vdd2が印加される。この電源電圧vdd2の値は、周辺回路部PERIに印加される電源電圧vddの値より大きく設定される。これは、メモリセルMCの動作マージンを確保するためである。電源電圧vdd2が印加されるワードドライバ22は、選択されたワード線WLjの電圧を電源電圧vdd2に設定する。

なお、図31において、カラムセレクタ23は、電源電圧vddが印加される周辺回路部PERIに属する構成例が示されている。この場合、図4に示される通り、ビット線対bt/bbのプリチャージ電圧は、vddに設定される。しかしながら、カラムセレクタ23をメモリコア部MRCに含ませる構成に変更しても良い。即ち、図4に示されるカラムセレクタ23において、スイッチ51〜スイッチ54に印加される電源電圧vddを電源電圧vdd2と変更しても良い。そのように変更することで、ビット線対bt/bbのプリチャージ電圧は、メモリセルMCに印加される電源電圧vdd2と等しく設定される。カラムセレクタ23に電源電圧vdd2を印加する場合、ライトアンプ25の出力段には、電源電圧vdd2が印加される。

実施の形態3に係る半導体装置LSI_3が備えるメモリモジュールMMDL3によれば、周辺回路部PERIとメモリコア部MRCの電源電圧が異なる場合であっても、メモリセルMCが、ビット線対bt/bbを介して、センスアンプ24にデータを印加するタイミングと、基準タイミング信号tmg1を遅延回路DLY1で所定時間遅延させて生成したセンスアンプ起動信号saeでセンスアンプ24が増幅動作を開始するタイミングと、を整合させることが可能となる。その結果、半導体装置LSI_3のアクセス時間の短縮および消費電力削減に効果がある。

メモリモジュールMMDL3は、基準タイミング信号tmg1を遅延回路DLY1で所定時間遅延させてセンスアンプ起動信号saeを生成する構成を有する。このセンスアンプ起動信号saeの生成は、遅延回路DLY1に限定されない。実施の形態1に係る半導体装置LSI_1が備えるメモリモジュールおよびその変形例と、実施の形態2に係る半導体装置LSI_2が備えるメモリモジュールおよびその変形例と、が有する遅延回路またはレプリカセル遅延回路を適用することも可能である。

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなく特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。