JP2013526066A - 低減されたダイ歪みアッセンブリのためのパッケージ基板のためのcte補償 - Google Patents

低減されたダイ歪みアッセンブリのためのパッケージ基板のためのcte補償 Download PDFInfo

- Publication number

- JP2013526066A JP2013526066A JP2013508271A JP2013508271A JP2013526066A JP 2013526066 A JP2013526066 A JP 2013526066A JP 2013508271 A JP2013508271 A JP 2013508271A JP 2013508271 A JP2013508271 A JP 2013508271A JP 2013526066 A JP2013526066 A JP 2013526066A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- dies

- die

- package substrate

- singulated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W70/69—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10D89/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/50—Multistep manufacturing processes of assemblies consisting of devices, the devices being individual devices of subclass H10D or integrated devices of class H10

-

- H10P72/74—

-

- H10W74/014—

-

- H10W90/00—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/0557—Disposition the external layer being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05638—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05647—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13025—Disposition the bump connector being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13144—Gold [Au] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13147—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

- H01L2224/16148—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked the bump connector connecting to a bonding area protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16227—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

- H01L2224/171—Disposition

- H01L2224/1718—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/17181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81894—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces

- H01L2224/81895—Direct bonding, i.e. joining surfaces by means of intermolecular attracting interactions at their interfaces, e.g. covalent bonds, van der Waals forces between electrically conductive surfaces, e.g. copper-copper direct bonding, surface activated bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

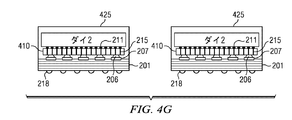

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06513—Bump or bump-like direct electrical connections between devices, e.g. flip-chip connection, solder bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06517—Bump or bump-like direct electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01058—Cerium [Ce]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0106—Neodymium [Nd]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

- H01L2924/01322—Eutectic Alloys, i.e. obtained by a liquid transforming into two solid phases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/146—Mixed devices

- H01L2924/1461—MEMS

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19043—Component type being a resistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

-

- H10P72/7416—

-

- H10P72/7418—

-

- H10P72/7434—

-

- H10W20/20—

-

- H10W72/0198—

-

- H10W72/07236—

-

- H10W72/07254—

-

- H10W72/244—

-

- H10W72/247—

-

- H10W72/252—

-

- H10W72/29—

-

- H10W72/942—

-

- H10W72/952—

-

- H10W74/00—

-

- H10W74/012—

-

- H10W74/019—

-

- H10W74/117—

-

- H10W74/15—

-

- H10W80/314—

-

- H10W90/297—

-

- H10W90/701—

-

- H10W90/722—

-

- H10W90/724—

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Wire Bonding (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/770,058 | 2010-04-29 | ||

| US12/770,058 US8298863B2 (en) | 2010-04-29 | 2010-04-29 | TCE compensation for package substrates for reduced die warpage assembly |

| PCT/US2011/034444 WO2011139875A2 (en) | 2010-04-29 | 2011-04-29 | Tce compensation for ic package substrates for reduced die warpage assembly |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013526066A true JP2013526066A (ja) | 2013-06-20 |

| JP2013526066A5 JP2013526066A5 (enExample) | 2014-05-22 |

Family

ID=44857606

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013508271A Pending JP2013526066A (ja) | 2010-04-29 | 2011-04-29 | 低減されたダイ歪みアッセンブリのためのパッケージ基板のためのcte補償 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US8298863B2 (enExample) |

| JP (1) | JP2013526066A (enExample) |

| CN (1) | CN102844861B (enExample) |

| WO (1) | WO2011139875A2 (enExample) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8227295B2 (en) * | 2008-10-16 | 2012-07-24 | Texas Instruments Incorporated | IC die having TSV and wafer level underfill and stacked IC devices comprising a workpiece solder connected to the TSV |

| US9048233B2 (en) | 2010-05-26 | 2015-06-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Package systems having interposers |

| US8786066B2 (en) * | 2010-09-24 | 2014-07-22 | Intel Corporation | Die-stacking using through-silicon vias on bumpless build-up layer substrates including embedded-dice, and processes of forming same |

| US8796075B2 (en) * | 2011-01-11 | 2014-08-05 | Nordson Corporation | Methods for vacuum assisted underfilling |

| US9443783B2 (en) | 2012-06-27 | 2016-09-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | 3DIC stacking device and method of manufacture |

| US10153179B2 (en) | 2012-08-24 | 2018-12-11 | Taiwan Semiconductor Manufacturing Company | Carrier warpage control for three dimensional integrated circuit (3DIC) stacking |

| KR20140110334A (ko) * | 2013-03-07 | 2014-09-17 | 삼성전자주식회사 | 반도체 패키지 및 그 제조 방법 |

| JP2014179419A (ja) * | 2013-03-14 | 2014-09-25 | Alpha- Design Kk | 電子部品の接合方法 |

| US8901748B2 (en) * | 2013-03-14 | 2014-12-02 | Intel Corporation | Direct external interconnect for embedded interconnect bridge package |

| US20150014852A1 (en) * | 2013-07-12 | 2015-01-15 | Yueli Liu | Package assembly configurations for multiple dies and associated techniques |

| US9892970B2 (en) | 2016-06-02 | 2018-02-13 | Globalfoundries Inc. | Integrated circuit structure having deep trench capacitor and through-silicon via and method of forming same |

| US9929085B2 (en) | 2016-06-02 | 2018-03-27 | Globalfoundries Inc. | Integrated circuit structure having deep trench capacitor and through-silicon via and method of forming same |

| US10815121B2 (en) | 2016-07-12 | 2020-10-27 | Hewlett-Packard Development Company, L.P. | Composite wafers |

| KR102649471B1 (ko) | 2016-09-05 | 2024-03-21 | 삼성전자주식회사 | 반도체 패키지 및 그의 제조 방법 |

| US9966363B1 (en) * | 2017-02-03 | 2018-05-08 | Nanya Technology Corporation | Semiconductor apparatus and method for preparing the same |

| US10396003B2 (en) * | 2017-10-18 | 2019-08-27 | Micron Technology, Inc. | Stress tuned stiffeners for micro electronics package warpage control |

| US10548230B2 (en) * | 2018-01-04 | 2020-01-28 | Micron Technology, Inc. | Method for stress reduction in semiconductor package via carrier |

| US20190259675A1 (en) * | 2018-02-19 | 2019-08-22 | Didrew Technology (Bvi) Limited | Glass frame fan out packaging and method of manufacturing thereof |

| US10692793B2 (en) * | 2018-03-02 | 2020-06-23 | Micron Technology, Inc. | Electronic device with a package-level thermal regulator mechanism and associated systems, devices, and methods |

| CN110634806A (zh) * | 2018-06-21 | 2019-12-31 | 美光科技公司 | 半导体装置组合件和其制造方法 |

| US11694906B2 (en) * | 2019-09-03 | 2023-07-04 | Amkor Technology Singapore Holding Pte. Ltd. | Semiconductor devices and methods of manufacturing semiconductor devices |

| US12412862B2 (en) * | 2021-04-28 | 2025-09-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Package structure and manufacturing method thereof |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003092375A (ja) * | 2001-09-19 | 2003-03-28 | Matsushita Electric Ind Co Ltd | 半導体装置、その製造方法およびその検査方法 |

| JP2005216989A (ja) * | 2004-01-28 | 2005-08-11 | Hitachi Maxell Ltd | マルチチップモジュールの製造方法 |

| JP2006294692A (ja) * | 2005-04-06 | 2006-10-26 | Nec Electronics Corp | 半導体装置およびその製造方法 |

| JP2007115774A (ja) * | 2005-10-18 | 2007-05-10 | Nec Electronics Corp | 半導体装置の製造方法 |

| JP2007214220A (ja) * | 2006-02-08 | 2007-08-23 | Oki Electric Ind Co Ltd | 半導体パッケージの製造方法 |

| JP2009117767A (ja) * | 2007-11-09 | 2009-05-28 | Shinko Electric Ind Co Ltd | 半導体装置の製造方法及びそれにより製造した半導体装置 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6294407B1 (en) * | 1998-05-06 | 2001-09-25 | Virtual Integration, Inc. | Microelectronic packages including thin film decal and dielectric adhesive layer having conductive vias therein, and methods of fabricating the same |

| US6008070A (en) * | 1998-05-21 | 1999-12-28 | Micron Technology, Inc. | Wafer level fabrication and assembly of chip scale packages |

| US6627998B1 (en) * | 2000-07-27 | 2003-09-30 | International Business Machines Corporation | Wafer scale thin film package |

| US6506681B2 (en) * | 2000-12-06 | 2003-01-14 | Micron Technology, Inc. | Thin flip—chip method |

| US6879492B2 (en) * | 2001-03-28 | 2005-04-12 | International Business Machines Corporation | Hyperbga buildup laminate |

| JP3831287B2 (ja) * | 2002-04-08 | 2006-10-11 | 株式会社日立製作所 | 半導体装置の製造方法 |

| KR100555505B1 (ko) * | 2003-07-09 | 2006-03-03 | 삼성전자주식회사 | 실리사이드층의 증착 및 제거에 의해서 콘택홀 바닥에서확장된 오픈 선폭을 구현하는 연결 콘택 형성 방법 |

| TWI245381B (en) * | 2003-08-14 | 2005-12-11 | Via Tech Inc | Electrical package and process thereof |

| TWI254425B (en) | 2004-10-26 | 2006-05-01 | Advanced Semiconductor Eng | Chip package structure, chip packaging process, chip carrier and manufacturing process thereof |

| US7256483B2 (en) * | 2004-10-28 | 2007-08-14 | Philips Lumileds Lighting Company, Llc | Package-integrated thin film LED |

| KR100688560B1 (ko) * | 2005-07-22 | 2007-03-02 | 삼성전자주식회사 | 웨이퍼 레벨 칩 스케일 패키지 및 그 제조 방법 |

| DE102005053842B4 (de) * | 2005-11-09 | 2008-02-07 | Infineon Technologies Ag | Halbleiterbauelement mit Verbindungselementen und Verfahren zur Herstellung desselben |

| SG133445A1 (en) * | 2005-12-29 | 2007-07-30 | Micron Technology Inc | Methods for packaging microelectronic devices and microelectronic devices formed using such methods |

| US7473577B2 (en) | 2006-08-11 | 2009-01-06 | International Business Machines Corporation | Integrated chip carrier with compliant interconnect |

| US7846776B2 (en) * | 2006-08-17 | 2010-12-07 | Micron Technology, Inc. | Methods for releasably attaching sacrificial support members to microfeature workpieces and microfeature devices formed using such methods |

| TWI316749B (en) * | 2006-11-17 | 2009-11-01 | Siliconware Precision Industries Co Ltd | Semiconductor package and fabrication method thereof |

| US7605477B2 (en) | 2007-01-25 | 2009-10-20 | Raytheon Company | Stacked integrated circuit assembly |

| US20080188037A1 (en) | 2007-02-05 | 2008-08-07 | Bridge Semiconductor Corporation | Method of manufacturing semiconductor chip assembly with sacrificial metal-based core carrier |

| US8012857B2 (en) * | 2007-08-07 | 2011-09-06 | Semiconductor Components Industries, Llc | Semiconductor die singulation method |

| TWI375321B (en) * | 2007-08-24 | 2012-10-21 | Xintec Inc | Electronic device wafer level scale packages and fabrication methods thereof |

| US20100090339A1 (en) * | 2008-09-12 | 2010-04-15 | Kumar Ananda H | Structures and Methods for Wafer Packages, and Probes |

| US8106504B2 (en) * | 2008-09-25 | 2012-01-31 | King Dragon International Inc. | Stacking package structure with chip embedded inside and die having through silicon via and method of the same |

| US8237257B2 (en) * | 2008-09-25 | 2012-08-07 | King Dragon International Inc. | Substrate structure with die embedded inside and dual build-up layers over both side surfaces and method of the same |

| US7863092B1 (en) * | 2008-09-30 | 2011-01-04 | Xilinx, Inc. | Low cost bumping and bonding method for stacked die |

| US8952519B2 (en) * | 2010-01-13 | 2015-02-10 | Chia-Sheng Lin | Chip package and fabrication method thereof |

| KR101698805B1 (ko) * | 2010-03-23 | 2017-02-02 | 삼성전자주식회사 | 웨이퍼 레벨의 패키지 방법 및 그에 의해 제조되는 반도체 소자 |

-

2010

- 2010-04-29 US US12/770,058 patent/US8298863B2/en active Active

-

2011

- 2011-04-29 WO PCT/US2011/034444 patent/WO2011139875A2/en not_active Ceased

- 2011-04-29 JP JP2013508271A patent/JP2013526066A/ja active Pending

- 2011-04-29 CN CN201180019483.4A patent/CN102844861B/zh active Active

-

2012

- 2012-09-25 US US13/625,932 patent/US8759154B2/en active Active

-

2014

- 2014-03-10 US US14/202,082 patent/US20140183719A1/en not_active Abandoned

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003092375A (ja) * | 2001-09-19 | 2003-03-28 | Matsushita Electric Ind Co Ltd | 半導体装置、その製造方法およびその検査方法 |

| JP2005216989A (ja) * | 2004-01-28 | 2005-08-11 | Hitachi Maxell Ltd | マルチチップモジュールの製造方法 |

| JP2006294692A (ja) * | 2005-04-06 | 2006-10-26 | Nec Electronics Corp | 半導体装置およびその製造方法 |

| JP2007115774A (ja) * | 2005-10-18 | 2007-05-10 | Nec Electronics Corp | 半導体装置の製造方法 |

| JP2007214220A (ja) * | 2006-02-08 | 2007-08-23 | Oki Electric Ind Co Ltd | 半導体パッケージの製造方法 |

| JP2009117767A (ja) * | 2007-11-09 | 2009-05-28 | Shinko Electric Ind Co Ltd | 半導体装置の製造方法及びそれにより製造した半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102844861B (zh) | 2016-01-13 |

| CN102844861A (zh) | 2012-12-26 |

| US20110266693A1 (en) | 2011-11-03 |

| US8298863B2 (en) | 2012-10-30 |

| US20140183719A1 (en) | 2014-07-03 |

| US8759154B2 (en) | 2014-06-24 |

| US20130029457A1 (en) | 2013-01-31 |

| WO2011139875A3 (en) | 2012-02-23 |

| WO2011139875A2 (en) | 2011-11-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102844861B (zh) | 对用于裸片翘曲减少的组装的ic封装衬底的tce补偿 | |

| TWI803310B (zh) | 積體電路元件和其形成方法 | |

| KR102730607B1 (ko) | 집적 회로 패키지 및 방법 | |

| US11152312B2 (en) | Packages with interposers and methods for forming the same | |

| US10283400B1 (en) | Semiconductor device package and manufacturing method thereof | |

| CN105428265B (zh) | 半导体装置的制造方法 | |

| US10090234B2 (en) | Semiconductor device package and manufacturing method thereof | |

| US7915080B2 (en) | Bonding IC die to TSV wafers | |

| US8647924B2 (en) | Semiconductor package and method of packaging semiconductor devices | |

| US11823913B2 (en) | Method of manufacturing an electronic device and electronic device manufactured thereby | |

| KR20220026996A (ko) | 집적 회로 패키지 및 방법 | |

| US20250038042A1 (en) | Semiconductor device package and manufacturing method thereof | |

| TWI856479B (zh) | 積體電路封裝體及其形成方法 | |

| US8643167B2 (en) | Semiconductor package with through silicon vias and method for making the same | |

| US12463192B2 (en) | Method of forming integrated circuit packages by bonding package component having first carrier to package substrate having second carrier | |

| CN220934063U (zh) | 集成电路封装 | |

| TWI907971B (zh) | 電子結構以及製造電子結構的方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140403 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140403 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150818 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20151117 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160405 |