JP2013093482A - 半導体装置および半導体装置の製造方法 - Google Patents

半導体装置および半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2013093482A JP2013093482A JP2011235617A JP2011235617A JP2013093482A JP 2013093482 A JP2013093482 A JP 2013093482A JP 2011235617 A JP2011235617 A JP 2011235617A JP 2011235617 A JP2011235617 A JP 2011235617A JP 2013093482 A JP2013093482 A JP 2013093482A

- Authority

- JP

- Japan

- Prior art keywords

- insulating layer

- drift region

- region

- field plate

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

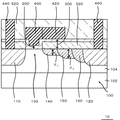

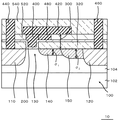

【選択図】図1

Description

半導体基板と、

前記半導体基板に設けられた第1導電型のソース領域と、

前記半導体基板に設けられ、平面視で前記ソース領域から離間して設けられた第1導電型の第1ドリフト領域と、

前記半導体基板のうち、平面視で前記ソース領域および前記第1ドリフト領域に挟まれた領域であるチャネル領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域のうち前記ソース領域と反対側の領域に接している第1導電型の第2ドリフト領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接しており、前記第1ドリフト領域および前記第2ドリフト領域よりも不純物濃度が高い第1導電型のドレイン領域と、

前記チャネル領域上に設けられたゲート絶縁層と、

前記ゲート絶縁層上に接し、平面視で前記チャネル領域と重なるように設けられたゲート電極と、

前記半導体基板上に設けられ、少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられ、前記ゲート絶縁層よりも厚い第1フィールドプレート絶縁層と、

前記第1フィールド絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられた第1フィールドプレート電極と、

を備え、

前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、下記式(1)を満たす半導体装置が提供される。

半導体基板に第1導電型の不純物を導入することにより、第1ドリフト領域を形成する第1ドリフト領域工程と

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域に接するように、第2ドリフト領域を形成する第2ドリフト領域形成工程と、

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域のうち前記第2ドリフト領域と反対側の領域から離間した位置に、ソース領域を形成する工程と、

前記半導体基板に前記第1ドリフト領域および前記第2ドリフト領域よりも高い不純物濃度で第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接するように、ドレイン領域を形成する工程と、

前記半導体基板上に、平面視で前記ソース領域および前記第1ドリフト領域に挟まれたチャネル領域に重なるようにゲート絶縁層を形成するゲート絶縁層形成工程と、

少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、前記ゲート絶縁層よりも厚く第1フィールドプレート絶縁層を形成する第1フィールドプレート絶縁層形成工程と、

前記ゲート絶縁層上に接するとともに、平面視で前記チャネル領域と重なるようにゲート電極を形成する工程と、

前記第1フィールドプレート絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、第1フィールドプレート電極を形成する工程と、

を備え、

前記第1ドリフト領域形成工程、前記第2ドリフト領域形成工程、前記ゲート絶縁層形成工程および前記第1フィールドプレート絶縁層形成工程において、前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、上記式(1)を満たすように、前記第1ドリフト領域、前記第2ドリフト領域、前記ゲート絶縁層および前記第1フィールドプレート絶縁層を形成する半導体装置の製造方法が提供される。

図1〜図4を用い、第1の実施形態に係る半導体装置10について説明する。この半導体装置10は、以下の構成を備えている。第1導電型のソース領域110は、半導体基板100に設けられている。第1導電型の第1ドリフト領域140は、半導体基板100に設けられ、平面視でソース領域110から離間して設けられている。半導体基板100のうち、平面視でソース領域110および第1ドリフト領域140に挟まれた領域には、チャネル領域130が形成されている。第1導電型の第2ドリフト領域150は、半導体基板100に設けられ、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、半導体基板100に設けられ、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。また、第1導電型のドレイン領域120は、第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高い。チャネル領域130上には、ゲート絶縁層200が設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130重なるように設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。また、第1フィールドプレート絶縁層300は、ゲート絶縁層200よりも厚い。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。さらに、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2としたとき、下記式(1)を満たす。

図12は、第2の実施形態に係る半導体装置10の構成を示す断面図である。第2の実施形態は、第1ドリフト領域140および第2ドリフト領域150に加え、ドリフト領域がさらに設けられている点を除いて、第1の実施形態と同様である。以下、詳細を説明する

図13は、第3の実施形態に係る半導体装置10の構成を示す断面図である。第3の実施形態は、以下の点を除いて、第1の実施形態と同様である。第1層間絶縁層520は、少なくともゲート電極400を覆うように設けられている。ソース電極440は、ソース領域110に接続している。また、第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。第1の実施形態における第1フィールドプレート電極420がゲート電極400に接続しているのに対して、第2の実施形態では第1フィールドプレート電極420がソース電極440に接続している。以下、詳細を説明する

図16は、第4の実施形態に係る半導体装置10の構成を示す断面図である。第4の実施形態は、第1フィールドプレート電極420が第2フィールドプレート電極480上に接している点を除いて、第1の実施形態、または第3の実施形態の一部と同様である。

図20は、第5の実施形態に係る半導体装置10の構成を示す断面図である。第5の実施形態は、半導体基板100がSi基板である点を除いて、第1の実施形態と同様である。

図21は、第6の実施形態に係る半導体装置10の構成を示す断面図である。第6の実施形態は、ゲート絶縁層200上に下地絶縁層320が設けられている点を除いて、第1の実施形態、または第5の実施形態と同様である。

100 半導体基板

102 下地基板

104 III族窒化物半導体層

110 ソース領域

120 ドレイン領域

130 チャネル領域

140 第1ドリフト領域

150 第2ドリフト領域

160 第3ドリフト領域

200 ゲート絶縁層

210 チャネル開口部

240 保護層

300 第1フィールドプレート絶縁層

320 下地絶縁層

400 ゲート電極

420 第1フィールドプレート絶縁層

430 ソース開口部

440 ソース電極

450 ドレイン開口部

460 ドレイン電極

480 第2フィールドプレート絶縁層

520 第1層間絶縁層

540 第2層間絶縁層

600 フォトレジスト層

A 比較例

B 比較例

C 比較例

Claims (20)

- 半導体基板と、

前記半導体基板に設けられた第1導電型のソース領域と、

前記半導体基板に設けられ、平面視で前記ソース領域から離間して設けられた第1導電型の第1ドリフト領域と、

前記半導体基板のうち、平面視で前記ソース領域および前記第1ドリフト領域に挟まれた領域であるチャネル領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域のうち前記ソース領域と反対側の領域に接している第1導電型の第2ドリフト領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接しており、前記第1ドリフト領域および前記第2ドリフト領域よりも不純物濃度が高い第1導電型のドレイン領域と、

前記チャネル領域上に設けられたゲート絶縁層と、

前記ゲート絶縁層上に接し、平面視で前記チャネル領域と重なるように設けられたゲート電極と、

前記半導体基板上に設けられ、少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられ、前記ゲート絶縁層よりも厚い第1フィールドプレート絶縁層と、

前記第1フィールド絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられた第1フィールドプレート電極と、

を備え、

前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、下記式(1)を満たす半導体装置。

- 請求項1に記載の半導体装置において、

前記半導体基板は、主面側にIII族窒化物半導体層を備え、

前記ソース領域、前記チャネル領域、前記第1ドリフト領域、前記第2ドリフト領域および前記ドレイン領域は、当該III族窒化物半導体層に形成されている半導体装置。 - 請求項2に記載の半導体装置において、

前記チャネル領域の不純物濃度は、1×10−16atoms/cm3以下である半導体装置。 - 請求項2または3に記載の半導体装置において、

前記III族窒化物半導体層は、真性半導体である半導体装置。 - 請求項2〜4のいずれか一項に記載の半導体装置において、

前記ソース領域、前記第1ドリフト領域、前記第2ドリフト領域および前記ドレイン領域は、n型であり、

当該n型の不純物は、Siである半導体装置。 - 請求項5に記載の半導体装置において、

前記III族窒化物半導体層のうち、前記ソース領域および前記ドレイン領域の間に位置する部分には、p型の不純物領域が形成されていない半導体装置。 - 請求項2〜6のいずれか一項に記載の半導体装置において、

前記半導体基板のうち、前記III族窒化物半導体層は、下地基板上に設けられ、

当該下地基板は、Si基板、サファイア基板、SiC基板またはGaN基板である半導体装置。 - 請求項1に記載の半導体装置において、

前記半導体基板は、Si基板である半導体装置。 - 請求項1〜8のいずれか一項に記載の半導体装置において、

N1<N2である半導体装置。 - 請求項1〜8のいずれか一項に記載の半導体装置において、

N1>N2である半導体装置。 - 請求項1〜10のいずれか一項に記載の半導体装置において、

前記第1フィールドプレート電極は、前記ゲート電極に接続し、前記ゲート電極と一体として形成されている半導体装置。 - 請求項1〜10のいずれか一項に記載の半導体装置において、

少なくとも前記ゲート電極を覆うように設けられた第1層間絶縁層と、

前記ソース領域に接続するソース電極をさらに備え、

前記第1フィールドプレート絶縁層は、前記第1層間絶縁層の一部を含み、

前記第1フィールドプレート電極は前記ソース電極に接続している半導体装置。 - 請求項12に記載の半導体装置において、

前記ゲート電極に接続するとともに、平面視で前記第1ドリフト領域の一部と重なるように設けられた第2フィールドプレート電極をさらに備え、

前記第1層間絶縁層は、少なくとも前記ゲート電極および前記第2フィールドプレート電極を覆うように設けられている半導体装置。 - 請求項1〜10のいずれか一項に記載の半導体装置において、

前記ゲート電極に接続するとともに、平面視で前記第1ドリフト領域の一部と重なるように設けられた第2フィールドプレート電極と、

前記半導体基板上に設けられ、前記ゲート電極および前記第2フィールドプレート電極の上面と同一面を形成するように設けられた第1層間絶縁層と、

をさらに備え、

前記第1フィールドプレート絶縁層は、前記第1層間絶縁層の一部を含み、

前記第1フィールドプレート電極は、前記第1フィールドプレート絶縁層のうち、前記第1層間絶縁層上および前記第2フィールドプレート電極上に接している半導体装置。 - 請求項1〜14に記載の半導体装置において、

前記半導体基板上に接し、平面視で前記チャネル領域と重なる領域に開口部を有する下地絶縁層をさらに備え、

前記ゲート絶縁層は、前記開口部に露出した前記半導体基板上、および前記下地絶縁層上に接して設けられ、

前記第1フィールドプレート絶縁層は、前記下地絶縁層の一部および前記ゲート絶縁層の一部を含む半導体装置。 - 半導体基板に第1導電型の不純物を導入することにより、第1ドリフト領域を形成する第1ドリフト領域工程と

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域に接するように、第2ドリフト領域を形成する第2ドリフト領域形成工程と、

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域のうち前記第2ドリフト領域と反対側の領域から離間した位置に、ソース領域を形成する工程と、

前記半導体基板に前記第1ドリフト領域および前記第2ドリフト領域よりも高い不純物濃度で第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接するように、ドレイン領域を形成する工程と、

前記半導体基板上に、平面視で前記ソース領域および前記第1ドリフト領域に挟まれたチャネル領域に重なるようにゲート絶縁層を形成するゲート絶縁層形成工程と、

少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、前記ゲート絶縁層よりも厚く第1フィールドプレート絶縁層を形成する第1フィールドプレート絶縁層形成工程と、

前記ゲート絶縁層上に接するとともに、平面視で前記チャネル領域と重なるようにゲート電極を形成する工程と、

前記第1フィールドプレート絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、第1フィールドプレート電極を形成する工程と、

を備え、

前記第1ドリフト領域形成工程、前記第2ドリフト領域形成工程、前記ゲート絶縁層形成工程および前記第1フィールドプレート絶縁層形成工程において、前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、下記式(1)を満たすように、前記第1ドリフト領域、前記第2ドリフト領域、前記ゲート絶縁層および前記第1フィールドプレート絶縁層を形成する半導体装置の製造方法。

- 請求項16に記載の半導体装置の製造方法において、

前記半導体基板は、主面にIII族窒化物半導体層を備える半導体装置の製造方法。 - 請求項16または17に記載の半導体装置の製造方法において、

前記ゲート絶縁層形成工程は、

前記半導体基板上に、下地絶縁層を形成する工程と、

前記下地絶縁層のうち、少なくとも平面視で前記チャネル領域に重なる位置にチャネル開口部を形成する工程と、

前記チャネル開口部に露出した前記半導体基板上、および前記下地絶縁層上に、ゲート絶縁層を形成する工程と、

を備え、

前記第1フィールドプレート絶縁層形成工程は前記ゲート絶縁層形成工程を含み、

前記第1フィールドプレート絶縁層は、前記下地絶縁層および前記ゲート絶縁層を含む半導体装置の製造方法。 - 請求項16〜18のいずれか一項に記載の半導体装置の製造方法において、

前記ゲート電極に接続するとともに、平面視で前記第1ドリフト領域の一部と重なるように、第2フィールドプレート電極を形成する工程と、

少なくとも前記ゲート電極および前記第2フィールドプレート電極を覆うように第1層間絶縁層を形成する第1層間絶縁層形成工程と、

前記第1層間絶縁層のうち平面視で前記ソース領域と重なる部分にソース開口部を形成する工程と、

前記ソース開口部に金属を埋め込むことにより、ソース電極を形成する工程と、

をさらに備え、

前記第1フィールドプレート絶縁層形成工程は、前記第1層間絶縁層形成工程を含み、

前記第1フィールドプレート絶縁層は前記第1層間絶縁層の一部を含み、

前記第1フィールドプレート電極形成工程において、

前記第1フィールドプレート絶縁層のうち前記第1層間絶縁層上に、前記ソース電極に接続するように前記第1フィールドプレート電極を形成する半導体装置の製造方法。 - 請求項16〜18のいずれか一項に記載の半導体装置の製造方法において、

前記ゲート電極に接続するとともに、平面視で前記第1ドリフト領域の一部と重なるように、第2フィールドプレート電極を形成する工程と、

少なくとも前記ゲート電極および前記第2フィールドプレート電極を覆うように第1層間絶縁層を形成する第1層間絶縁層形成工程と、

前記ゲート電極および前記第2フィールドプレート電極の上面と同一面を形成するように、前記第1層間絶縁層を平坦化する平坦化工程と、

をさらに備え、

前記第1フィールドプレート絶縁層形成工程は、前記第1層間絶縁層形成工程および前記平坦化工程を含み、

前記第1フィールドプレート絶縁層は前記第1層間絶縁層の一部を含み、

前記第1フィールドプレート電極形成工程において、

前記第1フィールドプレート絶縁層のうち、前記第1層間絶縁層上および前記第2フィールドプレート電極上に接するように、前記第1フィールドプレート電極を形成する半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011235617A JP2013093482A (ja) | 2011-10-27 | 2011-10-27 | 半導体装置および半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011235617A JP2013093482A (ja) | 2011-10-27 | 2011-10-27 | 半導体装置および半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2013093482A true JP2013093482A (ja) | 2013-05-16 |

| JP2013093482A5 JP2013093482A5 (ja) | 2014-09-18 |

Family

ID=48616384

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011235617A Pending JP2013093482A (ja) | 2011-10-27 | 2011-10-27 | 半導体装置および半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2013093482A (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9461122B2 (en) | 2014-03-19 | 2016-10-04 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method for the same |

| US9722067B2 (en) | 2015-09-10 | 2017-08-01 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US10026804B2 (en) | 2014-03-19 | 2018-07-17 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US10332997B2 (en) | 2017-11-10 | 2019-06-25 | Hitachi, Ltd. | Semiconductor device and method of manufacturing semiconductor device |

| CN113316837A (zh) * | 2019-01-21 | 2021-08-27 | 株式会社电装 | 半导体装置的制造方法 |

| KR20220100492A (ko) * | 2021-01-08 | 2022-07-15 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 메모리 윈도우를 확대하기 위한 분극 강화 구조물 |

Citations (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5368581A (en) * | 1976-12-01 | 1978-06-19 | Hitachi Ltd | Semiconductor device |

| JPS5683076A (en) * | 1979-12-10 | 1981-07-07 | Sharp Corp | High tension mos field-effect transistor |

| JPS61180483A (ja) * | 1985-02-05 | 1986-08-13 | Matsushita Electric Ind Co Ltd | 高耐圧mos型半導体装置 |

| JPH07211917A (ja) * | 1994-01-19 | 1995-08-11 | Nippon Telegr & Teleph Corp <Ntt> | 横形mos電界効果トランジスタ |

| JPH11224945A (ja) * | 1998-02-05 | 1999-08-17 | Matsushita Electron Corp | 半導体装置 |

| JPH11261066A (ja) * | 1997-12-17 | 1999-09-24 | Korea Electronics Telecommun | 二重フィールド板構造を有する電力素子 |

| JP2002353444A (ja) * | 2001-05-28 | 2002-12-06 | Fuji Electric Co Ltd | 半導体装置 |

| JP2004502306A (ja) * | 2000-06-23 | 2004-01-22 | シリコン・ワイヤレス・コーポレイション | 速度飽和モードでの動作時に線形伝達特性を持つmosfetデバイスとその製造方法及び動作方法 |

| JP2004335990A (ja) * | 2003-03-10 | 2004-11-25 | Fuji Electric Device Technology Co Ltd | Mis型半導体装置 |

| US20040238854A1 (en) * | 2003-03-11 | 2004-12-02 | Infineon Technologies Ag | Field effect transistor |

| JP2006344957A (ja) * | 2005-06-08 | 2006-12-21 | Samsung Electronics Co Ltd | 厚いエッジゲート絶縁膜パターンを有するmos電界効果トランジスタ及びその製造方法 |

| JP2008135700A (ja) * | 2006-11-01 | 2008-06-12 | Furukawa Electric Co Ltd:The | Iii族窒化物膜の製造方法及びiii族窒化物半導体素子 |

| JP2008277640A (ja) * | 2007-05-02 | 2008-11-13 | Toshiba Corp | 窒化物半導体素子 |

| JP2008311392A (ja) * | 2007-06-14 | 2008-12-25 | Furukawa Electric Co Ltd:The | Iii族窒化物半導体を用いた電界効果トランジスタ |

| JP2009515332A (ja) * | 2005-11-02 | 2009-04-09 | エヌエックスピー ビー ヴィ | 半導体デバイスの製造方法 |

| US20090267145A1 (en) * | 2008-04-23 | 2009-10-29 | Ciclon Semiconductor Device Corp. | Mosfet device having dual interlevel dielectric thickness and method of making same |

| US20110079846A1 (en) * | 2009-10-02 | 2011-04-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | High voltage devices, systems, and methods for forming the high voltage devices |

| JP2011124282A (ja) * | 2009-12-08 | 2011-06-23 | Sharp Corp | 電界効果トランジスタ |

| JP2011198837A (ja) * | 2010-03-17 | 2011-10-06 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

-

2011

- 2011-10-27 JP JP2011235617A patent/JP2013093482A/ja active Pending

Patent Citations (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5368581A (en) * | 1976-12-01 | 1978-06-19 | Hitachi Ltd | Semiconductor device |

| JPS5683076A (en) * | 1979-12-10 | 1981-07-07 | Sharp Corp | High tension mos field-effect transistor |

| JPS61180483A (ja) * | 1985-02-05 | 1986-08-13 | Matsushita Electric Ind Co Ltd | 高耐圧mos型半導体装置 |

| JPH07211917A (ja) * | 1994-01-19 | 1995-08-11 | Nippon Telegr & Teleph Corp <Ntt> | 横形mos電界効果トランジスタ |

| JPH11261066A (ja) * | 1997-12-17 | 1999-09-24 | Korea Electronics Telecommun | 二重フィールド板構造を有する電力素子 |

| JPH11224945A (ja) * | 1998-02-05 | 1999-08-17 | Matsushita Electron Corp | 半導体装置 |

| JP2004502306A (ja) * | 2000-06-23 | 2004-01-22 | シリコン・ワイヤレス・コーポレイション | 速度飽和モードでの動作時に線形伝達特性を持つmosfetデバイスとその製造方法及び動作方法 |

| JP2002353444A (ja) * | 2001-05-28 | 2002-12-06 | Fuji Electric Co Ltd | 半導体装置 |

| JP2004335990A (ja) * | 2003-03-10 | 2004-11-25 | Fuji Electric Device Technology Co Ltd | Mis型半導体装置 |

| US20040238854A1 (en) * | 2003-03-11 | 2004-12-02 | Infineon Technologies Ag | Field effect transistor |

| JP2006344957A (ja) * | 2005-06-08 | 2006-12-21 | Samsung Electronics Co Ltd | 厚いエッジゲート絶縁膜パターンを有するmos電界効果トランジスタ及びその製造方法 |

| JP2009515332A (ja) * | 2005-11-02 | 2009-04-09 | エヌエックスピー ビー ヴィ | 半導体デバイスの製造方法 |

| JP2008135700A (ja) * | 2006-11-01 | 2008-06-12 | Furukawa Electric Co Ltd:The | Iii族窒化物膜の製造方法及びiii族窒化物半導体素子 |

| JP2008277640A (ja) * | 2007-05-02 | 2008-11-13 | Toshiba Corp | 窒化物半導体素子 |

| JP2008311392A (ja) * | 2007-06-14 | 2008-12-25 | Furukawa Electric Co Ltd:The | Iii族窒化物半導体を用いた電界効果トランジスタ |

| US20090267145A1 (en) * | 2008-04-23 | 2009-10-29 | Ciclon Semiconductor Device Corp. | Mosfet device having dual interlevel dielectric thickness and method of making same |

| US20110079846A1 (en) * | 2009-10-02 | 2011-04-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | High voltage devices, systems, and methods for forming the high voltage devices |

| JP2011124282A (ja) * | 2009-12-08 | 2011-06-23 | Sharp Corp | 電界効果トランジスタ |

| JP2011198837A (ja) * | 2010-03-17 | 2011-10-06 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9461122B2 (en) | 2014-03-19 | 2016-10-04 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method for the same |

| US10026804B2 (en) | 2014-03-19 | 2018-07-17 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US10714566B2 (en) | 2014-03-19 | 2020-07-14 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US9722067B2 (en) | 2015-09-10 | 2017-08-01 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US10332997B2 (en) | 2017-11-10 | 2019-06-25 | Hitachi, Ltd. | Semiconductor device and method of manufacturing semiconductor device |

| CN113316837A (zh) * | 2019-01-21 | 2021-08-27 | 株式会社电装 | 半导体装置的制造方法 |

| CN113316837B (zh) * | 2019-01-21 | 2023-12-05 | 株式会社电装 | 半导体装置的制造方法 |

| KR20220100492A (ko) * | 2021-01-08 | 2022-07-15 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 메모리 윈도우를 확대하기 위한 분극 강화 구조물 |

| US11705516B2 (en) | 2021-01-08 | 2023-07-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Polarization enhancement structure for enlarging memory window |

| KR102640580B1 (ko) * | 2021-01-08 | 2024-02-23 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 메모리 윈도우를 확대하기 위한 분극 강화 구조물 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10943833B2 (en) | Silicon and silicon germanium nanowire formation | |

| CN104835847B (zh) | 半导体器件 | |

| US10522532B2 (en) | Through via extending through a group III-V layer | |

| KR101315009B1 (ko) | 고전압 접합 종단을 갖는 고전압 저항기 | |

| US8461647B2 (en) | Semiconductor device having multi-thickness gate dielectric | |

| US9035355B2 (en) | Multi-channel HEMT | |

| KR101813177B1 (ko) | 고전자이동도 트랜지스터 및 그 제조방법 | |

| US8890244B2 (en) | Lateral power MOSFET structure and method of manufacture | |

| TWI578528B (zh) | 具有內埋層之半導體裝置及其製造方法 | |

| US8766276B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| US10164049B2 (en) | Structure and formation method of semiconductor device with gate stack | |

| KR20160038011A (ko) | 추가적인 소자를 생성하기 위한 폴리실리콘 층을 갖는 GaN 트랜지스터 | |

| TW201919243A (zh) | 半導體裝置以及其製造方法 | |

| CN111129123B (zh) | 接触场板蚀刻的组合蚀刻停止层、集成芯片及其形成方法 | |

| JP2013093482A (ja) | 半導体装置および半導体装置の製造方法 | |

| CN110957257B (zh) | 绝缘体上半导体衬底、其形成方法以及集成电路 | |

| JP2013069778A (ja) | 半導体装置 | |

| CN108475693A (zh) | 具有可调功函数的场效应晶体管叠层 | |

| TWI634660B (zh) | 高壓半導體裝置及其製造方法 | |

| JP6084357B2 (ja) | 半導体装置 | |

| US20120061747A1 (en) | Semiconductor device | |

| US8258584B2 (en) | Offset gate semiconductor device | |

| US20190019869A1 (en) | Semiconductor device and method for manufacturing the same | |

| CN107026166B (zh) | 半导体装置及方法 | |

| US20130102117A1 (en) | Manufacturing Processes for Field Effect Transistors Having Strain-Induced Chanels |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140804 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140804 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150717 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150825 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151002 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160426 |