JP2012504792A - 記憶制御装置及び記憶制御装置の制御方法 - Google Patents

記憶制御装置及び記憶制御装置の制御方法 Download PDFInfo

- Publication number

- JP2012504792A JP2012504792A JP2011514949A JP2011514949A JP2012504792A JP 2012504792 A JP2012504792 A JP 2012504792A JP 2011514949 A JP2011514949 A JP 2011514949A JP 2011514949 A JP2011514949 A JP 2011514949A JP 2012504792 A JP2012504792 A JP 2012504792A

- Authority

- JP

- Japan

- Prior art keywords

- microprocessor

- control information

- update

- shared

- local

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0815—Cache consistency protocols

- G06F12/0837—Cache consistency protocols with software control, e.g. non-cacheable data

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Multi Processors (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Abstract

Description

共有メモリには、共有制御情報に加えて、共有制御情報の更新状態を管理するための共有制御情報更新管理部が設けられており、

各ローカルメモリには、ローカル制御情報及びパージメッセージ記憶部に加えて、ローカル制御情報の更新状態を管理するためのローカル更新管理部と、共有制御情報更新管理部で管理されている更新状態を示す値のコピーを記憶する更新値記憶部とが記憶されており、

共有制御情報更新管理部は、各マイクロプロセッサパッケージ内の各マイクロプロセッサを識別するためのマイクロプロセッサ識別情報と、各マイクロプロセッサにより更新された回数を示すカウンタ値とを対応付けて管理しており、さらに、マイクロプロセッサにより共有制御情報が更新される場合に、更新元のマイクロプロセッサによって当該更新元のマイクロプロセッサに対応するカウンタ値が更新されるようになっており、

各ローカル更新管理部も、各マイクロプロセッサ識別情報毎にカウンタ値を対応付けて管理しており、さらに、各ローカル更新管理部に対応する各マイクロプロセッサがローカル制御情報を更新する場合に、その対応するマイクロプロセッサに関連するカウンタ値が更新されるようになっており、さらに、対応するマイクロプロセッサ以外の他のマイクロプロセッサに関連するパージメッセージに基づいて、他のマイクロプロセッサに対応するカウンタ値が更新されるようになっており、

各更新値記憶部に対応する各マイクロプロセッサが共有メモリ内の共有制御情報にアクセスした場合に、共有制御情報更新管理部で管理されている各カウンタ値が取得されて、それら取得された各カウンタ値が更新値記憶部に上書きで記憶されるようになっており、

共有メモリは、各マイクロプロセッサが各ローカルメモリにコピー可能な情報を記憶するための共有キャッシュ領域と、各マイクロプロセッサのうちオーナーとして設定されるオーナーマイクロプロセッサのみが、オーナーマイクロプロセッサ内のローカルメモリにコピー可能であり、かつ、オーナーマイクロプロセッサ以外の他のマイクロプロセッサはコピーできない情報を記憶するための排他キャッシュ領域と、各マイクロプロセッサのいずれもが各ローカルメモリにコピーできない情報を記憶するための非キャッシュ領域と、を備えており、

共有キャッシュ領域には、比較的更新頻度が少ないが複数のマイクロプロセッサから比較的高頻度でアクセスされ得る第1情報が記憶されるようになっており、

排他キャッシュ領域には、オーナーマイクロプロセッサが比較的高頻度に参照または更新する第2情報が記憶されるようになっており、

非キャッシュ領域には、複数のマイクロプロセッサから比較的高頻度で参照または更新される第3情報が記憶されるようになっており、

各マイクロプロセッサは、

共有キャッシュ領域に記憶されている情報を更新した場合には、更新のたびにパージメッセージを作成してパージメッセージ記憶部に記憶させ、一連の更新処理が完了した後で、パージメッセージ記憶部に記憶された各パージメッセージを他の各マイクロプロセッサにそれぞれ送信し、

排他キャッシュ領域に記憶されている情報を更新する場合において、自分がオーナーマイクロプロセッサである場合は、パージメッセージを作成せず、自分がオーナーマイクロプロセッサ以外の他のマイクロプロセッサである場合は、更新のたびにパージメッセージを作成してパージメッセージ記憶部に記憶させ、一連の更新処理が完了した後で、パージメッセージ記憶部に記憶された各パージメッセージをオーナーマイクロプロセッサのみに送信し、

非キャッシュ領域に記憶されている情報を更新した場合には、パージメッセージを作成しないようになっており、

さらに、各マイクロプロセッサは、共有制御情報のうち同一箇所の更新、または、連続する箇所の更新、または、重複する箇所の更新がされた場合には、複数の更新を統合するようにしてパージメッセージを送信させるようになっている。

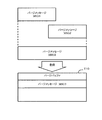

3:マイクロプロセッサパッケージ

4:共有メモリ

5:スイッチ

6:マイクロプロセッサ

7:ローカルメモリ

8A:共有キャッシュ領域

8B:排他キャッシュ領域

8C:非キャッシュ領域

10:記憶制御装置

110:フロントエンドパッケージ

120:マイクロプロセッサパッケージ

121:マイクロプロセッサ

122:ローカルメモリ

130:メモリパッケージ

131:共有メモリ

140:バックエンドパッケージ

151:記憶装置

Channel)ディスク、SCSI(Small Computer System Interface)ディスク、SATAディスク、ATA(AT Attachment)ディスク、SAS(Serial Attached SCSI)ディスク等を用いることができる。

なお、本発明は、上述した実施例に限定されない。当業者であれば、本発明の範囲内で、種々の追加や変更等を行うことができる。例えば、各実施例を適宜組み合わせる構成としてもよい。

Claims (15)

- ホストコンピュータ(2,30)と記憶装置(151)との間のデータ入出力を制御する記憶制御装置(1,10)であって、

共有制御情報を記憶する共有メモリ(4,131)と、

複数のマイクロプロセッサ(6,121)と、

前記各マイクロプロセッサにそれぞれ対応して設けられるローカルメモリ(7,122)であって、前記共有メモリに記憶される前記共有制御情報のうち少なくとも一部がローカル制御情報としてコピーされる各ローカルメモリと、

前記各マイクロプロセッサのうちの一つのマイクロプロセッサから他の前記各マイクロプロセッサに、または、特定の一つまたは複数の前記マイクロプロセッサに、向けて送信されるパージメッセージであって、前記ローカルメモリに記憶されている前記ローカル制御情報が無効である旨を通知するためのパージメッセージを記憶するパージメッセージ記憶部(7B,T10)と、

前記各ローカル制御情報が前記共有制御情報に同期しているか否かを管理するための制御情報同期管理部と、

を備え、

前記各マイクロプロセッサは、前記共有制御情報を更新する場合に、前記パージメッセージを作成して前記パージメッセージ記憶部に記憶させ、さらに、前記共有制御情報の更新と非同期で、前記パージメッセージ記憶部に記憶された前記パージメッセージを送信させる、

記憶制御装置。

- 複数のマイクロプロセッサパッケージ(3,120)を備え、前記各マイクロプロセッサパッケージは、少なくとも一つの前記マイクロプロセッサと、少なくとも一つの前記ローカルメモリと、少なくとも一つの前記パージメッセージ記憶部とを備えており、

前記各マイクロプロセッサパッケージと前記共有メモリとは、スイッチ(5,160)を介して接続されており、

前記共有メモリには、前記共有制御情報に加えて、前記共有制御情報の更新状態を管理するための共有制御情報更新管理部(9,T13)が設けられており、

前記各ローカルメモリには、前記ローカル制御情報及び前記パージメッセージ記憶部に加えて、ローカル制御情報の更新状態を管理するためのローカル更新管理部(7C,T11)と、前記共有制御情報更新管理部で管理されている前記更新状態を示す値のコピーを記憶する更新値記憶部(7D,T12)とが記憶されており、

前記共有制御情報更新管理部は、前記各マイクロプロセッサパッケージ内の前記各マイクロプロセッサを識別するためのマイクロプロセッサ識別情報と、前記各マイクロプロセッサにより更新された回数を示すカウンタ値とを対応付けて管理しており、さらに、前記マイクロプロセッサにより前記共有制御情報が更新される場合に、更新元のマイクロプロセッサによって当該更新元のマイクロプロセッサに対応する前記カウンタ値が更新されるようになっており、

前記各ローカル更新管理部も、前記各マイクロプロセッサ識別情報毎に前記カウンタ値を対応付けて管理しており、さらに、前記各ローカル更新管理部に対応する前記各マイクロプロセッサが前記ローカル制御情報を更新する場合に、その対応する前記マイクロプロセッサに関連するカウンタ値が更新されるようになっており、さらに、前記対応する前記マイクロプロセッサ以外の他の前記マイクロプロセッサに関連する前記パージメッセージに基づいて、前記他の前記マイクロプロセッサに対応するカウンタ値が更新されるようになっており、

前記各更新値記憶部に対応する前記各マイクロプロセッサが前記共有メモリ内の前記共有制御情報にアクセスした場合に、前記共有制御情報更新管理部で管理されている前記各カウンタ値が取得されて、それら取得された前記各カウンタ値が前記更新値記憶部に上書きで記憶されるようになっており、

前記共有メモリは、前記各マイクロプロセッサが前記各ローカルメモリにコピー可能な情報を記憶するための共有キャッシュ領域(8A,1311)と、前記各マイクロプロセッサのうちオーナーとして設定されるオーナーマイクロプロセッサのみが、前記オーナーマイクロプロセッサ内の前記ローカルメモリにコピー可能であり、かつ、前記オーナーマイクロプロセッサ以外の他のマイクロプロセッサはコピーできない情報を記憶するための排他キャッシュ領域(8B,1312)と、前記各マイクロプロセッサのいずれもが前記各ローカルメモリにコピーできない情報を記憶するための非キャッシュ領域(8C,1313)と、を備えており、

前記共有キャッシュ領域には、比較的更新頻度が少ないが複数のマイクロプロセッサから比較的高頻度でアクセスされ得る第1情報(D1,D11)が記憶されるようになっており、

前記排他キャッシュ領域には、前記オーナーマイクロプロセッサが比較的高頻度に参照または更新する第2情報(D2,D12)が記憶されるようになっており、

前記非キャッシュ領域には、複数のマイクロプロセッサから比較的高頻度で参照または更新される第3情報(D3,D13)が記憶されるようになっており、

前記各マイクロプロセッサは、

前記共有キャッシュ領域に記憶されている情報を更新した場合には、前記更新のたびに前記パージメッセージを作成して前記パージメッセージ記憶部に記憶させ、一連の更新処理が完了した後で、前記パージメッセージ記憶部に記憶された前記各パージメッセージを他の各マイクロプロセッサにそれぞれ送信し、

前記排他キャッシュ領域に記憶されている情報を更新する場合において、自分が前記オーナーマイクロプロセッサである場合は、前記パージメッセージを作成せず、自分が前記オーナーマイクロプロセッサ以外の他のマイクロプロセッサである場合は、更新のたびに前記パージメッセージを作成して前記パージメッセージ記憶部に記憶させ、一連の更新処理が完了した後で、前記パージメッセージ記憶部に記憶された前記各パージメッセージを前記オーナーマイクロプロセッサのみに送信し、

前記非キャッシュ領域に記憶されている情報を更新した場合には、前記パージメッセージを作成しないようになっており、

さらに、前記各マイクロプロセッサは、前記共有制御情報のうち同一箇所の更新、または、連続する箇所の更新、または、重複する箇所の更新がされた場合には、複数の更新を統合するようにして前記パージメッセージを送信させるようになっている、

請求項1に記載の記憶制御装置。

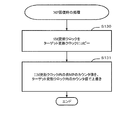

- 前記各マイクロプロセッサは、前記制御情報同期管理部に基づいて前記各ローカル制御情報が前記共有制御情報に同期していると判定される場合は、対応する前記各ローカルメモリから前記ローカル制御情報を使用し、前記制御情報同期管理部に基づいて前記各ローカル制御情報が前記共有制御情報に同期していないと判定される場合は、前記共有メモリ内の前記共有制御情報を使用する、

請求項1に記載の記憶制御装置。

- 前記共有メモリには、前記共有制御情報に加えて、前記共有制御情報の更新状態を管理するための共有制御情報更新管理部(9,T13)が設けられており、

前記各ローカルメモリには、前記ローカル制御情報及び前記パージメッセージ記憶部に加えて、ローカル制御情報の更新状態を管理するためのローカル更新管理部(7C,T11)と、前記共有制御情報更新管理部で管理されている前記更新状態を示す値のコピーを記憶する更新値記憶部(7D,T12)とが記憶されており、

前記制御情報同期管理部は、前記共有制御情報更新管理部と、前記各ローカル更新管理部と、前記各更新値管理部とを備えて構成される、

請求項1に記載の記憶制御装置。

- 前記共有制御情報更新管理部は、前記各マイクロプロセッサパッケージ内の前記各マイクロプロセッサを識別するためのマイクロプロセッサ識別情報と、前記各マイクロプロセッサにより更新された回数を示すカウンタ値とを対応付けて管理しており、さらに、前記マイクロプロセッサにより前記共有制御情報が更新される場合に、更新元のマイクロプロセッサによって当該更新元のマイクロプロセッサに対応する前記カウンタ値が更新されるようになっており、

前記各ローカル更新管理部も、前記各マイクロプロセッサ識別情報毎に前記カウンタ値を対応付けて管理しており、さらに、前記各ローカル更新管理部に対応する前記各マイクロプロセッサが前記ローカル制御情報を更新する場合に、その対応する前記マイクロプロセッサに関連するカウンタ値が更新されるようになっており、さらに、前記対応する前記マイクロプロセッサ以外の他の前記マイクロプロセッサに関連する前記パージメッセージに基づいて、前記他の前記マイクロプロセッサに対応するカウンタ値が更新されるようになっている、

請求項4に記載の記憶制御装置。

- 前記各更新値記憶部に対応する前記各マイクロプロセッサが前記共有メモリ内の前記共有制御情報にアクセスした場合に、前記共有制御情報更新管理部で管理されている前記各カウンタ値が取得されて、それら取得された前記各カウンタ値が前記更新値記憶部に上書きで記憶されるようになっている、

請求項5に記載の記憶制御装置。

- 前記共有メモリは、

前記各マイクロプロセッサが前記各ローカルメモリにコピー可能な情報を記憶するための共有キャッシュ領域(8A,1311)と、

前記各マイクロプロセッサのうちオーナーとして設定されるオーナーマイクロプロセッサのみが、前記オーナーマイクロプロセッサ内の前記ローカルメモリにコピー可能であり、かつ、前記オーナーマイクロプロセッサ以外の他のマイクロプロセッサはコピーできない情報を記憶するための排他キャッシュ領域(8B,1312)と、

を備えている、

請求項1に記載の記憶制御装置。

- 前記共有メモリは、

前記各マイクロプロセッサが前記各ローカルメモリにコピー可能な情報を記憶するための共有キャッシュ領域(8A,1311)と、

前記各マイクロプロセッサのいずれもが前記各ローカルメモリにコピーできない情報を記憶するための非キャッシュ領域(8C,1313)と、

を備えている、

請求項1に記載の記憶制御装置。

- 前記共有メモリは、

前記各マイクロプロセッサのうちオーナーとして設定されるオーナーマイクロプロセッサのみが、前記オーナーマイクロプロセッサ内の前記ローカルメモリにコピー可能であり、かつ、前記オーナーマイクロプロセッサ以外の他のマイクロプロセッサはコピーできない情報を記憶するための排他キャッシュ領域(8B,1312)と、

前記各マイクロプロセッサのいずれもが前記各ローカルメモリにコピーできない情報を記憶するための非キャッシュ領域(8C,1313)と、

を備えている、

請求項1に記載の記憶制御装置。

- 前記共有メモリは、

前記各マイクロプロセッサが前記各ローカルメモリにコピー可能な情報を記憶するための共有キャッシュ領域(8A,1311)と、

前記各マイクロプロセッサのうちオーナーとして設定されるオーナーマイクロプロセッサのみが、前記オーナーマイクロプロセッサ内の前記ローカルメモリにコピー可能であり、かつ、前記オーナーマイクロプロセッサ以外の他のマイクロプロセッサはコピーできない情報を記憶するための排他キャッシュ領域(8B,1312)と、

前記各マイクロプロセッサのいずれもが前記各ローカルメモリにコピーできない情報を記憶するための非キャッシュ領域(8C,1313)と、

を備えている、

請求項1に記載の記憶制御装置。

- 前記共有キャッシュ領域には、比較的更新頻度が少ないが複数のマイクロプロセッサから比較的高頻度でアクセスされ得る第1情報(D1,D11)が記憶されるようになっており、

前記排他キャッシュ領域には、前記オーナーマイクロプロセッサが比較的高頻度に参照または更新する第2情報(D2,D12)が記憶されるようになっており、

前記非キャッシュ領域には、複数のマイクロプロセッサから比較的高頻度で参照または更新される第3情報(D3,D13)が記憶されるようになっている、

請求項10に記載の記憶制御装置。

- 前記各マイクロプロセッサは、

前記共有キャッシュ領域に記憶されている情報を更新した場合には、前記更新のたびに前記パージメッセージを作成して前記パージメッセージ記憶部に記憶させ、一連の更新処理が完了した後で、前記パージメッセージ記憶部に記憶された前記各パージメッセージを他の各マイクロプロセッサにそれぞれ送信し、

前記排他キャッシュ領域に記憶されている情報を更新する場合において、自分が前記オーナーマイクロプロセッサである場合は、前記パージメッセージを作成せず、自分が前記オーナーマイクロプロセッサ以外の他のマイクロプロセッサである場合は、更新のたびに前記パージメッセージを作成して前記パージメッセージ記憶部に記憶させ、一連の更新処理が完了した後で、前記パージメッセージ記憶部に記憶された前記各パージメッセージを前記オーナーマイクロプロセッサのみに送信し、

前記非キャッシュ領域に記憶されている情報を更新した場合には、前記パージメッセージを作成しないようになっている、

請求項10または請求項11のいずれかに記載の記憶制御装置。

- 前記各マイクロプロセッサは、前記共有制御情報のうち同一箇所の更新、または、連続する箇所の更新、または、重複する箇所の更新がされた場合に、複数の更新を統合するようにして前記パージメッセージを送信させる、

請求項1に記載の記憶制御装置。

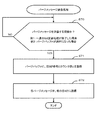

- 前記各マイクロプロセッサは、

他の各マイクロプロセッサが正常に監視しているか否かを監視しており(S120)、

いずれかのマイクロプロセッサで障害が発生した場合には(S121)、前記共有制御情報更新管理部で管理されている各カウント値を取得して前記更新値記憶部に上書きで記憶し(S123)、

前記障害の発生した前記マイクロプロセッサについて、前記ローカル更新管理部で管理されているカウント値と前記更新値管理部に記憶されているカウント値と異なるか否かを判定し(S124)、

前記ローカル更新管理部で管理されているカウント値と前記更新値管理部に記憶されているカウント値とが異なる場合、前記ローカル更新管理部で管理されている前記障害の発生した前記マイクロプロセッサの前記カウント値を、前記更新値管理部内の対応するカウント値で上書きし(S125)、

前記ローカルメモリにコピーされているローカル制御情報をクリアさせる(S126)、

請求項1に記載の記憶制御装置。

- 共有制御情報を記憶する共有メモリ(4,131)と、複数のマイクロプロセッサ(6,121)と、前記各マイクロプロセッサにそれぞれ対応して設けられるローカルメモリ(7,122)とを備える記憶制御装置の制御方法であって、

前記各ローカルメモリには、前記共有メモリに記憶される前記共有制御情報のうち少なくとも一部がローカル制御情報としてコピーされており、

前記共有制御情報を更新する場合には、更新元のマイクロプロセッサに対応する前記ローカルメモリ以外の他の前記各ローカルメモリに記憶されている前記ローカル制御情報が無効であることを示すパージメッセージを作成して保存し、

前記共有制御情報を更新する一連の処理が完了した場合に、前記保存されている前記パージメッセージを前記他の前記各ローカルメモリに対応する前記各マイクロプロセッサに送信し、

前記パージメッセージを受信した前記他の前記各マイクロプロセッサは、前記無効とされた箇所の情報を使用する場合に、前記共有メモリにアクセスして取得するようになっている、

記憶制御装置の制御方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2009/000645 WO2010095166A1 (en) | 2009-02-17 | 2009-02-17 | Storage controller and method of controlling storage controller |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012504792A true JP2012504792A (ja) | 2012-02-23 |

| JP5198659B2 JP5198659B2 (ja) | 2013-05-15 |

Family

ID=40801761

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011514949A Expired - Fee Related JP5198659B2 (ja) | 2009-02-17 | 2009-02-17 | 記憶制御装置及び記憶制御装置の制御方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8527710B2 (ja) |

| EP (1) | EP2344947B1 (ja) |

| JP (1) | JP5198659B2 (ja) |

| WO (1) | WO2010095166A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014527204A (ja) * | 2011-10-07 | 2014-10-09 | 株式会社日立製作所 | ストレージシステム |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9223699B2 (en) * | 2013-03-15 | 2015-12-29 | Intel Corporation | Cache management in managed runtime environments |

| WO2015030819A1 (en) * | 2013-08-30 | 2015-03-05 | Hewlett-Packard Development Company, L.P. | Completion packet return |

| US20150370707A1 (en) * | 2014-06-24 | 2015-12-24 | Qualcomm Incorporated | Disunited shared-information and private-information caches |

| US10705958B2 (en) * | 2018-08-22 | 2020-07-07 | Advanced Micro Devices, Inc. | Coherency directory entry allocation based on eviction costs |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02226449A (ja) * | 1989-02-28 | 1990-09-10 | Toshiba Corp | キャッシュメモリ制御方式 |

| JPH05298122A (ja) * | 1992-04-17 | 1993-11-12 | Daikin Ind Ltd | マルチタスク処理装置 |

| JPH09138783A (ja) * | 1995-11-15 | 1997-05-27 | Hitachi Ltd | マルチプロセッサシステム |

| JPH10301659A (ja) * | 1997-04-28 | 1998-11-13 | Hitachi Ltd | マイクロプロセッサ |

| JPH11102321A (ja) * | 1997-09-26 | 1999-04-13 | Nec Corp | 分散共有メモリ型並列計算機のキャッシュコヒーレンシ制御方式 |

| JPH11272552A (ja) * | 1998-03-24 | 1999-10-08 | Mitsubishi Electric Corp | ブリッジ方法、バスブリッジ及びマルチプロセッサシステム |

| JP2003044358A (ja) * | 2001-07-31 | 2003-02-14 | Mitsubishi Electric Corp | キャッシュメモリ制御装置 |

| JP2003316753A (ja) * | 2002-04-26 | 2003-11-07 | Fujitsu Ltd | マルチプロセッサ装置 |

| JP2006011932A (ja) * | 2004-06-28 | 2006-01-12 | Hitachi Ltd | ストレージ装置及びストレージ装置の排他制御方法 |

| JP2007249573A (ja) * | 2006-03-15 | 2007-09-27 | Hitachi Ltd | 自動拡張可能なボリュームに対して最適なi/oコマンドを発行するストレージシステム及びその制御方法 |

| JP2007280127A (ja) * | 2006-04-07 | 2007-10-25 | Oki Electric Ind Co Ltd | プロセッサ間通信方法 |

| JP2008065706A (ja) * | 2006-09-08 | 2008-03-21 | Hitachi Ltd | 記憶システム及びその制御方法並びに記憶制御装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0340046A (ja) * | 1989-07-06 | 1991-02-20 | Hitachi Ltd | キャッシュメモリ制御方式および情報処理装置 |

| US5506967A (en) * | 1993-06-15 | 1996-04-09 | Unisys Corporation | Storage queue with adjustable level thresholds for cache invalidation systems in cache oriented computer architectures |

| JP3858492B2 (ja) * | 1998-12-28 | 2006-12-13 | 株式会社日立製作所 | マルチプロセッサシステム |

| JP2002032265A (ja) * | 2000-07-14 | 2002-01-31 | Hitachi Ltd | キャッシュ・アクセス制御方式およびデータ処理システム |

| US7243229B2 (en) * | 2001-10-02 | 2007-07-10 | Hitachi, Ltd. | Exclusive access control apparatus and method |

| US7117315B2 (en) * | 2002-06-27 | 2006-10-03 | Fujitsu Limited | Method and apparatus for creating a load module and a computer product thereof |

| JP2005267008A (ja) * | 2004-03-17 | 2005-09-29 | Hitachi Ltd | ストレージ管理方法およびストレージ管理システム |

| JP4794194B2 (ja) | 2005-04-01 | 2011-10-19 | 株式会社日立製作所 | ストレージシステム及び記憶制御方法 |

| JP4859471B2 (ja) * | 2006-02-02 | 2012-01-25 | 株式会社日立製作所 | ストレージシステム及びストレージコントローラ |

| JP5183403B2 (ja) | 2008-09-30 | 2013-04-17 | 株式会社日立製作所 | ストレージシステムおよび制御プログラムならびにストレージシステム制御方法 |

-

2009

- 2009-02-17 WO PCT/JP2009/000645 patent/WO2010095166A1/en not_active Ceased

- 2009-02-17 EP EP09787855A patent/EP2344947B1/en not_active Not-in-force

- 2009-02-17 JP JP2011514949A patent/JP5198659B2/ja not_active Expired - Fee Related

- 2009-02-17 US US12/310,448 patent/US8527710B2/en not_active Expired - Fee Related

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02226449A (ja) * | 1989-02-28 | 1990-09-10 | Toshiba Corp | キャッシュメモリ制御方式 |

| JPH05298122A (ja) * | 1992-04-17 | 1993-11-12 | Daikin Ind Ltd | マルチタスク処理装置 |

| JPH09138783A (ja) * | 1995-11-15 | 1997-05-27 | Hitachi Ltd | マルチプロセッサシステム |

| JPH10301659A (ja) * | 1997-04-28 | 1998-11-13 | Hitachi Ltd | マイクロプロセッサ |

| JPH11102321A (ja) * | 1997-09-26 | 1999-04-13 | Nec Corp | 分散共有メモリ型並列計算機のキャッシュコヒーレンシ制御方式 |

| JPH11272552A (ja) * | 1998-03-24 | 1999-10-08 | Mitsubishi Electric Corp | ブリッジ方法、バスブリッジ及びマルチプロセッサシステム |

| JP2003044358A (ja) * | 2001-07-31 | 2003-02-14 | Mitsubishi Electric Corp | キャッシュメモリ制御装置 |

| JP2003316753A (ja) * | 2002-04-26 | 2003-11-07 | Fujitsu Ltd | マルチプロセッサ装置 |

| JP2006011932A (ja) * | 2004-06-28 | 2006-01-12 | Hitachi Ltd | ストレージ装置及びストレージ装置の排他制御方法 |

| JP2007249573A (ja) * | 2006-03-15 | 2007-09-27 | Hitachi Ltd | 自動拡張可能なボリュームに対して最適なi/oコマンドを発行するストレージシステム及びその制御方法 |

| JP2007280127A (ja) * | 2006-04-07 | 2007-10-25 | Oki Electric Ind Co Ltd | プロセッサ間通信方法 |

| JP2008065706A (ja) * | 2006-09-08 | 2008-03-21 | Hitachi Ltd | 記憶システム及びその制御方法並びに記憶制御装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014527204A (ja) * | 2011-10-07 | 2014-10-09 | 株式会社日立製作所 | ストレージシステム |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2344947B1 (en) | 2012-07-04 |

| WO2010095166A1 (en) | 2010-08-26 |

| EP2344947A1 (en) | 2011-07-20 |

| US20110029736A1 (en) | 2011-02-03 |

| US8527710B2 (en) | 2013-09-03 |

| JP5198659B2 (ja) | 2013-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4738941B2 (ja) | ストレージシステム及びストレージシステムの管理方法 | |

| US7783850B2 (en) | Method and apparatus for master volume access during volume copy | |

| JP4387116B2 (ja) | ストレージシステムの制御方法、及びストレージシステム | |

| US9069476B2 (en) | Method for managing storage system using flash memory, and computer | |

| US9262265B2 (en) | Storage system and storage control apparatus | |

| US8495288B2 (en) | Storage controller and duplicated data detection method using storage controller | |

| US20150012699A1 (en) | System and method of versioning cache for a clustering topology | |

| US8825975B2 (en) | Caching source blocks of data for target blocks of data | |

| US8949536B2 (en) | Prefetching source tracks for destaging updated tracks in a copy relationship | |

| US20050182906A1 (en) | Systems and methods for cache synchronization between redundant storage controllers | |

| JP7010809B2 (ja) | デデュープ可能なメモリキャッシュ及びそのための動作方法 | |

| US20150339058A1 (en) | Storage system and control method | |

| US8627011B2 (en) | Managing metadata for data in a copy relationship | |

| US10754780B2 (en) | Maintaining track format metadata for target tracks in a target storage in a copy relationship with source tracks in a source storage | |

| JP4920291B2 (ja) | 計算機システム、アクセス制御方法及び管理計算機 | |

| JP4911198B2 (ja) | ストレージ制御装置、ストレージシステムおよびストレージ制御方法 | |

| CN100421080C (zh) | 改善资料写入效率的方法以及实施此方法的子系统与系统 | |

| JP5198659B2 (ja) | 記憶制御装置及び記憶制御装置の制御方法 | |

| JP2008269374A (ja) | ストレージシステムおよびその制御方法 | |

| CN110502188A (zh) | 一种基于数据库读写性能的数据存储方法与装置 | |

| WO2015011825A1 (ja) | ストレージシステムおよびストレージシステムの制御方法 | |

| CN106610788B (zh) | 硬盘阵列控制方法及装置 | |

| US6732194B1 (en) | Method and apparatus for multi-sequential data operations | |

| EP1855187A2 (en) | Computer system for managing number of writes for storage medium and control method therefor | |

| US9864688B1 (en) | Discarding cached data before cache flush |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120608 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120619 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120820 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130129 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130206 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5198659 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |