JP2012155195A - ブザー駆動回路 - Google Patents

ブザー駆動回路 Download PDFInfo

- Publication number

- JP2012155195A JP2012155195A JP2011015275A JP2011015275A JP2012155195A JP 2012155195 A JP2012155195 A JP 2012155195A JP 2011015275 A JP2011015275 A JP 2011015275A JP 2011015275 A JP2011015275 A JP 2011015275A JP 2012155195 A JP2012155195 A JP 2012155195A

- Authority

- JP

- Japan

- Prior art keywords

- transistors

- pair

- voltage

- power supply

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

- 238000010586 diagram Methods 0.000 description 10

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

Images

Landscapes

- Electronic Switches (AREA)

Abstract

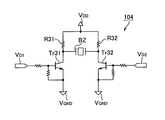

【解決手段】互いに極性の異なる一対のトランジスタTr1及びTr2が、10V系の電源電圧VDD間に直列接続される。互いに極性の異なる一対のトランジスタTr3及びTr4が、電源電圧VDD間に直列接続されると共に一対のトランジスタTr1及びTr2に並列接続される。ブザーBZが、トランジスタTr1及びTr2の接続点と、トランジスタTr3及びTr4の接続点と、の間に接続される。第1レベルシフト回路31が、5V系の駆動電圧VD1を10V系の駆動電圧Vb1にレベルアップしてトランジスタTr1及びTr2のベースに供給する。第2レベルシフト回路32が、5V系の駆動電圧VD2を10V系の駆動電圧Vb2にレベルアップしてトランジスタTr3及びTr4のベースに供給する。

【選択図】図1

Description

以下、第1実施形態における本発明のブザー駆動回路を図1及び図2に基づいて説明する。図1は、第1実施形態における本発明のブザー駆動回路を示す回路図である。図2(A)〜(H)は、図1に示すブザー駆動回路を構成するCPUから出力される駆動電圧VD1及びVD2、トランジスタTr5〜Tr8のオンオフ状態、駆動電圧Vb1及びVb2、トランジスタTr1〜Tr4のオンオフ状態を示すタイムチャートである。

VBZ=10V(VDD)−0.8V(トランジスタTr1のベースエミッタ間電圧)−0.8(トランジスタTr4のベースエミッタ間電圧)=8.4V…(1)

結果、ブザー電圧VBZの振幅はその2倍の16.8Vとなる。

次に、第2実施形態における本発明のブザー駆動回路を図4に基づいて説明する。図4は、第2実施形態における本発明のブザー駆動回路を示す回路図である。第1実施形態と第2実施形態とで大きく異なる点は、トランジスタTr1〜Tr1の極性である。即ち、第1実施形態では、NPN型のトランジスタTr1及びTr3、PNP型のトランジスタTr2及びTr4を用いていたが、第2実施形態ではプッシュプル回路を廃止してPNP型のトランジスタTr1及びTr3、NPN型のトランジスタTr2及びTr4を用いている。なお、トランジスタTr1〜Tr4の極性を変えることにより、第2実施形態においては、駆動電圧VD1がHレベル、駆動電圧VD2がLレベルのときは、第1実施形態とは逆に、トランジスタTr1及びTr4がオフ、トランジスタTr2及びTr3がオンし、駆動電圧VD1がLレベル、駆動電圧VD2がHレベルのときは、トランジスタTr1及びTr4がオン、トランジスタTr2及びTr3がオフする。

VBZ=10V(VDD)−0.1V(トランジスタTr1のコレクタエミッタ間電圧Vce)−0.1(トランジスタTr4のコレクタエミッタ間電圧Vce)=9.8V…(2)

結果、ブザー電圧VBZの振幅はその2倍の19.6Vとなり、第1実施形態よりも振幅を大きくして音圧を高くできる。

次に、第3実施形態について説明する。ところで、上述した第2実施形態では、図6に示すように、トランジスタTr1及びT2のベース、トランジスタTr3及びTr4のベースを共通接続すると、トランジスタTr1、Tr3のベースエミッタ間に等価されるダイオードD5と、トランジスタTr2、Tr4のベースエミッタ間に等価されるダイオードD8と、の順方向が電源電圧VDDの印加方向と同一になってしまうため、図中点線で示すように、トランジスタTr1〜Tr4がオフのときに共通接続されたベースを介して電流が流れてしまう。

31 第1レベルシフト回路

32 第2レベルシフト回路

BZ ブザー

R24 第1抵抗

R25 第1抵抗

R26 第2抵抗

R27 第2抵抗

Tr1 トランジスタ(第1トランジスタ)

Tr2 トランジスタ(第1トランジスタ)

Tr3 トランジスタ(第2トランジスタ)

Tr4 トランジスタ(第2トランジスタ)

VD1 駆動電圧

VD2 駆動電圧

VDD 電源電圧

Claims (4)

- パルス状の駆動電圧を出力する出力手段と、前記駆動電圧の出力に応じて鳴動するブザーと、前記駆動電圧よりも高い電源電圧を供給する電圧源と、互いに極性が異なりかつ前記電源電圧間に直列接続された一対の第1トランジスタと、互いに極性が異なりかつ前記電源電圧間に直列接続されると共に前記一対の第1トランジスタに並列接続された一対の第2トランジスタと、を備え、前記ブザーが、前記一対の第1トランジスタ同士の接続点と前記一対の第2トランジスタ同士の接続点との間に接続され、前記一対の第1トランジスタの前記電源電圧プラス側及び前記一対の第2トランジスタの前記電源電圧マイナス側と、前記一対の第1トランジスタの前記電源電圧マイナス側及び前記一対の第2トランジスタの前記電源電圧プラス側と、のオンオフが互いに反転するように、前記一対の第1トランジスタ及び前記一対の第2トランジスタのベースに前記パルス状の駆動電圧が供給されたブザー駆動回路であって、

前記出力手段からの駆動電圧を前記電源電圧系の電圧にシフトアップして前記一対の第1トランジスタのうち少なくとも前記電源電圧プラス側のベースに出力する第1レベルシフト回路と、

前記出力手段からの駆動電圧を前記電源電圧系の電圧にシフトアップして前記一対の第2トランジスタのうち少なくとも前記電源電圧プラス側のベースに出力する第2レベルシフト回路と、

をさらに備えたことを特徴とするブザー駆動回路。 - 前記一対の第1トランジスタのうち前記電源電圧プラス側が、PNP型トランジスタで構成され、前記一対の第1トランジスタのうち前記電源電圧マイナス側が、NPN型トランジスタで構成され、

前記一対の第2トランジスタのうち前記電源電圧プラス側が、PNP型トランジスタで構成され、前記一対の第2トランジスタのうち前記電源電圧マイナス側が、NPN型トランジスタで構成されている

ことを特徴とする請求項1記載のブザー駆動回路。 - 前記出力手段が、互いにHレベル、Lレベルが反転した一対の前記パルス状の駆動電圧を出力し、

前記第1レベルシフト回路が、前記一対の駆動電圧の一方をシフトアップすると共に当該一方の駆動電圧のHレベル、Lレベルを反転させて前記一対の第1トランジスタのうち前記電源電圧プラス側のベースのみに出力し、

前記第2レベルシフト回路が、前記一対の駆動電圧の他方をシフトアップすると共に当該他方の駆動電圧のHレベル、Lレベルを反転させて前記一対の第2トランジスタのうち前記電源電圧プラス側のベースのみに出力し、

前記一対の第1トランジスタのうち前記電源電圧マイナス側のベースには、前記一対の駆動電圧の他方が供給され、

前記一対の第2トランジスタのうち前記電源電圧のマイナス側のベースには、前記一対の駆動電圧の一方が供給されている

ことを特徴とする請求項2に記載のブザー駆動回路。 - 前記一対の第1トランジスタ間に設けられた第1抵抗と、

前記一対の第2トランジスタ間に設けられた第2抵抗と、

をさらに備えたことを特徴とする請求項2又は3に記載のブザー駆動回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011015275A JP2012155195A (ja) | 2011-01-27 | 2011-01-27 | ブザー駆動回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011015275A JP2012155195A (ja) | 2011-01-27 | 2011-01-27 | ブザー駆動回路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012155195A true JP2012155195A (ja) | 2012-08-16 |

Family

ID=46836960

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011015275A Abandoned JP2012155195A (ja) | 2011-01-27 | 2011-01-27 | ブザー駆動回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012155195A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103281652A (zh) * | 2013-04-22 | 2013-09-04 | 无锡艾柯威科技有限公司 | 一种蜂鸣器驱动电路 |

| CN104575479A (zh) * | 2015-02-04 | 2015-04-29 | 常州东村电子有限公司 | 一种电磁式蜂鸣器主动方波驱动电路 |

| CN107680573A (zh) * | 2017-10-30 | 2018-02-09 | 联合汽车电子有限公司 | 蜂鸣器驱动电路 |

| CN108470558A (zh) * | 2018-05-30 | 2018-08-31 | 杭州百隆电子有限公司 | 一种蜂鸣器驱动电路及驱动系统 |

| CN111063330A (zh) * | 2020-01-22 | 2020-04-24 | 无锡十顶电子科技有限公司 | 一种低电压时增强驱动能力的蜂鸣器驱动电路 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS53129074A (en) * | 1977-04-18 | 1978-11-10 | Ricoh Watch | Alarm drive device for electronic timepiece |

| JPH08294177A (ja) * | 1995-04-20 | 1996-11-05 | Matsushita Electric Works Ltd | 電動式開閉装置の操作システム |

| JP2000261262A (ja) * | 1999-03-10 | 2000-09-22 | Yrp Kokino Idotai Tsushin Kenkyusho:Kk | 線形増幅回路 |

-

2011

- 2011-01-27 JP JP2011015275A patent/JP2012155195A/ja not_active Abandoned

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS53129074A (en) * | 1977-04-18 | 1978-11-10 | Ricoh Watch | Alarm drive device for electronic timepiece |

| JPH08294177A (ja) * | 1995-04-20 | 1996-11-05 | Matsushita Electric Works Ltd | 電動式開閉装置の操作システム |

| JP2000261262A (ja) * | 1999-03-10 | 2000-09-22 | Yrp Kokino Idotai Tsushin Kenkyusho:Kk | 線形増幅回路 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103281652A (zh) * | 2013-04-22 | 2013-09-04 | 无锡艾柯威科技有限公司 | 一种蜂鸣器驱动电路 |

| CN104575479A (zh) * | 2015-02-04 | 2015-04-29 | 常州东村电子有限公司 | 一种电磁式蜂鸣器主动方波驱动电路 |

| CN104575479B (zh) * | 2015-02-04 | 2018-06-05 | 常州东村电子有限公司 | 一种电磁式蜂鸣器主动方波驱动电路 |

| CN107680573A (zh) * | 2017-10-30 | 2018-02-09 | 联合汽车电子有限公司 | 蜂鸣器驱动电路 |

| CN107680573B (zh) * | 2017-10-30 | 2024-04-16 | 联合汽车电子有限公司 | 蜂鸣器驱动电路 |

| CN108470558A (zh) * | 2018-05-30 | 2018-08-31 | 杭州百隆电子有限公司 | 一种蜂鸣器驱动电路及驱动系统 |

| CN111063330A (zh) * | 2020-01-22 | 2020-04-24 | 无锡十顶电子科技有限公司 | 一种低电压时增强驱动能力的蜂鸣器驱动电路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2012155195A (ja) | ブザー駆動回路 | |

| KR960014972A (ko) | 기록 드라이버 회로 | |

| JP2008079276A (ja) | 電圧レベル変換回路及びそれを備えるディスプレイ装置 | |

| JP5348115B2 (ja) | 負荷駆動装置 | |

| JP2009230842A (ja) | サンプルホールド回路 | |

| JP2004032619A (ja) | 演算増幅回路 | |

| JPH0644705B2 (ja) | 半導体回路 | |

| JP6500511B2 (ja) | スイッチング素子のドライブ回路 | |

| JP6600207B2 (ja) | 基準電流源回路 | |

| JP2011155497A (ja) | レベルシフト回路 | |

| JP5014910B2 (ja) | 出力回路 | |

| JP3087237B2 (ja) | レベル変換回路 | |

| JP2002043915A (ja) | ドライバ回路 | |

| JP2783797B2 (ja) | 差動出力コンパレータ | |

| JP2006229501A (ja) | 振幅設定回路 | |

| JP4768653B2 (ja) | 演算増幅器 | |

| JP2026018110A (ja) | 音声出力装置 | |

| JP3097593B2 (ja) | 半導体装置 | |

| JP4784210B2 (ja) | 電流スイッチ | |

| JPS63128814A (ja) | レベル変換回路 | |

| JP4990750B2 (ja) | モジュール回路 | |

| JPS6011608Y2 (ja) | ソレノイド駆動回路 | |

| JP5350882B2 (ja) | 容量増倍回路 | |

| JP4465419B2 (ja) | 極性反転回路 | |

| JP2009296414A (ja) | エミッタ結合形無安定マルチバイブレータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20120926 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20120927 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20121005 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140421 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140507 |

|

| A762 | Written abandonment of application |

Free format text: JAPANESE INTERMEDIATE CODE: A762 Effective date: 20140611 |