JP2011508458A - 選択的に製造されたカーボンナノチューブ可逆抵抗切替素子を使用するメモリセルおよびそれを形成する方法 - Google Patents

選択的に製造されたカーボンナノチューブ可逆抵抗切替素子を使用するメモリセルおよびそれを形成する方法 Download PDFInfo

- Publication number

- JP2011508458A JP2011508458A JP2010540945A JP2010540945A JP2011508458A JP 2011508458 A JP2011508458 A JP 2011508458A JP 2010540945 A JP2010540945 A JP 2010540945A JP 2010540945 A JP2010540945 A JP 2010540945A JP 2011508458 A JP2011508458 A JP 2011508458A

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- cnt

- manufacturing

- layer

- switching element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000002041 carbon nanotube Substances 0.000 title claims abstract description 291

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 title claims abstract description 264

- 229910021393 carbon nanotube Inorganic materials 0.000 title claims abstract description 261

- 230000015654 memory Effects 0.000 title claims abstract description 244

- 238000000034 method Methods 0.000 title claims abstract description 105

- 230000002441 reversible effect Effects 0.000 title claims abstract description 94

- 239000000463 material Substances 0.000 claims abstract description 178

- 238000004519 manufacturing process Methods 0.000 claims abstract description 81

- 239000000758 substrate Substances 0.000 claims abstract description 37

- 238000000151 deposition Methods 0.000 claims abstract description 25

- 238000010899 nucleation Methods 0.000 claims description 96

- 239000004020 conductor Substances 0.000 claims description 94

- 229910052751 metal Inorganic materials 0.000 claims description 75

- 239000002184 metal Substances 0.000 claims description 75

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 51

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 48

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 claims description 44

- 239000003054 catalyst Substances 0.000 claims description 27

- 239000010941 cobalt Substances 0.000 claims description 26

- 229910017052 cobalt Inorganic materials 0.000 claims description 26

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 26

- 229910052759 nickel Inorganic materials 0.000 claims description 24

- 229910021332 silicide Inorganic materials 0.000 claims description 23

- 229910052742 iron Inorganic materials 0.000 claims description 22

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 22

- 238000005530 etching Methods 0.000 claims description 21

- 239000004065 semiconductor Substances 0.000 claims description 21

- 238000005229 chemical vapour deposition Methods 0.000 claims description 17

- 239000010409 thin film Substances 0.000 claims description 16

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 14

- 229920005591 polysilicon Polymers 0.000 claims description 14

- 238000000059 patterning Methods 0.000 claims description 12

- SCCCLDWUZODEKG-UHFFFAOYSA-N germanide Chemical compound [GeH3-] SCCCLDWUZODEKG-UHFFFAOYSA-N 0.000 claims description 7

- 229910044991 metal oxide Inorganic materials 0.000 claims description 5

- 150000004706 metal oxides Chemical class 0.000 claims description 5

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 claims description 5

- 238000007788 roughening Methods 0.000 claims description 5

- 230000007547 defect Effects 0.000 claims description 4

- 230000005669 field effect Effects 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 276

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 47

- 229910052710 silicon Inorganic materials 0.000 description 47

- 239000010703 silicon Substances 0.000 description 47

- 230000004888 barrier function Effects 0.000 description 46

- 230000015572 biosynthetic process Effects 0.000 description 35

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 29

- 239000003989 dielectric material Substances 0.000 description 22

- 229910052721 tungsten Inorganic materials 0.000 description 20

- 239000010937 tungsten Substances 0.000 description 20

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 16

- 239000012790 adhesive layer Substances 0.000 description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 230000008569 process Effects 0.000 description 12

- -1 tungsten nitride Chemical class 0.000 description 11

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 10

- 238000000137 annealing Methods 0.000 description 9

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 8

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 8

- 229910052786 argon Inorganic materials 0.000 description 8

- 230000008021 deposition Effects 0.000 description 8

- 150000004767 nitrides Chemical class 0.000 description 8

- ORQBXQOJMQIAOY-UHFFFAOYSA-N nobelium Chemical compound [No] ORQBXQOJMQIAOY-UHFFFAOYSA-N 0.000 description 8

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- 238000005498 polishing Methods 0.000 description 7

- 239000010936 titanium Substances 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 6

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 6

- 230000012010 growth Effects 0.000 description 6

- 235000012239 silicon dioxide Nutrition 0.000 description 6

- 239000000377 silicon dioxide Substances 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 229910052799 carbon Inorganic materials 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 150000002739 metals Chemical class 0.000 description 4

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 230000003746 surface roughness Effects 0.000 description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- HMDDXIMCDZRSNE-UHFFFAOYSA-N [C].[Si] Chemical compound [C].[Si] HMDDXIMCDZRSNE-UHFFFAOYSA-N 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 239000007943 implant Substances 0.000 description 3

- 230000005012 migration Effects 0.000 description 3

- 238000013508 migration Methods 0.000 description 3

- 239000002071 nanotube Substances 0.000 description 3

- 238000003786 synthesis reaction Methods 0.000 description 3

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 2

- 239000005977 Ethylene Substances 0.000 description 2

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 2

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 230000003698 anagen phase Effects 0.000 description 2

- 239000011231 conductive filler Substances 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 238000010891 electric arc Methods 0.000 description 2

- 238000007772 electroless plating Methods 0.000 description 2

- 238000009713 electroplating Methods 0.000 description 2

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- KTWOOEGAPBSYNW-UHFFFAOYSA-N ferrocene Chemical compound [Fe+2].C=1C=C[CH-]C=1.C=1C=C[CH-]C=1 KTWOOEGAPBSYNW-UHFFFAOYSA-N 0.000 description 2

- 229930195733 hydrocarbon Natural products 0.000 description 2

- 150000002430 hydrocarbons Chemical class 0.000 description 2

- 238000011065 in-situ storage Methods 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 239000008096 xylene Substances 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 238000004026 adhesive bonding Methods 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000012018 catalyst precursor Substances 0.000 description 1

- 150000001793 charged compounds Chemical class 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 238000001802 infusion Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 238000012876 topography Methods 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/02—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using elements whose operation depends upon chemical change

- G11C13/025—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using elements whose operation depends upon chemical change using fullerenes, e.g. C60, or nanotubes, e.g. carbon or silicon nanotubes

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0004—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising amorphous/crystalline phase transition cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/101—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including resistors or capacitors only

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/20—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

- H10B63/84—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays arranged in a direction perpendicular to the substrate, e.g. 3D cell arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/021—Formation of switching materials, e.g. deposition of layers

- H10N70/023—Formation of switching materials, e.g. deposition of layers by chemical vapor deposition, e.g. MOCVD, ALD

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/884—Switching materials based on at least one element of group IIIA, IVA or VA, e.g. elemental or compound semiconductors

- H10N70/8845—Carbon or carbides

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/30—Resistive cell, memory material aspects

- G11C2213/35—Material including carbon, e.g. graphite, grapheme

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/79—Array wherein the access device being a transistor

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Theoretical Computer Science (AREA)

- Mathematical Physics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Memories (AREA)

- Carbon And Carbon Compounds (AREA)

Abstract

Description

本願は、2007年12月31日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY FABRICATED CARBON NANO-TUBE REVERSIBLE RESISTANCE-SWITCHING ELEMENT FORMED OVER A BOTTOM CONDUCTOR AND METHODS OF FORMING THE SAME 」という米国特許出願第11/968,156号(代理人整理番号:MD−351)(特許文献2)、および2007年12月31日に出願された「MEMORY CELL WITH PLANARIZED CARBON NANOTUBE LAYER AND METHODS OF FORMING THE SAME 」という米国特許出願第11/968,159号(代理人整理番号:MD−368)(特許文献3)に関連し、その全体があらゆる目的のために本願明細書において参照により援用されている。

しかし、再書込み可能な抵抗率切替材料から記憶装置を製造することは技術的にやりがいがあり、抵抗率切替材料を使用する記憶装置を形成する改良された方法が望ましい。

図1は、本発明に従って提供される代表的なメモリセル100の略図である。メモリセル100は、ステアリング素子104に結合された可逆抵抗切替素子102を含む。

可逆抵抗切替素子102は、2つ以上の状態の間で可逆的に切り替わり得る抵抗率を有する可逆抵抗率切替材料(単独には示されていない)を含む。例えば、素子102の可逆抵抗率切替材料は、製造時には初期低抵抗率状態にあり得る。第1の電圧および/または電流が加えられると、材料は高抵抗率状態に切り替わることができる。第2の電圧および/または電流を加えることにより、可逆抵抗率切替材料を低抵抗率状態に戻すことができる。あるいは、可逆抵抗切替素子102は、製造時には初期高抵抗状態にあることができ、それは、適切な1つまたは複数の電圧および/または1つまたは複数の電流が加えられると、低抵抗状態に可逆的に切り替わることができる。メモリセルにおいて使用されるとき、1つの抵抗状態はバイナリ「0」を表すことができ、他の1つの抵抗状態はバイナリ「1」を表すことができるけれども、2つより多いデータ/抵抗状態が使用され得る。多数の可逆抵抗率切替材料と、可逆抵抗切替素子を使用するメモリセルの操作とが、例えば、前に援用されている特許文献4に記載されている。

メモリセル100、可逆抵抗切替素子102およびステアリング素子104の代表的な実施形態が、以下で図2A〜5を参照して記載される。

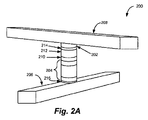

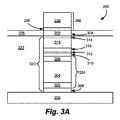

図2Aは、本発明に従って提供されるメモリセル200の第1の実施形態の略透視図である。図2Aを参照すると、メモリセル200は、第1の導体206と第2の導体208との間でダイオード204と直列に結合された可逆抵抗切替素子202を含む。ある実施形態では、可逆抵抗切替素子202とダイオード204との間に障壁層210、伝導層212および/またはCNTシーディング層214が形成され得る。例えば、障壁層210は窒化チタン、窒化タンタル、窒化タングステンなどを含むことができ、伝導層212はタングステンまたは他の適切な金属層を含むことができる。

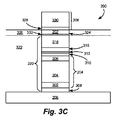

ダイオード204は、ダイオードのp領域より上にn領域があって上を向いているかあるいはダイオードのn領域より上にp領域があって下を向いている垂直多結晶pnまたはpinダイオードなどの任意の適切なダイオードを含むことができる。ダイオード204の代表的な実施形態は、以下で図3A〜Cを参照して記載される。

前述したように、ダイオード204は垂直のpnダイオードあるいはpinダイオードであってよく、それは上または下を向くことができる。隣り合うメモリレベル同士が導体を共有する図2Dの実施形態では、隣り合うメモリレベル同士は、好ましくは、例えば第1のメモリレベルでは下向きpinダイオード、隣接する第2のメモリレベルでは上向きpinダイオード(あるいはその逆)など、反対方向を向くダイオードを有する。

他の1つの代表的な実施形態では、CNTは、約20分間にわたる、約5.5Torrの圧力の約20%C2 H4 および80%アルゴン中での約650℃の温度でのCVDによってニッケル触媒層上に形成され得る。他の温度、ガス、比、圧力および/または成長時間が使用され得る。

さらに他の1つの実施形態では、CNTは、約8〜30分間にわたる、約100〜200ワットのRF電力を用いる、約80%のアルゴン、水素および/またはアンモニアで希釈された約20%のメタン、エチレン、アセチレンまたは他の炭化水素中での約600〜900℃の温度でのプラズマエンハンストCVDを用いてニッケル、コバルト、鉄などの金属触媒層上に形成され得る。他の温度、ガス、比、電力および/または成長時間が使用され得る。

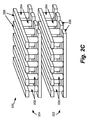

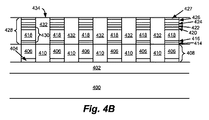

図4A〜Dは、本発明に従う第1のメモリレベルの製造中の基板400の一部分の横断面図を示す。以下に説明するように、第1のメモリレベルは、基板より上にカーボンナノチューブ(CNT)材料を選択的に製造することによって形成された可逆抵抗切替素子を各々含む複数のメモリセルを含む。(図2C〜2Dを参照して前に説明したように、)第1のメモリレベルより上に付加的なメモリレベルが製造され得る。

絶縁層402が基板400より上に形成される。ある実施形態では、絶縁層402は、二酸化ケイ素、窒化ケイ素、オキシ窒化ケイ素の層あるいは他の任意の適切な絶縁層であり得る。

伝導層426の形成後、伝導層426の上にCNTシーディング層427が形成される。ある実施形態では、CNTシーディング層427は、約1,000〜約5,000オングストロームの窒化チタンまたは窒化タンタルであり得るけれども、他の厚さが使用され得る。

他の1つの代表的な実施形態では、CNTは、約20分間にわたる、約5.5Torrの圧力の約20%C2 H4 および80%アルゴン中での約650℃の温度でのCVDによってニッケル触媒層上に形成され得る。他の温度、ガス、比、圧力および/または成長時間が使用され得る。

さらに他の1つの実施形態では、CNTは、約8〜30分間にわたる、約100〜200ワットのRF電力を用いる、約80%のアルゴン、水素および/またはアンモニアで希釈された約20%のメタン、エチレン、アセチレンまたは他の炭化水素中での約600〜900℃の温度でのプラズマエンハンストCVDを用いてニッケル、コバルト、鉄などの金属触媒層上に形成され得る。他の温度、ガス、比、電力および/または成長時間が使用され得る。

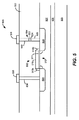

図5は、本発明に従って提供される代表的なメモリセル500の横断面図である。メモリセル500は、基板505より上に形成された可逆抵抗切替素子504に結合された薄膜金属酸化物半導体電界効果トランジスタ(MOSFET)502などの薄膜トランジスタ(TFT)を含む。例えば、MOSFET502は、任意の適切な基板上に形成されたnチャネルまたはpチャネルの薄膜MOSFETであり得る。図に示されている実施形態では、二酸化ケイ素、窒化ケイ素、酸窒化物などの絶縁領域506が基板505より上に形成され、堆積させられたシリコン、ゲルマニウム、シリコン−ゲルマニウムなどの堆積させられた半導体領域507が絶縁領域506より上に形成される。薄膜MOSFET502は、堆積させられた半導体領域507の中に形成され、絶縁領域506によって基板505から絶縁される。

従って、本発明は、その代表的な実施形態に関して開示されたけれども、他の実施形態が、添付の特許請求の範囲により定義される発明の精神および範囲の中にあるかもしれないということを理解するべきである。

Claims (92)

- メモリセルを製造する方法であって、

基板より上にステアリング素子を製造するステップと、

前記基板より上にカーボンナノチューブ(CNT)材料を選択的に製造することによって前記ステアリング素子に結合された可逆抵抗切替素子を製造するステップと、

を含む方法。 - 請求項1記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

CNTシーディング層を製造するステップと、

前記CNTシーディング層をパターニングしエッチングするステップと、

前記CNTシーディング層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項2記載の方法において、

前記CNTシーディング層を製造するステップは、

窒化チタンを堆積させるステップと、

前記堆積させられた窒化チタンの表面を粗くするステップと、

を含む方法。 - 請求項3記載の方法において、

前記粗くされた窒化チタン表面上に金属層を選択的に堆積させるステップをさらに含む方法。 - 請求項4記載の方法において、

前記金属層は、ニッケル、コバルトまたは鉄を含む方法。 - 請求項2記載の方法において、

前記CNTシーディング層を製造するステップは、

第1の導体より上に窒化チタンを堆積させるステップと、

前記窒化チタン上に金属触媒層を選択的に堆積させるステップと、

を含む方法。 - 請求項6記載の方法において、

前記金属層は、ニッケル、コバルトまたは鉄を含む方法。 - 請求項2記載の方法において、

前記CNTシーディング層をパターニングしエッチングするステップは、前記ステアリング素子をパターニングしエッチングするステップを含む方法。 - 請求項2記載の方法において、

前記CNTシーディング層上にCNT材料を選択的に製造するステップは、化学蒸着(CVD)またはプラズマエンハンストCVDを用いてCNT材料を前記CNTシーディング層上に堆積させるステップを含む方法。 - 請求項2記載の方法において、

前記CNT材料の切替特性を調整するために前記CNT材料に欠陥を生じさせるステップをさらに含む方法。 - 請求項1記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

金属層を選択的に堆積させるステップと、

前記堆積させられた金属層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項11記載の方法において、

前記金属層は、ニッケル、コバルトまたは鉄を含む方法。 - 請求項1記載の方法において、

前記可逆抵抗切替素子は、前記ステアリング素子より上に製造される方法。 - 請求項1記載の方法において、

前記ステアリング素子を製造するステップは、pnダイオードまたはpinダイオードを製造するステップを含む方法。 - 請求項14記載の方法において、

前記ステアリング素子を製造するステップは、多結晶ダイオードを製造するステップを含む方法。 - 請求項15記載の方法において、

前記ステアリング素子を製造するステップは、垂直多結晶ダイオードを製造するステップを含む方法。 - 請求項16記載の方法において、

前記ステアリング素子を製造するステップは、低抵抗率状態にある多結晶材料を有する垂直多結晶ダイオードを製造するステップを含む方法。 - 請求項1記載の方法において、

前記ステアリング素子を製造するステップは、薄膜トランジスタを製造するステップを含む方法。 - 請求項18記載の方法において、

前記ステアリング素子を製造するステップは、薄膜金属酸化物半導体電界効果トランジスタ(MOSFET)を製造するステップを含む方法。 - 請求項1記載の方法を用いて形成されたメモリセル。

- 請求項16記載の方法を用いて形成されたメモリセル。

- メモリセルを製造する方法であって、

基板より上に第1の導体を製造するステップと、

前記第1の導体より上にカーボンナノチューブ(CNT)材料を選択的に製造することによって前記第1の導体より上に可逆抵抗切替素子を製造するステップと、

前記第1の導体より上にダイオードを製造するステップと、

前記ダイオードおよび前記可逆抵抗切替素子より上に第2の導体を製造するステップと、

を含む方法。 - 請求項22記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

CNTシーディング層を製造するステップと、

前記CNTシーディング層をパターニングしエッチングするステップと、

前記CNTシーディング層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項23記載の方法において、

前記CNTシーディング層を製造するステップは、

窒化チタンを堆積させるステップと、

前記堆積させられた窒化チタンの表面を粗くするステップと、

を含む方法。 - 請求項24記載の方法において、

前記粗くされた窒化チタン表面上に金属層を選択的に堆積させるステップをさらに含む方法。 - 請求項23記載の方法において、

前記CNTシーディング層をパターニングしエッチングするステップは、前記ダイオードをパターニングしエッチングするステップを含む方法。 - 請求項22記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

金属層を選択的に堆積させるステップと、

前記堆積させられた金属層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項22記載の方法において、

前記可逆抵抗切替素子は、前記ステアリング素子より上に製造される方法。 - 請求項22記載の方法において、

前記ダイオードを製造するステップは、垂直多結晶ダイオードを製造するステップを含む方法。 - 請求項29記載の方法において、

前記垂直多結晶ダイオードの多結晶材料と接触するシリサイド、シリサイド−ゲルマニドまたはゲルマニドの領域を前記多結晶材料が低抵抗率状態にあるように製造するステップをさらに含む方法。 - 請求項22記載の方法を用いて形成されたメモリセル。

- 請求項30の方法を用いて形成されたメモリセル。

- メモリセルを製造する方法であって、

基板より上に第1の導体を製造するステップと、

前記第1の導体より上に垂直多結晶ダイオードを製造するステップと、

前記垂直多結晶ダイオードより上にカーボンナノチューブ(CNT)材料を選択的に製造することによって前記垂直多結晶ダイオードより上に可逆抵抗切替素子を製造するステップと、

前記可逆抵抗切替素子より上に第2の導体を製造するステップと、

を含む方法。 - 請求項33記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

CNTシーディング層を製造するステップと、

前記CNTシーディング層をパターニングしエッチングするステップと、

前記CNTシーディング層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項34記載の方法において、

前記CNTシーディング層を製造するステップは、

窒化チタンを堆積させるステップと、

前記堆積させられた窒化チタンの表面を粗くするステップと、

を含む方法。 - 請求項35記載の方法において、

前記粗くされた窒化チタン表面上に金属層を選択的に堆積させるステップをさらに含む方法。 - 請求項34記載の方法において、

前記CNTシーディング層をパターニングしエッチングするステップは、前記ダイオードをパターニングしエッチングするステップを含む方法。 - 請求項33記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

金属層を選択的に堆積させるステップと、

前記堆積させられた金属層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項33記載の方法において、

前記垂直多結晶ダイオードの多結晶材料と接触するシリサイド、シリサイド−ゲルマニドまたはゲルマニドの領域を前記多結晶材料が低抵抗率状態にあるように製造するステップをさらに含む方法。 - 請求項33記載の方法を用いて形成されたメモリセル。

- メモリセルを製造する方法であって、

ソース領域およびドレイン領域を有する薄膜トランジスタを製造するステップと、

前記トランジスタの前記ソース領域または前記ドレイン領域に結合された第1の導体を製造するステップと、

前記第1の導体より上にカーボンナノチューブ(CNT)材料を選択的に製造することによって前記第1の導体に結合された可逆抵抗切替素子を製造するステップと、

前記可逆抵抗切替素子より上に第2の導体を製造するステップと、

を含む方法。 - 請求項41記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

CNTシーディング層を製造するステップと、

前記CNTシーディング層をパターニングしエッチングするステップと、

前記CNTシーディング層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項42記載の方法において、

前記CNTシーディング層を製造するステップは、

窒化チタンを堆積させるステップと、

前記堆積させられた窒化チタンの表面を粗くするステップと、

を含む方法。 - 請求項41記載の方法において、

前記可逆抵抗切替素子を製造するステップは、

金属層を選択的に堆積させるステップと、

前記堆積させられた金属層上にCNT材料を選択的に製造するステップと、

を含む方法。 - 請求項41記載の方法を用いて形成されたメモリセル。

- 請求項1記載の方法において、

前記CNT材料を選択的に製造するステップは、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを有するCNT材料を製造するステップを含む方法。 - 請求項22記載の方法において、

前記CNT材料を選択的に製造するステップは、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを有するCNT材料を製造するステップを含む方法。 - 請求項33記載の方法において、

前記CNT材料を選択的に製造するステップは、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを有するCNT材料を製造するステップを含む方法。 - メモリセルであって、

ステアリング素子と、

前記ステアリング素子に結合され、選択的に製造されたカーボンナノチューブ(CNT)材料を含む可逆抵抗切替素子と、

を備えるメモリセル。 - 請求項49記載のメモリセルにおいて、

前記ステアリング素子は、pnダイオードまたはpinダイオードを含むメモリセル。 - 請求項50記載のメモリセルにおいて、

前記ダイオードは、垂直多結晶ダイオードを含むメモリセル。 - 請求項51記載のメモリセルにおいて、

前記垂直多結晶ダイオードは、低抵抗率状態にある多結晶材料を含むメモリセル。 - 請求項49記載のメモリセルにおいて、

前記ステアリング素子は、薄膜トランジスタを含むメモリセル。 - 請求項53記載のメモリセルにおいて、

前記薄膜トランジスタは、金属酸化物半導体電界効果トランジスタ(MOSFET)を含むメモリセル。 - 請求項49記載のメモリセルにおいて、

前記CNT材料がその上に選択的に製造されるパターニングされエッチングされたCNTシーディング層をさらに含むメモリセル。 - 請求項55記載のメモリセルにおいて、

前記CNTシーディング層は、伝導層を含むメモリセル。 - 請求項56記載のメモリセルにおいて、

前記伝導層は、窒化チタンを含むメモリセル。 - 請求項57記載のメモリセルにおいて、

前記窒化チタンは、粗面化されるメモリセル。 - 請求項56記載のメモリセルにおいて、

前記伝導層は、ニッケル、コバルトまたは鉄を含むメモリセル。 - 請求項55記載のメモリセルにおいて、

前記CNTシーディング層は、前記ステアリング素子と共にパターニングされエッチングされるメモリセル。 - 請求項55記載のメモリセルにおいて、

前記CNT材料は、前記CNT材料の切替特性を調整する欠陥を含むメモリセル。 - メモリセルであって、

第1の導体と、

前記第1の導体より上に形成された第2の導体と、

前記第1の導体および前記第2の導体の間に形成されたダイオードと、

前記第1の導体および前記第2の導体の間に選択的に製造されたカーボンナノチューブ(CNT)材料を含む可逆抵抗切替素子と、

を備えるメモリセル。 - 請求項62記載のメモリセルにおいて、

前記ダイオードは、垂直多結晶ダイオードを含むメモリセル。 - 請求項63記載のメモリセルにおいて、

前記可逆抵抗切替素子は、前記垂直多結晶ダイオードより上にあるメモリセル。 - 請求項63記載のメモリセルにおいて、

前記多結晶材料が低抵抗率状態にあるように前記垂直多結晶ダイオードの多結晶材料と接触するシリサイド、シリサイド−ゲルマニドまたはゲルマニドの領域をさらに備えるメモリセル。 - 請求項62記載のメモリセルにおいて、

前記CNT材料がその上に選択的に製造されるパターニングされエッチングされたCNTシーディング層をさらに含むメモリセル。 - 請求項66記載のメモリセルにおいて、

前記CNTシーディング層は、伝導層を含むメモリセル。 - 請求項67記載のメモリセルにおいて、

前記伝導層は、窒化チタンを含むメモリセル。 - 請求項68記載のメモリセルにおいて、

前記窒化チタンは、粗面化されるメモリセル。 - 請求項67記載のメモリセルにおいて、

前記伝導層は、ニッケル、コバルトまたは鉄を含むメモリセル。 - メモリセルであって、

ソース領域およびドレイン領域を有する薄膜トランジスタと、

前記ソース領域または前記ドレイン領域に結合された第1の導体と、

前記第1の導体より上に選択的に製造されたカーボンナノチューブ(CNT)材料を含む可逆抵抗切替素子と、

前記可逆抵抗切替素子より上に形成された第2の導体と、

を備えるメモリセル。 - 請求項71記載のメモリセルにおいて、

前記薄膜トランジスタは、nチャネルまたはpチャネルの金属酸化物半導体電界効果トランジスタを含むメモリセル。 - 請求項71記載のメモリセルにおいて、

前記CNT材料がその上に選択的に製造されるパターニングされエッチングされたCNTシーディング層をさらに含むメモリセル。 - 請求項71記載のメモリセルにおいて、

前記CNTシーディング層は、伝導層を含むメモリセル。 - 請求項74記載のメモリセルにおいて、

前記伝導層は、窒化チタンを含むメモリセル。 - 請求項75記載のメモリセルにおいて、

前記窒化チタンは、粗面化されるメモリセル。 - 複数の不揮発性メモリセルであって、

第1の方向に延びる第1の複数の実質的に平行で実質的に共面の導体と、

複数のダイオードと、

複数の可逆抵抗切替素子と、

前記第1の方向とは異なる第2の方向に延びる第2の複数の実質的に平行で実質的に共面の導体と、を備え、

各メモリセルにおいて、前記ダイオードのうちの1つと前記可逆抵抗切替素子のうちの1つとは直列に配列され、前記第1の導体のうちの1つと前記第2の導体のうちの1つとの間に配置され、

各可逆抵抗切替素子は、選択的に製造されたカーボンナノチューブ(CNT)材料を含む複数の不揮発性メモリセル。 - 請求項77記載の複数の不揮発性メモリセルにおいて、

各ダイオードは、垂直多結晶ダイオードである複数の不揮発性メモリセル。 - 請求項78記載の複数の不揮発性メモリセルにおいて、

前記多結晶材料が低抵抗率状態にあるように各垂直多結晶ダイオードの多結晶材料と接触するシリサイド、シリサイド−ゲルマニドまたはゲルマニドの領域をさらに備える複数の不揮発性メモリセル。 - 請求項77記載の複数の不揮発性メモリセルにおいて、

各可逆抵抗切替素子は、前記可逆抵抗切替素子の前記CNT材料がその上に選択的に製造されるパターニングされエッチングされたCNTシーディング層を含む複数の不揮発性メモリセル。 - 請求項80記載の複数の不揮発性メモリセルにおいて、

各可逆抵抗切替素子の前記CNTシーディング層は、伝導層を含む複数の不揮発性メモリセル。 - 請求項81記載の複数の不揮発性メモリセルにおいて、

各可逆抵抗切替素子の前記伝導層は、窒化チタンを含む複数の不揮発性メモリセル。 - 請求項82の複数の不揮発性メモリセルにおいて、

各可逆抵抗切替素子の前記窒化チタンは、粗面化される複数の不揮発性メモリセル。 - モノリシックな3次元メモリアレイであって、

基板より上に形成された第1のメモリレベルであって、

複数のメモリセルであって、前記第1のメモリレベルの各メモリセルは、

ステアリング素子と、

前記ステアリング素子に結合され、選択的に製造されたカーボンナノチューブ(CNT)材料を含む可逆抵抗切替素子と、を含む複数のメモリセルを備えるようにした第1のメモリレベルと、

前記第1のメモリレベルより上にモノリシック的に形成された少なくとも第2のメモリレベルと、

を備えるモノリシックな3次元メモリアレイ。 - 請求項84記載のモノリシックな3次元メモリアレイにおいて、

各ステアリング素子は、垂直多結晶ダイオードを含むモノリシックな3次元メモリアレイ。 - 請求項85記載のモノリシックな3次元メモリアレイにおいて、

各垂直多結晶ダイオードは、垂直ポリシリコンダイオードを含むモノリシックな3次元メモリアレイ。 - 請求項84記載のモノリシックな3次元メモリアレイにおいて、

各可逆抵抗切替素子は、前記可逆抵抗切替素子の前記CNT材料がその上に選択的に製造されるパターニングされエッチングされたCNTシーディング層を含むモノリシックな3次元メモリアレイ。 - 請求項49記載のメモリセルにおいて、

前記CNT材料は、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを含むメモリセル。 - 請求項62記載のメモリセルにおいて、

前記CNT材料は、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを含むメモリセル。 - 請求項71記載のメモリセルにおいて、

前記CNT材料は、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを含むメモリセル。 - 請求項77記載の複数の不揮発性メモリセルにおいて、

各可逆抵抗切替素子の前記CNT材料は、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを含む複数の不揮発性メモリ。 - 請求項84記載のモノリシックな3次元メモリアレイにおいて、

各可逆抵抗切替素子の前記CNT材料は、前記CNT材料における横方向伝導を減少させるように実質的に垂直に整列させられたCNTを含むモノリシックな3次元メモリアレイ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/968,154 US8236623B2 (en) | 2007-12-31 | 2007-12-31 | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element and methods of forming the same |

| PCT/US2008/088584 WO2009088888A2 (en) | 2007-12-31 | 2008-12-30 | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element and methods of forming the same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011508458A true JP2011508458A (ja) | 2011-03-10 |

| JP2011508458A5 JP2011508458A5 (ja) | 2011-12-15 |

Family

ID=40798167

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010540945A Pending JP2011508458A (ja) | 2007-12-31 | 2008-12-30 | 選択的に製造されたカーボンナノチューブ可逆抵抗切替素子を使用するメモリセルおよびそれを形成する方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8236623B2 (ja) |

| EP (1) | EP2227824B1 (ja) |

| JP (1) | JP2011508458A (ja) |

| KR (1) | KR101494746B1 (ja) |

| CN (1) | CN101919047B (ja) |

| TW (1) | TW200943489A (ja) |

| WO (1) | WO2009088888A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9048176B2 (en) | 2011-09-08 | 2015-06-02 | Kabushiki Kaisha Toshiba | Nonvolatile storage device |

Families Citing this family (70)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9287356B2 (en) * | 2005-05-09 | 2016-03-15 | Nantero Inc. | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same |

| US8000127B2 (en) * | 2009-08-12 | 2011-08-16 | Nantero, Inc. | Method for resetting a resistive change memory element |

| US9390790B2 (en) | 2005-04-05 | 2016-07-12 | Nantero Inc. | Carbon based nonvolatile cross point memory incorporating carbon based diode select devices and MOSFET select devices for memory and logic applications |

| US8217490B2 (en) * | 2005-05-09 | 2012-07-10 | Nantero Inc. | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same |

| US7835170B2 (en) * | 2005-05-09 | 2010-11-16 | Nantero, Inc. | Memory elements and cross point switches and arrays of same using nonvolatile nanotube blocks |

| US7479654B2 (en) | 2005-05-09 | 2009-01-20 | Nantero, Inc. | Memory arrays using nanotube articles with reprogrammable resistance |

| US8183665B2 (en) * | 2005-11-15 | 2012-05-22 | Nantero Inc. | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same |

| US8513768B2 (en) * | 2005-05-09 | 2013-08-20 | Nantero Inc. | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same |

| US9911743B2 (en) * | 2005-05-09 | 2018-03-06 | Nantero, Inc. | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same |

| US7781862B2 (en) * | 2005-05-09 | 2010-08-24 | Nantero, Inc. | Two-terminal nanotube devices and systems and methods of making same |

| US7575693B2 (en) | 2005-05-23 | 2009-08-18 | Nantero, Inc. | Method of aligning nanotubes and wires with an etched feature |

| US8878235B2 (en) * | 2007-12-31 | 2014-11-04 | Sandisk 3D Llc | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element and methods of forming the same |

| US20090166610A1 (en) * | 2007-12-31 | 2009-07-02 | April Schricker | Memory cell with planarized carbon nanotube layer and methods of forming the same |

| US8558220B2 (en) * | 2007-12-31 | 2013-10-15 | Sandisk 3D Llc | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element formed over a bottom conductor and methods of forming the same |

| US8110476B2 (en) | 2008-04-11 | 2012-02-07 | Sandisk 3D Llc | Memory cell that includes a carbon-based memory element and methods of forming the same |

| US8304284B2 (en) * | 2008-04-11 | 2012-11-06 | Sandisk 3D Llc | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element, and methods of forming the same |

| EP2263252B1 (en) * | 2008-04-11 | 2013-10-09 | SanDisk 3D LLC | Methods for etching carbon nano-tube films for use in non-volatile memories |

| CN102027610B (zh) * | 2008-04-11 | 2012-12-05 | 桑迪士克3D有限责任公司 | 包括碳纳米管可逆电阻切换元件的存储器单元及其形成方法 |

| WO2009126846A1 (en) * | 2008-04-11 | 2009-10-15 | Sandisk 3D, Llc | Damascene integration methods for graphitic films in three-dimensional memories and memories formed therefrom |

| US8530318B2 (en) * | 2008-04-11 | 2013-09-10 | Sandisk 3D Llc | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element formed over a bottom conductor and methods of forming the same |

| US8133793B2 (en) | 2008-05-16 | 2012-03-13 | Sandisk 3D Llc | Carbon nano-film reversible resistance-switchable elements and methods of forming the same |

| US8569730B2 (en) * | 2008-07-08 | 2013-10-29 | Sandisk 3D Llc | Carbon-based interface layer for a memory device and methods of forming the same |

| US8309407B2 (en) * | 2008-07-15 | 2012-11-13 | Sandisk 3D Llc | Electronic devices including carbon-based films having sidewall liners, and methods of forming such devices |

| WO2010009364A1 (en) * | 2008-07-18 | 2010-01-21 | Sandisk 3D, Llc | Carbon-based resistivity-switching materials and methods of forming the same |

| US20100032639A1 (en) * | 2008-08-07 | 2010-02-11 | Sandisk 3D Llc | Memory cell that includes a carbon-based memory element and methods of forming the same |

| US9263126B1 (en) | 2010-09-01 | 2016-02-16 | Nantero Inc. | Method for dynamically accessing and programming resistive change element arrays |

| US8319205B2 (en) * | 2008-08-14 | 2012-11-27 | Nantero Inc. | Nonvolatile nanotube programmable logic devices and a nonvolatile nanotube field programmable gate array using same |

| US8431417B2 (en) * | 2008-08-19 | 2013-04-30 | Sandisk 3D Llc | Methods for increasing carbon nano-tube (CNT) yield in memory devices |

| WO2010048408A2 (en) | 2008-10-23 | 2010-04-29 | Sandisk 3D, Llc | Carbon-based memory elements exhibiting reduced delamination and methods of forming the same |

| US8835892B2 (en) * | 2008-10-30 | 2014-09-16 | Sandisk 3D Llc | Electronic devices including carbon nano-tube films having boron nitride-based liners, and methods of forming the same |

| US20100108976A1 (en) * | 2008-10-30 | 2010-05-06 | Sandisk 3D Llc | Electronic devices including carbon-based films, and methods of forming such devices |

| US8421050B2 (en) * | 2008-10-30 | 2013-04-16 | Sandisk 3D Llc | Electronic devices including carbon nano-tube films having carbon-based liners, and methods of forming the same |

| US7915637B2 (en) * | 2008-11-19 | 2011-03-29 | Nantero, Inc. | Switching materials comprising mixed nanoscopic particles and carbon nanotubes and method of making and using the same |

| JP2010157569A (ja) * | 2008-12-26 | 2010-07-15 | Funai Electric Advanced Applied Technology Research Institute Inc | メモリセルアレイ |

| WO2010078467A1 (en) * | 2008-12-31 | 2010-07-08 | Sandisk 3D, Llc | Modulation of resistivity in carbon-based read-writeable materials |

| US8183121B2 (en) * | 2009-03-31 | 2012-05-22 | Sandisk 3D Llc | Carbon-based films, and methods of forming the same, having dielectric filler material and exhibiting reduced thermal resistance |

| US8509124B2 (en) * | 2009-04-03 | 2013-08-13 | Lg Electronics Inc. | Method for transceiving a signal in wireless communication system |

| US8551855B2 (en) * | 2009-10-23 | 2013-10-08 | Sandisk 3D Llc | Memory cell that includes a carbon-based reversible resistance switching element compatible with a steering element, and methods of forming the same |

| US8481396B2 (en) * | 2009-10-23 | 2013-07-09 | Sandisk 3D Llc | Memory cell that includes a carbon-based reversible resistance switching element compatible with a steering element, and methods of forming the same |

| US8551850B2 (en) * | 2009-12-07 | 2013-10-08 | Sandisk 3D Llc | Methods of forming a reversible resistance-switching metal-insulator-metal structure |

| US8222704B2 (en) * | 2009-12-31 | 2012-07-17 | Nantero, Inc. | Compact electrical switching devices with nanotube elements, and methods of making same |

| US8450181B2 (en) * | 2010-01-08 | 2013-05-28 | Sandisk 3D Llc | In-situ passivation methods to improve performance of polysilicon diode |

| WO2011097389A1 (en) * | 2010-02-04 | 2011-08-11 | Sandisk 3D Llc | Non-volatile memory cell containing nanodots and method of making thereof |

| US8389375B2 (en) * | 2010-02-11 | 2013-03-05 | Sandisk 3D Llc | Memory cell formed using a recess and methods for forming the same |

| US8237146B2 (en) * | 2010-02-24 | 2012-08-07 | Sandisk 3D Llc | Memory cell with silicon-containing carbon switching layer and methods for forming the same |

| US20110210306A1 (en) * | 2010-02-26 | 2011-09-01 | Yubao Li | Memory cell that includes a carbon-based memory element and methods of forming the same |

| US8481394B2 (en) * | 2010-03-04 | 2013-07-09 | Sandisk 3D Llc | Memory cell that includes a carbon-based memory element and methods of forming the same |

| US8471360B2 (en) | 2010-04-14 | 2013-06-25 | Sandisk 3D Llc | Memory cell with carbon switching material having a reduced cross-sectional area and methods for forming the same |

| KR101110543B1 (ko) | 2010-04-21 | 2012-02-09 | 주식회사 하이닉스반도체 | 고집적 반도체 장치 |

| US8436447B2 (en) | 2010-04-23 | 2013-05-07 | Sandisk 3D Llc | Memory cell that includes a carbon-based memory element and methods of forming the same |

| JP2012019191A (ja) * | 2010-06-10 | 2012-01-26 | Toshiba Corp | 不揮発性記憶装置の製造方法 |

| US8883589B2 (en) | 2010-09-28 | 2014-11-11 | Sandisk 3D Llc | Counter doping compensation methods to improve diode performance |

| CN102117823B (zh) * | 2010-11-04 | 2013-02-13 | 中国科学院上海微系统与信息技术研究所 | 电阻转换存储纳米结构及其自对准制造方法 |

| US9018692B2 (en) | 2011-01-19 | 2015-04-28 | Macronix International Co., Ltd. | Low cost scalable 3D memory |

| KR20120137862A (ko) * | 2011-06-13 | 2012-12-24 | 삼성전자주식회사 | 3차원 더블 크로스 포인트 어레이를 갖는 반도체 메모리 소자 및 그 제조방법 |

| US9054295B2 (en) * | 2011-08-23 | 2015-06-09 | Micron Technology, Inc. | Phase change memory cells including nitrogenated carbon materials, methods of forming the same, and phase change memory devices including nitrogenated carbon materials |

| US8822288B2 (en) | 2012-07-02 | 2014-09-02 | Sandisk Technologies Inc. | NAND memory device containing nanodots and method of making thereof |

| US8823075B2 (en) | 2012-11-30 | 2014-09-02 | Sandisk Technologies Inc. | Select gate formation for nanodot flat cell |

| US8987802B2 (en) | 2013-02-28 | 2015-03-24 | Sandisk Technologies Inc. | Method for using nanoparticles to make uniform discrete floating gate layer |

| US9331181B2 (en) | 2013-03-11 | 2016-05-03 | Sandisk Technologies Inc. | Nanodot enhanced hybrid floating gate for non-volatile memory devices |

| US9214351B2 (en) | 2013-03-12 | 2015-12-15 | Macronix International Co., Ltd. | Memory architecture of thin film 3D array |

| US9177808B2 (en) | 2013-05-21 | 2015-11-03 | Sandisk Technologies Inc. | Memory device with control gate oxygen diffusion control and method of making thereof |

| US8969153B2 (en) | 2013-07-01 | 2015-03-03 | Sandisk Technologies Inc. | NAND string containing self-aligned control gate sidewall cladding |

| US9559113B2 (en) | 2014-05-01 | 2017-01-31 | Macronix International Co., Ltd. | SSL/GSL gate oxide in 3D vertical channel NAND |

| US9923139B2 (en) * | 2016-03-11 | 2018-03-20 | Micron Technology, Inc. | Conductive hard mask for memory device formation |

| US9947400B2 (en) | 2016-04-22 | 2018-04-17 | Nantero, Inc. | Methods for enhanced state retention within a resistive change cell |

| US10355206B2 (en) | 2017-02-06 | 2019-07-16 | Nantero, Inc. | Sealed resistive change elements |

| KR20180095977A (ko) * | 2017-02-20 | 2018-08-29 | 에스케이하이닉스 주식회사 | 카본 나노 튜브들을 갖는 시냅스를 포함하는 뉴로모픽 소자 |

| CN110085589B (zh) * | 2018-01-26 | 2021-03-26 | 中芯国际集成电路制造(天津)有限公司 | 碳纳米管模块、半导体器件及制造方法 |

| US11349071B2 (en) * | 2019-11-04 | 2022-05-31 | Globalfoundries Singapore Pte. Ltd. | Memory device and a method for forming the memory device |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005072171A (ja) * | 2003-08-22 | 2005-03-17 | Fujitsu Ltd | 半導体装置およびその製造方法 |

| JP2005229019A (ja) * | 2004-02-16 | 2005-08-25 | Univ Nagoya | カーボンナノチューブに対する電極の形成方法及びそれを用いたカーボンナノチューブfet |

| JP2006092746A (ja) * | 2005-12-26 | 2006-04-06 | Kenji Sato | カーボンナノチューブを用いた記憶素子 |

| WO2006121837A2 (en) * | 2005-05-09 | 2006-11-16 | Sandisk 3D Llc | Nonvolatile memory cell comprising a diode and a resistance-switching material |

| JP2007067374A (ja) * | 2005-08-31 | 2007-03-15 | Samsung Electronics Co Ltd | ナノ弾性メモリ素子及びその製造方法 |

| JP2007103529A (ja) * | 2005-09-30 | 2007-04-19 | Fujitsu Ltd | 垂直配向カーボンナノチューブを用いた電子デバイス |

| JP2007165873A (ja) * | 2005-12-12 | 2007-06-28 | Hitachi Global Storage Technologies Netherlands Bv | 単極抵抗ランダムアクセスメモリ(rram)デバイス、および垂直スタックアーキテクチャ |

| US20070190722A1 (en) * | 2002-12-19 | 2007-08-16 | Herner S B | Method to form upward pointing p-i-n diodes having large and uniform current |

| JP2007525030A (ja) * | 2004-02-26 | 2007-08-30 | インターナショナル・ビジネス・マシーンズ・コーポレーション | カーボンナノチューブ複合材相互接続ビアを用いた集積回路チップ |

Family Cites Families (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2136197A (en) * | 1996-03-01 | 1997-09-16 | Micron Technology, Inc. | Novel vertical diode structures with low series resistance |

| US5915167A (en) * | 1997-04-04 | 1999-06-22 | Elm Technology Corporation | Three dimensional structure memory |

| US6034882A (en) | 1998-11-16 | 2000-03-07 | Matrix Semiconductor, Inc. | Vertically stacked field programmable nonvolatile memory and method of fabrication |

| US6706402B2 (en) * | 2001-07-25 | 2004-03-16 | Nantero, Inc. | Nanotube films and articles |

| US6858481B2 (en) | 2001-08-13 | 2005-02-22 | Advanced Micro Devices, Inc. | Memory device with active and passive layers |

| US7038935B2 (en) * | 2002-08-02 | 2006-05-02 | Unity Semiconductor Corporation | 2-terminal trapped charge memory device with voltage switchable multi-level resistance |

| AU2003296988A1 (en) * | 2002-12-19 | 2004-07-29 | Matrix Semiconductor, Inc | An improved method for making high-density nonvolatile memory |

| US7176064B2 (en) | 2003-12-03 | 2007-02-13 | Sandisk 3D Llc | Memory cell comprising a semiconductor junction diode crystallized adjacent to a silicide |

| US6946719B2 (en) | 2003-12-03 | 2005-09-20 | Matrix Semiconductor, Inc | Semiconductor device including junction diode contacting contact-antifuse unit comprising silicide |

| WO2004084229A1 (en) * | 2003-03-18 | 2004-09-30 | Kabushiki Kaisha Toshiba | Programmable resistance memory device |

| WO2005019793A2 (en) * | 2003-05-14 | 2005-03-03 | Nantero, Inc. | Sensor platform using a horizontally oriented nanotube element |

| US7405465B2 (en) | 2004-09-29 | 2008-07-29 | Sandisk 3D Llc | Deposited semiconductor structure to minimize n-type dopant diffusion and method of making |

| US7405165B2 (en) * | 2004-11-05 | 2008-07-29 | Taiwan Semiconductor Manufacturing Co, Ltd | Dual-tank etch method for oxide thickness control |

| GB0426863D0 (en) | 2004-12-07 | 2005-01-12 | Univ Southampton | Method of manufacturing carbon nanotubes |

| US7208372B2 (en) | 2005-01-19 | 2007-04-24 | Sharp Laboratories Of America, Inc. | Non-volatile memory resistor cell with nanotip electrode |

| US7145824B2 (en) | 2005-03-22 | 2006-12-05 | Spansion Llc | Temperature compensation of thin film diode voltage threshold in memory sensing circuit |

| US7579631B2 (en) | 2005-03-22 | 2009-08-25 | Spansion Llc | Variable breakdown characteristic diode |

| US7781862B2 (en) * | 2005-05-09 | 2010-08-24 | Nantero, Inc. | Two-terminal nanotube devices and systems and methods of making same |

| US7479654B2 (en) | 2005-05-09 | 2009-01-20 | Nantero, Inc. | Memory arrays using nanotube articles with reprogrammable resistance |

| US20060250836A1 (en) * | 2005-05-09 | 2006-11-09 | Matrix Semiconductor, Inc. | Rewriteable memory cell comprising a diode and a resistance-switching material |

| US9196615B2 (en) * | 2005-05-09 | 2015-11-24 | Nantero Inc. | Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same |

| EP1890810A2 (en) | 2005-06-17 | 2008-02-27 | Inter-Universitair Microelektronica Centrum | Formation of metal-containing nanoparticles for use as catalysts in carbon nanotube synthysis |

| US7286388B1 (en) | 2005-06-23 | 2007-10-23 | Spansion Llc | Resistive memory device with improved data retention |

| US7482653B2 (en) * | 2005-07-20 | 2009-01-27 | Micron Technology, Inc. | Non-volatile memory with carbon nanotubes |

| JP2007049084A (ja) * | 2005-08-12 | 2007-02-22 | Toshiba Corp | スイッチ素子、メモリ素子および磁気抵抗効果素子 |

| US20070238319A1 (en) | 2005-08-31 | 2007-10-11 | Jewell-Larsen Nels E | Mechanically actuated nanotube switches |

| KR100695164B1 (ko) | 2005-11-09 | 2007-03-14 | 삼성전자주식회사 | 스위칭 소자로서 트랜지스터 및 다이오드를 포함하는하이브리드 타입의 비휘발성 메모리 소자 |

| US7385839B2 (en) * | 2005-12-01 | 2008-06-10 | International Business Machines Corporation | Memory devices using carbon nanotube (CNT) technologies |

| KR100674144B1 (ko) | 2006-01-05 | 2007-01-29 | 한국과학기술원 | 탄소 나노 튜브를 이용한 상변화 메모리 및 이의 제조 방법 |

| US7575984B2 (en) * | 2006-05-31 | 2009-08-18 | Sandisk 3D Llc | Conductive hard mask to protect patterned features during trench etch |

| JP6114487B2 (ja) | 2006-08-08 | 2017-04-12 | ナンテロ,インク. | メモリ素子およびクロスポイントスイッチと不揮発性ナノチューブブロックとを使用したそのアレイ |

| US8030637B2 (en) * | 2006-08-25 | 2011-10-04 | Qimonda Ag | Memory element using reversible switching between SP2 and SP3 hybridized carbon |

| EP1892722A1 (en) | 2006-08-25 | 2008-02-27 | Infineon Technologies AG | Information storage elements and methods of manufacture thereof |

| US7638383B2 (en) * | 2006-09-19 | 2009-12-29 | Intel Corporation | Faceted catalytic dots for directed nanotube growth |

| KR100791948B1 (ko) * | 2006-09-27 | 2008-01-04 | 삼성전자주식회사 | 탄소나노튜브 배선 형성방법 및 이를 이용한 반도체 소자의배선 형성방법 |

| KR100801084B1 (ko) | 2007-01-08 | 2008-02-05 | 삼성전자주식회사 | 저항체를 이용한 비휘발성 메모리 장치 및 그 제조 방법 |

| US7846785B2 (en) * | 2007-06-29 | 2010-12-07 | Sandisk 3D Llc | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same |

| US8233308B2 (en) * | 2007-06-29 | 2012-07-31 | Sandisk 3D Llc | Memory cell that employs a selectively deposited reversible resistance-switching element and methods of forming the same |

| US8558220B2 (en) | 2007-12-31 | 2013-10-15 | Sandisk 3D Llc | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element formed over a bottom conductor and methods of forming the same |

| US20090166610A1 (en) | 2007-12-31 | 2009-07-02 | April Schricker | Memory cell with planarized carbon nanotube layer and methods of forming the same |

-

2007

- 2007-12-31 US US11/968,154 patent/US8236623B2/en not_active Expired - Fee Related

-

2008

- 2008-12-30 CN CN200880123685.1A patent/CN101919047B/zh not_active Expired - Fee Related

- 2008-12-30 EP EP08869555.6A patent/EP2227824B1/en active Active

- 2008-12-30 KR KR1020107013893A patent/KR101494746B1/ko not_active IP Right Cessation

- 2008-12-30 WO PCT/US2008/088584 patent/WO2009088888A2/en active Application Filing

- 2008-12-30 JP JP2010540945A patent/JP2011508458A/ja active Pending

- 2008-12-31 TW TW097151907A patent/TW200943489A/zh unknown

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070190722A1 (en) * | 2002-12-19 | 2007-08-16 | Herner S B | Method to form upward pointing p-i-n diodes having large and uniform current |

| JP2005072171A (ja) * | 2003-08-22 | 2005-03-17 | Fujitsu Ltd | 半導体装置およびその製造方法 |

| JP2005229019A (ja) * | 2004-02-16 | 2005-08-25 | Univ Nagoya | カーボンナノチューブに対する電極の形成方法及びそれを用いたカーボンナノチューブfet |

| JP2007525030A (ja) * | 2004-02-26 | 2007-08-30 | インターナショナル・ビジネス・マシーンズ・コーポレーション | カーボンナノチューブ複合材相互接続ビアを用いた集積回路チップ |

| WO2006121837A2 (en) * | 2005-05-09 | 2006-11-16 | Sandisk 3D Llc | Nonvolatile memory cell comprising a diode and a resistance-switching material |

| JP2007067374A (ja) * | 2005-08-31 | 2007-03-15 | Samsung Electronics Co Ltd | ナノ弾性メモリ素子及びその製造方法 |

| JP2007103529A (ja) * | 2005-09-30 | 2007-04-19 | Fujitsu Ltd | 垂直配向カーボンナノチューブを用いた電子デバイス |

| JP2007165873A (ja) * | 2005-12-12 | 2007-06-28 | Hitachi Global Storage Technologies Netherlands Bv | 単極抵抗ランダムアクセスメモリ(rram)デバイス、および垂直スタックアーキテクチャ |

| JP2006092746A (ja) * | 2005-12-26 | 2006-04-06 | Kenji Sato | カーボンナノチューブを用いた記憶素子 |

Non-Patent Citations (1)

| Title |

|---|

| JPN6013035088; Phil Smith et al.: 'Polishing TiN for Nanotube Synthesis' Proceedings of the 16th Annual Meeting of ASPE , 200111, American Society for Precision Engineering * |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9048176B2 (en) | 2011-09-08 | 2015-06-02 | Kabushiki Kaisha Toshiba | Nonvolatile storage device |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2009088888A3 (en) | 2009-09-17 |

| US20090168491A1 (en) | 2009-07-02 |

| CN101919047B (zh) | 2013-07-10 |

| KR101494746B1 (ko) | 2015-03-02 |

| US8236623B2 (en) | 2012-08-07 |

| CN101919047A (zh) | 2010-12-15 |

| EP2227824A4 (en) | 2010-12-15 |

| WO2009088888A2 (en) | 2009-07-16 |

| TW200943489A (en) | 2009-10-16 |

| EP2227824A2 (en) | 2010-09-15 |

| EP2227824B1 (en) | 2014-04-16 |

| KR20100133948A (ko) | 2010-12-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8236623B2 (en) | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element and methods of forming the same | |

| US8558220B2 (en) | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element formed over a bottom conductor and methods of forming the same | |

| US8304284B2 (en) | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element, and methods of forming the same | |

| JP5469159B2 (ja) | カーボンナノチューブ可逆抵抗スイッチング素子を含むメモリセルおよびその形成方法 | |

| JP2011508980A (ja) | 平坦化されたカーボンナノチューブ層を有するメモリセルおよびそれを形成する方法 | |

| US8466044B2 (en) | Memory cell that includes a carbon-based memory element and methods forming the same | |

| US8530318B2 (en) | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element formed over a bottom conductor and methods of forming the same | |

| US20100102291A1 (en) | Carbon-based memory elements exhibiting reduced delamination and methods of forming the same | |

| KR20110005692A (ko) | 탄소계 메모리 소자를 포함한 메모리 셀과 이를 형성하는 방법 | |

| US8878235B2 (en) | Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element and methods of forming the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111026 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111026 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130711 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130723 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20131021 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131028 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20131028 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20131126 |