図1は高速I/Fを含んだ伝送システムの構成を示す図である。本実施例では、動作周波数帯に応じて送信機と受信機の電源電圧および各種パラメータを最適化するシステムを示す。本実施例の伝送システムは、送信側LSIの内部にある送信機となる送信側I/Fマクロ101と、受信側LSIの内部にある受信機となる受信側I/Fマクロ102と、送信側I/Fマクロ101と受信側I/Fマクロ102とを接続する伝送路103とを備える。送信側I/Fマクロ101は複数の動作周波数帯を有する。受信側マクロ102も、送信側マクロ101と対応する複数の動作周波数帯を有する。さらに、本実施例の伝送システムは、上位システム制御装置104と、電源コントローラ105と、I/Fパラメータコントローラ106と、I/Fパラメータ最適化テーブル107とを有する。

電源コントローラ105はシステム上のI/Fに供給する電源電圧を制御する回路であり、例えばDC−DCコンバータを備えたような制御回路である。I/Fパラメータコントローラ106は送信側I/Fマクロ101、受信側I/Fマクロ102に対して各IFパラメータの設定を行う。I/Fパラメータ最適化テーブル107は、例えば、RAMやフラッシュメモリ、レジスタファイル、ハードディスク等の記憶装置に格納されている。I/Fパラメータ最適化テーブル107には、伝送システムの動作周波数帯毎の、予め求められている、送信側I/Fマクロ101と受信側I/Fマクロ102の電源電圧、エンファシス強度、イコライザ強度が含まれている。

本実施例の伝送システムの動作を説明するために、例として、送信側LSIと受信側LSIも含めたシステム全体が扱うアプリケーションがアプリケーションAからアプリケーションBに変化したことにより、動作周波数が最大で5GHzから最大で0.5GHzに変化した場合、すなわち、すなわち動作周波数帯を5GHzから0.5GHzに下げた場合に、電源電圧およびI/Fの各種パラメータを最適化する場合の動作の説明を行う。

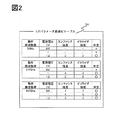

上位システム制御装置104は、送信側LSIと受信側LSIも含めたシステム全体の稼動状態をモニタし、送信側I/Fマクロ101と受信側I/Fマクロ102の動作周波数帯、すなわち伝送システムの動作周波数帯を決定する。この例では、上位システム制御装置104が、アプリケーションAからアプリケーションBに切り替わった事をモニタ、検出し、送信側I/Fマクロ101と受信側I/Fマクロ102の動作周波数帯を5GHzから0.5GHzへ下げることを決定する。上位システム制御装置104は、さらに、決定した動作周波数帯に基づいて、送信側I/Fマクロ101と受信側I/Fマクロ102の、最適な電源電圧値と各種I/Fパラメータの設定情報をI/Fパラメータ最適化テーブル107から取得する。例えば、I/Fパラメータ最適化テーブル107には、図2のI/Fパラメータ最適化テーブル201に示すデータが前もって格納されている。このテーブルを「動作周波数帯0.5GHz」をキーワードにして検索すると、「電源電圧」、「エンファシス強度」、「イコライザ強度」の各パラメータを取得することができる。消費電力を下げることを目的としているため、上位システム制御装置104は、I/Fパラメータ最適化テーブル107から取得可能なパラメータの中で最も電源電圧の低い条件を選ぶ。本実施例では、「電源電圧0.6(V)」、「エンファシス強度1」、「イコライザ強度1」というパラメータが取得される。本実施例では、送信側I/Fマクロ101の設定パラメータとしてはエンファシス強度を、受信側I/Fマクロ102の設定パラメータとしてはイコライザ強度をテーブル化する例を示したが、エンファシス強度、イコライザ強度以外に、出力振幅制御値、送端抵抗制御値などを予めテーブル化して取得することもできる。

上位システム制御装置104は、I/Fパラメータ最適化テーブル107から取得した電源電圧の設定パラメータを電源コントローラ105へ、各I/FのパラメータをI/Fパラメータコントローラ106に出力する。電源コントローラ105は、上位システム制御装置104から取得したパラメータに基づいて、送信側I/Fマクロ101に対して電源制御信号108を、受信側I/Fマクロ102に対して電源制御信号109をそれぞれ送信し、送信側I/Fマクロ101と受信側I/Fマクロ102の電源電圧の設定を行う。これにより、送信側I/Fマクロ101、受信側I/Fマクロ102の電源電圧の最適化、すなわち低電力化を行うことができる。なお、本実施例では、送信側I/Fマクロ101、受信側I/Fマクロ102とに同じ電源電圧値を設定しているが、互いに異なる電源電圧値が最適値の場合もある。互いに異なる電源電圧値がそれぞれの最適値の場合には、それぞれの最適な電源電圧値をI/Fパラメータ最適化テーブル107に格納しておき、送信側I/Fマクロ101と受信側I/Fマクロ102とにそれぞれの最適な電源電圧の設定を行う。I/Fパラメータコントローラ106は、上位システム制御装置104から取得したパラメータに基づいて、送信側I/Fマクロ101に対してパラメータ設定信号110を、受信側I/Fマクロ102に対してパラメータ設定信号111を送信し、各I/Fパラメータの設定を行う。本実施例では、送信側I/Fマクロ101と受信側I/Fマクロ102とに電源電圧0.6Vが設定され、「エンファシス強度1」が送信側I/Fマクロ101に対して設定され、「イコライザ強度1」が受信側I/Fマクロ102に対して設定される。これにより、低電力のために最適化されている電源電圧が瞬時に得られ、低電力のために最適化されている電源電圧において最適化されているI/Fパラメータが、電源電圧を変化させる前後の間で再調整や再トレーニングを行うことなく、短時間に設定される。従って、アプリケーションが変わり、動作周波数帯が変化する際に、動的に伝送システムの低電力化を行うことができる。

図3に本実施例の伝送システムにおいて、動作環境が変化し、動作周波数帯の切替が行われた際にI/Fパラメータの最適化を行う処理のフローチャートを示す。ステップ301で動作環境が変化した場合はステップ302へ進む。本実施例の説明において動作環境が変化した場合とは、上述のように、システムが処理するアプリケーションがアプリケーションAからアプリケーションBに変化した場合である。動作環境が変化したかどうかの判断は、上位システム制御装置104が行う。動作環境の変化を検出しない限りはステップ301で待機し、動作環境の変化を待つ。従って、動作環境の変化が無ければ、I/Fに設定されている条件を保持した状態でデータの伝送が行われる。動作環境の変化があって、ステップ302に進むと、上位システム制御装置104が、変化後の動作環境に合った動作周波数帯を決定する。動作周波数帯が決定されると、ステップ303にて上位システム制御装置104がI/Fパラメータ最適化テーブル107を参照し、電源電圧設定情報とI/Fパラメータ設定情報を取得し、ステップ304へ進む。ステップ304では、I/Fパラメータ最適化テーブル107から取得したパラメータ値の、送信側I/Fマクロ101と受信側I/Fマクロ102への設定が行われる。上位システム制御装置104が取得した電源電圧設定情報とI/Fパラメータ設定情報は、電源コントローラ105とI/Fパラメータコントローラ106を介して、送信側I/Fマクロ101と受信側I/Fマクロ102の電源電圧とI/Fパラメータとして設定され、動作周波数帯の切り替えが終了する。切り替えの終了後、ステップ301へ戻る。以上のように、動作環境の変化に応じて、動的に送信側I/Fマクロ101と受信側I/Fマクロ102の電源電圧とI/Fパラメータの切り替えが行われる。

実施例1のI/Fパラメータ最適化テーブル107の作成は、外部装置を実施例1の伝送システムに接続して行うことができるが、伝送システムに組み込まれているテスト装置で行うことも可能である。実施例2では、伝送システムにトレーニングモードを実行するテスト装置を組み込んだ場合の実施例を示す。

図4に、トレーニングモードを実行するテスト装置を組み込んだ場合の、送信側I/Fの構成を示す。送信側I/F401は入力端子に入力されたLSI内部信号を、出力端子から後述の受信用I/Fへと接続されている伝送路408に向けて出力するものである。送信側I/F401はドライバ回路402、スイッチング回路404、トレーニング信号発生器405を備える。

ドライバ回路402はI/Fパラメータを持つ出力回路であり、例えばCMOSタイプやCMLタイプの回路により構成される。I/Fパラメータ設定情報403はI/Fパラメータコントローラ407から送信される信号である。I/Fパラメータ設定情報403はドライバ回路402のI/Fパラメータを制御する信号であり、例えばエンファシス強度制御や出力振幅制御、送端抵抗制御等の制御信号である。スイッチング回路404は通常モードと後述するトレーニングモードを切り換える回路であり、上位システム制御装置から送信される通常モード/トレーニングモード切替制御信号406により制御される。トレーニング信号発生器405はトレーニング時に使用する信号を発生する回路であり、例えばPRBS(Pseudo Random Binary Sequence)等の疑似ランダムパターンを発生する信号発生器である。なお、図4ではトレーニング信号発生器405を送信側I/F401の内部に有する構成例を示しているが、送信側I/F401の外部、またはシステムの外部に実装することも可能である。

図5に受信側I/Fの詳細を示す。受信側I/F501の通常動作は、送信側I/F401に接続されている伝送路408を介し入力端子に受信した信号を、出力端子からLSI内部に向けて伝送するものである。受信側I/F501はレシーバ回路502、スイッチング回路504、ループバックパス505、ループバック用ドライバ506を備える。レシーバ回路502はI/Fパラメータをもつ入力回路であり、例えばCMOSタイプやCMLタイプの回路により構成される。I/Fパラメータ設定情報503はレシーバ回路502のI/Fパラメータを制御する信号であり、例えばイコライザ強度制御やオフセット調整制御、受端抵抗制御等の制御信号である。スイッチング回路504は通常モードと後述するトレーニングモードを切り換える回路であり、上位システム制御装置からの通常モード/トレーニングモード切替制御信号508により制御される。ループバックパス505とループバック用ドライバ506はトレーニングモードにて使用する観測経路であり、レシーバ回路502の受信した信号をループバックモニタ端子510に出力する。

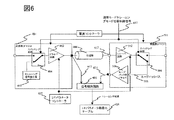

図6は図4、図5で示したI/Fを含んだシステムのトレーニングモードについて説明した図である。ここでのトレーニング対象は伝送路408で接続された送信側I/Fマクロ401と受信側I/Fマクロ502である。トレーニング時には各I/Fマクロをトレーニングモードに切り替える。

各I/Fマクロをトレーニングモードに切り換えることで、トレーニング用信号の発生や、受信信号をモニタ信号に出力するループバックを行うことが可能となる。トレーニングモードへの切替は、上位システム制御装置からの通常モード/トレーニングモード切替制御信号607により行う。送信側I/Fマクロ401はトレーニングモードに切り換えた場合の形態であり、トレーニング信号発生器405から出力した信号を、スイッチング回路404を介し、ドライバ回路402から伝送路408を通じ受信側I/Fマクロ501に向けて送信する。受信側I/Fマクロ501はループバックモードに切り換えた場合の例である。レシーバ回路502にて受信した信号を、スイッチング回路504を介し、ループバックパス505を通じてループバック用ドライバ506から出力する。信号観測回路606は信号観測機能を有するものであり、例えばBER測定や、EYEマスクパタン判定等の機能を持つものである。

信号観測回路606はドライバ回路402の出力信号613とループバック用ドライバ506からの出力信号614を比較し伝送性能に対する判定を行う。なお、入力端子617での出力信号の波形を観測することによりドライバ回路402より出力された波形について伝送路を通過した後の状態で観測することもできる。信号観測回路606による伝送性能の判定を必要に応じてI/Fパラメータの組合せを換えながら実行し、トレーニング結果、すなわち判定結果をI/Fパラメータ最適化テーブル616内へ格納する。なお信号観測回路606の実装については、システム内部、システム外部のどちらでも可能であり、システム外部に実装する場合はBERTやオシロスコープ等の測定装置を利用することも可能である。また、システム内に実装する場合は、I/Fマクロと共通のLSI上に実装することも可能である。

図7にエンファシス強度[7:0]、イコライザ強度[7:0]をパラメータに持つI/Fに対するトレーニングおよび、I/Fパラメータ最適化テーブルに格納されるデータの例を示す。この例では、トレーニングのパラメータとして動作周波数帯と電源電圧を選んでいる。動作環境パラメータ701は、電源電圧を0.6V、1.0V、1.2Vと、動作周波数帯を0.5GHz、2.5GHz、5.0GHzとした場合である。動作環境パラメータ701から決定する各A〜Iの条件に対して、エンファシス強度[7:0]、イコライザ強度[7:0]を総当りで切替え、BERを取得する。動作環境パラメータ701の条件で取得したBER結果の例をトレーニング結果702,703に示す。動作環境パラメータ701の全ての条件に対して取得したBER結果からI/Fパラメータ最適化データを取得し、I/Fパラメータ最適化テーブル704内に格納する。I/Fパラメータ最適化テーブルは、あるキーワードに対してI/Fパラメータを決定するものであり、図7に示すように動作周波数帯と電源電圧に対してI/Fパラメータを決定するものに限らず、様々なキーワードに対してI/Fパラメータを決定するテーブルも実現することができる。例えば、I/Fパラメータ最適化テーブル作成時に、電源電圧をパラメータとしたトレーニングを行い、同じ動作周波数帯であっても、より短距離の伝送経路では、電源電圧を引き下げることができる等、伝送路長に合わせた電源電圧の最適化を行うことが可能である。

図8に図6に示す構成の、図7に示すトレーニング例における、トレーニングのフローチャートを示す。トレーニングを行う際にはまずステップ801にてI/Fをトレーニングモードに切り換える。トレーニングモードへの切り替えの信号は、上位システム制御装置から発せられる。ステップ802で動作環境パラメータの初期値を設定する。動作環境パラメータとは電源電圧や動作周波数帯等を決定するパラメータである。その他の動作環境パラメータとしては、温度や伝送路長等も挙げることができる。ステップ803ではI/Fパラメータを初期化する。ステップ802とステップ803で決定する動作環境パラメータとI/Fパラメータの初期値はトレーニングの初期状態であり、トレーニングの仕様に合わせて任意に変更することが可能である。ステップ804でトレーニング信号を発生する。このとき図6のトレーニング信号発生器405から出力された信号は、スイッチング回路404を介し、ドライバ回路402から伝送路408を通じ受信側I/Fマクロ501に向けて送信される。受信側I/Fマクロ501はレシーバ回路502にて受信した信号を、スイッチング回路504を介し、ループバックパス505と通じてループバック用ドライバ506から出力する。ステップ805でトレーニング結果の取得を行う。信号観測回路606は、伝送性能を観測し、判定する。例えば、ドライバ回路402の出力信号613とループバック用ドライバ506からの出力信号614を比較しBER評価を行い、判定を行う。ステップ806ではトレーニング結果をI/Fパラメータ最適化テーブルへ格納する。例えばトレーニング結果702のエンファシス強度1、イコライザ強度2の判定が決定した時点でI/Fパラメータ最適化テーブルへトレーニング結果を格納する。ステップ807で、必要なI/Fパラメータの組合せに対するトレーニングが完了したかを判定する。必要なI/Fパラメータの組合せはトレーニングの仕様、目的に応じて任意に決定するものである。図7の例では、必要なI/Fパラメータの組合せはエンファシス強度[7:0]パターン、イコライザ強度[7:0]パターンで64パターンの組合せとなる。必要なI/Fパラメータの組合せに対するトレーニングが完了していれば、ステップ809へ進む。必要なI/Fパラメータの組合せに対するトレーニングが完了していない場合は、ステップ808へ進み、新たにI/Fパラメータの組合せを設定し、ステップ805へ進む。ステップ809で必要な動作環境パラメータの組合せに対するトレーニングが完了したかを判定する。必要な動作環境パラメータの組合せはトレーニングの仕様、目的に応じて任意に決定するものである。図7の例では、必要な動作環境パラメータの組合せは電源電圧が0.6V、1.0V、1.2V、動作周波数帯がそれぞれの電源電圧に対して0.5GHz、2.5GHz、5.0GHzの計9パターンの組合せとなる。必要な動作環境パラメータの組合せが完了していない場合は、ステップ810へ進み新たに動作環境パラメータを設定し、ステップ803へ進む。必要な動作環境パラメータの組合せが完了していれば、トレーニングは完了となり、I/Fパラメータ最適化テーブルが完成する。以上のステップ801〜810によりトレーニングが完了する。これにより、予めI/Fの最適な電源電圧とI/Fパラメータのテーブルを得ることができる。

以上、本実施形態によって、本発明を詳細に説明したが、上記に限定されるものではなく、その要旨を逸脱しない範囲で変更が可能である。