JP2011029068A - 電流帰還型電源及び荷電粒子線装置 - Google Patents

電流帰還型電源及び荷電粒子線装置 Download PDFInfo

- Publication number

- JP2011029068A JP2011029068A JP2009175305A JP2009175305A JP2011029068A JP 2011029068 A JP2011029068 A JP 2011029068A JP 2009175305 A JP2009175305 A JP 2009175305A JP 2009175305 A JP2009175305 A JP 2009175305A JP 2011029068 A JP2011029068 A JP 2011029068A

- Authority

- JP

- Japan

- Prior art keywords

- current

- terminal

- feedback

- input

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Amplifiers (AREA)

Abstract

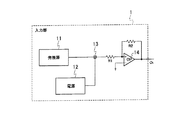

【解決手段】 入力信号を入力して、入力信号を反転した信号を出力する入力部1と、入力端子INを入力部1に接続し、帰還端子FBを負荷4の第1端子N4に接続し、出力端子OUTを負荷4の第2端子N3に接続し、帰還端子FBから帰還される帰還電流IFをゼロにする電流帰還部2と、第1端子N4と接地電位間に接続され、負荷4に流れる電流の大きさを段階的に切り替えるゲイン切り替え部3とを備え、入力信号のパターンに対応した電流を負荷4に流す。

【選択図】図1

Description

図1に示したように、本発明の実施の形態に係る電流帰還型電源は、入力信号を入力して、入力信号を反転した信号を出力する入力部1と、入力端子INを入力部1に接続し、帰還端子FBを負荷4の第1端子N4に接続し、出力端子OUTを負荷4の第2端子N3に接続し、帰還端子FBから帰還される帰還電流IFをゼロにする電流帰還部2と、第1端子N4と接地電位間に接続され、負荷4に流れる電流の大きさを段階的に切り替えるゲイン切り替え部3とを備え、入力信号のパターンに対応した電流を負荷4に流す。入力部1は、所定の電流パターンを有する入力信号を反転した信号を出力する。「所定の電流パターン」とは、負荷4に供給しようとするパターンに対応して決められる。例えば、荷電粒子線装置などで照射対象の表面に荷電粒子線を走査するために、図3に示すような鋸波のパターンを持つ信号が必要になるが、鋸波のパターンは一例であり、荷電粒子線を走査する以外の目的であれば、当業者が様々のパターンを設定可能である。入力部1は、外部から図3に示すような鋸波の入力信号を受信するように構成しても良いが、図4に示すように、発振器11と電源12を内蔵し、発振器11の出力と電源12の出力とをアナログ乗算器(混合器)13で乗算して鋸波を生成するように構成することもできる。

I1b=I1a ……(1)

である。入力ノードDと出力ノードEの間に、定電圧回路24と電流循環回路25とが並列に接続されている。定電圧回路24は入力ノードDと出力ノードEの間に一定の電位を生成するので、定電圧回路24を通る電流IMは一定である。したがって入力ノードDから電流循環回路25へ流れる電流IDと、電流循環回路25から出力ノードEへ流れる電流IEとが実質的に同じID=IEになると、第1のカレントミラー回路22での電流I1bと第2のカレントミラー回路23での電流I2bとが実質的に同じI1b=I2bになる。

IE=ID−IL ……(2)

の関係になる。ここで、

IE ≒ ID ……(3)

と近似できるためには、ILがIDより無視できるほど十分小さい必要がある。電流循環回路25は、入力電流IDを十分大きい係数の乗算により増幅してから負荷4に電流を供給し、その後、同一な係数による除算により減幅して出力する。電流循環回路25の増幅係数Aを考慮すると、(2)式は、

IE=ID−IL/A ……(4)

となる。仮に、増幅係数Aが100とすると、電流IDと電流IEとの差分はIL/100となるので、増幅係数が大きければ大きいほどその差分は小さくなる。出力ノードEにおいて、電流関係は、

I2b=IM+IE ……(4)

となり、入力ノードDにおいて、電流関係は、

I1b=IM+ID ……(5)

となる。第2のカレントミラー回路23には、帰還ノードBを経由して流入する第2の基準電流I2aを流す電流経路と、第2の基準電流I2aに等しい第2のミラー電流I2bが、出力ノードEを経由して流入する電流経路の二つの電流経路が備えられている。したがって流入電流I2bと実質的に同じ電流I2aが帰還ノードBに接続された電流経路に流れる:

I2b=I2a ……(6)

又、電流帰還部2において、電流循環回路25の増幅係数をAとすると、

I1a=I2a−IL/A ……(7)

となるので、増幅係数Aが十分大きくなれば、IL/Aは無視できるほど小さくなり、

I1a≒I2a ……(8)

と近似できるので、帰還ノードBへ、帰還端子FBを介して出力ノードCから帰還される帰還電流IFは実質的にゼロとなる。よって、負荷4に流れる電流ILは、ゲイン切り替え部3を流れる電流ICに等しくなる。即ち、

IL≒IC ……(9)

で近似できる。

図2に示したように、第1の具体的回路例に係る電流帰還型電源は、図1において回路ブロック表示した電流帰還型電源と同様に、入力部1、電流帰還部2、ゲイン切り替え部3,及び負荷4を備え、電流帰還部2は、電圧伝達回路21、第1のカレントミラー回路22,第2のカレントミラー回路23,定電圧回路24、及び電流循環回路25aを有する。入力部1は、外部から図3に示すような鋸波の入力信号を受信するように構成しても良いが、図4に示すように、発振器11と電源12を内蔵し、発振器11の出力と電源12の出力とをアナログ乗算器(混合器)13で乗算して鋸波を生成するように構成することもできる。本発明の第1の具体的回路例において、入力部1は図4に示すように、抵抗器R1の一端に入力される入力信号Vinを反転して出力する反転回路(R1,R2,14)を有する。抵抗器R1,R2及びオペレーショナル増幅器14からなる反転回路の出力Voutは:

Vout=−R2/R1・Vin ……(10)

で示される。式(10)から、R1=R2であれば、入力信号Vinを増幅しないで、その波形のみを反転して、入力部1の出力端子Oiに出力することとなる。例えば、R1=R2=10kΩ程度の値を採用可能である。図4に示した発振器11、電源12、アナログ乗算器(混合器)13や反転回路(R1,R2,14)などは、所定のパターンの入力信号を得るための入力部1の一例に過ぎない。希望のパターンによって入力部1の構成もそれに応じて設計することができる。

I1a=I1b+2IBase ……(11)

ここで、IBaseは、第1のカレントミラー回路22を構成するトランジスタTr5及びTr6の各々のベース電流である。一般的に、ベース電流はエミッタ電流及びコレクタ電流のわりに極めて少ないので、

I1a≒I1b ……(12)

と近似できる。第1の具体的回路例においては、第1のカレントミラー回路22は、一例に過ぎず、他の形態のカレントミラー回路を使用することもできる。後述する第2のカレントミラー回路も同様である。

IE=β8・IB ……(13)

電流循環回路25aのトランジスタTr8のエミッタ電流IEはすべて電流循環回路25aのトランジスタ(第3の出力トランジスタTr)Tr9のベース端子に流入する。トランジスタTr9の電流増幅率をβ9とすれば、トランジスタTr9のエミッタ電流は、トランジスタTr9のベース電流I'Bと以下のような関係になる:

I'E=β9・I'B ……(14)

結局、電流循環回路25aのトランジスタTr8のベース端子に流入した少量の電流は、電流循環回路25aのトランジスタTr8及びトランジスタTr9を経て「β8・β9」倍の電流になる。通常、トランジスタの電流増幅率β8,β9は、数10〜数10000であるので、電流循環回路25aのトランジスタTr9のエミッタ端子から、電流帰還部2の出力端子OUTとトランジスタ(第4の出力トランジスタTr)Tr10に大電流が流れ出る。

β8・β9ID−IL=β8・β9IE ……(15)

したがって、入力ノードDから流入する電流IDと出力ノードEへの流出する電流IEの差は以下のようになることが分かる:

ID−IE=I1b−I2b=IL/β8・β9 ……(16)

ここで、電流増幅率β8,β9,β10,β11は、通常、数10〜数10000の値であり、ILが比較的小さい値であることを勘案すると、IL/β8・β9(=1/β10・β11)は無視することができるほど十分小さい値であるので、

I1b≒I2b ……(17)

と近似できる。

I2a=I2b+2IBase ……(18)

ここで、IBaseはトランジスタTr10及びトランジスタTr9のそれぞれのベース電流である。一般的に、ベース電流はエミッタ電流及びコレクタ電流のわりに極めて少ないので、

I2a≒I2b ……(19)

と近似できる。式(12),(17)及び(19)から、

I1a≒I2a ……(20)

と近似できる。即ち、帰還ノードBに流入する電流I1aと帰還ノードBから流出する電流I2aとは互いに実質的に同じである。したがって帰還ノードBへ、電流帰還部2の帰還端子FBを介して出力ノードCから帰還される帰還電流IFは実質的にゼロになる。よって、式(9)に示したように、負荷4に流れる電流ILは、ゲイン切り替え部3を流れる電流ICに等しくなる。

IC=VC/Rc1=−Vin/1 ……(20)

第1の具体的回路例に係る電流帰還型電源においては、帰還ノードBへ、電流帰還部2の帰還端子FBを介して出力ノードCから帰還される帰還電流IF=0となるように動作するので、式(9)から、負荷4には電流IL=ICが流れることになる。一方、第2の検出抵抗Rc2が10Ωで、第2のスイッチSw2がオンになると、ゲイン切り替え部3を流れる電流ICは以下のようになる:

IC=VC/Rc2=−Vin/10 ……(21)

即ち、スイッチを第1のスイッチSw1から第2のスイッチSw2に切り替えると、ゲイン切り替え部3を流れる電流ICは第1の検出抵抗Rc1を流れる電流の0.1倍になる。同様に、スイッチを第2のスイッチSw2から第3のスイッチSw3に切り替えると、ゲイン切り替え部3を流れる電流ICは第1の検出抵抗Rc1を流れる電流の0.01倍になり、スイッチを第3のスイッチSw3から第4のスイッチSw4に切り替えると、ゲイン切り替え部3を流れる電流ICは第1の検出抵抗Rc1を流れる電流の0.001倍になる。このようにして、第1の検出抵抗Rc1、第2の検出抵抗Rc2、第3の検出抵抗Rc3、第4の検出抵抗Rc4の抵抗値を、順に10倍ずつ大きくなるようにすれば、スイッチSw1〜Sw4を選択的にオンすることによって、負荷4に流れる電流ILの値を10倍ずつ切り替えることができる。

図5に示したように、第2の具体的回路例に係る電流帰還型電源は、図2に示した第1の具体的回路例と同様に、入力部1、電流帰還部2、ゲイン切り替え部3,及び負荷4を備え、電流帰還部2は、帰還端子FBに接続される帰還ノードBを有し、入力端子INから入力信号を反転した信号を入力し、帰還ノードBの電位を入力端子INの電位に等しくする電圧伝達回路21と、帰還ノードBに第1の基準電流を流す電流経路と、第1の基準電流に等しい第1のミラー電流を流す電流経路とを有する第1のカレントミラー回路22と、帰還ノードBを経由して流れる第2の基準電流を流す電流経路と、第2の基準電流に等しい第2のミラー電流を流す電流経路とを有する第2のカレントミラー回路23と、第1のミラー電流を流す電流経路に接続された入力ノードDと、第2のミラー電流を流す電流経路に接続された出力ノードE間に接続され、第1のミラー電流の一部を入力して、入力ノードDと出力ノードE間に一定の電位を生成する定電圧回路24と、入力ノードDと出力ノードE間に接続され、第1のミラー電流の残余を入力し、ミラー電流の残余を増幅し、増幅した電流の一部を出力端子OUTから負荷4の第2端子N3に供給し、増幅した電流の残余を第2のカレントミラー回路23に出力する電流循環回路25bを有する。

β8ID−IL=β8IE ……(22)

したがって、入力ノードDから流入する電流IDと出力ノードEへの流出する電流IEの差は以下のようになることが分かる:

ID−IE=I1b−I2b=IL/β8 ……(23)

ここで、電流増幅率β8,β11が十分大きければ、ILが比較的小さい値であることを勘案すると、IL/β8(=IL/β11)は無視することが可能になるので、第2の具体的回路例においても、式(17)で近似可能となる。よって、第2の具体的回路例においても、式(12),(17)及び(19)から、式(20)の近似が可能となり、帰還ノードBへ、電流帰還部2の帰還端子FBを介して出力ノードCから帰還される帰還電流IFは実質的にゼロになる。よって、式(9)に示したように、負荷4に流れる電流ILは、ゲイン切り替え部3を流れる電流ICに等しくなる。

上記の回路ブロック表示した電流帰還型電源、或いは、第1若しくは第2の具体的回路例に係る電流帰還型電源は、荷電粒子源(図示省略)と、荷電粒子源から出射した荷電粒子線を集束させる集束レンズ系(図示省略)と、集束させられた荷電粒子線を、照射対象上の所定領域に走査する走査コイル4と、照射対象を搭載し、照射対象上の所望の位置に荷電粒子線が照射されるように移動可能なステージ(図示省略)と、走査コイル4に走査電流を供給するスイープ電源とを備える荷電粒子線装置のスイープ電源に適用可能である。

上記のように、本発明は上記の実施の形態及び実施例によって記載したが、この開示の一部をなす論述及び図面は本発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例及び運用技術が明らかとなろう。

2…電流帰還部

3…ゲイン切り替え部

4…負荷

21…電圧伝達回路

22…第1のカレントミラー回路

23…第2のカレントミラー回路

24…定電圧回路

25…電流循環回路

FB…帰還端子

IN…入力端子

N3…第2端子

N4…第1端子

OUT…出力端子

Claims (6)

- 入力信号を入力して、前記入力信号を反転した信号を出力する入力部と、

入力端子を前記入力部に接続し、帰還端子を負荷の第1端子に接続し、出力端子を前記負荷の第2端子に接続し、前記帰還端子から帰還される帰還電流をゼロにする電流帰還部と、

前記第1端子と接地電位間に接続され、前記負荷に流れる電流の大きさを段階的に切り替えるゲイン切り替え部

とを備え、前記入力信号のパターンに対応した電流を前記負荷に流すことを特徴とする電流帰還型電源。 - 前記ゲイン切り替え部が、互いに抵抗値が異なる複数の検出抵抗を切り替え可能に並列接続してなることを特徴とする請求項1に記載の電流帰還型電源。

- 前記電流帰還部が、

前記帰還端子に接続される帰還ノードを有し、前記入力端子から前記入力信号を反転した信号を入力し、前記帰還ノードの電位を前記入力端子の電位に等しくする電圧伝達回路と、

前記帰還ノードに第1の基準電流を流す電流経路と、前記第1の基準電流に等しい第1のミラー電流を流す電流経路とを有する第1のカレントミラー回路と、

前記帰還ノードを経由して流入する第2の基準電流を流す電流経路と、前記第2の基準電流に等しい第2のミラー電流を流す電流経路とを有する第2のカレントミラー回路と、

前記第1のミラー電流を流す電流経路に接続された入力ノードと、前記第2のミラー電流を流す電流経路に接続された出力ノード間に接続され、前記第1のミラー電流の一部を入力して、前記入力ノードと前記出力ノード間に一定の電位を生成する定電圧回路と、

前記入力ノードと前記出力ノード間に接続され、前記第1のミラー電流の残余を入力し、前記ミラー電流の残余を増幅し、増幅した電流の一部を前記出力端子から前記負荷の第2端子に供給し、増幅した電流の残余を前記第2のカレントミラー回路に出力する電流循環回路

とを備えることを特徴とする請求項1又は2に記載の電流帰還型電源。 - 前記電圧伝達回路が、

コレクタ端子を正電源側に接続し、エミッタ端子を前記入力端子に接続した第1のトランジスタと、

コレクタ端子を負電源側に接続し、エミッタ端子を前記入力端子に接続した第2のトランジスタと、

ベース端子を前記第1のトランジスタのベース端子に接続し、コレクタ端子を前記第1の基準電流を流す電流経路に接続し、エミッタ端子を第1の帰還ノード抵抗を介して前記帰還端子に接続した第3のトランジスタと、

ベース端子を前記第2のトランジスタのベース端子に接続し、コレクタ端子を前記第2の基準電流を流す電流経路に接続し、エミッタ端子を第2の帰還ノード抵抗を介して前記帰還端子に接続した第4のトランジスタ

とを備えることを特徴とする請求項3に記載の電流帰還型電源。 - 前記電流循環回路が、

ベース端子を前記入力ノードに接続し、コレクタ端子を前記正電源側に接続し、エミッタ端子を前記出力端子に接続された出力回路に接続した第1の出力トランジスタと、

該第1の出力トランジスタと電流増幅率が等しく、エミッタ端子を前記出力回路に接続し、コレクタ端子を負電源側に接続し、ベース端子を前記出力ノードに接続した第2の出力トランジスタ

とを備えることを特徴とする請求項3又は4に記載の電流帰還型電源。 - 荷電粒子源と、

前記荷電粒子源から出射した荷電粒子線を集束させる集束レンズ系と、

集束させられた前記荷電粒子線を、照射対象上の所定領域に走査する走査コイルと、

前記照射対象を搭載し、前記照射対象上の所望の位置に前記荷電粒子線が照射されるように移動可能なステージと、

前記走査コイルに走査電流を供給するスイープ電源

とを備え、前記スイープ電源が、走査信号を入力して、前記走査信号を反転した信号を出力する入力部と、入力端子を前記入力部に接続し、帰還端子を前記走査コイルの第1端子に接続し、出力端子を前記走査コイルの第2端子に接続し、前記帰還端子から帰還される帰還電流をゼロにする電流帰還部と、前記第1端子と接地電位間に接続され、前記走査コイルに流れる電流の大きさを段階的に切り替えるゲイン切り替え部とを有し、前記走査信号のパターンに対応した電流を前記走査コイルに流す電流帰還型電源であることを特徴とする荷電粒子線装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009175305A JP5515484B2 (ja) | 2009-07-28 | 2009-07-28 | 電流帰還型電源及び荷電粒子線装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009175305A JP5515484B2 (ja) | 2009-07-28 | 2009-07-28 | 電流帰還型電源及び荷電粒子線装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011029068A true JP2011029068A (ja) | 2011-02-10 |

| JP5515484B2 JP5515484B2 (ja) | 2014-06-11 |

Family

ID=43637579

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009175305A Active JP5515484B2 (ja) | 2009-07-28 | 2009-07-28 | 電流帰還型電源及び荷電粒子線装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5515484B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013042494A (ja) * | 2011-08-11 | 2013-02-28 | Fujitsu Semiconductor Ltd | 電流モード回路の入力インピーダンスを維持するシステム及び方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5769322U (ja) * | 1980-10-15 | 1982-04-26 | ||

| JPH0454458A (ja) * | 1990-06-22 | 1992-02-21 | Hitachi Ltd | 電流検出装置 |

| JP2007150380A (ja) * | 2005-11-24 | 2007-06-14 | Hitachi High-Technologies Corp | 演算増幅器及びそれを用いた走査電子顕微鏡 |

| JP2009224292A (ja) * | 2008-03-19 | 2009-10-01 | Shimadzu Corp | 荷電粒子線走査装置 |

-

2009

- 2009-07-28 JP JP2009175305A patent/JP5515484B2/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5769322U (ja) * | 1980-10-15 | 1982-04-26 | ||

| JPH0454458A (ja) * | 1990-06-22 | 1992-02-21 | Hitachi Ltd | 電流検出装置 |

| JP2007150380A (ja) * | 2005-11-24 | 2007-06-14 | Hitachi High-Technologies Corp | 演算増幅器及びそれを用いた走査電子顕微鏡 |

| JP2009224292A (ja) * | 2008-03-19 | 2009-10-01 | Shimadzu Corp | 荷電粒子線走査装置 |

Non-Patent Citations (1)

| Title |

|---|

| JPN7013001410; Jeffrey Lies, Tamara Papalias and Mike Wong: '「ノイズ・歪みを考えた高速アンプの賢い選択法」' EDN Japan , 200605, p. 85 - 90, リード・ビジネス・インフォメーション株式会社 * |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013042494A (ja) * | 2011-08-11 | 2013-02-28 | Fujitsu Semiconductor Ltd | 電流モード回路の入力インピーダンスを維持するシステム及び方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5515484B2 (ja) | 2014-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006511143A (ja) | バイアス制御を伴う電力増幅器 | |

| JP2017092526A (ja) | 電力増幅回路 | |

| EP0921634A1 (en) | Differential amplifier with adjustable linearity | |

| JP2005101734A (ja) | 高出力増幅回路 | |

| US6362682B2 (en) | Common-mode feedback circuit and method | |

| US4219781A (en) | Transistor amplifier circuit | |

| JP5515484B2 (ja) | 電流帰還型電源及び荷電粒子線装置 | |

| US4356452A (en) | Class A push-pull amplifier with bias controlling circuit | |

| US6577195B2 (en) | Bipolar differential amplifier | |

| TWI297239B (en) | Improved adjustable gain control system and method thereof | |

| US5889433A (en) | Amplifier having a high current efficiency | |

| JP4000003B2 (ja) | 可変利得増幅器 | |

| US20060238235A1 (en) | Switchable current mirror with feedback | |

| KR20030011833A (ko) | 전력 소모가 적은 바이어스 회로를 갖는 ft 배율기 증폭기 | |

| JP3850799B2 (ja) | 可調増幅器に対して指数的な先行歪みを与えるための回路構造 | |

| JPH0350447B2 (ja) | ||

| US4295101A (en) | Class AB push-pull quasi-linear amplifiers | |

| US6831516B2 (en) | Method of forming a variable propagation delay semiconductor device and structure therefor | |

| JPH06177731A (ja) | 電流切換回路 | |

| JPS60248010A (ja) | 複合トランジスタ回路 | |

| JPH0851324A (ja) | バッファアンプ | |

| JP3752029B2 (ja) | ラインレシーバ | |

| JP2006221579A (ja) | 基準電流発生回路 | |

| JP2025015968A (ja) | 温度補償回路 | |

| RU2183380C2 (ru) | Многокаскадный транзисторный усилитель |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111102 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130416 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130614 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130903 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131101 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140304 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140317 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5515484 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |