JP2010258301A - インターポーザ及び半導体装置 - Google Patents

インターポーザ及び半導体装置 Download PDFInfo

- Publication number

- JP2010258301A JP2010258301A JP2009108269A JP2009108269A JP2010258301A JP 2010258301 A JP2010258301 A JP 2010258301A JP 2009108269 A JP2009108269 A JP 2009108269A JP 2009108269 A JP2009108269 A JP 2009108269A JP 2010258301 A JP2010258301 A JP 2010258301A

- Authority

- JP

- Japan

- Prior art keywords

- interposer

- connection terminal

- chip

- wiring board

- chip component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15172—Fan-out arrangement of the internal vias

- H01L2924/15174—Fan-out arrangement of the internal vias in different layers of the multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Landscapes

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

Abstract

【課題】導電パターンを電解めっきによって形成するため、基板の厚さや基板を貫通する貫通導体部の径に制限が存在する従来のインターポーザの課題を解消する。

【解決手段】電子部品の接続端子と配線基板の接続端子とを電気的に接続する基板状のインターポーザ30は、複数のチップ部品32がモールド樹脂34によって一体化されており、チップ部品32には、本体部32a周面に沿って本体部32aよりも低電気抵抗の電極32bが帯状に形成され、チップ部品32の電極32bが電子部品の接続端子と配線基板の接続端子とを電気的に接続できるように、インターポーザ30の両面に露出している。

【選択図】図1

【解決手段】電子部品の接続端子と配線基板の接続端子とを電気的に接続する基板状のインターポーザ30は、複数のチップ部品32がモールド樹脂34によって一体化されており、チップ部品32には、本体部32a周面に沿って本体部32aよりも低電気抵抗の電極32bが帯状に形成され、チップ部品32の電極32bが電子部品の接続端子と配線基板の接続端子とを電気的に接続できるように、インターポーザ30の両面に露出している。

【選択図】図1

Description

本発明はインターポーザ及び半導体装置に関する。

半導体装置には、図6に示す様に、半導体素子100の接続端子と配線基板102の接続端子とをインターポーザ104によって電気的に接続したものがある(例えば、下記特許文献1参照)。

このインターポーザ104には、シリコン基板等の基板を貫通する貫通導体部104aと、貫通導体部104aの両端部にパッド104b、104bとから成る導電パターンが形成されている。かかる導電パターンは、電解めっきによって形成されている。

このインターポーザ104には、シリコン基板等の基板を貫通する貫通導体部104aと、貫通導体部104aの両端部にパッド104b、104bとから成る導電パターンが形成されている。かかる導電パターンは、電解めっきによって形成されている。

図6に示すインターポーザ104を用いることによって、半導体素子100の実装強度等の向上を図ることができる。

しかし、図6に示すインターポーザ104の導電パターンは、電解めっきによって形成しているため、インターポーザ104の厚さや貫通導体部104aの径には制限がある。

つまり、基板を貫通する貫通孔内に電解めっきによってめっき金属を充填して貫通導体部104aを形成する際に、高アスペスト比の貫通孔内には充分にめっき金属を充填できないからである。

そこで、本発明は、導電パターンを電解めっきによって形成するため、基板の厚さや基板を貫通する貫通導体部の径に制限が存在する従来のインターポーザの課題を解消し、基板の厚さや基板を貫通する貫通導体部の径の制限を解消できるインターポーザ及びこのインターポーザを用いた半導体装置を提供することを目的とする。

しかし、図6に示すインターポーザ104の導電パターンは、電解めっきによって形成しているため、インターポーザ104の厚さや貫通導体部104aの径には制限がある。

つまり、基板を貫通する貫通孔内に電解めっきによってめっき金属を充填して貫通導体部104aを形成する際に、高アスペスト比の貫通孔内には充分にめっき金属を充填できないからである。

そこで、本発明は、導電パターンを電解めっきによって形成するため、基板の厚さや基板を貫通する貫通導体部の径に制限が存在する従来のインターポーザの課題を解消し、基板の厚さや基板を貫通する貫通導体部の径の制限を解消できるインターポーザ及びこのインターポーザを用いた半導体装置を提供することを目的とする。

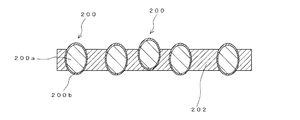

本発明者は、前記課題を解消すべく、先ず、図7に示す様に、インターポーザの貫通導体部を金属コアボール200によって形成することを試みた。金属コアボール200は、銅等の金属から成るボール状のコア部200aの周面をはんだ200bによって覆われているものである。

かかる複数の金属コアボール200,200・・を樹脂モールドによって一体化してインターポーザを形成したところ、図7に示す如く、位置ずれが生じた金属コアボール200が存在した。溶融したモールド樹脂202の流動に伴って、金属コアボール200が移動したものと推察される。この様に、金属コアボール200の位置ずれが生じたインターポーザは、インターポーザとして用いることはできない。

また、金属コアボール200,200・・の各々を、樹脂モールドに先立って所定箇所に位置決めする際に、金属コアボール200を所定箇所に落とし込む貫通孔が形成されたマスク板を用いることを必要とし、煩雑である。

かかる複数の金属コアボール200,200・・を樹脂モールドによって一体化してインターポーザを形成したところ、図7に示す如く、位置ずれが生じた金属コアボール200が存在した。溶融したモールド樹脂202の流動に伴って、金属コアボール200が移動したものと推察される。この様に、金属コアボール200の位置ずれが生じたインターポーザは、インターポーザとして用いることはできない。

また、金属コアボール200,200・・の各々を、樹脂モールドに先立って所定箇所に位置決めする際に、金属コアボール200を所定箇所に落とし込む貫通孔が形成されたマスク板を用いることを必要とし、煩雑である。

本発明者は、金属コアボール200に代えて、四角形状の本体部の両端部を包むように電極が形成されているチップコンデンサを用いて樹脂モールドしたところ、チップコンデンサの電極から成る貫通導体部が所定位置に形成されたインターポーザを容易に得ることができ、前記課題を解消できることを見出した。

すなわち、前記課題を解決するための手段としては、電子部品の接続端子と配線基板の接続端子とを電気的に接続するインターポーザが、複数のチップ部品が樹脂によって一体化された基板状のインターポーザであって、前記チップ部品の本体部の周面に沿って、前記本体部よりも低電気抵抗の電極が、前記インターポーザの一面側と他面側とを電気的に接続するように帯状に形成され、前記チップ部品の電極が、前記電子部品の接続端子と前記配線基板の接続端子とを電気的に接続できるように、前記インターポーザの両面に露出しているインターポーザを提供できる。

また、前記課題を解決するための手段としては、半導体素子の接続端子と配線基板の接続端子とが、前述したインターポーザによって電気的に接続されている半導体装置を提供できる。

すなわち、前記課題を解決するための手段としては、電子部品の接続端子と配線基板の接続端子とを電気的に接続するインターポーザが、複数のチップ部品が樹脂によって一体化された基板状のインターポーザであって、前記チップ部品の本体部の周面に沿って、前記本体部よりも低電気抵抗の電極が、前記インターポーザの一面側と他面側とを電気的に接続するように帯状に形成され、前記チップ部品の電極が、前記電子部品の接続端子と前記配線基板の接続端子とを電気的に接続できるように、前記インターポーザの両面に露出しているインターポーザを提供できる。

また、前記課題を解決するための手段としては、半導体素子の接続端子と配線基板の接続端子とが、前述したインターポーザによって電気的に接続されている半導体装置を提供できる。

本発明者が課題を解決できる手段として提供したインターポーザでは、複数のチップ部品が樹脂によって一体化された基板状のインターポーザを用いる。このチップ部品としては、本体部の両端側の各周面に沿って形成された、本体部よりも低電気抵抗の帯状の電極の各々に、少なくとも二面が互いに対向する平坦面を形成したチップ部品を用いている。

かかるチップ部品の各電極の平坦面の少なくとも一部をインターポーザの表面に露出している。このため、チップ部品の各電極を、インターポーザを貫通する貫通導体部として用いることができる。

その結果、このインターポーザを、電子部品の接続端子と対応する前記配線基板の接続端子との接続を行うことのできるインターポーザとして利用できる。

従って、電解めっきによって貫通導体部を形成することを要しないため、インターポーザの厚さやインターポーザを貫通する貫通導体部の径の制限を解消できる。

また、チップ部品を所定位置に配設する際には、チップマウンタを用いて行うことができ、インターポーザの製造工程の簡素化も図ることができる。

かかるチップ部品の各電極の平坦面の少なくとも一部をインターポーザの表面に露出している。このため、チップ部品の各電極を、インターポーザを貫通する貫通導体部として用いることができる。

その結果、このインターポーザを、電子部品の接続端子と対応する前記配線基板の接続端子との接続を行うことのできるインターポーザとして利用できる。

従って、電解めっきによって貫通導体部を形成することを要しないため、インターポーザの厚さやインターポーザを貫通する貫通導体部の径の制限を解消できる。

また、チップ部品を所定位置に配設する際には、チップマウンタを用いて行うことができ、インターポーザの製造工程の簡素化も図ることができる。

本発明者が課題を解決できる手段として提供した半導体装置の一例を図1に示す。図1に示す半導体装置は、電子部品としての半導体内蔵基板10とマザーボードとしての配線基板20とを、インターポーザ30によって電気的に接続しているものである。

半導体内蔵基板10は、多層配線基板12の一面側に半導体素子14をフリップチップ方式で搭載し、多層配線基板12の他面側に外部接続端子としてのはんだボール16,16・・が設けられている。

また、配線基板20には、多層配線基板22の一面側に、外部接続端子としてのはんだボール24,24・・が設けられている。この多層配線基板22には、半導体内蔵基板10の外周縁近傍に設けられている信号用配線と接続される信号用配線26a、半導体内蔵基板10の中央部近傍に設けられているグランド用配線と接続されるグランド用配線26b、及び半導体内蔵基板10の中央部近傍に設けられている電源用配線と接続される電源用配線26cが形成されている。

半導体内蔵基板10は、多層配線基板12の一面側に半導体素子14をフリップチップ方式で搭載し、多層配線基板12の他面側に外部接続端子としてのはんだボール16,16・・が設けられている。

また、配線基板20には、多層配線基板22の一面側に、外部接続端子としてのはんだボール24,24・・が設けられている。この多層配線基板22には、半導体内蔵基板10の外周縁近傍に設けられている信号用配線と接続される信号用配線26a、半導体内蔵基板10の中央部近傍に設けられているグランド用配線と接続されるグランド用配線26b、及び半導体内蔵基板10の中央部近傍に設けられている電源用配線と接続される電源用配線26cが形成されている。

かかる半導体内蔵基板10と配線基板20とを電気的に接続するインターポーザ30を図2に示す。図2に示すインターポーザ30は、基板状であって、複数のチップ部品32,32・・が、モールド樹脂34,34・・で一体化されている。

図2に示すインターポーザ30では、その両面側の各表面に、チップ部品32,32・・の各本体部32aの両端部に形成された帯状の電極32bの一部が露出している。

かかるチップ部品32は、図3(a)に示す様に、四角形状の本体部32aの両端側の各周面に沿って、本体部32aよりも低電気抵抗値の金属から成る帯状の電極32bが形成されている。電極32bは、図3(b)に示す様に、本体部32aの端面を覆うように形成されている。

この様な、図3に示すチップ部品32の電極32bには、互いに対向する平坦面35,35が形成されており、平坦面35,35の各々がインターポーザ30の両面に露出している。このため、チップ部品32の電極32b,32bの各々は、インターポーザ30を貫通する貫通導体部としての役割を奏する。

図2に示すインターポーザ30では、その両面側の各表面に、チップ部品32,32・・の各本体部32aの両端部に形成された帯状の電極32bの一部が露出している。

かかるチップ部品32は、図3(a)に示す様に、四角形状の本体部32aの両端側の各周面に沿って、本体部32aよりも低電気抵抗値の金属から成る帯状の電極32bが形成されている。電極32bは、図3(b)に示す様に、本体部32aの端面を覆うように形成されている。

この様な、図3に示すチップ部品32の電極32bには、互いに対向する平坦面35,35が形成されており、平坦面35,35の各々がインターポーザ30の両面に露出している。このため、チップ部品32の電極32b,32bの各々は、インターポーザ30を貫通する貫通導体部としての役割を奏する。

チップ部品32としては、本体部32aの両端側の各周面に沿って、本体部32aよりも低電気抵抗の帯状の電極32b,32bが形成されたチップ部品を用いることができる。このため、図4(a)に示す様に、チップコンデンサをチップ部品32として用いることができる。図4(a)に示すチップ部品32は、チタン酸バリウム等の誘電体材料から成る本体部32a内に、電極32b,32bから延出された延出電極32c,32c・・が設けられている。かかる図4(a)に示すチップ部品32は、グランド用配線、電源用配線の接続に好適に用いることができる。

図4(a)に示すチップ部品32に代えて、図4(b)に示す様に、延出電極32c,32c・・を、図4(a)に示すチップ部品32の延出電極32c,32c・・よりも短くしてもよい。

また、図4(a)(b)に示すチップ部品32の本体部32aを、アルミナ等の絶縁性材料によって形成してもよい。かかるチップ部品32は、信号用配線の接続に好適に用いることができる。

図4(a)に示すチップ部品32に代えて、図4(b)に示す様に、延出電極32c,32c・・を、図4(a)に示すチップ部品32の延出電極32c,32c・・よりも短くしてもよい。

また、図4(a)(b)に示すチップ部品32の本体部32aを、アルミナ等の絶縁性材料によって形成してもよい。かかるチップ部品32は、信号用配線の接続に好適に用いることができる。

図3及び図4(a)(b)に示すチップ部品32を用いた図1に示す半導体装置では、半導体内蔵基板10のはんだボール16,16・・の各々と配線基板20の外部接続端子としてのはんだボール24とがチップ部品32の帯状の電極32bによって接続されて、半導体内蔵基板10のはんだボール16から配線基板20のはんだボール24に至る複数の配線が形成される。かかる複数の配線は、配線を形成する金属よりも高抵抗の材料を介して互いに離間されている。

図3及び図4(a)(b)に示すチップ部品32の様に、電極32b,32bを形成する金属よりも高抵抗の材料を介して互いに離間されているチップ部品に代えて、図4(c)に示す様に、チップ抵抗器を用いることができる。図4(c)に示すチップ部品32は、絶縁性材料から成る本体部32aに電極32b,32bを接続する抵抗体が設けられているものである。この抵抗体は、電極32b,32bを形成する金属よりも高抵抗の材料によって形成されている。

その他に、チップ部品32として、チップインダクタを用いることができる。

図3及び図4(a)(b)に示すチップ部品32の様に、電極32b,32bを形成する金属よりも高抵抗の材料を介して互いに離間されているチップ部品に代えて、図4(c)に示す様に、チップ抵抗器を用いることができる。図4(c)に示すチップ部品32は、絶縁性材料から成る本体部32aに電極32b,32bを接続する抵抗体が設けられているものである。この抵抗体は、電極32b,32bを形成する金属よりも高抵抗の材料によって形成されている。

その他に、チップ部品32として、チップインダクタを用いることができる。

図3及び図4に示す四角形状のチップ部品32を用いてインターポーザ30を製造するには、図5(a)に示す様に、支持板50の一面側に設置した熱剥離シート52上の所定箇所に、チップ部品32,32・・を配設する。このチップ部品32,32・・の配設は、チップマウンターを用いて行うことができる。

次いで、チップ部品32,32・・を、図5(b)に示す様に、モールド樹脂34によって樹脂モールドする。この際に、四角形状のチップ部品32は、その平坦面と支持板50の一面側との接触面積が大きいため、溶融したモールド樹脂の流動によって移動せず、当初の配設位置で一体化できる。

更に、モールド樹脂34にブラスト加工を施して、図5(c)に示す様に、チップ部品32,32・・の各平坦面35を露出することによって、チップ部品32,32の間がモールド樹脂に充填されている基板状のインターポーザ30を得ることができる。

その後、所定温度に加熱して、熱剥離シート52からインターポーザ30を剥離して、図2に示すインターポーザ30を得ることができる。

次いで、チップ部品32,32・・を、図5(b)に示す様に、モールド樹脂34によって樹脂モールドする。この際に、四角形状のチップ部品32は、その平坦面と支持板50の一面側との接触面積が大きいため、溶融したモールド樹脂の流動によって移動せず、当初の配設位置で一体化できる。

更に、モールド樹脂34にブラスト加工を施して、図5(c)に示す様に、チップ部品32,32・・の各平坦面35を露出することによって、チップ部品32,32の間がモールド樹脂に充填されている基板状のインターポーザ30を得ることができる。

その後、所定温度に加熱して、熱剥離シート52からインターポーザ30を剥離して、図2に示すインターポーザ30を得ることができる。

以上、説明してきた図1では、電子部品として、半導体素子を内蔵する半導体内蔵基板10を用いているが、電子部品として、半導体素子、受動部品、受動部品を内蔵する内蔵基板、半導体素子及び受動部品を内蔵する内蔵基板を用いることができる。

これまで、説明してきたインターポーザ30では、チップ部品32の電極32b,32bの平坦面の全面を露出しているが、平坦面の一部を露出するようにしてもよい。

また、チップ部品32は、本体部32aも四角形状であったが、本体部32aは円筒状であってもよい。

更に、チップ部品32の電極32b,32bは、少なくとも二面が互いに対向する平坦面に形成されていればよく、その横断面形状が四角形状でなくてもよい。また、電極32b,32bは、本体部32aの両端側の各周面に沿って帯状の電極が形成されていればよく、本体部32aの両端面に電極が形成されておらず、本体部32aの端面が露出していてもよい。

これまで、説明してきたインターポーザ30では、チップ部品32の電極32b,32bの平坦面の全面を露出しているが、平坦面の一部を露出するようにしてもよい。

また、チップ部品32は、本体部32aも四角形状であったが、本体部32aは円筒状であってもよい。

更に、チップ部品32の電極32b,32bは、少なくとも二面が互いに対向する平坦面に形成されていればよく、その横断面形状が四角形状でなくてもよい。また、電極32b,32bは、本体部32aの両端側の各周面に沿って帯状の電極が形成されていればよく、本体部32aの両端面に電極が形成されておらず、本体部32aの端面が露出していてもよい。

10 半導体内蔵基板

20 配線基板

30 インターポーザ

32 チップ部品

32a 本体部

32b 電極

34 モールド樹脂

35 電極32bの平坦面

20 配線基板

30 インターポーザ

32 チップ部品

32a 本体部

32b 電極

34 モールド樹脂

35 電極32bの平坦面

Claims (7)

- 電子部品の接続端子と配線基板の接続端子とを電気的に接続するインターポーザが、複数のチップ部品が樹脂によって一体化された基板状のインターポーザであって、

前記チップ部品の本体部の周面に沿って、前記本体部よりも低電気抵抗の電極が、前記インターポーザの一面側と他面側とを電気的に接続するように帯状に形成され、

前記チップ部品の電極が、前記電子部品の接続端子と前記配線基板の接続端子とを電気的に接続できるように、前記インターポーザの両面に露出していることを特徴とするインターポーザ。 - チップ部品が、四角形状の本体部の両端側の各周面に沿って金属から成る複数の帯状の電極が形成されているチップ部品である請求項1記載のインターポーザ。

- 電子部品に形成された複数の接続端子の各々と配線基板の接続端子とが前記電極によって接続されて形成される複数の配線は、互いに前記配線を形成する金属よりも高抵抗の材料を介して互いに離間されている請求項1又は請求項2記載のインターポーザ。

- 樹脂が、モールド樹脂であって、チップ部品間に充填されている請求項1〜3のいずれか一項記載のインターポーザ。

- チップ部品が、チップコンデンサ、チップ抵抗器又はチップインダクタである請求項1〜4のいずれか一項記載のインターポーザ。

- 半導体素子の接続端子と配線基板の接続端子とが、請求項1〜5のいずれか一項記載のインターポーザによって電気的に接続されていることを特徴とする半導体装置。

- 配線基板が、インターポーザのチップ部品の帯状の電極と接続される接続端子と反対側面に複数の外部接続端子が設けられた配線基板であって、電子部品に形成された複数の接続端子の各々と前記配線基板の接続端子とがチップ部品の帯状の電極によって接続されて形成される、前記電子部品の接続端子から前記配線基板の外部接続端子に至る複数の配線が、互いに前記配線を形成する金属よりも高抵抗の材料を介して互いに離間されている請求項6記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009108269A JP2010258301A (ja) | 2009-04-27 | 2009-04-27 | インターポーザ及び半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009108269A JP2010258301A (ja) | 2009-04-27 | 2009-04-27 | インターポーザ及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010258301A true JP2010258301A (ja) | 2010-11-11 |

| JP2010258301A5 JP2010258301A5 (ja) | 2012-04-12 |

Family

ID=43318855

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009108269A Pending JP2010258301A (ja) | 2009-04-27 | 2009-04-27 | インターポーザ及び半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010258301A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014212183A (ja) * | 2013-04-18 | 2014-11-13 | 大日本印刷株式会社 | 貫通電極基板の製造方法、貫通電極基板、および半導体装置 |

| US10806033B2 (en) | 2017-10-03 | 2020-10-13 | Murata Manufacturing Co., Ltd. | Interposer and electronic device |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03501426A (ja) * | 1988-08-01 | 1991-03-28 | サーキット・コンポーネンツ・インコーポレイテッド | 高誘電率の軟質シート材料 |

| JPH1074668A (ja) * | 1996-08-30 | 1998-03-17 | Rohm Co Ltd | アレイ型固体電解コンデンサの構造及びその製造方法 |

| JP2001352004A (ja) * | 2000-06-09 | 2001-12-21 | Fujitsu Ltd | 回路基板及びその製造方法並びに半導体装置 |

| JP2005150490A (ja) * | 2003-11-18 | 2005-06-09 | Canon Inc | Icとプリント配線基板間のシート部品 |

| JP2005236008A (ja) * | 2004-02-19 | 2005-09-02 | Fujitsu Ltd | コンデンサシート |

| JP2009049087A (ja) * | 2007-08-16 | 2009-03-05 | Panasonic Corp | 電子部品と電子部品の製造方法 |

-

2009

- 2009-04-27 JP JP2009108269A patent/JP2010258301A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03501426A (ja) * | 1988-08-01 | 1991-03-28 | サーキット・コンポーネンツ・インコーポレイテッド | 高誘電率の軟質シート材料 |

| JPH1074668A (ja) * | 1996-08-30 | 1998-03-17 | Rohm Co Ltd | アレイ型固体電解コンデンサの構造及びその製造方法 |

| JP2001352004A (ja) * | 2000-06-09 | 2001-12-21 | Fujitsu Ltd | 回路基板及びその製造方法並びに半導体装置 |

| JP2005150490A (ja) * | 2003-11-18 | 2005-06-09 | Canon Inc | Icとプリント配線基板間のシート部品 |

| JP2005236008A (ja) * | 2004-02-19 | 2005-09-02 | Fujitsu Ltd | コンデンサシート |

| JP2009049087A (ja) * | 2007-08-16 | 2009-03-05 | Panasonic Corp | 電子部品と電子部品の製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014212183A (ja) * | 2013-04-18 | 2014-11-13 | 大日本印刷株式会社 | 貫通電極基板の製造方法、貫通電極基板、および半導体装置 |

| US10806033B2 (en) | 2017-10-03 | 2020-10-13 | Murata Manufacturing Co., Ltd. | Interposer and electronic device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9578745B2 (en) | Printed wiring board, method for manufacturing printed wiring board and package-on-package | |

| US9693458B2 (en) | Printed wiring board, method for manufacturing printed wiring board and package-on-package | |

| US7790270B2 (en) | Wiring board and semiconductor device | |

| KR101420514B1 (ko) | 전자부품들이 구비된 기판구조 및 전자부품들이 구비된 기판구조의 제조방법 | |

| KR20090012664A (ko) | 금속 베이스 패키지 기판과 이를 이용한 3차원 다층 패키지모듈 및 그 제조방법 | |

| CN104064514A (zh) | 半导体器件制造方法以及半导体安装基板 | |

| TWI498056B (zh) | 具有內埋元件的電路板、其製作方法及封裝結構 | |

| TWI466611B (zh) | 晶片封裝結構、具有內埋元件的電路板及其製作方法 | |

| JP5093104B2 (ja) | 受動部品内蔵インターポーザ | |

| KR101565690B1 (ko) | 회로기판, 회로기판 제조방법, 전자부품 패키지 및 전자부품 패키지 제조방법 | |

| US9894790B2 (en) | Electronic component module and manufacturing method thereof | |

| JP2017084886A (ja) | 配線基板およびこれを用いた半導体素子の実装構造。 | |

| JP2010272563A (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| JP2010258301A (ja) | インターポーザ及び半導体装置 | |

| KR20160138754A (ko) | 인쇄회로기판, 반도체 패키지 및 그 제조방법 | |

| JP2007027472A5 (ja) | ||

| JP2010258301A5 (ja) | ||

| KR102536256B1 (ko) | 임베디드 인쇄회로기판 | |

| JP2004303944A (ja) | モジュール基板及びその製造方法 | |

| JP5601413B2 (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| US9107296B2 (en) | Thermo/electrical conductor arrangement for multilayer printed circuit boards | |

| KR100679816B1 (ko) | 반도체 패키지 | |

| KR102426111B1 (ko) | 임베디드 인쇄회로기판 | |

| KR100661653B1 (ko) | 기판조립체 | |

| JP2015159160A (ja) | 配線基板及び接続構造 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120229 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120229 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130702 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140408 |