JP2010087185A - シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置 - Google Patents

シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置 Download PDFInfo

- Publication number

- JP2010087185A JP2010087185A JP2008253931A JP2008253931A JP2010087185A JP 2010087185 A JP2010087185 A JP 2010087185A JP 2008253931 A JP2008253931 A JP 2008253931A JP 2008253931 A JP2008253931 A JP 2008253931A JP 2010087185 A JP2010087185 A JP 2010087185A

- Authority

- JP

- Japan

- Prior art keywords

- plasma

- processing

- oxide film

- silicon oxide

- range

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000012545 processing Methods 0.000 title claims abstract description 148

- 230000003647 oxidation Effects 0.000 title claims abstract description 76

- 238000007254 oxidation reaction Methods 0.000 title claims abstract description 76

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 title claims abstract description 72

- 229910052814 silicon oxide Inorganic materials 0.000 title claims abstract description 66

- 238000000034 method Methods 0.000 title claims description 72

- 238000003860 storage Methods 0.000 title claims description 12

- 239000007789 gas Substances 0.000 claims abstract description 87

- 239000001301 oxygen Substances 0.000 claims abstract description 50

- 229910052760 oxygen Inorganic materials 0.000 claims abstract description 50

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims abstract description 49

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 29

- 239000010703 silicon Substances 0.000 claims abstract description 29

- 230000008569 process Effects 0.000 claims description 40

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 28

- 230000007246 mechanism Effects 0.000 claims description 20

- 230000001590 oxidative effect Effects 0.000 claims description 3

- 239000011148 porous material Substances 0.000 abstract 1

- 235000012431 wafers Nutrition 0.000 description 37

- 239000000758 substrate Substances 0.000 description 17

- 239000004065 semiconductor Substances 0.000 description 15

- 230000005855 radiation Effects 0.000 description 14

- 239000000463 material Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 230000005540 biological transmission Effects 0.000 description 11

- 150000002500 ions Chemical class 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- 229910004298 SiO 2 Inorganic materials 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 239000011261 inert gas Substances 0.000 description 7

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 6

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 6

- 239000010453 quartz Substances 0.000 description 6

- 239000004020 conductor Substances 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- 230000007547 defect Effects 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 3

- 239000000498 cooling water Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- -1 for example Substances 0.000 description 3

- 230000000644 propagated effect Effects 0.000 description 3

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- 229910018557 Si O Inorganic materials 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 229910001882 dioxygen Inorganic materials 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Inorganic materials [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 230000035882 stress Effects 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910004541 SiN Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 230000005672 electromagnetic field Effects 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical group [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229960001730 nitrous oxide Drugs 0.000 description 1

- 235000013842 nitrous oxide Nutrition 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 1

- 239000004810 polytetrafluoroethylene Substances 0.000 description 1

- 230000001902 propagating effect Effects 0.000 description 1

- 238000010926 purge Methods 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000009279 wet oxidation reaction Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/316—Inorganic layers composed of oxides or glassy oxides or oxide based glass

- H01L21/3165—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation

- H01L21/31654—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation of semiconductor materials, e.g. the body itself

- H01L21/31658—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation of semiconductor materials, e.g. the body itself by thermal oxidation, e.g. of SiGe

- H01L21/31662—Inorganic layers composed of oxides or glassy oxides or oxide based glass formed by oxidation of semiconductor materials, e.g. the body itself by thermal oxidation, e.g. of SiGe of silicon in uncombined form

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32192—Microwave generated discharge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/3244—Gas supply means

- H01J37/32449—Gas control, e.g. control of the gas flow

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02236—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02236—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor

- H01L21/02238—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor silicon in uncombined form, i.e. pure silicon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/02252—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by plasma treatment, e.g. plasma oxidation of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28211—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation in a gaseous ambient using an oxygen or a water vapour, e.g. RTO, possibly through a layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40117—Multistep manufacturing processes for data storage electrodes the electrodes comprising a charge-trapping insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/518—Insulating materials associated therewith the insulating material containing nitrogen, e.g. nitride, oxynitride, nitrogen-doped material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

- H01L29/7881—Programmable transistors with only two possible levels of programmation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/792—Field effect transistors with field effect produced by an insulated gate with charge trapping gate insulator, e.g. MNOS-memory transistors

Abstract

【解決手段】 複数の孔を有する平面アンテナ31により処理容器1にマイクロ波を導入するプラズマ酸化処理装置100において、処理ガス中の酸素の割合を0.1%以上10%以下の範囲内、処理容器1内の圧力を1.3Pa以上266.Pa以下の範囲内に設定し、高周波電源44から、ウエハWを載置する載置台2の電極にウエハWの面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給し、ウエハWにRFバイアスを印加しながら、ウエハWのシリコンに対してプラズマ酸化処理を行う。

【選択図】図1

Description

前記処理ガス中の酸素の割合が0.1%以上10%以下の範囲内であり、かつ前記処理容器内の圧力が1.3Pa以上266.6Pa以下の範囲内の条件で前記プラズマを生成させるとともに、前記処理容器内において被処理体を載置する載置台に被処理体の面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給して被処理体にバイアスを印加しながらシリコンを酸化することを特徴とする。

前記制御プログラムは、実行時に、プラズマ処理装置の処理容器内で、被処理体の表面に露出したシリコンに酸素を含有する処理ガスのプラズマを作用させてシリコン酸化膜を形成する処理において、前記処理ガス中の酸素の割合が0.1%以上10%以下の範囲内であり、かつ前記処理容器内の圧力が1.3Pa以上266.6Pa以下の範囲内の条件で前記プラズマを生成させるとともに、前記処理容器内において被処理体を載置する載置台に被処理体の面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給して被処理体にバイアスを印加するように、コンピュータに前記プラズマ処理装置を制御させるものであることを特徴とする。

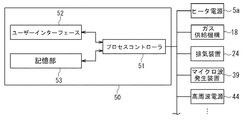

前記処理容器の前記開口を塞ぐ誘電体部材と、

前記誘電体部材の外側に設けられ、前記処理容器内に電磁波を導入するためのアンテナと、

前記処理容器内に酸素を含有する処理ガスを供給するガス供給機構と、

前記処理容器内を減圧排気する排気機構と、

前記処理容器内で被処理体を載置する載置台と、

前記載置台に接続された高周波電源と、

前記処理容器内で、被処理体の表面に露出したシリコンに前記処理ガスのプラズマを作用させてシリコン酸化膜を形成する処理において、前記処理ガス中の酸素の割合が0.1%以上10%以下の範囲内であり、かつ前記処理容器内の圧力が1.3Pa以上266.6Pa以下の範囲内の条件で前記プラズマを生成させるとともに、前記処理容器内において被処理体を載置する載置台に被処理体の面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給して被処理体にバイアスを印加するように制御する制御部と、

を備えたことを特徴とする。

ここで、プラズマ酸化処理装置100において行なわれるプラズマ酸化処理の好ましい条件について説明を行う。処理ガスとしては、希ガスとしてArガスを、酸素含有ガスとしてO2ガスをそれぞれ使用することが好ましい。このとき、処理ガス中に含まれるO2ガスの流量比率(体積比率)は、高密度なイオンを生成させてシリコン酸化膜の表面およびSi/SiO2界面を平坦化する観点から、0.1%以上10%以下の範囲内が好ましく、0.5%以上2%以下の範囲内がより好ましい。

処理圧力;133.3Pa

Arガス流量;990mL/min(sccm)

O2ガス流量;10mL/min(sccm)

高周波電力の周波数:13.56MHz

高周波電力のパワー:600W(パワー密度0.849W/cm2)

マイクロ波の周波数:2.45GHz

マイクロ波パワー:4000W(パワー密度2.05W/cm2)

処理温度:465℃

目標膜厚:8nm(456秒)

ウエハ径:300mm

<条件2>

処理圧力;667Pa

Arガス流量;1200mL/min(sccm)

O2ガス流量;388mL/min(sccm)

H2ガス流量;12mL/min(sccm)

高周波電力の周波数:13.56MHz

高周波電力のパワー:600W(パワー密度0.849W/cm2)

マイクロ波の周波数:2.45GHz

マイクロ波パワー:4000W(パワー密度2.05W/cm2)

処理温度:465℃

目標膜厚:8nm(405秒)

ウエハ径:300mm

Claims (7)

- プラズマ処理装置の処理容器内で、被処理体の表面に露出したシリコンに酸素を含有する処理ガスのプラズマを作用させて酸化処理を施し、シリコン酸化膜を形成するシリコン酸化膜の形成方法であって、

前記処理ガス中の酸素の割合が0.1%以上10%以下の範囲内であり、かつ前記処理容器内の圧力が1.3Pa以上266.6Pa以下の範囲内の条件で前記プラズマを生成させるとともに、前記処理容器内において被処理体を載置する載置台に被処理体の面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給して被処理体にバイアスを印加しながらシリコンを酸化することを特徴とするシリコン酸化膜の形成方法。 - 前記高周波電力の周波数は、400kHz以上60MHz以下の範囲内であることを特徴とする請求項1に記載のシリコン酸化膜の形成方法。

- 処理温度が室温以上600℃以下の範囲内であることを特徴とする請求項1または請求項2に記載のシリコン酸化膜の形成方法。

- 前記プラズマは、前記処理ガスと、複数のスロットを有する平面アンテナにより前記処理容器内に導入されるマイクロ波と、によって形成されるマイクロ波励起プラズマであることを特徴とする請求項1から請求項3のいずれか1項に記載のシリコン酸化膜の形成方法。

- 前記マイクロ波のパワー密度が、被処理体の面積あたり0.255W/cm2以上2.55W/cm2以下の範囲内であることを特徴とする請求項4に記載のシリコン酸化膜の形成方法。

- コンピュータ上で動作する制御プログラムが記憶されたコンピュータ読み取り可能な記憶媒体であって、

前記制御プログラムは、実行時に、プラズマ処理装置の処理容器内で、被処理体の表面に露出したシリコンに酸素を含有する処理ガスのプラズマを作用させてシリコン酸化膜を形成する処理において、前記処理ガス中の酸素の割合が0.1%以上10%以下の範囲内であり、かつ前記処理容器内の圧力が1.3Pa以上266.6Pa以下の範囲内の条件で前記プラズマを生成させるとともに、前記処理容器内において被処理体を載置する載置台に被処理体の面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給して被処理体にバイアスを印加するように、コンピュータに前記プラズマ処理装置を制御させるものであることを特徴とするコンピュータ読み取り可能な記憶媒体。 - プラズマを用いて被処理体を処理する上部が開口した処理容器と、

前記処理容器の前記開口を塞ぐ誘電体部材と、

前記誘電体部材の外側に設けられ、前記処理容器内に電磁波を導入するためのアンテナと、

前記処理容器内に酸素を含有する処理ガスを供給するガス供給機構と、

前記処理容器内を減圧排気する排気機構と、

前記処理容器内で被処理体を載置する載置台と、

前記載置台に接続された高周波電源と、

前記処理容器内で、被処理体の表面に露出したシリコンに前記処理ガスのプラズマを作用させてシリコン酸化膜を形成する処理において、前記処理ガス中の酸素の割合が0.1%以上10%以下の範囲内であり、かつ前記処理容器内の圧力が1.3Pa以上266.6Pa以下の範囲内の条件で前記プラズマを生成させるとともに、前記処理容器内において被処理体を載置する載置台に被処理体の面積当り0.14W/cm2以上2.13W/cm2以下の範囲内の出力で高周波電力を供給して被処理体にバイアスを印加するように制御する制御部と、

を備えたことを特徴とするプラズマ酸化処理装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008253931A JP5357487B2 (ja) | 2008-09-30 | 2008-09-30 | シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置 |

| KR1020117007367A KR101255905B1 (ko) | 2008-09-30 | 2009-09-25 | 실리콘 산화막의 형성 방법 및 장치 |

| CN2009801373923A CN102165568B (zh) | 2008-09-30 | 2009-09-25 | 硅氧化膜的形成方法和装置 |

| PCT/JP2009/066588 WO2010038654A1 (ja) | 2008-09-30 | 2009-09-25 | シリコン酸化膜の形成方法及び装置 |

| TW098132716A TWI482220B (zh) | 2008-09-30 | 2009-09-28 | Method and device for forming silicon oxide film |

| US13/074,062 US8389420B2 (en) | 2008-09-30 | 2011-03-29 | Method and apparatus for forming silicon oxide film |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008253931A JP5357487B2 (ja) | 2008-09-30 | 2008-09-30 | シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010087185A true JP2010087185A (ja) | 2010-04-15 |

| JP5357487B2 JP5357487B2 (ja) | 2013-12-04 |

Family

ID=42073418

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008253931A Active JP5357487B2 (ja) | 2008-09-30 | 2008-09-30 | シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8389420B2 (ja) |

| JP (1) | JP5357487B2 (ja) |

| KR (1) | KR101255905B1 (ja) |

| CN (1) | CN102165568B (ja) |

| TW (1) | TWI482220B (ja) |

| WO (1) | WO2010038654A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016530719A (ja) * | 2013-08-12 | 2016-09-29 | マイクロン テクノロジー, インク. | 半導体構造および半導体構造の製造方法 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5567392B2 (ja) * | 2010-05-25 | 2014-08-06 | 東京エレクトロン株式会社 | プラズマ処理装置 |

| JP2014194921A (ja) * | 2013-03-01 | 2014-10-09 | Tokyo Electron Ltd | マイクロ波処理装置及びマイクロ波処理方法 |

| CN103855035A (zh) * | 2014-03-27 | 2014-06-11 | 上海华力微电子有限公司 | 一种制备栅介质层的设备 |

| US10818804B2 (en) | 2015-10-28 | 2020-10-27 | Taiwan Semiconductor Manufacturing Co., Ltd. | Floating gate isolation and method for manufacturing the same |

| CN112447472B (zh) * | 2019-08-27 | 2023-03-07 | 中微半导体设备(上海)股份有限公司 | 改善气体均一分布的等离子体反应装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0729898A (ja) * | 1993-07-15 | 1995-01-31 | Tadahiro Omi | 半導体製造方法 |

| JP2003282567A (ja) * | 2002-03-26 | 2003-10-03 | Hitachi Kokusai Electric Inc | 半導体装置の製造方法及び半導体装置 |

| WO2006129643A1 (ja) * | 2005-05-31 | 2006-12-07 | Tokyo Electron Limited | プラズマ処理装置およびプラズマ処理方法 |

| JP2008251855A (ja) * | 2007-03-30 | 2008-10-16 | Tokyo Electron Ltd | シリコン酸化膜の形成方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6228751B1 (en) * | 1995-09-08 | 2001-05-08 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device |

| TWI235433B (en) | 2002-07-17 | 2005-07-01 | Tokyo Electron Ltd | Oxide film forming method, oxide film forming apparatus and electronic device material |

| TW200511430A (en) * | 2003-05-29 | 2005-03-16 | Tokyo Electron Ltd | Plasma processing apparatus and plasma processing method |

| JP5089121B2 (ja) | 2006-09-29 | 2012-12-05 | 東京エレクトロン株式会社 | シリコン酸化膜の形成方法およびプラズマ処理装置 |

| US7910495B2 (en) * | 2006-09-29 | 2011-03-22 | Tokyo Electron Limited | Plasma oxidizing method, plasma processing apparatus, and storage medium |

| JP2008124424A (ja) * | 2006-10-16 | 2008-05-29 | Tokyo Electron Ltd | プラズマ成膜装置及びプラズマ成膜方法 |

-

2008

- 2008-09-30 JP JP2008253931A patent/JP5357487B2/ja active Active

-

2009

- 2009-09-25 WO PCT/JP2009/066588 patent/WO2010038654A1/ja active Application Filing

- 2009-09-25 KR KR1020117007367A patent/KR101255905B1/ko active IP Right Grant

- 2009-09-25 CN CN2009801373923A patent/CN102165568B/zh active Active

- 2009-09-28 TW TW098132716A patent/TWI482220B/zh active

-

2011

- 2011-03-29 US US13/074,062 patent/US8389420B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0729898A (ja) * | 1993-07-15 | 1995-01-31 | Tadahiro Omi | 半導体製造方法 |

| JP2003282567A (ja) * | 2002-03-26 | 2003-10-03 | Hitachi Kokusai Electric Inc | 半導体装置の製造方法及び半導体装置 |

| WO2006129643A1 (ja) * | 2005-05-31 | 2006-12-07 | Tokyo Electron Limited | プラズマ処理装置およびプラズマ処理方法 |

| JP2008251855A (ja) * | 2007-03-30 | 2008-10-16 | Tokyo Electron Ltd | シリコン酸化膜の形成方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016530719A (ja) * | 2013-08-12 | 2016-09-29 | マイクロン テクノロジー, インク. | 半導体構造および半導体構造の製造方法 |

| US10103160B2 (en) | 2013-08-12 | 2018-10-16 | Micron Technology, Inc. | Semiconductor structures including dielectric materials having differing removal rates |

| US11063059B2 (en) | 2013-08-12 | 2021-07-13 | Micron Technology, Inc. | Semiconductor structures including dielectric materials having differing removal rates |

| US11889693B2 (en) | 2013-08-12 | 2024-01-30 | Micron Technology, Inc. | Semiconductor devices including stack oxide materials having different densities or different oxide portions, and semiconductor devices including stack dielectric materials having different portions |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2010038654A1 (ja) | 2010-04-08 |

| TW201030846A (en) | 2010-08-16 |

| JP5357487B2 (ja) | 2013-12-04 |

| CN102165568A (zh) | 2011-08-24 |

| KR101255905B1 (ko) | 2013-04-17 |

| US20110171835A1 (en) | 2011-07-14 |

| CN102165568B (zh) | 2013-06-05 |

| TWI482220B (zh) | 2015-04-21 |

| US8389420B2 (en) | 2013-03-05 |

| KR20110055707A (ko) | 2011-05-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5073482B2 (ja) | シリコン酸化膜の製造方法、その制御プログラム、記憶媒体及びプラズマ処理装置 | |

| JP5138261B2 (ja) | シリコン酸化膜の形成方法、プラズマ処理装置および記憶媒体 | |

| JP4979575B2 (ja) | 基板の窒化処理方法および絶縁膜の形成方法 | |

| TWI402912B (zh) | Manufacturing method of insulating film and manufacturing method of semiconductor device | |

| WO2011040455A1 (ja) | 選択的プラズマ窒化処理方法及びプラズマ窒化処理装置 | |

| JP5231233B2 (ja) | プラズマ酸化処理方法、プラズマ処理装置、及び、記憶媒体 | |

| WO2011114961A1 (ja) | シリコン酸化膜の形成方法、及びプラズマ酸化処理装置 | |

| JP4979389B2 (ja) | プラズマ処理装置 | |

| JP2007042951A (ja) | プラズマ処理装置 | |

| TW201812073A (zh) | 氮化矽膜之處理方法及氮化矽膜之形成方法 | |

| JP5390379B2 (ja) | プラズマ窒化処理におけるチャンバ内の前処理方法、プラズマ処理方法、および記憶媒体 | |

| US20110017586A1 (en) | Method for forming silicon oxide film, storage medium, and plasma processing apparatus | |

| WO2006025363A1 (ja) | シリコン酸化膜の形成方法、半導体装置の製造方法およびコンピュータ記憶媒体 | |

| JP5096047B2 (ja) | マイクロ波プラズマ処理装置およびマイクロ波透過板 | |

| JP5357487B2 (ja) | シリコン酸化膜の形成方法、コンピュータ読み取り可能な記憶媒体およびプラズマ酸化処理装置 | |

| JP5231232B2 (ja) | プラズマ酸化処理方法、プラズマ処理装置、及び、記憶媒体 | |

| JP5271702B2 (ja) | シリコン酸化膜の形成方法およびシリコン酸化膜の形成装置 | |

| JP5291467B2 (ja) | プラズマ酸化処理方法、記憶媒体、及び、プラズマ処理装置 | |

| JP2013033979A (ja) | マイクロ波プラズマ処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20110801 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130604 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130731 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130820 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130830 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5357487 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |