JP2010073773A - 半導体集積回路装置の製造方法 - Google Patents

半導体集積回路装置の製造方法 Download PDFInfo

- Publication number

- JP2010073773A JP2010073773A JP2008237544A JP2008237544A JP2010073773A JP 2010073773 A JP2010073773 A JP 2010073773A JP 2008237544 A JP2008237544 A JP 2008237544A JP 2008237544 A JP2008237544 A JP 2008237544A JP 2010073773 A JP2010073773 A JP 2010073773A

- Authority

- JP

- Japan

- Prior art keywords

- film

- integrated circuit

- semiconductor integrated

- circuit device

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Formation Of Insulating Films (AREA)

- Chemical Vapour Deposition (AREA)

- Element Separation (AREA)

Abstract

【解決手段】本願発明は、近接したトレンチ配列部分をHDP−CVDによる酸化シリコン系の埋め込み絶縁膜によって埋め込む際に、成膜ステップとエッチング・ガスを含むガス雰囲気中でのエッチングを交互に繰り返すことによって、平坦な埋め込み特性を得ることができる。

【選択図】図23

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

(a)ウエハの第1の主面上の窒化シリコンを主要な成分とする膜パターンをマスクとして、前記ウエハの前記第1の主面側にSTI用の素子分離溝を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記素子分離溝を満たし、前記膜パターンを覆うように、酸化シリコン膜系の第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記HDP−CVD装置の前記処理チャンバ内のエッチング・ガスを含む気相エッチング雰囲気中で、前記第1の絶縁膜に対してプラズマ・エッチング処理を実行する工程;

(d)前記工程(c)の後、前記膜パターンを覆う前記第1の絶縁膜をCMP処理により、除去する工程。

(e)前記工程(c)と(d)の間において、前記工程(b)から(c)を、1回以上の所定の繰り返し回数だけ繰り返す工程。

(f)前記工程(a)と(b)の間に、前記HDP−CVD装置の前記処理チャンバ内において、前記第1のHDP−CVD処理よりもスパッタ/成膜比が大きい第2のHDP−CVD処理により、前記素子分離溝の内面および前記膜パターンを覆うように、酸化シリコン膜系の第2の絶縁膜を形成する工程。

(a)ウエハの第1の主面上の窒化シリコンを主要な成分とする膜パターンをマスクとして、前記ウエハの前記第1の主面側にSTI用の素子分離溝を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記素子分離溝を満たし、前記膜パターンを覆うように、酸化シリコン膜系の第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記膜パターンを覆う前記第1の絶縁膜をCMP処理により、除去する工程;

(d)前記工程(a)と(b)の間に、前記HDP−CVD装置の前記処理チャンバ内において、前記第1のHDP−CVD処理よりもスパッタ/成膜比が大きい第2のHDP−CVD処理により、前記素子分離溝の内面および前記膜パターンを覆うように、酸化シリコン膜系の第2の絶縁膜を形成する工程。

(a)ウエハの第1の主面上の窒化シリコンを主要な成分とする膜パターンをマスクとして、前記ウエハの前記第1の主面側にSTI用の素子分離溝を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記素子分離溝を満たし、前記膜パターンを覆うように、酸化シリコン膜系の第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記HDP−CVD装置の前記処理チャンバ内の気相エッチング雰囲気中で、前記第1の絶縁膜に対してエッチングを施す工程;

(d)前記工程(c)の後、前記膜パターンを覆う前記第1の絶縁膜をCMP処理により、除去する工程;

(e)前記工程(c)と(d)の間において、前記工程(b)から(c)を、1回以上の所定の繰り返し回数だけ繰り返す工程。

(a)ウエハの第1の主面上に凸部および凹部を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記凹部を満たし、前記凸部を覆うように、第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記HDP−CVD装置の前記処理チャンバ内のエッチング・ガスを含む気相エッチング雰囲気中で、前記第1の絶縁膜に対してプラズマ・エッチング処理を実行する工程;

(d)前記工程(c)の後、前記凸部を覆う前記第1の絶縁膜をCMP処理により、除去する工程。

(e)前記工程(c)と(d)の間において、前記工程(b)から(c)を、1回以上の所定の繰り返し回数だけ繰り返す工程。

(a)ウエハの第1の主面上に凸部および凹部を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記凹部を満たし、前記凸部を覆うように、第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記第1の絶縁膜をエッチング・ガスを含む気相エッチング雰囲気中で、プラズマ・エッチング処理を実行する工程。

(e)前記工程(c)の後、前記工程(b)から(c)を、1回以上の所定の繰り返し回数だけ繰り返す工程。

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

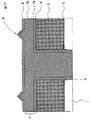

図1は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(ウエハ準備工程)である。図2は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(表面酸化工程)である。図3は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(窒化シリコン膜成膜工程)である。図4は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(トレンチ形成用レジスト塗布・パターニング工程)である。図5は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(トレンチ・ドライ・エッチング工程)である。図6は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(レジスト除去工程)である。図7は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(トレンチ内壁酸化工程)である。図8は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(トレンチ埋め込み工程)である。図9は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(STI−CMP工程)である。図10は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(窒化シリコン膜除去工程)である。図11は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(ポリシリコン膜形成工程)である。図12は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図(ゲート電極形成工程)である。図13は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス広域断面フロー図12に続くR2部分に対応する単位MISFET領域の要部デバイス模式断面図(ソース・ドレイン形成工程)である。図14は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図6のR1部分に対応するレジスト除去工程)である。図15は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図6に対応する内壁酸化前洗浄工程)である。図16は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図7に対応する内壁酸化工程)である。図17は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図8に対応するトレンチ埋め込み工程)である。図18は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図10に対応する窒化シリコン膜除去工程)である。図19は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図11に対応するポリシリコン膜形成工程)である。図20は本願の一実施の形態の半導体集積回路装置の製造方法に関するデバイス部分断面フロー図(図12に対応するゲート電極形成工程)である。これらに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法に関する全体プロセス・フロー等を説明する。ここでは、一例として、65nmテクノロジ・ノードのプロセスを説明する。

図21は本願の一実施の形態の半導体集積回路装置の製造方法におけるトレンチ埋め込み工程50(図22または図23)に使用するHDP−CVD装置の模式断面図である。これに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法におけるトレンチ埋め込み工程に使用するICP型のHDP−CVD装置31(図21)の概要を説明する。ここでは、300φウエハ用枚葉型HDP−CVD装置の具体例として、ノベラス(Novellus)社のスピード(SPEED)について説明する。

図23は図22における埋め込み膜・キャップ膜成膜工程50の詳細プロセス・ブロック・フロー図である。図24は図23の一連のプロセスを説明するための成膜・エッチング・プロセス説明図である。これらに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法におけるトレンチ埋め込み工程50(図22又は23)の詳細を説明する。以下の各処理工程は、たとえば0.4Pa(3mTorr)、範囲としては0.04から4Pa(0.3から30mTorr)程度の真空度で実行される。

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

1a (半導体ウエハの)デバイス面すなわち第1の主面(または製造工程中のデバイス面側最上面)

2 表面熱酸化膜(パッド酸化膜)

3 窒化シリコン膜(膜パターン)

4 レジスト膜(またはレジスト膜パターン)

5 トレンチ(素子分離溝)

6 内壁熱酸化膜

7 埋め込み絶縁膜(埋め込み酸化シリコン膜またはSTI絶縁膜)

7a ライナー埋め込み絶縁膜

7b 主要埋め込み絶縁膜

8 キャップ絶縁膜(キャップ酸化シリコン膜)

9 絶縁膜の突起部

10 ゲート絶縁膜

11 ポリ・シリコン膜すなわちゲート電極用導電膜(またはゲート電極膜)

12 サイド・ウォール絶縁膜

14 ソース・ドレイン領域

15 酸化膜後退部

31 HDP−CVD装置

32 処理チャンバ(成膜又はエッチング室)

33 ウエハ・ステージ

33a ウエハ・ステージ上面

34 ガス供給ノズル

35 ガス供給制御系

36 ガス供給ライン

37 ガス迂回ライン

38 真空排気系

39 セラミック・ドーム(HDP−CVD装置の外壁)

41 予熱

42 ライナー成膜実行(第2のHDP−CVD処理)

43 主埋め込み膜成膜1(第1のHDP−CVD処理)

44 エッチ・バック1(プラズマ・エッチング処理)

45 主埋め込み膜成膜N

46 エッチ・バックN

47 キャップ膜成膜

48 主埋め込み膜成膜2

49 エッチ・バック2

50 埋め込み膜・キャップ膜成膜工程

51 埋め込み膜成膜工程

52 ライナー成膜工程

53 埋め込み膜成膜・エッチ・バック繰り返し工程

54 埋め込み膜成膜・エッチ・バック組み合わせ単位工程1

55 埋め込み膜成膜・エッチ・バック組み合わせ単位工程N

56 埋め込み膜成膜・エッチ・バック組み合わせ単位工程2

71 ウエハ準備

72 表面酸化

73 窒化シリコン膜成膜(CMPストップ膜)

74 トレンチ形成用レジスト・パターン形成

75 トレンチ形成

76 トレンチ形成用レジスト・パターン除去

77 内壁酸化前洗浄

78 内壁酸化

81 CMP処理(STI−CMP)

82 酸化膜ウエット・エッチング

83 窒化シリコン膜除去

84 ゲート酸化前洗浄

85 ゲート酸化

86 ポリ・シリコン膜成膜

87 ゲート電極パターニング

88 ソース・ドレイン形成

HF 高周波電源(高周波数側RF電源)

LF 低周波電源(低周波数側RF電源)

MF 中間周波電源(中間RF電源)

R1 トレンチ上端部領域

R2 単位MISFET領域

TC キャップ膜の膜厚

TL ライナー膜の膜厚

TM 主埋め込み膜全体の厚さ

TT ライナー膜およびキャップ膜を含む埋め込み膜全体の厚さ

T1 単位成膜ステップでの成膜厚(初期成膜厚)

T2 単位エッチ・バック・ステップでのエッチング量(エッチ・バック量)

T3 単位最終膜厚

Claims (20)

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)ウエハの第1の主面上の窒化シリコンを主要な成分とする膜パターンをマスクとして、前記ウエハの前記第1の主面側にSTI用の素子分離溝を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記素子分離溝を満たし、前記膜パターンを覆うように、酸化シリコン膜系の第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記HDP−CVD装置の前記処理チャンバ内のエッチング・ガスを含む気相エッチング雰囲気中で、前記第1の絶縁膜に対してプラズマ・エッチング処理を実行する工程;

(d)前記工程(c)の後、前記膜パターンを覆う前記第1の絶縁膜をCMP処理により、除去する工程。 - 前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(e)前記工程(c)と(d)の間において、前記工程(b)から(c)を、1回以上の所定の繰り返し回数だけ繰り返す工程。 - 前記1項の半導体集積回路装置の製造方法において、前記CMP処理は、セリア砥粒を主要な砥粒成分として含む研磨スラリを用いて実行される。

- 前記1項の半導体集積回路装置の製造方法において、前記CMP処理は、界面活性剤を含み、且つ、セリア砥粒を主要な砥粒成分として含む研磨スラリを用いて実行される。

- 前記2項の半導体集積回路装置の製造方法において、前記所定の繰り返し回数は、1回以上、20回未満である。

- 前記1項の半導体集積回路装置の製造方法において、前記エッチング・ガスは、弗素原子を有するとともに、窒素、炭素、または水素の少なくとも一つを有する。

- 前記1項の半導体集積回路装置の製造方法において、前記HDP−CVD装置はICP型装置である。

- 前記1項の半導体集積回路装置の製造方法において、前記エッチング・ガスは、弗素原子を有するとともに、窒素を有する。

- 前記1項の半導体集積回路装置の製造方法において、前記エッチング・ガスは、NF3である。

- 前記1項の半導体集積回路装置の製造方法において、前記気相エッチング雰囲気は、不活性ガスを含む。

- 前記1項の半導体集積回路装置の製造方法において、前記工程(d)は、前記膜パターンを前記CMP処理のストッパとして、実行される。

- 前記1項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(f)前記工程(a)と(b)の間に、前記HDP−CVD装置の前記処理チャンバ内において、前記第1のHDP−CVD処理よりもスパッタ/成膜比が大きい第2のHDP−CVD処理により、前記素子分離溝の内面および前記膜パターンを覆うように、酸化シリコン膜系の第2の絶縁膜を形成する工程。 - 前記12項の半導体集積回路装置の製造方法において、前記第2の絶縁膜の形成開始時の前記ウエハの温度は、摂氏500度以上、摂氏700度以下である。

- 前記12項の半導体集積回路装置の製造方法において、前記第2のHDP−CVD処理のスパッタ/成膜比は、前記第1のHDP−CVD処理よりもスパッタ/成膜比よりも2倍以上大きい。

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)ウエハの第1の主面上の窒化シリコンを主要な成分とする膜パターンをマスクとして、前記ウエハの前記第1の主面側にSTI用の素子分離溝を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記素子分離溝を満たし、前記膜パターンを覆うように、酸化シリコン膜系の第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記膜パターンを覆う前記第1の絶縁膜をCMP処理により、除去する工程;

(d)前記工程(a)と(b)の間に、前記HDP−CVD装置の前記処理チャンバ内において、前記第1のHDP−CVD処理よりもスパッタ/成膜比が大きい第2のHDP−CVD処理により、前記素子分離溝の内面および前記膜パターンを覆うように、酸化シリコン膜系の第2の絶縁膜を形成する工程。 - 前記15項の半導体集積回路装置の製造方法において、前記第2の絶縁膜の形成開始時の前記ウエハの温度は、摂氏500度以上、摂氏700度以下である。

- 前記15項の半導体集積回路装置の製造方法において、前記第2のHDP−CVD処理のスパッタ/成膜比は、前記第1のHDP−CVD処理よりもスパッタ/成膜比よりも2倍以上大きい。

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)ウエハの第1の主面上の窒化シリコンを主要な成分とする膜パターンをマスクとして、前記ウエハの前記第1の主面側にSTI用の素子分離溝を形成する工程;

(b)前記工程(a)の後、HDP−CVD装置の処理チャンバ内の気相成膜雰囲気中において、第1のHDP−CVD処理により、前記素子分離溝を満たし、前記膜パターンを覆うように、酸化シリコン膜系の第1の絶縁膜を形成する工程;

(c)前記工程(b)の後、前記HDP−CVD装置の前記処理チャンバ内の気相エッチング雰囲気中で、前記第1の絶縁膜に対してエッチングを施す工程;

(d)前記工程(c)の後、前記膜パターンを覆う前記第1の絶縁膜をCMP処理により、除去する工程;

(e)前記工程(c)と(d)の間において、前記工程(b)から(c)を、1回以上の所定の繰り返し回数だけ繰り返す工程。 - 前記18項の半導体集積回路装置の製造方法において、前記CMP処理は、界面活性剤を含み、且つ、セリア砥粒を主要な砥粒成分として含む研磨スラリを用いて実行される。

- 前記18項の半導体集積回路装置の製造方法において、前記所定の繰り返し回数は、1回以上、20回未満である。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008237544A JP5514420B2 (ja) | 2008-09-17 | 2008-09-17 | 半導体集積回路装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008237544A JP5514420B2 (ja) | 2008-09-17 | 2008-09-17 | 半導体集積回路装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010073773A true JP2010073773A (ja) | 2010-04-02 |

| JP5514420B2 JP5514420B2 (ja) | 2014-06-04 |

Family

ID=42205316

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008237544A Expired - Fee Related JP5514420B2 (ja) | 2008-09-17 | 2008-09-17 | 半導体集積回路装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5514420B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9005459B2 (en) | 2011-03-18 | 2015-04-14 | Tokyo Electron Limited | Film deposition method and film deposition apparatus |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005302848A (ja) * | 2004-04-07 | 2005-10-27 | Toshiba Corp | 半導体製造装置および半導体製造方法 |

| JP2006190784A (ja) * | 2005-01-05 | 2006-07-20 | Renesas Technology Corp | 半導体装置の製造方法 |

| WO2007001878A2 (en) * | 2005-06-24 | 2007-01-04 | Applied Materials, Inc. | Gapfill using deposition-etch sequence |

| JP2007214278A (ja) * | 2006-02-08 | 2007-08-23 | Fujitsu Ltd | 半導体装置の製造方法および半導体装置 |

| JP2007305981A (ja) * | 2006-04-17 | 2007-11-22 | Applied Materials Inc | 総合プロセスモジュレーション(ipm)hdp−cvdによるギャップ充填のための新規な解決法 |

-

2008

- 2008-09-17 JP JP2008237544A patent/JP5514420B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005302848A (ja) * | 2004-04-07 | 2005-10-27 | Toshiba Corp | 半導体製造装置および半導体製造方法 |

| JP2006190784A (ja) * | 2005-01-05 | 2006-07-20 | Renesas Technology Corp | 半導体装置の製造方法 |

| WO2007001878A2 (en) * | 2005-06-24 | 2007-01-04 | Applied Materials, Inc. | Gapfill using deposition-etch sequence |

| JP2008547224A (ja) * | 2005-06-24 | 2008-12-25 | アプライド マテリアルズ インコーポレイテッド | 堆積・エッチングシーケンスを用いたギャップ充填 |

| JP2007214278A (ja) * | 2006-02-08 | 2007-08-23 | Fujitsu Ltd | 半導体装置の製造方法および半導体装置 |

| JP2007305981A (ja) * | 2006-04-17 | 2007-11-22 | Applied Materials Inc | 総合プロセスモジュレーション(ipm)hdp−cvdによるギャップ充填のための新規な解決法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9005459B2 (en) | 2011-03-18 | 2015-04-14 | Tokyo Electron Limited | Film deposition method and film deposition apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5514420B2 (ja) | 2014-06-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100878015B1 (ko) | 산화물 제거 방법 및 이를 이용한 트렌치 매립 방법 | |

| JP4669679B2 (ja) | 窒化珪素膜の製造方法及び半導体装置の製造方法 | |

| US7271463B2 (en) | Trench insulation structures including an oxide liner that is thinner along the walls of the trench than along the base | |

| TWI352387B (en) | Etch methods to form anisotropic features for high | |

| US9305831B2 (en) | Integrated metal spacer and air gap interconnect | |

| CN106653675B (zh) | 浅沟槽隔离结构的形成方法 | |

| US20060094215A1 (en) | Technique for forming a dielectric etch stop layer above a structure including closely spaced lines | |

| JP2010080798A (ja) | 半導体集積回路装置および半導体集積回路装置の製造方法 | |

| JP2003309108A (ja) | エッチング方法 | |

| TW201025447A (en) | Manufacturing method of semiconductor device | |

| JP2007142155A (ja) | 酸化処理方法および半導体装置の製造方法 | |

| JPH11340317A (ja) | 分離構造形成方法 | |

| US8641828B2 (en) | Cleaning method of semiconductor manufacturing process | |

| JP5514420B2 (ja) | 半導体集積回路装置の製造方法 | |

| US20030232503A1 (en) | Method for manufacturing semiconductor device | |

| KR20060038022A (ko) | 반도체 소자의 소자분리막 형성방법 | |

| US8569143B2 (en) | Methods of fabricating a semiconductor IC having a hardened shallow trench isolation (STI) | |

| KR100524805B1 (ko) | 반도체 소자의 트렌치 갭필 방법 | |

| TWI564945B (zh) | 半導體製程中的清洗方法 | |

| US6887767B2 (en) | Method for manufacturing semiconductor device | |

| TWI719243B (zh) | 鰭型場效電晶體及其製造方法 | |

| JP2010010400A (ja) | 半導体集積回路装置の製造方法 | |

| JP2023057062A (ja) | 傾斜酸化を用いたシームレスな間隙充填のための方法 | |

| KR100920048B1 (ko) | 반도체 소자의 제조방법 | |

| TW202338066A (zh) | 鉬的蝕刻方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110908 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130515 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130606 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130729 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140313 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140331 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5514420 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |