JP2010068630A - インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム、このインバータ制御回路を実現するためのプログラム、及びこのプログラムを記録した記録媒体 - Google Patents

インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム、このインバータ制御回路を実現するためのプログラム、及びこのプログラムを記録した記録媒体 Download PDFInfo

- Publication number

- JP2010068630A JP2010068630A JP2008232838A JP2008232838A JP2010068630A JP 2010068630 A JP2010068630 A JP 2010068630A JP 2008232838 A JP2008232838 A JP 2008232838A JP 2008232838 A JP2008232838 A JP 2008232838A JP 2010068630 A JP2010068630 A JP 2010068630A

- Authority

- JP

- Japan

- Prior art keywords

- phase

- waveform

- pulse width

- value

- absolute value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000005070 sampling Methods 0.000 claims abstract description 29

- 238000006243 chemical reaction Methods 0.000 description 23

- 238000000034 method Methods 0.000 description 16

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 15

- 238000001514 detection method Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 239000003990 capacitor Substances 0.000 description 1

Images

Landscapes

- Inverter Devices (AREA)

Abstract

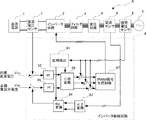

【解決手段】三相インバータ回路が有する各相のスイッチング手段をPWM信号で制御するインバータ制御回路において、各サンプリング期間の三相インバータ回路が出力する各相の線間電圧波形をそれぞれ生成するための、絶対値がパルス幅を表し正負がパルス波形の極性を表す3つのパルス幅値を算出する算出手段67と、算出手段67により算出された3つのパルス幅値のうち絶対値が最大であるパルス幅値が0より大きいか否かを判別する判別手段67と、判別手段67による判別結果により異なる規則で当該サンプリング期間の各相の波形を決定し、PWM信号を生成するPWM信号生成手段67とを備えた。

【選択図】図1

Description

1 直流電源

2 インバータ回路

3 フィルタ回路

4 変圧回路

5 商用電力系統

6 インバータ制御回路

61 位相検出回路

62 PI制御回路

63 αβ変換回路

64 dq変換回路

65 PI制御回路

66 三相変換回路

67 PWM信号生成回路(算出手段、判別手段、PWM信号生成手段)

7 直流電圧センサ

8 電流センサ

9 線間電圧センサ

Claims (5)

- 三相インバータ回路が有する各相のスイッチング手段をPWM信号で制御するインバータ制御回路であって、

各サンプリング期間の前記三相インバータ回路が出力する各相の線間電圧波形をそれぞれ生成するための、絶対値がパルス幅を表し正負がパルス波形の極性を表す3つのパルス幅値を算出する算出手段と、

前記算出手段により算出された3つのパルス幅値のうち絶対値が最大であるパルス幅値が0より大きいか否かを判別する判別手段と、

絶対値が最大であるパルス幅値が0より大きい場合は予め設定された第1の規則で当該サンプリング期間の各相の波形を決定し、絶対値が最大であるパルス幅値が0より小さい場合は予め設定された前記第1の規則とは異なる規則で当該サンプリング期間の各相の波形を決定して前記PWM信号を生成するPWM信号生成手段と、

を備えていることを特徴とするインバータ制御回路。 - 前記PWM信号生成手段は、

絶対値が最大であるパルス幅値が0より大きい場合、

前記パルス幅値の絶対値が最大である第1の相の波形を、当該第1の相のパルス幅値の期間のオン状態が中央に配置されたパルス波形とし、

前記第1の相の次の第2の相の波形を、全区間がオフ状態の波形とし、

前記第2の相の次の第3の相の波形を、前記第2の相のパルス幅値の絶対値の期間のオン状態が中央に配置されたパルス波形とし、

絶対値が最大であるパルス幅値が0より小さい場合、

前記第1の相の波形を、全区間がオフ状態の波形とし、

前記第2の相の波形を、前記第1の相のパルス幅値の絶対値の期間のオン状態が中央に配置されたパルス波形とし、

前記第3の相の波形を、当該第3の相のパルス幅値の期間のオン状態が中央に配置されたパルス波形とする、

請求項1に記載のインバータ制御回路。 - 請求項1または2に記載のインバータ制御回路を備えている系統連系インバータシステム。

- コンピュータを、

三相インバータ回路が有する各相のスイッチング手段をPWM信号で制御するインバータ制御回路として機能させるためのプログラムであって、

前記コンピュータを、

各サンプリング期間の前記三相インバータ回路が出力する各相の線間電圧波形をそれぞれ生成するための、絶対値がパルス幅を表し正負がパルス波形の極性を表す3つのパルス幅値を算出する算出手段と、

前記算出手段により算出された3つのパルス幅値のうち絶対値が最大であるパルス幅値が0より大きいか否かを判別する判別手段と、

絶対値が最大であるパルス幅値が0より大きい場合は予め設定された第1の規則で当該サンプリング期間の各相の波形を決定し、絶対値が最大であるパルス幅値が0より小さい場合は予め設定された前記第1の規則とは異なる規則で当該サンプリング期間の各相の波形を決定して前記PWM信号を生成するPWM信号生成手段と、

して機能させるためのプログラム。 - 請求項4に記載のプログラムを記録したコンピュータ読み取り可能な記録媒体。

Priority Applications (12)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008232838A JP5270272B2 (ja) | 2008-09-11 | 2008-09-11 | インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム、このインバータ制御回路を実現するためのプログラム、及びこのプログラムを記録した記録媒体 |

| EP18213860.2A EP3484037B1 (en) | 2008-09-11 | 2009-07-13 | Inverter control circuit and utility interactive inverter system with inverter control circuit |

| EP09812956.2A EP2325991B1 (en) | 2008-09-11 | 2009-07-13 | Inverter control circuit and interconnection inverter system having that inverter control circuit |

| US12/991,630 US8446742B2 (en) | 2008-09-11 | 2009-07-13 | Inverter control circuit and interconnection inverter system having that inverter control circuit |

| AU2009290165A AU2009290165B2 (en) | 2008-09-11 | 2009-07-13 | Inverter control circuit and interconnection inverter system having that inverter control circuit |

| ES09812956T ES2712889T3 (es) | 2008-09-11 | 2009-07-13 | Circuito de control de inversor y sistema inversor de interconexión que comprende dicho circuito de control de inversor |

| PCT/JP2009/062652 WO2010029808A1 (ja) | 2008-09-11 | 2009-07-13 | インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム |

| ES20179308T ES2907380T3 (es) | 2008-09-11 | 2009-07-13 | Circuito de control de inversor y sistema inversor interactivo que comprende dicho circuito de control de inversor |

| CN200980127594.XA CN102099996B (zh) | 2008-09-11 | 2009-07-13 | 逆变器控制电路、具备该逆变器控制电路的系统互连逆变器系统 |

| KR1020107029446A KR20110056261A (ko) | 2008-09-11 | 2009-07-13 | 인버터 제어회로 및 이 인버터 제어회로를 구비한 계통연계 인버터 시스템 |

| ES18213860T ES2814602T3 (es) | 2008-09-11 | 2009-07-13 | Circuito de control de inversor y sistema inversor interactivo con la red eléctrica con circuito de control de inversor |

| EP20179308.0A EP3726720B1 (en) | 2008-09-11 | 2009-07-13 | Inverter control circuit and utility interactive inverter system with inverter control circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008232838A JP5270272B2 (ja) | 2008-09-11 | 2008-09-11 | インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム、このインバータ制御回路を実現するためのプログラム、及びこのプログラムを記録した記録媒体 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010068630A true JP2010068630A (ja) | 2010-03-25 |

| JP5270272B2 JP5270272B2 (ja) | 2013-08-21 |

Family

ID=42193721

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008232838A Active JP5270272B2 (ja) | 2008-09-11 | 2008-09-11 | インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム、このインバータ制御回路を実現するためのプログラム、及びこのプログラムを記録した記録媒体 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5270272B2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011217464A (ja) * | 2010-03-31 | 2011-10-27 | Daihen Corp | インバータ制御回路、および、このインバータ制御回路を備えた系統連系インバータシステム |

| KR101178393B1 (ko) | 2010-12-30 | 2012-08-30 | 서울과학기술대학교 산학협력단 | 3상 간접전류제어 방식의 계통연계형 인버터의 제어방법 |

| EP2503680A2 (en) | 2011-03-24 | 2012-09-26 | Daihen Corporation | Control circuit for controlling power conversion circuit, inverter apparatus including the control circuit, and interconnection inverter system including inverter apparatus |

| JP2013021895A (ja) * | 2011-07-14 | 2013-01-31 | Daihen Corp | インバータ装置、および、このインバータ装置を備えた系統連系インバータシステム |

| DE102014110472A1 (de) | 2013-07-25 | 2015-03-12 | Daihen Corporation | Verfahren zum Steuern von Vorrichtungen, die mit einer Kommunikationsfunktion versehen sind, und bei der Ausführung des Verfahrens verwendete Vorrichtung |

| KR20190060966A (ko) | 2011-03-24 | 2019-06-04 | 가부시키가이샤 다이헨 | 전력변환회로를 제어하는 제어회로, 이 제어회로를 구비한 인버터 장치 및 이 인버터 장치를 구비한 계통연계 인버터 시스템 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05284751A (ja) * | 1992-03-31 | 1993-10-29 | Fuji Electric Co Ltd | 3パルスpwmインバータの制御装置 |

| JP2007288858A (ja) * | 2006-04-13 | 2007-11-01 | Sharp Corp | モータ制御装置、冷蔵庫、空気調和機 |

| JP2007295777A (ja) * | 2006-04-27 | 2007-11-08 | Fuji Electric Holdings Co Ltd | 多重電力変換器の制御装置 |

-

2008

- 2008-09-11 JP JP2008232838A patent/JP5270272B2/ja active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05284751A (ja) * | 1992-03-31 | 1993-10-29 | Fuji Electric Co Ltd | 3パルスpwmインバータの制御装置 |

| JP2007288858A (ja) * | 2006-04-13 | 2007-11-01 | Sharp Corp | モータ制御装置、冷蔵庫、空気調和機 |

| JP2007295777A (ja) * | 2006-04-27 | 2007-11-08 | Fuji Electric Holdings Co Ltd | 多重電力変換器の制御装置 |

Cited By (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014064469A (ja) * | 2010-03-31 | 2014-04-10 | Daihen Corp | インバータ制御回路、および、このインバータ制御回路を備えた系統連系インバータシステム |

| JP2011217464A (ja) * | 2010-03-31 | 2011-10-27 | Daihen Corp | インバータ制御回路、および、このインバータ制御回路を備えた系統連系インバータシステム |

| KR101178393B1 (ko) | 2010-12-30 | 2012-08-30 | 서울과학기술대학교 산학협력단 | 3상 간접전류제어 방식의 계통연계형 인버터의 제어방법 |

| EP3396841A1 (en) | 2011-03-24 | 2018-10-31 | Daihen Corporation | Control circuit for controlling power conversion circuit, inverter apparatus including the control circuit, and interconnection inverter system including the inverter apparatus |

| US9294009B2 (en) | 2011-03-24 | 2016-03-22 | Daihen Corporation | Inverter apparatus including control circuit employing two-phase modulation control, and interconnection inverter system including the inverter apparatus |

| US9979317B2 (en) | 2011-03-24 | 2018-05-22 | Daihen Corporation | Inverter apparatus including control circuit employing two-phase modulation control, and interconnection inverter system including the inverter apparatus |

| EP2503680A2 (en) | 2011-03-24 | 2012-09-26 | Daihen Corporation | Control circuit for controlling power conversion circuit, inverter apparatus including the control circuit, and interconnection inverter system including inverter apparatus |

| US10141864B2 (en) | 2011-03-24 | 2018-11-27 | DAUHEN Corporation | Inverter apparatus including control circuit employing two-phase modulation control, and interconnection inverter system including the inverter apparatus |

| KR20190060966A (ko) | 2011-03-24 | 2019-06-04 | 가부시키가이샤 다이헨 | 전력변환회로를 제어하는 제어회로, 이 제어회로를 구비한 인버터 장치 및 이 인버터 장치를 구비한 계통연계 인버터 시스템 |

| US10389269B2 (en) | 2011-03-24 | 2019-08-20 | Daihen Corporation | Inverter apparatus including control circuit employing two-phase modulation control, and interconnection inverter system including the inverter apparatus |

| US10630200B2 (en) | 2011-03-24 | 2020-04-21 | Daihen Corporation | Inverter apparatus including control circuit employing two-phase modulation control, and interconnection inverter system including the inverter apparatus |

| JP2013021895A (ja) * | 2011-07-14 | 2013-01-31 | Daihen Corp | インバータ装置、および、このインバータ装置を備えた系統連系インバータシステム |

| DE102014110472A1 (de) | 2013-07-25 | 2015-03-12 | Daihen Corporation | Verfahren zum Steuern von Vorrichtungen, die mit einer Kommunikationsfunktion versehen sind, und bei der Ausführung des Verfahrens verwendete Vorrichtung |

| US10247764B2 (en) | 2013-07-25 | 2019-04-02 | Daihen Corporation | Method for controlling devices provided with communication function, and device used in implementing the method |

| US11029345B2 (en) | 2013-07-25 | 2021-06-08 | Daihen Corporation | Method for controlling devices provided with communication function, and device used in implementing the method |

| US11624760B2 (en) | 2013-07-25 | 2023-04-11 | Daihen Corporation | Method for controlling devices provided with communication function, and device used in implementing the method |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5270272B2 (ja) | 2013-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5270272B2 (ja) | インバータ制御回路、このインバータ制御回路を備えた系統連系インバータシステム、このインバータ制御回路を実現するためのプログラム、及びこのプログラムを記録した記録媒体 | |

| JP5794274B2 (ja) | マトリクスコンバータ | |

| JP6134733B2 (ja) | 多相変換器システムおよび方法 | |

| JP5549697B2 (ja) | 電流形電力変換装置 | |

| JP2012170277A (ja) | 電力変換装置および電動パワーステアリングの制御装置 | |

| JP2008306805A (ja) | 電力変換装置 | |

| JP2009100505A (ja) | 3レベル電力変換装置 | |

| JP2009201248A (ja) | クランプ式電力変換装置 | |

| JP3856689B2 (ja) | 中性点クランプ式電力変換器の制御装置 | |

| JPWO2014024460A1 (ja) | モータ制御装置 | |

| US9685884B2 (en) | Seven-level inverter apparatus | |

| JPWO2019180763A1 (ja) | 電力変換装置および回転機駆動システム | |

| JP2004201440A (ja) | パルス幅変調方法とその装置及び電力変換方法と電力変換器 | |

| JP5364303B2 (ja) | 電流制御型電力変換器及び電流制御型電力変換器の出力電流波形改善方法 | |

| JPWO2020089990A1 (ja) | 電力変換装置 | |

| JP2000050529A (ja) | 電力変換装置の電流制限方法 | |

| WO2019049713A1 (ja) | 電力変換装置およびその制御方法 | |

| JP2000299984A (ja) | 三相/単相pwmサイクロコンバータの制御装置 | |

| JP2007097394A (ja) | 電力変換器 | |

| JP5768957B2 (ja) | 3相v結線式インバータの制御装置 | |

| JP2009142005A (ja) | 系統連係型インバータ制御装置及び制御方法 | |

| JP2006109541A (ja) | 電力変換器の制御装置 | |

| JP2008295135A (ja) | 電力変換装置 | |

| JP6110093B2 (ja) | インバータ装置、および制御方法 | |

| JP4448294B2 (ja) | 電力変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110801 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130509 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5270272 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |