JP2010062387A - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP2010062387A JP2010062387A JP2008227418A JP2008227418A JP2010062387A JP 2010062387 A JP2010062387 A JP 2010062387A JP 2008227418 A JP2008227418 A JP 2008227418A JP 2008227418 A JP2008227418 A JP 2008227418A JP 2010062387 A JP2010062387 A JP 2010062387A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- insulating film

- film

- low

- tunnel insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/68—Floating-gate IGFETs

- H10D30/681—Floating-gate IGFETs having only two programming levels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/031—Manufacture or treatment of data-storage electrodes

- H10D64/035—Manufacture or treatment of data-storage electrodes comprising conductor-insulator-conductor-insulator-semiconductor structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/031—Manufacture or treatment of data-storage electrodes

- H10D64/037—Manufacture or treatment of data-storage electrodes comprising charge-trapping insulators

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/681—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered

- H10D64/685—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered being perpendicular to the channel plane

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

【解決手段】半導体基板1と、前記半導体基板に離間して形成されたソース領域2aおよびドレイン領域2bと、ソース領域とドレイン領域との間の半導体基板上に形成された第1の絶縁膜3であって、第1の絶縁層と、第1の絶縁層上に形成され第1の絶縁層より誘電率が高く、母材と異なる元素が添加されることにより形成される、ホールの捕獲および放出をする第1のサイトを有している第2の絶縁層とを備える第1の絶縁膜3と、第1の絶縁膜上に形成された電荷蓄積膜4と、電荷蓄積膜上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された制御ゲート電極6と、を有する記憶素子を備えている。

【選択図】図1

Description

本発明の第1実施形態による不揮発性半導体記憶装置は、例えば、マトリクス状に配置されたNANDセルユニットを有している、各NANDセルユニットは、直列に接続されたメモリセルで形成されたNANDセルを含んでいる。各メモリセルMCは、図1に示すように、p型のSi基板1に離間して形成された、n型不純物(例えば、P(リン)やAs(ヒ素))を含むn型ソース領域2aおよびドレイン領域2bを備えている。ソース領域2aとドレイン領域2bとの間のSi基板1上にトンネル絶縁膜3が形成され、このトンネル絶縁膜3上に電荷蓄積膜4が形成され、この電荷蓄積膜4上に電極間絶縁膜5が形成され、この電極間絶縁膜5上に制御ゲート電極6が形成された構成となっている。そして、制御ゲート電極6、電極間絶縁膜5、電荷蓄積膜4、およびトンネル絶縁膜3からなる積層構造のゲートは、シリコン酸化膜7によって覆われている。ここで、電荷蓄積膜4として、浮遊ゲート電極を用いてFG型の不揮発性半導体記憶装置にしても良いし、トラップ絶縁膜を用いていわゆるMONOS型の不揮発性半導体記憶装置にしても良い。

εox×Eox=ε1×E1=ε2×E2 (4)

となる。ここで、εox(=3.9)はSiO2の誘電率である。実電界は、E1=V1/T1、E2=V2/T2と定義した。つまり、

ε1×V1/T1=ε2×V2/T2 (5)

を満たす。(4)式からわかるように、high−k層よりもlow−k層の方の実電界が強くなる。これは、ε1<ε2であるので、E1>E2となるからである。それ故、low−k層の物理層厚T1がhigh−k層の物理層厚T2と比較してある程度厚い場合、low−k層にかかる電圧V1がhigh−k層にかかる電圧V2よりも高くなる。これは、ε1<ε2であるので、例えば、T1>T2のとき、(ε1/T1)<(ε2/T2)となる。これと(5)式から、V1>V2となるからである。

TFN(φb *,m*,E)=1 (8)

で定義される。ここで、m*はトンネル絶縁膜中をトンネルしているホールの有効質量、φb *はトンネル絶縁膜の実効的なバリアハイト、E1およびE2はそれぞれlow−k層およびhigh−k層における実電界を示す。なお、F−Nトンネルとは、図5(a)に示すように、ホールが絶縁膜の傾斜した価電子帯を通り抜ける(電子の場合は伝導帯を通り抜ける)トンネルことを意味し、D−T(Direct Tunneling)とは、図5(b)に示すように、ホールが絶縁膜の価電子帯を通り抜けず、対向する電極に直接到達するトンネルのことを意味する。なお、ここではホールのトンネリングを説明しやすいように、エネルギーを示す縦軸を通常(電子の場合)とは反対向き、すなわち図において上下反対に示した。また、これより先、断り無くエネルギー軸を逆向きに取る場合もあるが、内容から逆向きであることは容易に判断できる。

P=p1×(1−f)=p2×f (9)

を満たす。このとき、f=p1/(p1+p2)となるので、

P=1/(1/p1+1/p2) (10)

となる。アシストレベルを介さない場合の確率はp1とp2の積、p1×p2であり、(10)式よりも小さな値となる。それゆえ、アシストレベルを介するとリーク電流は、アシストレベルを介さない場合よりも高くなる。

φT2 *=φT2−φb2 *

と定義した。

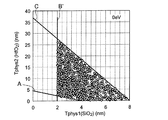

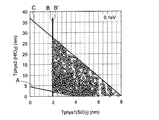

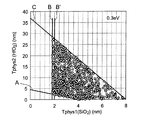

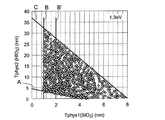

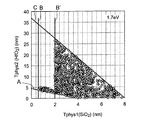

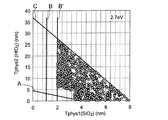

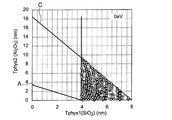

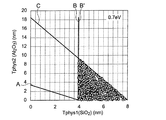

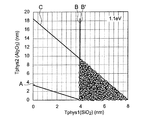

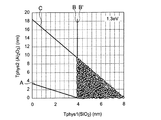

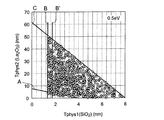

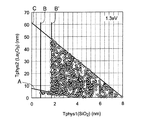

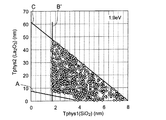

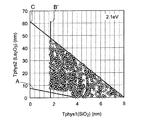

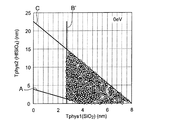

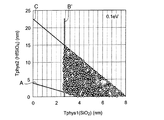

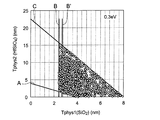

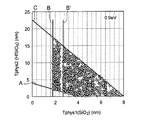

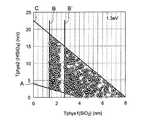

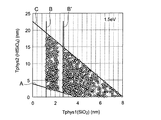

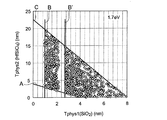

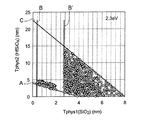

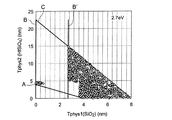

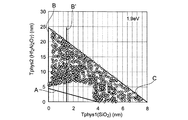

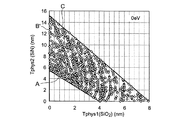

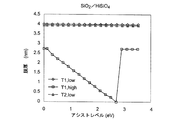

次に、第1実施形態の不揮発性半導体記憶装置において、積層構造のトンネル絶縁膜は、どの膜厚範囲であれば、トンネル絶縁膜として要求されるスペックを満たすかを調べた。SiO2層のEOTすなわちTeq1(SiO2)を横軸に、HfO2層のEOTすなわちTeq2(HfO2)を縦軸にとって、トンネル絶縁膜として求められるスペックを満たす範囲を図9に示す。つまり、当然ながら、点で示したところだけでなく、それ以外の、点と点の間の領域も含まれる。なお、SiO2層とHfO2層の両方を合わせたEOT(Teq,all)の上限を8nmとした。この上限は、図9において、直線C(Teq1+Teq2=8)で表される。それ故、図9に示す、Teq1+Teq2>8となる領域(直線Cより上の領域)は、スペックを満たす範囲に含まれていない。図9において、直線Aは低電界でリーク電流を抑えるのに最低限必要な膜厚の割合を示している。直線Aと横軸が交わる点LSは、SiO2層だけの場合であり、電荷保持するのに、ホールによる電流の場合、SiO2層が約4nmが必要であることを示している。ちなみに、電子による電流の場合は5nmであった。そして、直線Aと縦軸が交わる点LHは、HfO2層だけの場合であり、直線AはSiO2層とHfO2層の積層構造が電荷保持するのに必要な最低限必要な膜厚を表している。

次に、本発明の第2実施形態による不揮発性半導体記憶装置を説明する。第1実施形態の不揮発性半導体記憶装置においては、トンネル絶縁膜は、high−k層だけにアシストレベルが形成されていたが、本実施形態の不揮発性半導体記憶装置においては、high−k層だけでなく、low−k層にもアシストレベルが形成されたトンネル絶縁膜を有している。第2実施形態の不揮発性半導体記憶装置は、トンネル絶縁膜以外、第1実施形態と同じ構成となっている。

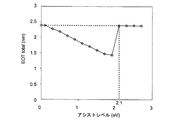

ここまでは、アシストレベルとして、1.1eVの場合だけを示したが、他の値でも構わない。しかしながら、アシストレベルの値は何でも良いわけではなく、本発明の上記実施形態における効果を得るためには、以下に説明する範囲にあることが好ましい。

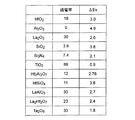

以上の説明では、high−k層として、HfO2の例を示したが、他のhigh−k層でも同じ効果がある。他のhigh−k層として、例えば、図15に示す表に揚げたようなものがある(例えば、J. Robertson, J. Vac. Sci. Technol. B, 18, 1785 (2000)、

G. Yu et al., Appl. Phys. Lett, 81, 376 (2002)、G. D. Wilk et al., Symp. VLSI Tech. Dig. 88 (2002)、G. Seguini et al., Appl. Phys. Lett. 88, 202903 (2006)、またはA. Dimoulas et al., Appl. Phys. Lett. 85, 3205 (2004)参照)。これらの誘電率とバンドオフセットΔEVとの関係をプロットしたものを図16に示す。ここで、バンドオフセットΔEVとは、Si基板の価電子帯の上端EVとhigh−k層の価電子帯の上端EVとの差であり、トンネル絶縁膜においてホールのバリアハイトに対応する。

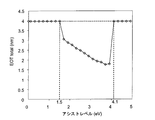

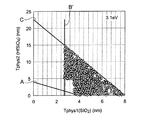

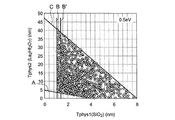

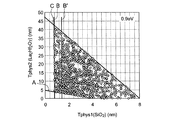

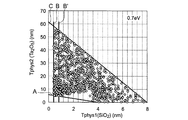

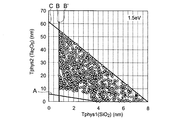

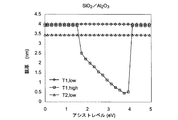

また、high−k層としてAl2O3層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図17A乃至図17Zに示す。図17A乃至図17Zはそれぞれ、Al2O3層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eV、2.1eV、2.3eV、2.5eV、2.7eV、2.9eV、3.1eV、3.3eV、3.5eV、3.7eV、3.9eV、4.1eV、4.3eV、4.5eV、4.7eV、4.9eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図18に示す。図18からわかるように、high−k層としてAl2O3層を選択した場合の、アシストレベルは1.5eV以上であり、4.1eV以下であることが好ましい。なお、アシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図17J乃至図17U)。

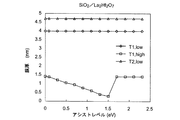

また、high−k層としてLa2O3層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図19A乃至図19Nに示す。図19A乃至図19Nそれぞれ、La2O3層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eV、2.1eV、2.3eV、2.5eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図20に示す。図20からわかるように、high−k層としてLa2O3層を選択した場合の、アシストレベルは0.1eV以上、1.9eV未満であることが好ましい。なお、アシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図19C乃至図19J)。

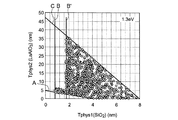

また、high−k層としてHfSiO4層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図21A乃至図21Sに示す。図21A乃至図21Sはそれぞれ、HfSiO4層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eV、2.1eV、2.3eV、2.5eV、2.7eV、2.9eV、3.1eV、3.3eV、3.5eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図22に示す。図22からわかるように、high−k層としてHfSiO4層を選択した場合の、アシストレベルは0.1eVより大きく、2.9eV以下であることが好ましい。なお、アシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図21C乃至図21O)。また、HfSiO4は、アシストレベルが無い場合、SiO2層の層厚は2.7nmが必要であるが(図21A)、HfSiO4に0.3eV以上に深いアシストレベルがあれば、SiO2層が無くても、つまりHfSiO4の単層でもトンネル絶縁膜として用いることができる(図21C乃至図21O)。このとき、2.9eVよりも深いアシストレベルが有る場合は、EOTを可及的に薄くする効果は達成できない。また、low−k層としてSiO2を用いたが、SiNはHfSiO4層より誘電率が低いので、SiO2層と同様に、HfSiO4層に対してlow−k層として用いることができる。上述の説明ではlow−k層がSiO2層であって、high−k層がHfSiO4層であったが、low−k層が酸化シリコン層であって、high−k層がハフニウムシリケート(HfSiO)層である場合でもアシストレベルが上述の範囲であれば同様の範囲で同様の効果を得ることができる。

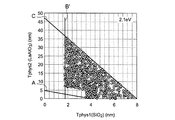

また、high−k層としてLaAlO3層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図23A乃至図23Nに示す。図23A乃至図23Nはそれぞれ、LaAlO3層のアシストレベルが、0eV(無い場合)0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eV、2.1eV、2.3eV、2.5eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図24に示す。図24からわかるように、high−k層としてLaAlO3層を選択した場合の、アシストレベルは0eVより大きく、1.9eV未満であることが好ましい。なお、アシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図23B乃至図23J)。この例では、low−k層としてSiO2を用いたが、SiN(窒化シリコン)はLaAlO3層より誘電率が低いので、SiO2層と同様に、LaAlO3層に対してlow−k層として用いることができる。上述の説明ではlow−k層がSiO2層であって、high−k層がLaAlO3層であったが、low−k層が酸化シリコン層であってhigh−k層がランタンアルミネート(LaAlO)層である場合でもアシストレベルが上述の範囲であれば同様の範囲で同様の効果を得ることができる。

また、high−k層としてHf2Al2O7((HfO2)2/3(Al2O3)1/3)層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図25A乃至図25Oに示す。図25A乃至図25Oはそれぞれ、Hf2Al2O7層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eV、2.1eV、2.3eV、2.5eV、2.7eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図26に示す。図26からわかるように、high−k層としてHf2Al2O7層を選択した場合の、アシストレベルは0.1eVより大きく、2.1eV以下であることが好ましい。なお、Hf2Al2O7層にアシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図25C乃至図25K)。また、Hf2Al2O7層は、1.5eV以上1.7eV以下にアシストレベルがあれば、SiO2層が無くても、つまりHf2Al2O7の単層としてトンネル絶縁膜に用いることができる(図25J乃至図25K)。しかし、Hf2Al2O7層は、2.1eV以上2.7eVにアシストレベルがある場合は、EOTを可及的に薄くする効果は達成できない。なお、low−k層としてSiO2を用いたが、SiN(窒化シリコン)はHf2Al2O7層より誘電率が低いので、SiO2層と同様に、Hf2Al2O7層に対してlow−k層として用いることができる。上述の説明ではlow−k層がSiO2層であって、high−k層がHf2Al2O7層であったが、low−k層が酸化シリコン層であって、high−k層がハフニウムアルミネート(HfAlO)層である場合でもアシストレベルが上述の範囲であれば同様の範囲で同様の効果を得ることができる。

また、high−k層としてLa2Hf2O7層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図27A乃至図27Mに示す。図27a乃至図27Mはそれぞれ、La2Hf2O7層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eV、2.1eV、2.3eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図28に示す。図28からわかるように、high−k層としてLa2Hf2O7層を選択した場合の、アシストレベルは0.1eV以上1.7eV以下であることが好ましい。なお、アシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図27C乃至図27I)。この例では、low−k層としてSiO2を用いたが、SiN(窒化シリコン)はLa2Hf2O7層より誘電率が低いので、SiO2層と同様に、La2Hf2O7層に対してlow−k層として用いることができる。上述の説明ではlow−k層がSiO2層であって、high−k層がLa2Hf2O7層であったが、low−k層が酸化シリコン層であって、high−k層がランタンハフネート(LaHfO)層である場合でもアシストレベルが上述の範囲であれば同様の範囲で同様の効果を得ることができる。

また、SiN(窒化シリコン)は、SiO2の誘電率に較べてほぼ二倍と高いので、SiNはSiO2に対してhigh−k絶縁層として機能する。そこで、high−k層としてSiN層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図29A乃至図29Kに示す。図29A乃至図29Kはそれぞれ、SiN層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eV、1.9eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図30に示す。図30からわかるように、high−k層としてSiN層を選択した場合、EOTを薄くするための適切なアシストレベルは存在しない。しかし、アシストレベルを形成することによって、低い電界で消去特性のスペックを満たすので、消去効率を上げることができる。

また、high−k層としてTa2O5層、low−k層としてSiO2層を選択して積層した場合の、様々なアシストレベルにおいて、本発明の一実施形態で定義したトンネル絶縁膜に求められるスペックを満たす物理膜厚の範囲を図31A乃至図31Jに示す。図31A乃至図31Jはそれぞれ、Ta2O5層のアシストレベルが、0eV(無い場合)、0.1eV、0.3eV、0.5eV、0.7eV、0.9eV、1.1eV、1.3eV、1.5eV、1.7eVの場合の図である。そして、これらのアシストレベルと、トンネル絶縁膜のEOTとの関係を図32に示す。図32からわかるように、high−k層としてTa2O5層を選択した場合の、アシストレベルは0eVより大きく1.3eV以下であることが好ましい。なお、アシストレベルがある場合には、そのlow−k層の層厚(直線Bと横軸との交点の値)を、アシストレベルが無い場合に必要なlow−k層の層厚(直線B’と横軸との交点の値)よりも薄くすることができる(図31B乃至図31F)。この例では、low−k層としてSiO2を用いたが、SiN(窒化シリコン)はTa2O5層より誘電率が低いので、SiO2層と同様に、Ta2O5層に対してlow−k層として用いることができる。上述の説明ではlow−k層がSiO2層であって、high−k層がTa2O5層であったが、low−k層が酸化シリコン層であって、high−k層がタンタルオキサイド(TaO)層である場合でもアシストレベルが上述の範囲であれば同様の範囲で同様の効果を得ることができる。

T2=−(T2,low/T1,low)×T1+T2,low (13)

を満足する。これは、上述の、図10、図13A−図13P、図17A−図17Z、図19A−図19N、図21A−図21S、図23A−図23N、図25A−図25O、図27A−図27M、図29A−図29K、図31A−図31Jにおいて直線Aに対応する式である。T1,lowは直線Aと横軸との交点の値となり、T2,lowは直線Aと縦軸との交点の値となる。したがって、low−k層がSiO2の場合、T2,lowは4nmになる。

T1=T1,high (14)

となる。これは、図9に示す直線Bに対応する。

0 ≦ φt1 ≦ Δφb + φt2 (15)

を満たすか、あるいはlow−k層にトラップがない必要がある。ここで、Δφbは

Δφb= φb1−φb2 (16)

と定義した。(15)式を満たさないと、低電界でリーク電流が高くなり、電荷保持ができない。なお、φb1およびφb2はそれぞれシリコン基板のフェルミレベルEFに対するlow−k層およびhigh−k層のホールのバリアハイトを表す。

EOTtotal= T1×εox/ε1+ T2×εox/ε2= 8 (nm) (17)

と表される。したがって、(13)式、(14)式、(17)式のよって囲まれる領域がhigh−k層およびlow−k層のそれぞれの好適な物理膜厚の領域となる。この領域は、各材料におけるアシストレベルの好適な範囲によって変わることになる。また、この領域は、次の3つの不等式を満たす領域と同等である。

T2≧−(T2,low/T1,low)×T1+T2,low

T1≧T1,high

T1×εox/ε1+ T2×εox/ε2≦ 8

そして、トンネル絶縁膜を最小にする膜厚は、T1が(14)式によって求まり、T2が(14)式を(13)に代入することにより、

T2=−(T2,low/T1,low)×T1,high+T2,low (18)

となる。

ホールのアシストレベルは、膜と水平方向に一様に存在している必要はない。図44(a)、44(b)にアシストレベルが部分的にある場合のトンネル絶縁膜の模式図を示す。このトンネル絶縁膜は、基板1上にlow−k層8と、アシストレベルのあるhigh−k層9とを積層して形成される。ここで、アシストレベルがある領域の割合をRとすると、無い領域の割合は1−Rとなる。そして、アシストレベルがある場合のリーク電流をJtat、無い場合のリーク電流をJ0とすると、膜全体を流れる電流Jは、

J=R×Jtat+(1−R)×J0 (19)

と表せる。低電界では、リーク電流はアシストレベルの有無によらないため、リーク電流は膜全体で低く抑えられる。一方で、高電界では、アシストレベルがあるとリーク電流が高くなるので、アシストレベルのある領域だけでリーク電流を高くできる。アシストレベルは、図44(a)、44(b)に示すように、例えば、膜の端より内側にアシストレベルを形成することができる。こうすることによって、電界集中して絶縁破壊が起こりやすい端を避けてリーク電流を高くできるため、膜の信頼性を高くすることができる。

次に、本発明の第3実施形態によるFG型不揮発性メモリの製造方法を、図45(a)乃至図46(d)を参照して説明する。図45(a)、図45(c)、図45(e)、図46(a)、図46(c)と、図451(b)、図45(d)、図45(f)、図46(b)、図46(d)とは、それぞれ直交する断面を表している。

次に、本発明の第4実施形態によるMONOS型不揮発性メモリの製造方法を、図47(a)乃至図48(d)を参照して説明する。図47(a)、図47(c)、図47(e)、図48(a)、図48(c)と、図47(b)、図47(d)、図47(f)、図48(b)、図48(d)とは、それぞれ直交する断面を表している。

2a n型ソース領域、

2b n型ドレイン領域

3 トンネル絶縁膜

4 電荷蓄積膜

5 電極間絶縁膜

6 制御ゲート電極

7 シリコン酸化膜

8 低誘電率(low−k)層

9 高誘電率(high−k)層

22 トンネル絶縁膜

23 浮遊電極

24 マスク材

25 素子分離溝

26 シリコン酸化膜

27 電極間絶縁膜

28 制御電極(n+多結晶シリコン層)

29 WSi層

30 電極側壁酸化膜(シリコン酸化膜)

31 ソース/ドレイン拡散層

32 層間絶縁膜

33 トンネル絶縁膜

34 シリコン窒化膜

35 ブロック絶縁膜(HfAlO膜)

Claims (11)

- 半導体基板と、

前記半導体基板に離間して形成されたソース領域およびドレイン領域と、

前記ソース領域と前記ドレイン領域との間の前記半導体基板上に形成された第1の絶縁膜であって、第1の絶縁層と、前記第1の絶縁層上に形成され前記第1の絶縁層より誘電率が高く、母材と異なる元素が添加されることにより形成される、ホールの捕獲および放出をする第1のサイトを有している第2の絶縁層とを備え、前記第1のサイトは前記半導体基板を構成する材料のフェルミレベルよりも低いレベルにある第1の絶縁膜と、

前記第1の絶縁膜上に形成された電荷蓄積膜と、

前記電荷蓄積膜上に形成された第2の絶縁膜と、

前記第2の絶縁膜上に形成された制御ゲート電極と、

を有する記憶素子を備えたことを特徴とする不揮発性半導体記憶装置。 - 電荷保持状態で要求される条件として、前記第1の絶縁膜に印加される第1の電界における前記第1の絶縁膜のリーク電流をJlow以下とするとき、前記第1の絶縁層、前記第2の絶縁層の各単層においてリーク電流をJlow以下にするのに必要な物理膜厚をそれぞれT1,low、T2,lowとし、

消去時で要求される条件として、前記第1の絶縁膜に印加される第2の電界Ehighにおける前記第1の絶縁膜のリーク電流をJhigh以上とするとき、この条件に最低限必要な前記第1の絶縁層の層厚をT1,highとし、

前記第1および第2の絶縁層のそれぞれの誘電率をε1,ε2とし、シリコン酸化物の誘電率をεoxとすると、前記第1の絶縁層および前記第2の絶縁層を積層したときのそれぞれの物理膜厚をT1(nm)、T2(nm)としたとき、下記3つの不等式

T2≧−(T2,low/T1,low)×T1+T2,low

T1≧T1,high

T1×εox/ε1+ T2×εox/ε2≦ 8

を満たす範囲に前記第1の絶縁層および前記第2の絶縁層のそれぞれの物理膜厚が存在することを特徴とする請求項1記載の不揮発性半導体記憶装置。 - 前記第1の絶縁層が酸化シリコン層であり、かつ

前記第2の絶縁層がハフニア層であるときの前記第1のサイトは、前記ハフニア層の価電子帯の上端から0eVより大きく、2.2eV未満の範囲にあり、

前記第2の絶縁層がアルミナ層であるときの前記第1のサイトは、前記アルミナ層の価電子帯の上端から1.5eV以上、4.1eV以下の範囲にあり、

前記第2の絶縁層が酸化ランタン層であるときの前記第1のサイトは、前記酸化ランタン層の価電子帯の上端から0.1eV以上1.9eV未満の範囲にあり、

前記第2の絶縁層がハフニウムシリケート層であるときの前記第1のサイトは、前記ハフニウムシリケート層の価電子帯の上端から0.1eVより大きく2.9eV以下の範囲にあり、

前記第2の絶縁層がランタンアルミネート層であるときの前記第1のサイトは、前記ランタンアルミネート層の価電子帯の上端から0eVより大きく1.9eV未満の範囲にあり、

前記第2の絶縁層がハフニウムアルミネート層であるときの前記第1のサイトは、前記ハフニウムアルミネート層の価電子帯の上端から0.1eVより大きく2.1eV以下の範囲にあり、

前記第2の絶縁層がランタンハフネート層であるときの前記第1のサイトは、前記ランタンハフネート層の価電子帯の上端から0.1eV以上1.7eV以下の範囲にある

ことを特徴とする請求項1または2記載の不揮発性半導体記憶装置。 - 前記半導体基板の価電子帯の上端と前記第2の絶縁層の価電子帯の上端との差であるバンドオフセットΔEVは、1.8eV〜4.9eVの範囲にあることを特徴とする請求項1乃至3のいずれかに記載の不揮発性半導体記憶装置。

- 前記第1の絶縁膜は、EOTが1.02nm〜5nmの範囲にあることを特徴とする請求項1乃至4のいずれかに記載の不揮発性半導体記憶装置。

- 前記電荷蓄積膜は、トラップ絶縁膜であることを特徴とする請求項1乃至5のいずれかに記載の不揮発性半導体記憶装置。

- 前記電荷蓄積膜は、浮遊ゲート電極であることを特徴とする請求項1乃至5のいずれかに記載の不揮発性半導体記憶装置。

- 前記第1の絶縁膜は、前記ホールの捕獲および放出をするサイトが膜面方向において部分的に分布していることを特徴とする請求項1乃至7のいずれかに記載の不揮発性半導体記憶装置。

- 半導体基板と、

前記半導体基板に離間して形成されたソース領域およびドレイン領域と、

前記ソース領域と前記ドレイン領域との間の前記半導体基板上に形成され、母材と異なる元素が添加されることにより形成される、ホールの捕獲および放出をするサイトを有し前記ホールの捕獲および放出をするサイトは前記半導体基板を構成する材料の表面におけるフェルミレベルよりも低いレベルにある単一の層である第1の絶縁膜と、

前記第1の絶縁膜上に形成された電荷蓄積膜と、

前記電荷蓄積膜上に形成された第2の絶縁膜と、

前記第2の絶縁膜上に形成された制御ゲート電極と、

を有する記憶素子を備えたことを特徴とする不揮発性半導体記憶装置。 - 前記第1の絶縁膜は、

ハフニウムシリケート層であるとき前記サイトは前記ハフニウムシリケート層の価電子帯の上端から0.1eV以上2.9eV以下の範囲にあり、

ハフニウムアルミネート層であるとき前記サイトは前記ハフニウムアルミネート層の価電子帯の上端から0.1eV以上1.7eV以下の範囲にあり、

ことを特徴とする請求項9記載の不揮発性半導体記憶装置。 - 前記第1の絶縁膜に添加される元素は、Cr、Mn、V、Ru、Tc、Osから選択された少なくとも1つであることを特徴とする請求項1乃至10のいずれかに記載の不揮発性半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008227418A JP5361294B2 (ja) | 2008-09-04 | 2008-09-04 | 不揮発性半導体記憶装置 |

| US12/403,493 US8154072B2 (en) | 2008-09-04 | 2009-03-13 | Nonvolatile semiconductor memory apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008227418A JP5361294B2 (ja) | 2008-09-04 | 2008-09-04 | 不揮発性半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010062387A true JP2010062387A (ja) | 2010-03-18 |

| JP5361294B2 JP5361294B2 (ja) | 2013-12-04 |

Family

ID=41724013

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008227418A Expired - Fee Related JP5361294B2 (ja) | 2008-09-04 | 2008-09-04 | 不揮発性半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8154072B2 (ja) |

| JP (1) | JP5361294B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012109564A (ja) * | 2010-11-08 | 2012-06-07 | Imec | フローティングゲートメモリ構造の製造方法 |

| US9087910B2 (en) | 2012-09-06 | 2015-07-21 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method of the same |

| US9935122B2 (en) | 2015-09-10 | 2018-04-03 | Toshiba Memory Corporation | Nonvolatile semiconductor memory device having electron scattering and electron accumulation capacities in charge accumulation layer |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8878363B2 (en) * | 2009-06-26 | 2014-11-04 | Intel Corporation | Fermi-level unpinning structures for semiconductive devices, processes of forming same, and systems containing same |

| JPWO2011055433A1 (ja) | 2009-11-04 | 2013-03-21 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP5378255B2 (ja) * | 2010-02-02 | 2013-12-25 | 株式会社東芝 | 不揮発性半導体記憶装置および不揮発性半導体記憶装置の駆動方法 |

| JP2013058592A (ja) | 2011-09-08 | 2013-03-28 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2021125594A (ja) * | 2020-02-06 | 2021-08-30 | キオクシア株式会社 | 半導体記憶装置及びその製造方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06169083A (ja) * | 1992-11-30 | 1994-06-14 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JPH10247692A (ja) * | 1997-03-04 | 1998-09-14 | Sony Corp | 不揮発性記憶素子 |

| JP2002289709A (ja) * | 2001-03-28 | 2002-10-04 | Toshiba Corp | 半導体記憶素子 |

| JP2004336044A (ja) * | 2003-04-30 | 2004-11-25 | Samsung Electronics Co Ltd | ゲート積層物にoha膜を備える不揮発性半導体メモリ装置及びその製造方法 |

| JP2006114902A (ja) * | 2004-10-08 | 2006-04-27 | Samsung Electronics Co Ltd | 複数層のトンネリング障壁層を備える不揮発性メモリ素子及びその製造方法 |

| JP2007053171A (ja) * | 2005-08-16 | 2007-03-01 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JP2007294845A (ja) * | 2006-03-31 | 2007-11-08 | Toshiba Corp | 半導体装置およびその製造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3357861B2 (ja) | 1998-06-04 | 2002-12-16 | 株式会社東芝 | Mis半導体装置及び不揮発性半導体記憶装置 |

| JP2006005006A (ja) * | 2004-06-15 | 2006-01-05 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JP4976796B2 (ja) * | 2006-09-25 | 2012-07-18 | 株式会社東芝 | 半導体装置 |

| JP4314259B2 (ja) * | 2006-09-29 | 2009-08-12 | 株式会社東芝 | 不揮発性半導体メモリ |

| JP4357526B2 (ja) | 2006-12-08 | 2009-11-04 | 株式会社東芝 | 不揮発性半導体メモリ装置およびその製造方法 |

| JP4372174B2 (ja) * | 2007-03-28 | 2009-11-25 | 株式会社東芝 | 不揮発性半導体メモリ及びその製造方法 |

| JP4374037B2 (ja) * | 2007-03-28 | 2009-12-02 | 株式会社東芝 | 不揮発性半導体メモリ及びその製造方法 |

| JP2009231373A (ja) * | 2008-03-19 | 2009-10-08 | Toshiba Corp | 不揮発性半導体記憶装置 |

-

2008

- 2008-09-04 JP JP2008227418A patent/JP5361294B2/ja not_active Expired - Fee Related

-

2009

- 2009-03-13 US US12/403,493 patent/US8154072B2/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06169083A (ja) * | 1992-11-30 | 1994-06-14 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JPH10247692A (ja) * | 1997-03-04 | 1998-09-14 | Sony Corp | 不揮発性記憶素子 |

| JP2002289709A (ja) * | 2001-03-28 | 2002-10-04 | Toshiba Corp | 半導体記憶素子 |

| JP2004336044A (ja) * | 2003-04-30 | 2004-11-25 | Samsung Electronics Co Ltd | ゲート積層物にoha膜を備える不揮発性半導体メモリ装置及びその製造方法 |

| JP2006114902A (ja) * | 2004-10-08 | 2006-04-27 | Samsung Electronics Co Ltd | 複数層のトンネリング障壁層を備える不揮発性メモリ素子及びその製造方法 |

| JP2007053171A (ja) * | 2005-08-16 | 2007-03-01 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JP2007294845A (ja) * | 2006-03-31 | 2007-11-08 | Toshiba Corp | 半導体装置およびその製造方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012109564A (ja) * | 2010-11-08 | 2012-06-07 | Imec | フローティングゲートメモリ構造の製造方法 |

| US9087910B2 (en) | 2012-09-06 | 2015-07-21 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method of the same |

| US9935122B2 (en) | 2015-09-10 | 2018-04-03 | Toshiba Memory Corporation | Nonvolatile semiconductor memory device having electron scattering and electron accumulation capacities in charge accumulation layer |

Also Published As

| Publication number | Publication date |

|---|---|

| US8154072B2 (en) | 2012-04-10 |

| JP5361294B2 (ja) | 2013-12-04 |

| US20100052035A1 (en) | 2010-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9590117B2 (en) | Nonvolatile semiconductor memory device | |

| US11785774B2 (en) | Semiconductor device and method of manufacturing the same | |

| KR100858758B1 (ko) | 불휘발성 반도체 기억 장치 | |

| US7902588B2 (en) | Nonvolatile semiconductor memory device and method for manufacturing the same | |

| JP5361294B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2006005006A (ja) | 不揮発性半導体メモリ装置 | |

| US7943984B2 (en) | Nonvolatile semiconductor memory apparatus | |

| JP5150606B2 (ja) | 不揮発性半導体記憶装置 | |

| US20210083069A1 (en) | Semiconductor device and method for manufacturing the same | |

| CN101026193A (zh) | 非易失性半导体存储装置 | |

| JP2009170929A (ja) | 不揮発性半導体メモリ装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130614 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130620 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130806 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130903 |

|

| LAPS | Cancellation because of no payment of annual fees |