JP2010059511A - 直流電源装置 - Google Patents

直流電源装置 Download PDFInfo

- Publication number

- JP2010059511A JP2010059511A JP2008227865A JP2008227865A JP2010059511A JP 2010059511 A JP2010059511 A JP 2010059511A JP 2008227865 A JP2008227865 A JP 2008227865A JP 2008227865 A JP2008227865 A JP 2008227865A JP 2010059511 A JP2010059511 A JP 2010059511A

- Authority

- JP

- Japan

- Prior art keywords

- sample

- current

- output

- time

- command signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Inverter Devices (AREA)

Abstract

【解決手段】商用電源を整流する整流器と、この整流器の出力を交流に変換する半導体スイッチにより構成したインバータと、インバータの出力を降圧する変圧器と、変圧器の二次出力を整流するダイオードとから構成される直流電源装置において、変圧器の一次電流を検出する変流器と、変流器による電流検出信号をサンプルホールドする2個1組としたサンプルホールド回路11a、11bと、サンプルホールド回路11a、11bの出力の絶対値の平均値を算出する平均値回路14と、平均値回路14の出力をサンプルホールドするサンプルホールド回路15と、各サンプルホールド回路にサンプルホールド指令信号を与えるタイミング回路を設けた。

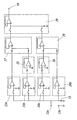

【選択図】図4

Description

図1は本発明の構成を示す主回路の結線図であって、第一の整流回路である整流器1とコンデンサ2により交流入力端子3から供給される交流電力を直流電力に変換する直流電源が設けてある。直流電源のプラス極には半導体スイッチ4a、4bのプラス極が接続してあり、該半導体スイッチ4a、4bのマイナス極にはそれぞれマイナス極を直流電源のマイナス極に接続した半導体スイッチ5a、5bのプラス極が接続してある。これらの半導体スイッチ4a、4b、5a、5bは単相インバータを構成する。

2 コンデンサ

3 交流入力端子

4a、4b、5a、5b 半導体スイッチ

6 変圧器

7a、7b ダイオード

8a、8b 直流出力端子

9 変流器

10 制御装置

11a、11b サンプルホールド回路

12a、12b 電流信号入力端子

13 終端抵抗

14 平均値回路

15 サンプルホールド回路

16 電流信号出力端子

17 コンパレータ

18 波形整形回路

19a、19b 電圧信号入力端子

20 検出信号出力端子

21、22 極性反転回路

23a、23b、24a、24b サンプルホールド回路

25、26 極性反転回路

27、28 平均値回路

29 サンプルホールド回路

Claims (9)

- 商用電源を整流する第一の整流回路と、この第一の整流回路の出力を交流に変換する単相のインバータと、インバータの出力を降圧する変圧器と、変圧器の二次出力を整流する第二の整流回路とから構成される直流電源装置において、変圧器の一次電流を検出する変流器と、変流器による電流検出信号をサンプルホールドする2個1組とした1組または2組のサンプルホールド手段と、1組2個のサンプルホールド手段の出力の絶対値の平均値をそれぞれ算出してその平均値を記憶する平均値記憶手段と、第二の整流回路の転流が終わった転流終了時点において前記の組としたサンプルホールド手段の一方に、インバータを構成する半導体スイッチがオフになったターンオフ時点において組としたサンプルホールド手段の他方にそれぞれサンプルホールド指令信号を与え、インバータを構成する半導体スイッチがオフになっている間のオフ中時点において平均値記憶手段に記憶指令信号を与える指令信号発生手段とを設け、平均値記憶手段の出力信号の絶対値を直流電源装置の直流出力電流に比例する信号とすることを特徴とする直流電源装置。

- 指令信号発生手段を、インバータが出力する交流の一方の極性の半サイクルの間の転流終了時点とターンオフ時点とにおいて組としたサンプルホールド手段の一方と他方にサンプルホールド指令信号を与え、同じ半サイクルの間のオフ中時点において平均値記憶手段に記憶指令信号を与えるものとしたことを特徴とする請求項1に記載の直流電源装置。

- 指令信号発生手段を、インバータが出力する交流の一方の極性の半サイクルの間のターンオフ時点において組としたサンプルホールド手段の一方に、後続する半サイクルの間の転流終了時点とオフ中時点とにおいて組としたサンプルホールド手段の他方と平均値記憶手段に、それぞれサンプルホールド指令信号及び記憶指令信号を与えるものとしたことを特徴とする請求項1に記載の直流電源装置。

- 指令信号発生手段を、インバータが出力する交流の一方の極性の半サイクルの間の転流終了時点において組としたサンプルホールド手段の一方に、後続する半サイクルの間のターンオフ時点とオフ中時点とにおいて組としたサンプルホールド手段の他方と平均値記憶手段に、それぞれサンプルホールド指令信号及び記憶指令信号を与えるものとしたことを特徴とする請求項1に記載の直流電源装置。

- 指令信号発生手段を、インバータが出力する交流の各半サイクルの間の転流終了時点とターンオフ時点とにおいて組としたサンプルホールド手段の一方と他方に、同じ半サイクルのオフ中時点において平均値記憶手段に、それぞれサンプルホールド指令信号及び記憶指令信号を与えるものとしたことを特徴とする請求項1に記載の直流電源装置。

- 指令信号発生手段を、インバータが出力する交流の一方の極性の半サイクルの間のターンオフ時点において一方の組としたサンプルホールド手段の一方に、後続する半サイクルの間の転流終了時点とオフ中時点とにおいて一方の組としたサンプルホールド手段の他方と平均値記憶手段に、インバータが出力する交流の他方の極性の半サイクルの間のターンオフ時点において他方の組としたサンプルホールド手段の一方に、後続する半サイクルの間の転流終了時点とオフ中時点とにおいて他方の組としたサンプルホールド手段の他方と平均値記憶手段に、それぞれサンプルホールド指令信号及び記憶指令信号を与えるものとしたことを特徴とする請求項1に記載の直流電源装置。

- 指令信号発生手段を、インバータが出力する交流の一方の極性の半サイクルの間の転流終了時点において一方の組としたサンプルホールド手段の一方に、後続する半サイクルの間のターンオフ時点とオフ中時点とにおいて一方の組としたサンプルホールド手段の他方と平均値記憶手段に、インバータが出力する交流の他方の極性の半サイクルの間の転流終了時点において他方の組としたサンプルホールド手段の一方に、後続する半サイクルの間のターンオフ時点とオフ中時点とにおいて他方の組としたサンプルホールド手段の他方と平均値記憶手段に、それぞれサンプルホールド指令信号及び記憶指令信号を与えるものとしたことを特徴とする請求項1に記載の直流電源装置。

- 商用電源を整流する第一の整流回路と、この整流器の出力を交流に変換する単相のインバータと、インバータの出力を降圧する変圧器と、変圧器の二次出力を整流する第二の整流回路とから構成される直流電源装置において、変圧器の一次電流を検出する変流器と、変流器による電流検出信号をサンプルホールドするサンプルホールド手段と、第二の整流回路の転流終了時点からインバータを構成する半導体スイッチがオフになるまでの間の中間の時点でサンプルホールド指令信号をサンプルホールド手段に与える指令信号発生手段とを設け、サンプルホールド手段の出力信号を直流電源装置の直流出力電流に比例する信号とすることを特徴とする直流電源装置。

- 第二の整流回路の出力電圧の立ち上がりを検出することにより第二の整流回路の転流期間の終了を検出する検出手段を設けたことを特徴とする請求項1ないし8のいずれかに記載の直流電源装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008227865A JP5565893B2 (ja) | 2008-09-05 | 2008-09-05 | 直流電源装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008227865A JP5565893B2 (ja) | 2008-09-05 | 2008-09-05 | 直流電源装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013223183A Division JP5643951B2 (ja) | 2013-10-28 | 2013-10-28 | 直流電源装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010059511A true JP2010059511A (ja) | 2010-03-18 |

| JP5565893B2 JP5565893B2 (ja) | 2014-08-06 |

Family

ID=42186624

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008227865A Active JP5565893B2 (ja) | 2008-09-05 | 2008-09-05 | 直流電源装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5565893B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103001506A (zh) * | 2012-11-13 | 2013-03-27 | 东莞市威力固电路板设备有限公司 | 电路板盲孔电镀的电源电路 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55110797A (en) * | 1979-02-16 | 1980-08-26 | Chuo Seisakusho:Kk | Apparatus for monitoring anode cage electric current of electroplating tank |

| JPS61230289A (ja) * | 1985-04-05 | 1986-10-14 | 株式会社東芝 | 誘導加熱調理器 |

| JPH0538158A (ja) * | 1991-07-25 | 1993-02-12 | Fuji Electric Co Ltd | 直流電源装置 |

| JPH099212A (ja) * | 1995-06-21 | 1997-01-10 | Toshiba Corp | ディスパーサル信号除去回路 |

| JP2002030497A (ja) * | 2000-07-11 | 2002-01-31 | Chuo Seisakusho Ltd | 高速パルス電源装置 |

| JP2003061357A (ja) * | 2001-08-17 | 2003-02-28 | Sansha Electric Mfg Co Ltd | メッキ用電源装置 |

-

2008

- 2008-09-05 JP JP2008227865A patent/JP5565893B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55110797A (en) * | 1979-02-16 | 1980-08-26 | Chuo Seisakusho:Kk | Apparatus for monitoring anode cage electric current of electroplating tank |

| JPS61230289A (ja) * | 1985-04-05 | 1986-10-14 | 株式会社東芝 | 誘導加熱調理器 |

| JPH0538158A (ja) * | 1991-07-25 | 1993-02-12 | Fuji Electric Co Ltd | 直流電源装置 |

| JPH099212A (ja) * | 1995-06-21 | 1997-01-10 | Toshiba Corp | ディスパーサル信号除去回路 |

| JP2002030497A (ja) * | 2000-07-11 | 2002-01-31 | Chuo Seisakusho Ltd | 高速パルス電源装置 |

| JP2003061357A (ja) * | 2001-08-17 | 2003-02-28 | Sansha Electric Mfg Co Ltd | メッキ用電源装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103001506A (zh) * | 2012-11-13 | 2013-03-27 | 东莞市威力固电路板设备有限公司 | 电路板盲孔电镀的电源电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5565893B2 (ja) | 2014-08-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5643951B2 (ja) | 直流電源装置 | |

| US10574135B2 (en) | Zero current detection circuit for bridgeless totem pole power factor correction converter and bridgeless totem pole power factor correction converter | |

| JP5974674B2 (ja) | スイッチング電源装置 | |

| US9917503B2 (en) | Overcurrent protection circuit and power factor correction circuit comprising the same | |

| JP6607495B2 (ja) | 電力変換装置 | |

| US10186983B2 (en) | Ideal diode bridge rectifying circuit and control method | |

| US9543836B2 (en) | Control device of a power conversion circuit | |

| JP2006109546A (ja) | 直流電源装置 | |

| JP5770364B2 (ja) | スイッチング電源回路、及びled照明装置 | |

| KR101985385B1 (ko) | 스위칭 전원 장치 및 그것을 구비한 광조사 장치 | |

| JP2017034829A (ja) | 電力変換装置 | |

| JP2015122946A (ja) | 同期整流器及びそれを制御する方法 | |

| JP6024356B2 (ja) | Ac−dcコンバータ | |

| JP2013222978A (ja) | パルス信号出力回路 | |

| JP2015070750A (ja) | 電力変換装置 | |

| JP5565893B2 (ja) | 直流電源装置 | |

| JP2013176218A (ja) | 電源制御装置 | |

| JP7300278B2 (ja) | スイッチング電源用pwm制御装置 | |

| JP4925339B2 (ja) | 高速反転パルス電源装置 | |

| KR102642655B1 (ko) | 스위칭 전원의 역률 개선용 pwm 제어 장치 | |

| JP4964106B2 (ja) | 高速パルス電源装置 | |

| JP2013062916A (ja) | 電力変換装置 | |

| CN113950791A (zh) | 用于驱动led负载的同步反激转换器 | |

| JP5927635B2 (ja) | 高速反転パルス電源装置 | |

| US10263540B2 (en) | Suppression of a DC component in a transformer of a voltage converter |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110520 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130325 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130913 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131028 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140613 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140613 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5565893 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |