JP2010056620A - ドライバ回路 - Google Patents

ドライバ回路 Download PDFInfo

- Publication number

- JP2010056620A JP2010056620A JP2008216548A JP2008216548A JP2010056620A JP 2010056620 A JP2010056620 A JP 2010056620A JP 2008216548 A JP2008216548 A JP 2008216548A JP 2008216548 A JP2008216548 A JP 2008216548A JP 2010056620 A JP2010056620 A JP 2010056620A

- Authority

- JP

- Japan

- Prior art keywords

- pull

- circuit

- resistor circuit

- output terminal

- resistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Logic Circuits (AREA)

- Dc Digital Transmission (AREA)

- Electronic Switches (AREA)

Abstract

【解決手段】第1のプルアップ抵抗回路P41、第3のプルアップ抵抗回路P43、第1のプルダウン抵抗回路N41、第3のプルダウン抵抗回路N43の抵抗値を第1の制御信号(SDATAP、SDATAM、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMP)に応じて変化させ、第2のプルアップ抵抗回路P42、第4のプルアップ抵抗回路P44、第2のプルダウン抵抗回路N42、第4のプルダウン抵抗回路N44の抵抗値を第2の制御信号(EMPHPP、EMPHPMN、EMPHPN、EMPHMP)に応じて変化させる

【選択図】図2

Description

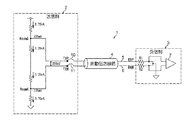

図1はPCI−ExPRess gen2の高速シリアル通信システムの構成例を示す回路図である。

図1に示されるように、高速シリアル通信システム1は、送信側回路2、受信側回路3、及び差動伝送線路4を備える。差動伝送線路4は、送信側回路2と受信側回路3との間に設けられた往路伝送線路5と復路伝送線路6とにより構成されている。受信側回路3は、受信側レシーブ回路7と、差動伝送線路4の終端抵抗である2つの抵抗R1、R2を備える。受信側レシーブ回路7の2つの入力端は差動伝送線路4に接続されている。

各抵抗R1、R2は、2つの接続部RXP、RXMの間で直列に接続され、各抵抗R1、R2の接続部は、接地電圧GNDに接続されている。

送信側回路2は、デジタル回路8とドライバ回路9とを備える。ドライバ回路9の2つの出力端「TXP」、「TXM」は、対応するワイヤボンディング10、11を介して往路伝送線路5及び復路伝送線路6にそれぞれ接続されている。デジタル回路8は、相反する信号レベルを有する対となる制御信号12をドライバ回路9にそれぞれ出力する。ドライバ回路9は、デジタル回路8からそれぞれ出力された制御信号12を低振幅のアナログ差動信号に変換して対応するワイヤボンディング10及びワイヤボンディング11に出力する。

送信側回路2は、差動伝送線路4を介して、アナログ差動信号を受信側回路3に送信する。そして、その差動信号は、受信側レシーブ回路7に入力される。各抵抗R1,R2は、受信側回路3におけるインピーダンス整合用の終端抵抗であり、差動伝送線路4上で伝送される差動信号の電圧振幅は、各抵抗R1,R2の抵抗値によって決まる。各抵抗R1,R2の抵抗値はそれぞれ50Ωである。インピーダンス整合は、差動伝送線路4上において、低振幅の差動信号を送受信する際に信号品質を良好なものにするために必要とされる。

また、特許文献2の図1には、IC内部終端用の各終端端子を分離し、それぞれの端子と実装基板あるいはパッケージリードとが接続されるようにワイヤを配置することで、実装ごとに出力端子のワイヤ長あるいはワイヤの形状が異なった場合でも、インダクタピーキーング量あるいは出力整合を最適化することができるドライバ回路が記載されている。

また特許文献2に記載されたドライバ回路では、データパターンによるインピーダンスの変動には対応できない。さらに、従来電源パッドが1つで済むところ、電源パッドを2つ配置しているため(P3、P4)、面積の増加につながる。

本発明は、上述の問題に鑑みてなされたものであり、高速なデータパターンの時のみ受動素子で周波数特性を改善して振幅にエンファシスをかけ、高速でないデータパターンは抵抗のみで50Ω終端することで、所望の振幅を得ることが可能な送信側ドライバ回路を提供することを目的とする。

請求項3に記載の発明は、前記第1乃至第4のプルアップ抵抗回路及びプルダウン抵抗回路は、スイッチング素子と抵抗とを直列に接続してなる部分抵抗回路を備え、前記第1のプルアップ抵抗回路は、前記第1の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第3のプルアップ抵抗回路は、前記第2の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第1のプルダウン抵抗回路は、前記第1の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第3のプルダウン抵抗回路は、前記第2の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第2のプルアップ抵抗回路は、前記第1の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第4のプルアップ抵抗回路は、前記第2の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第2のプルダウン抵抗回路は、前記第1の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第4のプルダウン抵抗回路は、前記第2の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、前記第1のプルアップ抵抗回路と前記第3のプルアップ抵抗回路と前記第1のプルダウン抵抗回路と前記第3のプルダウン抵抗回路は、該各抵抗回路に含まれるそれぞれのスイッチング素子が前記第1の制御信号に応じてオン又はオフすることにより抵抗値がそれぞれ変化し、前記第2のプルアップ抵抗回路と前記第4のプルアップ抵抗回路と前記第2のプルダウン抵抗回路と前記第4のプルダウン抵抗回路は、該各抵抗回路に含まれるそれぞれのスイッチング素子が前記第2の制御信号に応じてオン又はオフすることにより抵抗値がそれぞれ変化する請求項1または2に記載のドライバ回路を特徴とする。

請求項5に記載の発明は、前記受動素子はインダクタンスである請求項1乃至4の何れか一項に記載のドライバ回路を特徴とする。

請求項6に記載の発明は、前記受動素子はキャパシタンスである請求項1乃至4の何れか一項に記載のドライバ回路を特徴とする。

<第一の実施形態>

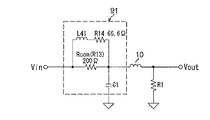

図2は、第一の実施形態に係る送信側ドライバ回路91の詳細な構成例を示す回路図である。図2に示されるように、ドライバ回路91は、12個のインバータ400乃至411と、第1のプルアップ抵抗回路P41と第1のプルダウン抵抗回路N41、出力端TXP(第1の出力端子)にインダクタンス(第1の受動素子)L41を介して接続される第2のプルアップ回路P42と第2のプルダウン抵抗回路N42と、第3のプルアップ抵抗回路P43と第3のプルダウン抵抗回路N43、出力端TXM(第2の出力端子)にインダクタンス(第2の受動素子)L42を介して接続される第4のプルアップ回路P44と第4のプルダウン抵抗回路N44とから構成される。

第1のプルダウン抵抗回路N41は、出力端TXPと所定のGNDとの間で並列に接続された4つの部分抵抗回路NR40乃至NR43を備える。ここで、部分抵抗回路NR40乃至NR43は全て同じ構成である。一例として、部分抵抗回路NR40は、直列に接続されたN型金属酸化膜電界効果トランジスタ(以下、「NMOSトランジスタ」という。)N411と抵抗R20とから構成されている。各NMOSトランジスタN411乃至N413のゲートは、インバータ405の出力端に接続され、NMOSトランジスタN414のゲートはインバータ404の出力端に接続されている。

第2のプルダウン抵抗回路は、出力端TXPとインダクタンスL41を介して、所定のGNDとの間で直列に接続された、NMOSトランジスタN421と抵抗R24とからなる部分抵抗回路NR44からなり、NMOSトランジスタN421のゲートはインバータ403の出力端と接続されている。

第3のプルアップ抵抗回路P43と第3のプルダウン抵抗回路N43は出力端TXMに直接に接続され、また第4のプルアップ抵抗回路P44と第4のプルダウン抵抗回路N44は出力端TXMとインダクタンスL42を介して接続されている。

また、各PMOSトランジスタP431乃至P433のゲートはインバータ406の出力端に接続され、PMOSトランジスタP434のゲートはインバータ407の出力端に接続され、PMOSトランジスタP441のゲートはインバータ408の出力端と接続されている。

また、各NMOSトランジスタN431乃至N433のゲートはインバータ411の出力端に接続され、NMOSトランジスタN434のゲートはインバータ410の出力端に接続され、NMOSトランジスタN441のゲートはインバータ409の出力端と接続されている。

そして、インバータ400乃至411には、デジタル回路8から出力される制御信号12(図1参照)を構成するデジタル信号DEMPHPP、SDATAP、EMPHPP、EMPHPN、SDATAP、DEMPHPN、DEMPHMP、SDATAM、EMPHMP、EMPHMN、SDATAM、DEMPHMNがそれぞれ入力される。

また、差動伝送線路4で伝送される高周波損失を防ぐために、差動信号の振幅を大きくして、S/N比をかせぐことが好ましい。なお、各抵抗R10乃至R13、R20乃至R23、R15乃至R18、R25乃至R28は200Ωで、R14、R24、R19、R29は66.6Ωである。

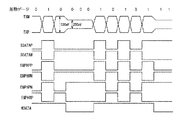

また、図3に示すSDATAP、SDATAM、EMPHPP、EMPHMN、EMPHPN、EMPHMP、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMPは、デジタル回路8からそれぞれ出力された対応する各デジタル信号の波形を示している。

ここで、シリアルデータ信号SDATAPとSDATAMの信号の組、ディエンファシス制御信号DEMPHPPとDEMPHMNの信号の組、ディエンファシス制御信号DEMPHPN及びDEMPHMPの信号の組は、それぞれ対を成す信号の組であり、これらの信号を第1の制御信号と表現する。また、エンファシス制御信号EMPHPPとEMPHPMNの信号の組、エンファシス制御信号EMPHPNとEMPHMPの信号の組は、それぞれ対を成すデジタル信号の組であり、これらの信号を第2の制御信号と表現する。

「差動データ」は、一対のシリアルデータ信号SDTAP、SDTAMに応じて差動伝送線路4に出力される差動データである。

プリエンファシス時にはSDATAPとEMPHPPとEMPHPNの信号レベルが一致し、SDATAMとEMPHMPとEMPHMNの信号レベルが一致する。

この時、DEMPHPPはLレベルにあり、インバータ400で反転された信号の電圧がPMOSトランジスタP411乃至P413の各ゲートに印加され、PMOSトランジスタP411乃至P413はオフになる。同様に、DEMPHPNはHレベルにあってNMOSトランジスタN411乃至N413をオフにし、DEMPHMPはLレベルにあってPMOSトランジスタP431乃至P433をオフにし、DEMPHMNはHレベルにあってNMOSトランジスタN431乃至N433をオフにする。すなわち、プリエンファシス時には、PMOSトランジスタP411乃至P413、P431乃至P433、NMOSトランジスタN411乃至N413、N431乃至N433がオフになる。

プリエンファシス時でかつ差動データが「1」の場合には、SDATAPとEMPHPPとEMPHPNはHレベルであり、SDATAMとEMPHMPとEMPHMNはLレベルである。

これにより、PMOSトランジスタP414、P421はオンし、NMOSトランジスタN414、N421はオフする。すなわち、出力端TXPはプルアップされる。

これにより、PMOSトランジスタP434、P441はオフし、NMOSトランジスタN434、N441はオンする。すなわち、出力端TXMはプルダウンされる。

プリエンファシス時でかつ差動データが「0」の場合には、SDATAPとEMPHPPとEMPHPNはLレベルであり、SDATAMとEMPHMPとEMPHMNはHレベルである。従って、差動データ「1」の時に比べると、各トランジスタのゲートに印加されるデジタル信号の電圧が反転するので、各トランジスタのオン、オフ関係も反転する。

これにより、PMOSトランジスタP414、P421はオフし、NMOSトランジスタN414、N421はオンする。すなわち、出力端TXPはプルダウンされる。また、PMOSトランジスタP434、P441はオンし、NMOSトランジスタN434、N441はオフする。すなわち、出力端TXMはプルアップされる。

ディエンファシス時には、EMPHPPはLレベルにあってPMOSトランジスタP421をオフにし、EMPHPNはHレベルにあってNMOSトランジスタN421をオフにする。また、EMPHMPはLレベルにあってPMOSトランジスタP441をオフにし、EMPHMNはHレベルにあってNMOSトランジスタN441をオフにする。すなわち、ディエンファシス時には、PMOSトランジスタP421、P441、NMOSトランジスタN421、N441がオフになる。

ディエンファシス時でかつ差動データが「1」の場合には、DEMPHPPはPMOSトランジスタP411乃至P413をオンにし、DEMPHPNはNMOSトランジスタN411乃至N413をオフにし、DEMPHMPはPMOSトランジスタP431乃至P433をオフにし、DEMPHMNはNMOSトランジスタN431乃至N433をオンにする。この時、NMOSトランジスタN414はオンで、PMOSトランジスタP434はオンである。従って、出力端TXPはプルアップされる。

ディエンファシス時でかつ差動データが「0」の場合には、DEMPHPPはPMOSトランジスタP411乃至P413をオフにし、DEMPHPNはNMOSトランジスタN411乃至N413をオンにし、DEMPHMPはPMOSトランジスタP431乃至P433をオンにし、DEMPHMNはNMOSトランジスタN431乃至N433をオフにする。この時、NMOSトランジスタN414をオフで、PMOSトランジスタP434はオフである。従って、出力端TXMはプルアップされる。

図4は、差動データ「1」かつプリエンファシス時の高速シリアル通信システム1の状態を説明する図である。

上述したように、差動データ「1」のプリエンファシス時には、部分抵抗回路PR40乃至PR42のPMOSトランジスタP411乃至P413がオフし、部分抵抗回路PR43のPMOSトランジスタP414はオンする。また、部分抵抗回路PR45乃至PR48のPMOSトランジスタのP431乃至P434がオフする。また、部分抵抗回路PR44のPMOSトランジスタP421がオンし、部分抵抗回路PR49のPMOSトランジスタP441はオフする。

これにより、出力端TXPと電源電圧Vccとの間で、抵抗R13(200Ω)とR14(66.6Ω)が並列に接続されるので、抵抗R13とR14の合成抵抗Rcom1の抵抗値は50Ωとなる。一方、出力端TXMとGNDとの間でR28(200Ω)とR29(66.6Ω)が並列に接続され、各抵抗R28乃至R29の合成抵抗Rcom2の抵抗値は50Ωとなる。ここで、電源電圧Vccを1Vとし、各合成抵抗Rcom1、Rcom2及び各終端抵抗R1、R2の分圧比を考慮すれば、出力端TXPと出力端TXMの電圧は、それぞれ750mV及び250mVであり、差動伝送線路4の電圧振幅は500mVである。また、この場合に、出力端TXPから出力端TXMに流れる定電流は5mAである。

また、差動データ「0」のプリエンファシス時は、出力端TXPと出力端TXMの電圧は、それぞれ250mV及び750mVとなる。なお、上述したように、各合成抵抗Rcom1及びRcom2はそれぞれ50Ωであり、終端抵抗のインピーダンス整合を実現している。

また、部分抵抗回路NR40乃至NR42のNMOSトランジスタN411乃至N413のトランジスタがオフし、部分抵抗回路NR43のNMOSトランジスタN414がオンする。また、部分抵抗回路NR45乃至NR47のNMOSトランジスタN431乃至N433がオンし、部分抵抗回路NR48のNMOSトランジスタN434がオフする。また、部分抵抗回路NR44のNMOSトランジスタN421がオフし、部分抵抗回路NR49のNMOSトランジスタN441がオフする。

このようにオンオフする抵抗の数を変えることで、合成抵抗を50Ωにして出力振幅の値を変えることが可能となる。

図7は、ドライバ回路91の動作を説明するための図である。出力端TXPが「1」でインダクタンスL41が0nHではない時の図を示している。プリエンファシス時には抵抗R14とインダクタンスL41がRcom(R13)に並列に接続される。インダクタンスL41の値によって、振幅が変化する。

このように本実施形態によれば、受動素子を介した抵抗回路のスイッチング素子を所望のデータパターンの時に制御することで、所望のデータパターン(本実施形態ではプリエンファシス時のみ)の振幅を改善することができる。更にDCの時の出力インピーダンスに影響を与えないドライバ回路を提供することができる。

また、並列に接続された部分抵抗回路のスイッチング素子をオン又はオフすることによって抵抗が変化するので、より低消費電力化が可能なドライバ回路を提供することができる。

本発明の第二の実施形態について、図面に基づいて説明する。

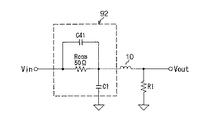

図9は、第二の実施形態に係る送信側ドライバ回路92の詳細な構成例を示す回路図である。本発明の第一の実施形態に係るドライバ回路91と異なる点は、インダクタンスL41の替わりにキャパシタンス(第1の受動素子)C41を備え、インダクタンスL42の替わりにキャパシタンス(第2の受動素子)C42を備え、抵抗R14、抵抗R24、抵抗R19、抵抗R29が排除された点にある。構成は実施例1とほぼ同様なので、詳細な説明を省略する。

次にドライバ回路92の動作を説明する。図10は、ドライバ回路92の動作を説明するためのタイミングチャートである。図10において、「TXP」、「TXM」は出力端TXP、TXMに出力された差動電圧の波形を示している。PCI−ExPRess gen2の高速通信シリアルシステムにおいて、プリエンファシス時の差動電圧の振幅が500mVの場合、それ以外のディエンファシス時の差動電圧は250mVである。

ここで、シリアルデータ信号SDATAPとSDATAMの信号の組、ディエンファシス制御信号DEMPHPPとDEMPHPNの信号の組は、それぞれ対を成す信号の組であり、これらの信号を第1の制御信号と表現する。また、エンファシス制御信号EMPHPPとEMPHPNの信号の組、エンファシス制御信号EMPHNMPとEMPHMNの信号の組は、それぞれ対を成す信号の組であり、これらの信号を第2の制御信号と表現する。

「差動データ」は、一対のシリアルデータ信号SDTAP、SDTAMに応じて差動伝送線路4に出力される差動データであり、SDATAPがLow(L)レベルで、かつSDATAMがHigh(H)レベルの時、差動データ「0」が出力される。SDATAMがLレベルで、SDATAPがHレベルの時、差動データ「1」が出力される。

プリエンファシス時にはSDATAPとEMPHPPの信号レベルが一致し、SDATAMとEMPHMPの信号レベルが一致する。

プリエンファシス時でかつ差動データが「1」の場合には、DEMPHPPとSDATAPとEMPHPPとEMPHPNはHレベルにあって、PMOSトランジスタP411乃至P414、P421をオンにする。また、NMOSトランジスタN411乃至N414、N421をオフにする。すなわち、出力端TXPはプルアップされる。

DEMPHMPとSDATAMとEMPHMPとEMPHMNはLレベルにあって、PMOSトランジスタP431乃至P434、P441をオフにする。また、NMOSトランジスタN431乃至N434、N441をオンにする。すなわち、出力端TXMはプルダウンされる。

プリエンファシス時でかつ差動データが「0」の場合には、DEMPHPPとSDATAPとEMPHPPとEMPHPNはLレベルにあって、PMOSトランジスタP411乃至P414、P421をオフにする。また、NMOSトランジスタN411乃至N414、N421をオンにする。すなわち、出力端TXPはプルダウンされる。

DEMPHMPとSDATAMとEMPHMPとEMPHMNはHレベルにあって、PMOSトランジスタP431乃至P434、P441をオンにする。また、NMOSトランジスタN431乃至N434、N441をオフにする。すなわち、出力端TXMはプルアップされる。

ディエンファシス時には、EMPHPPはLレベルにあってPMOSトランジスタP421をオフにし、EMPHPNはHレベルにあってNMOSトランジスタN421をオフにし、EMPHMPはLレベルにあってPMOSトランジスタP441をオフにし、EMPHMNはHレベルにあってPMOSトランジスタP441をオフにする。すなわち、ディエンファシス時には、PMOSトランジスタP421、P441、NMOSトランジスタN421、N441がオフになる。

ディエンファシス時でかつ差動データが「1」の場合には、DEMPHPPはPMOSトランジスタP411乃至P413をオンにし、NMOSトランジスタN411乃至N413をオフにする。この時、PMOSトランジスタP414はオフで、NMOSトランジスタN414はオンである。また、DEMPHMPはPMOSトランジスタP431乃至P433をオフにし、NMOSトランジスタN431乃至N433をオンにする。この時、PMOSトランジスタP434はオンで、NMOSトランジスタN434はオフである。従って、出力端TXPがプルアップされ、出力端TXMがプルダウンされる。

ディエンファシス時でかつ差動データが「0」の場合には、DEMPHPPはPMOSトランジスタP411乃至P413をオフにし、NMOSトランジスタN411乃至N413をオンにする。この時、PMOSトランジスタP414はオンで、NMOSトランジスタN414はオフである。また、DEMPHMPはPMOSトランジスタP431乃至P433をオンにし、NMOSトランジスタN431乃至N433をオフにする。この時、PMOSトランジスタP434はオフで、NMOSトランジスタN434はオンである。従って、出力端TXPがプルダウンされ、出力端TXMがプルアップされる。

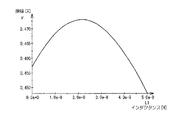

図12は、静電保護容量C1が1.2pF、ワイヤボンディング10が3nH相当で、キャパシタンスC41を0p〜5pFまで変化させた時のグラフである。縦軸が振幅(V)で、横軸は容量(F)を示している。キャパシタンスC41はプリエンファシス時のみ接続されるので、プリエンファシス時の振幅の改善をすることが可能である。DC時と同程度の振幅を得るには、キャパシタンスC41は1.5pFの容量が必要である。容量素子(受動素子)をインダクタンスからキャパシタンスにすることで、より大きく振幅を改善することが可能である。

このように本実施形態によれば、受動素子を介した抵抗回路のスイッチング素子を所望のデータパターンの時に制御することで、所望のデータパターン(本実施形態ではプリエンファシス時のみ)の振幅を改善することができる。更にDCの時の出力インピーダンスに影響を与えないドライバ回路を提供することができる。

また、並列に接続された部分抵抗回路のスイッチング素子をオン又はオフすることによって抵抗が変化するので、より低消費電力化が可能なドライバ回路を提供することができる。

図13は、第三の実施形態に係る送信側ドライバ回路93の詳細な構成例を示す回路図である。図13に示されるように、ドライバ回路93は9個のインバータ1400乃至1408と、第1のプルアップ抵抗回路P141と第1のプルダウン抵抗回路N141、出力端TXP(第1の出力端子)にインダクタンス(第1の受動素子)L141を介して接続される第2のプルアップ回路P142と第2のプルダウン抵抗回路と、第3のプルアップ抵抗回路P143と第3のプルダウン抵抗回路N143、出力端TXM(第2の出力端子)にインダクタンス(第2の受動素子)L142を介して接続される第4のプルアップ回路P144と第4のプルダウン抵抗回路N144と第5のプルダウン回路M141とから構成される。

第1のプルダウン抵抗回路N141は、出力端TXPと所定のGNDとの間で接続された部分抵抗回路NR141を備える。部分抵抗回路NR141は、直列に接続されたNMOSトランジスタN1411と抵抗R21とから構成されている。なお、本実施形態における回路では、出力端TXPと所定のGNDとの間で接続された部分抵抗回路は、部分抵抗回路NR141と同様の構成を有するため、以下その説明を省略する。NMOSトランジスタN1411のゲートは、インバータ1403の出力端に接続される。

第3のプルダウン抵抗回路は、出力端TXPと所定のGNDとの間で接続された部分抵抗回路NR143を備える。部分抵抗回路NR143に含まれるNMOSトランジスタN1431のゲートは、インバータ1407の出力端と接続される。

第2のプルアップ抵抗回路は、出力端TXPとインダクタンスL141を介して、所定の電源電圧Vccとの間で直列に接続された、部分抵抗回路PR142を備える。部分抵抗回路PR142に含まれるPMOSトランジスタP1421のゲートはインバータ1401の出力端と接続される。

第2のプルダウン抵抗回路は、出力端TXPとインダクタンスL141を介して、所定のGNDとの間で直列に接続された、部分抵抗回路NR142を備える。部分抵抗回路R142に含まれるNMOSトランジスタN1421のゲートは、インバータ1402の出力端と接続されている。

第4のプルダウン抵抗回路は、出力端TXMとインダクタンスL142を介して、所定のGNDとの間で直列に接続された、部分抵抗回路NR144を備える。部分抵抗回路NR144に含まれるNMOSトランジスタ、N1441のゲートはインバータ1406の出力端と接続されている。

本実施形態におけるドライバ回路93は、分流回路として働く第5のプルダウン抵抗回路M141を備える。第5のプルダウン抵抗回路M141は、出力端TXPと抵抗R31を介してNMOSトランジスタN1451と直列に接続され、出力端TXMと抵抗R32を介して、NMOSトランジスタN1451と直列に接続されている。抵抗R32は、抵抗R31が接続されていない方に接続されている。また、NMOSトランジスタN1451のゲートは、インバータ1408の出力端と接続される。

プリエンファシス時にはSDATAPとEMPHPPとEMPHPNの信号レベルが一致し、SDATAMとEMPHMPとEMPHMNの信号レベルが一致する。この時、MDATAはHレベルにあって、NMOSトランジスタN1451をオフにする。

ディエンファシス時にはEMPHPPはPMOSトランジスタP1421をオフにし、EMPHPNはNMOSトランジスタN1421をオフにし、EMPHMPはPMOSトランジスタP1441をオフにし、EMPHMNはNMOSトランジスタN1441をオフにし、MDATAはNMOSトランジスタN1451をオンにする。

部分抵抗回路PR142のPMOSトランジスタP1421がオフし、PR144のPMOSトランジスタP1441がオフする。

部分抵抗回路NR141とNR143のNMOSトランジスタN1411がオフし、部分抵抗回路NR143のNMOSトランジスタN1431がオンする。

部分抵抗回路NR142のNMOSトランジスタN1421がオフし、部分抵抗回路NR144のNMOSトランジスタN1441がオフする。

部分抵抗回路MR141(分流用部分抵抗回路)のNMOSトランジスタN1451がオンする。

トランジスタのサイズや抵抗を細分化し、オンオフする抵抗の数を変えることで、合成抵抗を50Ωにして出力振幅の値を変えることが可能となる。

尚、エンファシス時の構成は実施例1と等価なので、動作特性の説明は省略する。

本実施形態によれば、プリエンファシス時のみ振幅が改善され、且つDCのインピーダンスは50Ω整合が可能なドライバ回路を提供することができる。また、第一又は第二の実施形態に比べてスイッチング素子の個数が少なく、消費電流が小さいドライバ回路を提供可能にする。

図16は、本発明の第四の実施形態に係る送信側ドライバ回路94の詳細な構成例を示す回路図である。第三の実施形態に係るドライバ回路93と異なる点は、

インダクタンスL141、L142の替わりにキャパシタンスC171、C172を配置した点、出力端にキャパシタンスを介して接続される部分抵抗回路内に抵抗を備えていない点、第1のプルアップ抵抗回路と第1のプルダウン抵抗回路内の部分抵抗回路の数が異なる点にある。

図16に示されるように、ドライバ回路94は9個のインバータ1400乃至1408と、出力端TXPに接続される第1のプルアップ抵抗回路P141と第1のプルダウン抵抗回路N141と第2のプルアップ抵抗回路P171と第2のプルダウン抵抗回路N171と、出力端TXMに接続される第3のプルアップ抵抗回路P143と第3のプルダウン抵抗回路N143と第4のプルアップ抵抗回路P172と第4のプルダウン抵抗回路N172と、第5のプルダウン回路M141とを備える。

第1のプルダウン抵抗回路N141は、出力端TXPと所定のGNDとの間で接続された部分抵抗回路NR141を備える。部分抵抗回路PR141のPMOSトランジスタP1411のゲートはインバータ1400の出力端に接続され、部分抵抗回路NR141のNMOSトランジスタN1411のゲートは、インバータ1403の出力端に接続される。

第3のプルアップ抵抗回路P143は、出力端TXMと所定の電源電圧Vccとの間で接続された部分抵抗回路PR143を備える。

第3のプルダウン抵抗回路N143は、出力端TXMと所定のGNDとの間で接続された部分抵抗回路NR143を備える。部分抵抗回路PR143のPMOSトランジスタP1431のゲートはインバータ1404の出力端に接続され、部分抵抗回路NR143のNMOSトランジスタN1431のゲートは、インバータ1407の出力端に接続される。

第2のプルダウン抵抗回路N171は、出力端TXPと所定のGNDとの間で接続された部分抵抗回路NR142と、出力端TXPとキャパシタンスC171を介して、所定のGNDとの間で直列に接続された部分抵抗回路NR171とを備える。部分抵抗回路NR171は、NMOSトランジスタN1721からなる。部分抵抗回路NR142のNMOSトランジスタN1412と部分抵抗回路NR171のNMOSトランジスタN1721のゲートはインバータ1402の出力端と接続される。

第4のプルアップ抵抗回路P172は、出力端TXMと所定の電源電圧Vccとの間で接続された部分抵抗回路PR144と、出力端TXMとキャパシタンスC172(第2の受動素子)を介して所定の電源電圧Vccとの間で直列に接続された部分抵抗回路PR172とを備える。部分抵抗回路PR172は、PMOSトランジスタP1722からなる。PMOSトランジスタP1432とP1722のゲートはインバータ1405の出力端と接続されている。

第4のプルダウン抵抗回路N172は、出力端TXMと所定のGNDとの間で接続された部分抵抗回路NR144と、出力端TXMとキャパシタンスC172を介して所定のGNDとの間で直列に接続された部分抵抗回路NR172とを備える。部分抵抗回路NR172は、NMOSトランジスタN1722からなる。部分抵抗回路NR144のNMOSトランジスタN1432と部分抵抗回路NR172のNMOSトランジスタN1722のゲートはインバータ1406の出力端と接続される。

第5のプルダウン抵抗回路M141は、出力端TXPと抵抗R31を介してNMOSトランジスタN1451と直列に接続され、出力端TXMと抵抗R32を介して、NMOSトランジスタN1451と直列に接続されている。抵抗R32は、抵抗R31が接続されていない方に接続されている。また、NMOSトランジスタN1451のゲートは、インバータ1408の出力端と接続されている。

本実施形態によれば、プリエンファシス時のみ振幅が改善され、且つDCのインピーダンスは50Ω整合が可能なドライバ回路を提供することができる。また、本実施形態に係るドライバ回路は、第一又は第二の実施形態に係るドライバ回路より消費電流を小さくすることが可能である。

Claims (6)

- 差動信号を伝送する一対の伝送線路に接続された第1の出力端子と第2の出力端子とを備え、外部から入力された制御信号を前記差動信号に変換して前記第1の出力端子と第2の出力端子とに出力するドライバ回路において、

前記第1の出力端子は、第1のプルアップ抵抗回路を介して所定の電源電圧に接続されると共に、第1のプルダウン抵抗回路を介して接地電圧に接続され、第1の受動素子と第2のプルアップ抵抗回路を介して前記所定の電源電圧に接続されると共に、前記第1の受動素子と第2のプルダウン抵抗回路を介して前記接地電圧に接続され、

前記第2の出力端子は、第3のプルアップ抵抗回路を介して前記所定の電源電圧に接続されると共に、第3のプルダウン抵抗回路を介して前記接地電圧に接続され、第2の受動素子と第4のプルアップ抵抗回路を介して前記所定の電源電圧に接続されると共に、前記第4の受動素子と第4のプルダウン抵抗回路を介して前記接地電圧に接続され、

前記制御信号は第1の制御信号と第2の制御信号とを含み、

前記第1のプルアップ抵抗回路と前記第3のプルアップ抵抗回路と前記第1のプルダウン抵抗回路と前記第3のプルダウン抵抗回路は、前記第1の制御信号に応じて抵抗値がそれぞれ変化し、前記第2のプルアップ抵抗回路と前記第4のプルアップ抵抗回路と前記第2のプルダウン抵抗回路と前記第4のプルダウン抵抗回路は、前記第2の制御信号に応じて抵抗値がそれぞれ変化することを特徴とするドライバ回路。 - 前記第1の出力端子へ流れる電流、又は前記第2の出力端子へ流れる電流を分流する第5のプルダウン抵抗回路を備え、

前記制御信号は第3の制御信号を含み、

前記第5のプルダウン抵抗回路は、前記第3の制御信号に応じて抵抗値が変化することを特徴とする請求項1に記載のドライバ回路。 - 前記第1乃至第4のプルアップ抵抗回路及びプルダウン抵抗回路は、スイッチング素子と抵抗とを直列に接続してなる部分抵抗回路を備え、

前記第1のプルアップ抵抗回路は、前記第1の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第3のプルアップ抵抗回路は、前記第2の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第1のプルダウン抵抗回路は、前記第1の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第3のプルダウン抵抗回路は、前記第2の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第2のプルアップ抵抗回路は、前記第1の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第4のプルアップ抵抗回路は、前記第2の出力端子と前記所定の電源電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第2のプルダウン抵抗回路は、前記第1の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第4のプルダウン抵抗回路は、前記第2の出力端子と前記接地電圧との間に1又は複数の前記部分抵抗回路を並列に接続したものであり、

前記第1のプルアップ抵抗回路と前記第3のプルアップ抵抗回路と前記第1のプルダウン抵抗回路と前記第3のプルダウン抵抗回路は、該各抵抗回路に含まれるそれぞれのスイッチング素子が前記第1の制御信号に応じてオン又はオフすることにより抵抗値がそれぞれ変化し、

前記第2のプルアップ抵抗回路と前記第4のプルアップ抵抗回路と、前記第2のプルダウン抵抗回路と前記第4のプルダウン抵抗回路は、該各抵抗回路に含まれるそれぞれのスイッチング素子が前記第2の制御信号に応じてオン又はオフすることにより抵抗値がそれぞれ変化することを特徴とする請求項1または2に記載のドライバ回路。 - 前記第5のプルダウン抵抗回路は、少なくとも2つの抵抗でスイッチング素子を挟むように直列に接続してなる分流用部分抵抗回路を備え、

前記分流用部分抵抗回路の一端は前記第1の出力端子に接続され、他端は前記第2の出力端子に接続されるとともに、

前記第5のプルダウン抵抗回路は、前記第3の制御信号に応じて前記分流用部分抵抗回路のスイッチング素子がオン又はオフすることにより抵抗値が変化することを特徴とする請求項2及び3に記載のドライバ回路。 - 前記受動素子はインダクタンスであることを特徴とする請求項1乃至4の何れか一項に記載のドライバ回路。

- 前記受動素子はキャパシタンスであることを特徴とする請求項1乃至4の何れか一項に記載のドライバ回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216548A JP5540479B2 (ja) | 2008-08-26 | 2008-08-26 | ドライバ回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008216548A JP5540479B2 (ja) | 2008-08-26 | 2008-08-26 | ドライバ回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010056620A true JP2010056620A (ja) | 2010-03-11 |

| JP5540479B2 JP5540479B2 (ja) | 2014-07-02 |

Family

ID=42072127

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008216548A Expired - Fee Related JP5540479B2 (ja) | 2008-08-26 | 2008-08-26 | ドライバ回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5540479B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013046332A (ja) * | 2011-08-26 | 2013-03-04 | Renesas Electronics Corp | 半導体装置 |

| JP2015062296A (ja) * | 2010-12-14 | 2015-04-02 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | オンチップ電圧駆動型シングルエンド終端ドライバのためのプリエンファシス技法 |

| JP2015228554A (ja) * | 2014-05-30 | 2015-12-17 | ソニー株式会社 | 送信装置、受信装置、および通信システム |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01161943A (ja) * | 1987-12-18 | 1989-06-26 | Nec Corp | パルス伝送回路 |

| JPH02111126A (ja) * | 1988-10-19 | 1990-04-24 | Nec Corp | 伝送回路 |

| JP2000068816A (ja) * | 1998-06-05 | 2000-03-03 | Telefon Ab L M Ericsson | ディジタル信号をプリエンファシス伝送路経由で送信するための出力バッファ回路 |

| JP2004088693A (ja) * | 2002-08-29 | 2004-03-18 | Toshiba Corp | 差動データドライバー回路 |

| JP2006345532A (ja) * | 2005-06-09 | 2006-12-21 | Agilent Technol Inc | 信号整形回路 |

| JP2007036848A (ja) * | 2005-07-28 | 2007-02-08 | Ricoh Co Ltd | ドライバ回路 |

| JP2007124644A (ja) * | 2005-10-27 | 2007-05-17 | Internatl Business Mach Corp <Ibm> | 電子回路、該電子回路として構成された差分送信機、及び、自己直列終端送信機を形成する方法(振幅制御、プリ・エンファシス制御及びスルー・レート制御のためのセグメント化と振幅精度及び高電圧保護のための電圧調整とを有する自己直列終端シリアル・リンク送信機) |

| JP2008211620A (ja) * | 2007-02-27 | 2008-09-11 | Advantest Corp | ドライバ回路 |

| JP2008294837A (ja) * | 2007-05-25 | 2008-12-04 | Fuji Xerox Co Ltd | 信号伝送回路及び信号伝送システム |

| JP2009147512A (ja) * | 2007-12-12 | 2009-07-02 | Yokogawa Electric Corp | プリエンファシス回路 |

-

2008

- 2008-08-26 JP JP2008216548A patent/JP5540479B2/ja not_active Expired - Fee Related

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01161943A (ja) * | 1987-12-18 | 1989-06-26 | Nec Corp | パルス伝送回路 |

| JPH02111126A (ja) * | 1988-10-19 | 1990-04-24 | Nec Corp | 伝送回路 |

| JP2000068816A (ja) * | 1998-06-05 | 2000-03-03 | Telefon Ab L M Ericsson | ディジタル信号をプリエンファシス伝送路経由で送信するための出力バッファ回路 |

| JP2004088693A (ja) * | 2002-08-29 | 2004-03-18 | Toshiba Corp | 差動データドライバー回路 |

| JP2006345532A (ja) * | 2005-06-09 | 2006-12-21 | Agilent Technol Inc | 信号整形回路 |

| JP2007036848A (ja) * | 2005-07-28 | 2007-02-08 | Ricoh Co Ltd | ドライバ回路 |

| JP2007124644A (ja) * | 2005-10-27 | 2007-05-17 | Internatl Business Mach Corp <Ibm> | 電子回路、該電子回路として構成された差分送信機、及び、自己直列終端送信機を形成する方法(振幅制御、プリ・エンファシス制御及びスルー・レート制御のためのセグメント化と振幅精度及び高電圧保護のための電圧調整とを有する自己直列終端シリアル・リンク送信機) |

| JP2008211620A (ja) * | 2007-02-27 | 2008-09-11 | Advantest Corp | ドライバ回路 |

| JP2008294837A (ja) * | 2007-05-25 | 2008-12-04 | Fuji Xerox Co Ltd | 信号伝送回路及び信号伝送システム |

| JP2009147512A (ja) * | 2007-12-12 | 2009-07-02 | Yokogawa Electric Corp | プリエンファシス回路 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015062296A (ja) * | 2010-12-14 | 2015-04-02 | クゥアルコム・インコーポレイテッドQualcomm Incorporated | オンチップ電圧駆動型シングルエンド終端ドライバのためのプリエンファシス技法 |

| JP2013046332A (ja) * | 2011-08-26 | 2013-03-04 | Renesas Electronics Corp | 半導体装置 |

| CN102957420A (zh) * | 2011-08-26 | 2013-03-06 | 瑞萨电子株式会社 | 半导体器件 |

| US8674747B2 (en) | 2011-08-26 | 2014-03-18 | Renesas Electronics Corporation | Semiconductor device |

| CN102957420B (zh) * | 2011-08-26 | 2017-03-01 | 瑞萨电子株式会社 | 半导体器件 |

| JP2015228554A (ja) * | 2014-05-30 | 2015-12-17 | ソニー株式会社 | 送信装置、受信装置、および通信システム |

| US10038346B2 (en) | 2014-05-30 | 2018-07-31 | Sony Corporation | Transmission unit, reception unit, and communication system |

| US10756579B2 (en) | 2014-05-30 | 2020-08-25 | Sony Corporation | Transmission unit, reception unit, and communication system |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5540479B2 (ja) | 2014-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4609834A (en) | Integrated logic circuit incorporating a module which generates a control signal that cancels switching noise | |

| US20100289522A1 (en) | Signal transmitting device suited to fast signal transmission | |

| US6362644B1 (en) | Programmable termination for integrated circuits | |

| US7795919B2 (en) | Transmitter driver circuit in high-speed serial communications system | |

| US7916497B2 (en) | Printed circuit board and differential signaling structure | |

| JPH0823354A (ja) | 信号入出力装置 | |

| US20090072859A1 (en) | High speed io buffer | |

| EP2118760B1 (en) | A bi-directional interface circuit having a switchable current-source bias | |

| CN109714041B (zh) | 一种高速信号驱动电路 | |

| JPH08250995A (ja) | 出力回路 | |

| JP5540479B2 (ja) | ドライバ回路 | |

| JP2004153626A (ja) | センタタップ終端回路及びセンタタップ終端回路を有するプリント配線板 | |

| JP2010233140A (ja) | 半導体集積回路装置 | |

| US20090154591A1 (en) | High-speed serial data signal transmitter driver circuitry | |

| US6838900B2 (en) | Middle pull-up point-to-point transceiving bus structure | |

| JP3486337B2 (ja) | 信号の完全性を増す方法および集積回路 | |

| JP3958157B2 (ja) | 差動信号伝送線路の終端回路 | |

| JP2005260066A (ja) | フレキシブル基板及び電子機器 | |

| JP2003018224A (ja) | 差動信号伝送方式および差動信号伝送における送信および受信に使用するic | |

| JP2005086662A (ja) | 半導体装置 | |

| CN117453605B (zh) | 信号输出缓冲器、信号芯片和印制电路板 | |

| EP2464009B1 (en) | Differential signal termination circuit | |

| US6812869B1 (en) | Noise reduction techniques for programmable input/output circuits | |

| WO2019146430A1 (ja) | 通信システムおよび伝送装置 | |

| JPH07283836A (ja) | 信号伝送装置及び信号受信モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110607 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121204 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130409 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130610 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130820 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131018 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140408 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140421 |

|

| LAPS | Cancellation because of no payment of annual fees |