JP2010040955A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010040955A JP2010040955A JP2008205038A JP2008205038A JP2010040955A JP 2010040955 A JP2010040955 A JP 2010040955A JP 2008205038 A JP2008205038 A JP 2008205038A JP 2008205038 A JP2008205038 A JP 2008205038A JP 2010040955 A JP2010040955 A JP 2010040955A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- bonding

- wire

- substrate

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48095—Kinked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48471—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area being a ball bond, i.e. wedge-to-ball, reverse stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48475—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball

- H01L2224/48476—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area

- H01L2224/48477—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding)

- H01L2224/48478—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball

- H01L2224/48479—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Wire Bonding (AREA)

Abstract

【解決手段】上段の第2半導体チップ2の端部と下段の第1半導体チップ1の端部との距離が第1半導体チップ1の端部と配線基板7のボンディングリード7cとの距離よりも長くなるように、第2半導体チップ2が第1半導体チップ1上に搭載され、かつ第2半導体チップ2と接続する複数の第2ワイヤ3bが逆ボンディング方式により形成されていることで、第1半導体チップ1の外側で第2ワイヤ3bを急峻に立ち上がらせて接続することができるため、第1半導体チップ1の端部と第2ワイヤ3bの間にクリアランスを大きく設けることができ、下段側の第1半導体チップ1と第2ワイヤ3bのショートを防止できる。

【選択図】図3

Description

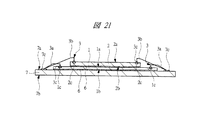

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図、図2は図1のA−A線に沿って切断した構造の一例を示す断面図、図3は図1のB−B線に沿って切断した構造の一例を示す断面図である。

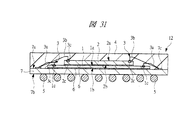

図30は本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図、図31は図30のA−A線に沿って切断した構造の一例を示す断面図、図32は図30のB−B線に沿って切断した構造の一例を示す断面図である。また、図33は図30に示す半導体装置の製造方法の第1ワイヤボンドにおける下段チップのワイヤボンディング状態の一例を示す平面図、図34は図33のA−A線に沿って切断した構造の一例を示す断面図、図35は図33のB−B線に沿って切断した構造の一例を示す断面図である。

1a 第1主面

1b 裏面

1c 第1パッド(第1電極パッド)

1d 中心

2 第2半導体チップ

2a 第2主面

2b 裏面

2c 第2パッド(第2電極パッド)

2d 中心

3 ワイヤ

3a 第1ワイヤ

3b 第2ワイヤ

3c 金バンプ

3d 折り曲げ点

4 封止体

5 半田ボール(外部端子)

6 接着剤

7 配線基板(基板)

7a 表面(主面)

7b 裏面

7c ボンディングリード

7d ソルダレジスト膜

7e 開口部

7f モールドエリア

7g チップ搭載領域

8 マルチチップモジュール(半導体装置)

9 モールド金型

9a 上型

9b キャビティ

9c ゲート

9d 下型

9e 金型面

9f ポット

9g ランナ

10 モールドレジン(樹脂)

11 充填方向

12 マルチチップモジュール(半導体装置)

13 半導体チップ

13a 主面

13b パッド

14 ワイヤリング方向

15 半導体装置

16 突起電極

17 アンダーフィル樹脂

Claims (11)

- 複数の第1ボンディングリード及び複数の第2ボンディングリードが形成された表面、及び前記表面と反対側の裏面を有する基板と、

複数の第1パッドが形成された第1主面、及び前記第1主面とは反対側の第1裏面を有し、前記基板の複数のボンディングリードの内側に位置するように、前記基板の前記表面上に搭載された第1半導体チップと、

複数の第2パッドが形成され、前記第1半導体チップの外形寸法よりも小さい第2主面、及び前記第2主面とは反対側の第2裏面を有し、前記第1半導体チップの前記複数の第1パッドの内側に位置し、前記第2裏面が前記第1半導体チップと対向するように、前記第1半導体チップ上に搭載された第2半導体チップと、

前記第1半導体チップの前記複数の第1パッドと前記基板の前記複数の第1ボンディングリードとをそれぞれ電気的に接続する複数の第1接続手段と、

前記第2半導体チップの前記複数の第2パッドと前記基板の前記複数の第2ボンディングリードとをそれぞれ電気的に接続する複数の第2接続手段と、

前記第1半導体チップ、前記第2半導体チップ及び前記複数の第2接続手段を封止する封止体と、

前記基板の前記裏面に設けられた複数の外部端子と、

を含み、

前記第2半導体チップは、前記第2半導体チップの端部と前記第1半導体チップの端部との距離が前記第1半導体チップの端部と前記基板の前記ボンディングリードとの距離よりも長くなるように、前記第1半導体チップの前記第1主面上に搭載され、

前記第2接続手段は、ワイヤであり、

前記第2ボンディングリード上における前記ワイヤと前記基板の前記表面との成す角度は、前記第2半導体チップの前記第2パッド上における前記ワイヤと前記第2半導体チップの前記第2主面との成す角度より大きいことを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記基板の前記表面の平面形状は、一対の第1辺と、前記第1辺と交差する一対の第2辺を有する四角形であり、

前記複数の第2ボンディングリードは、前記基板の前記第1辺に沿って形成され、

前記第2半導体チップの前記第2主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第3辺と、前記第3辺と交差する一対の第4辺を有する四角形であり、

前記複数の第2パッドは、前記第2半導体チップの前記第3辺に沿って形成されていることを特徴とする半導体装置。 - 請求項2記載の半導体装置において、

前記複数の第2ボンディングリードは、さらに前記第2辺に沿って形成され、

前記複数の第2パッドは、さらに前記第4辺に沿って形成され、

前記基板の前記第2辺に沿って形成された前記第2ボンディングリード上における前記ワイヤと前記基板の前記表面との成す角度は、前記第2半導体チップの前記第4辺に沿って形成された前記第2パッド上における前記ワイヤと前記第2半導体チップの前記第2主面との成す角度より小さいことを特徴とする半導体装置。 - 請求項3記載の半導体装置において、前記第1半導体チップの前記第1主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第5辺と、前記第5辺と交差する一対の第6辺を有する四角形であり、

前記第1半導体チップの前記第5辺と前記基板の前記第1辺に沿って形成された前記第2ボンディングリードとの距離(M1)は、前記第1半導体チップの前記第6辺と前記基板の前記第2辺に沿って形成された前記第2ボンディングリードとの距離(M2)よりも短いことを特徴とする半導体装置。 - 請求項4記載の半導体装置において、前記第2半導体チップの厚さは、前記第1半導体チップの厚さよりも厚いことを特徴とする半導体装置。

- (a)複数の第1ボンディングリード及び複数の第2ボンディングリードが形成された表面、及び前記表面と反対側の裏面を有する基板を準備する工程;

(b)複数の第1パッドが形成された第1主面、及び前記第1主面とは反対側の第1裏面を有する第1半導体チップを、前記基板の複数のボンディングリードの内側に位置するように、前記基板の前記表面上に搭載する工程;

(c)複数の第2パッドが形成され、前記第1半導体チップの外形寸法よりも小さい第2主面、及び前記第2主面とは反対側の第2裏面を有する第2半導体チップを、前記第1半導体チップの前記複数の第1パッドの内側に位置し、前記第2裏面が前記第1半導体チップと対向するように、前記第1半導体チップ上に搭載する工程;

(d)前記第1半導体チップの前記複数の第1パッドと前記基板の前記複数の第1ボンディングリードとを、複数の第1接続手段を介してそれぞれ電気的に接続する工程;

(e)前記第2半導体チップの前記複数の第2パッドと前記基板の前記複数の第2ボンディングリードとを、複数の第2接続手段を介してそれぞれ電気的に接続する工程;

(f)前記第1半導体チップ、前記第2半導体チップ及び前記複数の第2接続手段を樹脂で封止する工程;

(g)前記基板の前記裏面に複数の外部端子を形成する工程;

を含み、

前記第2半導体チップは、前記第2半導体チップの端部と前記第1半導体チップの端部との距離が前記第1半導体チップの端部と前記基板の前記ボンディングリードとの距離よりも長くなるように、前記第1半導体チップの前記第1主面上に搭載され、

前記第2接続手段は、ワイヤであり、

前記(e)工程では、前記基板の前記第2ボンディングリードに前記ワイヤの一端部を接続した後、前記ワイヤの一端部とは反対側の他端部を前記第2半導体チップの前記第2パッドに接続することを特徴とする半導体装置の製造方法。 - 請求項6記載の半導体装置の製造方法において、前記基板の前記表面の平面形状は、一対の第1辺と、前記第1辺と交差する一対の第2辺を有する四角形であり、

前記複数の第2ボンディングリードは、前記基板の前記第1辺に沿って形成され、

前記第2半導体チップの前記第2主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第3辺と、前記第3辺と交差する一対の第4辺を有する四角形であり、

前記複数の第2パッドは、前記第2半導体チップの前記第3辺に沿って形成されていることを特徴とする半導体装置の製造方法。 - 請求項7記載の半導体装置の製造方法において、前記(f)工程では、前記基板の前記第1辺側から前記樹脂を供給することを特徴とする半導体装置の製造方法。

- 請求項8記載の半導体装置の製造方法において、

前記複数の第2ボンディングリードは、さらに前記第2辺に沿って形成され、

前記複数の第2パッドは、さらに前記第4辺に沿って形成され、

前記基板の前記第2辺に沿って形成された前記第2ボンディングリードと前記第2半導体チップの前記第4辺に沿って形成された前記第2パッドとを電気的に接続する前記ワイヤは、前記第2半導体チップの前記第2パッドに前記ワイヤの一端部を接続した後、前記ワイヤの前記一端部とは反対側の前記他端部を前記基板の前記第2ボンディングリードに接続することを特徴とする半導体装置の製造方法。 - 請求項9記載の半導体装置の製造方法において、前記第1半導体チップの前記第1主面の平面形状は、前記基板の前記第1辺と並ぶ一対の第5辺と、前記第5辺と交差する一対の第6辺を有する四角形であり、

前記第1半導体チップの前記第5辺と前記基板の前記第1辺に沿って形成された前記第2ボンディングリードとの距離(M1)は、前記第1半導体チップの前記第6辺と前記基板の前記第2辺に沿って形成された前記第2ボンディングリードとの距離(M2)よりも短いことを特徴とする半導体装置の製造方法。 - 請求項10記載の半導体装置の製造方法において、前記第2半導体チップの厚さは前記第1半導体チップの厚さより厚いことを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008205038A JP5205173B2 (ja) | 2008-08-08 | 2008-08-08 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008205038A JP5205173B2 (ja) | 2008-08-08 | 2008-08-08 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010040955A true JP2010040955A (ja) | 2010-02-18 |

| JP2010040955A5 JP2010040955A5 (ja) | 2011-08-18 |

| JP5205173B2 JP5205173B2 (ja) | 2013-06-05 |

Family

ID=42013148

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008205038A Expired - Fee Related JP5205173B2 (ja) | 2008-08-08 | 2008-08-08 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5205173B2 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0525602A (ja) * | 1991-07-17 | 1993-02-02 | Nippon Steel Corp | メツキ密着性に優れたアルミニウムメツキオーステナイト系ステンレス鋼板の製造法 |

| JP2013125765A (ja) * | 2011-12-13 | 2013-06-24 | Elpida Memory Inc | 半導体装置 |

| CN109003947A (zh) * | 2018-07-23 | 2018-12-14 | 苏州锝耀电子有限公司 | 大功率层叠式芯片结构 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101858614B1 (ko) | 2017-11-01 | 2018-05-17 | 주식회사 에이맥스 | 절곡 성형강판을 이용한 강성 빌트업 빔과 그 제작방법 및 빌트업 빔의 단부 보강 연결 시스템 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000307057A (ja) * | 1999-02-17 | 2000-11-02 | Sharp Corp | 半導体装置、およびその製造方法 |

| JP2007184385A (ja) * | 2006-01-06 | 2007-07-19 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JP2008078367A (ja) * | 2006-09-21 | 2008-04-03 | Renesas Technology Corp | 半導体装置 |

| JP2008159786A (ja) * | 2006-12-22 | 2008-07-10 | Toshiba Corp | 半導体装置及び接着配線部材の製造方法 |

-

2008

- 2008-08-08 JP JP2008205038A patent/JP5205173B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000307057A (ja) * | 1999-02-17 | 2000-11-02 | Sharp Corp | 半導体装置、およびその製造方法 |

| JP2007184385A (ja) * | 2006-01-06 | 2007-07-19 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JP2008078367A (ja) * | 2006-09-21 | 2008-04-03 | Renesas Technology Corp | 半導体装置 |

| JP2008159786A (ja) * | 2006-12-22 | 2008-07-10 | Toshiba Corp | 半導体装置及び接着配線部材の製造方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0525602A (ja) * | 1991-07-17 | 1993-02-02 | Nippon Steel Corp | メツキ密着性に優れたアルミニウムメツキオーステナイト系ステンレス鋼板の製造法 |

| JP2013125765A (ja) * | 2011-12-13 | 2013-06-24 | Elpida Memory Inc | 半導体装置 |

| US9449951B2 (en) | 2011-12-13 | 2016-09-20 | Ps4 Luxco S.A.R.L. | Semiconductor device |

| CN109003947A (zh) * | 2018-07-23 | 2018-12-14 | 苏州锝耀电子有限公司 | 大功率层叠式芯片结构 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5205173B2 (ja) | 2013-06-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8076770B2 (en) | Semiconductor device including a first land on the wiring substrate and a second land on the sealing portion | |

| TWI495082B (zh) | 多層半導體封裝 | |

| US8389339B2 (en) | Method of manufacturing semiconductor device | |

| KR100690247B1 (ko) | 이중 봉합된 반도체 패키지 및 그의 제조 방법 | |

| JP4727850B2 (ja) | 半導体電子部品 | |

| US20050194673A1 (en) | Multi-chip package, a semiconductor device used therein and manufacturing method thereof | |

| US20120286411A1 (en) | Semiconductor device and manufacturing method thereof, and semiconductor module using the same | |

| KR20050119414A (ko) | 에지 패드형 반도체 칩의 스택 패키지 및 그 제조방법 | |

| JP2005183934A (ja) | オフセット接合型マルチチップ半導体装置 | |

| JP4942020B2 (ja) | 半導体装置 | |

| JP2003338519A (ja) | 半導体装置及びその製造方法 | |

| US20060284298A1 (en) | Chip stack package having same length bonding leads | |

| US7262494B2 (en) | Three-dimensional package | |

| JP2005317975A (ja) | ソルダバンプとゴールドバンプとの接合を持つシステムインパッケージ及びその製造方法 | |

| JP6196092B2 (ja) | 半導体装置 | |

| US9972560B2 (en) | Lead frame and semiconductor device | |

| JP2007027526A (ja) | 両面電極パッケージ及びその製造方法 | |

| US8648455B2 (en) | Semiconductor device and method of manufacturing the same | |

| JP5205173B2 (ja) | 半導体装置及びその製造方法 | |

| US8063474B2 (en) | Embedded die package on package (POP) with pre-molded leadframe | |

| US9252126B2 (en) | Multi Chip Package-type semiconductor device | |

| CN202394859U (zh) | 半导体封装构造 | |

| KR20150046117A (ko) | 장치 및 그 제조 방법 | |

| US20160141272A1 (en) | Semiconductor device and method of manufacturing same | |

| KR100800149B1 (ko) | 스택 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110706 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110706 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120327 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130122 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130218 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160222 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |