JP2010034152A - スピントランジスタ、リコンフィギャラブル論理回路、磁気抵抗効果素子、および磁気メモリ - Google Patents

スピントランジスタ、リコンフィギャラブル論理回路、磁気抵抗効果素子、および磁気メモリ Download PDFInfo

- Publication number

- JP2010034152A JP2010034152A JP2008192507A JP2008192507A JP2010034152A JP 2010034152 A JP2010034152 A JP 2010034152A JP 2008192507 A JP2008192507 A JP 2008192507A JP 2008192507 A JP2008192507 A JP 2008192507A JP 2010034152 A JP2010034152 A JP 2010034152A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- ferromagnetic

- film

- alloy containing

- spin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

Abstract

【解決手段】半導体基板上に離間して設けられたソース部およびドレイン部であって、前記ソース部およびドレイン部はそれぞれ、CoおよびFeを含む合金からなる第1強磁性層15a1、15b1と、前記第1強磁性層上に形成されたCoおよびMnを含むフルホイスラー合金からなる第2強磁性層15a2、15b2とを有する強磁性積層膜を含む、ソース部およびドレイン部15a、15bと、前記ソース部と前記ドレイン部との間の前記半導体基板上に設けられるゲート絶縁膜9と、ゲート絶縁膜上に設けられたゲート電極10と、を備えている。

【選択図】図3

Description

APL84(2004)2307.

本発明の第1実施形態によるスピンMOSFETの断面を図3に示す。本実施形態のスピンMOSFETは、n型のスピンMOSFETであって、p型半導体基板2の素子領域3に形成されている。この素子領域3は、素子分離絶縁膜4によって分離されている半導体領域である。半導体領域は、半導体基板の一部の領域であってもよいし、半導体基板に形成されたウェル領域であってもよい。また、SOI(Silicon On Insulator)基板のSOI層であってもよい。なお、本明細書では、素子領域3は、p型半導体基板2の一部の半導体領域であってもよいし、n型基板に形成されたpウェル領域であってもよい。また、SOI基板のp型のSOI層であってもよい。この素子領域3には、離間して形成されたn型不純物拡散領域6aおよびn型不純物拡散領域6bが設けられている。これらのn型不純物拡散領域6aおよびn型不純物拡散領域6bの表面には、これらのn型不純物拡散領域6aおよびn型不純物拡散領域6bよりも高濃度のn+不純物拡散領域7aおよびn+型不純物拡散領域7bがそれぞれ設けられている。n型不純物拡散領域6aおよびn+不純物拡散領域7aがソース領域5aを構成し、不純物拡散領域6bおよびn+不純物拡散領域7bがドレイン領域5bを構成する。

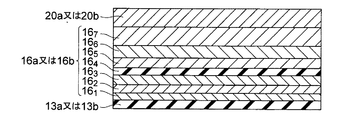

第1実施形態の変形例によるスピンMOSFETを図4に示す。本変形例のスピンMOSFETは、図3に示す第1実施形態のスピンMOSFETにおいて、ソース部15aおよびドレイン部15bの強磁性層15a2、15b2と非磁性金属層20a、20bとの間に、反強磁性層15a3、15b3をそれぞれ設けた構成となっている。この場合、ソース部15aは、ソース領域5a上にトンネルバリア14aを挟んで、CoおよびFeを含む合金からなる強磁性層15a1、CoおよびMnを含むフルホイスラー合金からなる強磁性層15a2、反強磁性層15a3がこの順序で積層された積層構造を有し、ドレイン部15bは、ドレイン領域5b上にトンネルバリア14bを挟んで、CoおよびFeを含む合金からなる強磁性層15b1、CoおよびMnを含むフルホイスラー合金からなる強磁性層15b2、反強磁性層15b3がこの順序で積層された積層構造を有している。そして、2つの積層構造のうち、一方の積層構造の強磁性層は、他方の積層構造の強磁性層よりも磁化反転が容易である構成となっている。

また、反強磁性層は、ソース部15aおよびドレイン部15bの一方に設けてもよい。この場合は、ソース部15aの強磁性積層膜15a1、15a2の膜面の面積と、ドレイン部15bの強磁性積層膜15b1、15b2の膜面の面積とが同じでもよい。

次に、本発明の第2実施形態によるスピンMOSFETの断面を図5に示す。本実施形態のスピンMOSFETは、n型のスピンMOSFETであって、図3に示す第1実施形態のスピンMOSFETのソース部15aおよびドレイン部15bを、ソース部16aおよびドレイン部16bにそれぞれ置き換えるとともに、トンネルバリア14aおよび14bをトンネル障壁となる誘電体層(例えば、酸化物、窒化物、または酸窒化物からなる層)13aおよび13bにそれぞれ置き換えた構成となっている。なお、誘電体層13a、13bは、MgOからなるトンネルバリアであることが好ましい。

また、本実施形態において、更にソース部16aおよびドレイン部16bのうちの一方の強磁性層を含む積層膜の面内形状を線対称な形状(対称軸が少なくとも1個存在する形状)にし、他方を線非対称な形状にすると、面積の大きな方のMTJのフリー層に対応する場所のスピンモーメントが反転しづらくなってスピン注入書き込み時のマージンが更に広がり、より好ましい。なお、本明細書では、「線非対称」な形状とは、線対称ではない形状を意味する。図7(a)、7(b)に線対称な形状の例を示し、図8(a)、8(b)に線非対称な形状の例を示す。図7(a)、7(b)に示す形状はそれぞれ長方形、楕円であり、図8(a)に示す形状は平行四辺形であり、図8(b)に示す形状は不等辺四角形の角を切り取ったものである。これらの例に限らず線対称な形状、線非対称な形状であれば本実施形態のソース部16aおよびドレイン部16bの膜面形状に用いることができる。

次に、第2実施形態の変形例によるスピンMOSFETの断面を図9に示す。本変形例のスピンMOSFETは、図5に示す第2実施形態のスピンMOSFETの誘電体層13aおよび13bを削除した構成となっている。すなわち、MOSFETのソース領域5aおよびドレイン領域5b上に直接、強磁性積層膜16a、16bを設けた構造となる。この場合、ソース領域5aおよびドレイン領域5bと、強磁性積層膜16a、16bとの界面に自然にショットキー障壁が形成される。

次に、本発明の第3実施形態によるスピンMOSFETの断面を図10に示す。本実施形態のスピンMOSFETは、図2に示す第2実施形態のスピンMOSFETにおいて、ソース部16aおよびドレイン部16bのうちの一方、例えばソース部16aをソース部17aに置き換えた構成となっている。ソース部17aは、CoおよびFeを含む合金からなる強磁性層17a1、CoおよびMnを含むフルホイスラー合金からなる強磁性層17a2、および反強磁性層17a3がこの順序で積層された積層構造を有している。強磁性層17a1および強磁性層17a2は、反強磁性層17a3によって磁化の向きが固着され、ソース部17aは磁化固着膜となる。他方、ドレイン部16bは、第2実施形態で説明したように、MTJ構造を有している。

次に、第3実施形態の変形例によるスピンMOSFETの断面を図11に示す。本変形例のスピンMOSFETは、図10に示す第3実施形態のスピンMOSFETの誘電体層13aおよび13bを削除した構成となっている。すなわち、MOSFETのソース領域5aおよびドレイン領域5b上に直接、強磁性積層膜17a、16bを設けた構造となっている。この場合、ソース領域5aおよびドレイン領域5bと、強磁性積層膜17a、16bとの界面に自然にショットキー障壁が形成される。

次に、本発明の第4実施形態によるスピンMOSFETを図12および図13を参照して説明する。図12および図13は、本実施形態のスピンMOSFETに用いられるソース部18aおよびドレイン部18bのそれぞれの断面図である。

次に、本発明の第5実施形態によるスピンMOSFETの断面を図14に示す。本実施形態のスピンMOSFETは、図5に示す第2実施形態のスピンMOSFETにおいて、ソース部16aおよびドレイン部16bをソース部22aおよびドレイン部22bにそれぞれ置き換えた構成となっている。

また、本実施形態において、第2実施形態で説明したように、更にソース部22aおよびドレイン部22bのうちの一方の強磁性層を含む積層膜の膜面の形状を線対称な形状にし、他方を線非対称な形状にすると、面積の大きな方のMTJのフリー層に対応する場所のスピンモーメントが反転しづらくなってスピン注入書き込み時のマージンが更に広がり、より好ましい。

次に、第5実施形態の変形例によるスピンMOSFETの断面を図16に示す。本変形例のスピンMOSFETは、図14に示す第5実施形態のスピンMOSFETにおいて、ソース領域5aとソース部22aとの間の誘電体層13aと、ドレイン領域5bとドレイン部22bとの間の誘電体層13bと、を削除した構成となっている。この場合、ソース領域5aおよびドレイン領域5bとソース部22aおよびドレイン部22bとの界面に自然にショットキー障壁が形成される。

次に、本発明の第6実施形態によるスピンMOSFETの断面を図17に示す。本実施形態のスピンMOSFETは、図14に示す第5実施形態のスピンMOSFETにおいて、ソース部22aおよびドレイン部22aのうちの一方、例えば、ソース部22aを図12に示すソース部18aに置き換えた構成となっている。すなわち、図17においては、ソース部18aが磁化固着層となっている。なお、図17においては、ソース部18aの積層数は図12に示す積層数と異なって表示している。

次に、第6実施形態の変形例によるスピンMOSFETの断面を図18に示す。本変形例のスピンMOSFETは、図17に示す第6実施形態のスピンMOSFETにおいて、ソース領域5aとソース部18aとの間の誘電体層13aと、ドレイン領域5bとドレイン部22bとの間の誘電体層13bと、を削除した構成となっている。この場合、ソース領域5aおよびドレイン領域5bと、ソース部18aおよびドレイン部22bとの界面に自然にショットキー障壁が形成される。

次に、本発明の第7実施形態によるスピンMOSFETの断面を図19に示す。本実施形態のスピンMOSFETは、図14に示す第5実施形態のスピンMOSFETにおいて、外部磁界がないときの磁化(スピンの磁化容易軸)が膜面に略平行であるソース部22aおよびドレイン部22bを、外部磁界が無いときの磁化(スピンの磁化容易軸)が膜面に略垂直なソース部30aおよびドレイン部30bに置き換えた構成となっている。

また、本実施形態において、第2実施形態で説明したように、更にソース部30aおよびドレイン部30bのうちの一方の強磁性層を含む積層膜の膜面の形状を線対称な形状にし、他方を線非対称な形状にすると、面積の大きな方のMTJのフリー層に対応する場所のスピンモーメントが反転しづらくなってスピン注入書き込み時のマージンが更に広がり、より好ましい。

次に、第7実施形態の変形例によるスピンMOSFETの断面を図21に示す。本変形例のスピンMOSFETは、図19に示す第7実施形態のスピンMOSFETにおいて、ソース領域5aとソース部30aとの間の誘電体層13aと、ドレイン領域5bとドレイン部30bとの間の誘電体層13bと、を削除した構成となっている。この場合、ソース領域5aおよびドレイン領域5bとソース部30aおよびドレイン部30bとの界面に自然にショットキー障壁が形成される。

次に、本発明の第8実施形態によるスピンMOSFETの断面を図22に示す。本実施形態のスピンMOSFETは、図19に示す第7実施形態のスピンMOSFETにおいて、ソース部30aおよびドレイン部30bのうちの一方、例えばソース部30aを、CoおよびMnを含むフルホイスラー合金層を有する磁化固定層34に置き換えた構成となっている。磁化固定層とは、磁化の向きが書き込み電流の流す前と流す後では不変(固定)となる層のことである。この磁化固定層34の一具体例を図23に示す。図23に示すように、磁化固定層34は、CoおよびFeを含む合金からなる強磁性層341と、CoおよびMnを含むフルホイスラー合金からなる強磁性層342と、スピンの磁化容易軸が膜面に略垂直な強磁性層343とがこの順序で積層された積層構造を有している。

本実施形態も第7実施形態と同様に、磁性層としてフルホイスラー合金を用いても、磁気抵抗変化率が可及的に高くかつ温度変化の影響を可及的に受けないスピンMOSFETを提供することができる。

次に、第8実施形態の変形例によるスピンMOSFETの断面を図24に示す。本変形例のスピンMOSFETは、図22に示す第8実施形態のスピンMOSFETにおいて、ソース領域5aとソース部34との間の誘電体層13aと、ドレイン領域5bとドレイン部30bとの間の誘電体層13bと、を削除した構成となっている。この場合、ソース領域5aおよびドレイン領域5bと、ソース部34およびドレイン部30bとの界面に自然にショットキー障壁が形成される。

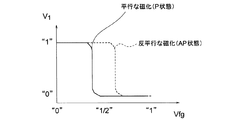

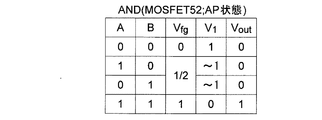

次に、本発明の第9実施形態によるリコンフィギャラブル論理回路を説明する。本実施形態のリコンフィギャラブル論理回路は、上述の第1乃至第8実施形態およびその変形例のいずれかに記載のスピンMOSFETを用いて構成した論理回路である。

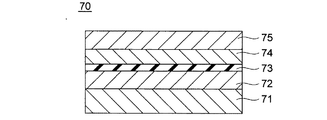

次に、本発明の第10実施形態による磁気抵抗効果素子の断面を図31に示す。本実施形態の磁気抵抗効果素子70は、CoおよびMnを含むフルホイスラー合金からなる強磁性層71と、CoおよびFeを含む合金からなる強磁性層72と、MgOからなるトンネルバリア73と、CoおよびFeを含む合金からなる強磁性層74と、CoおよびMnを含むフルホイスラー合金からなる強磁性層75とが、この順序で積層された積層構造を有している。すなわち、MgOからなるトンネルバリア73に接して両界面にCoおよびFeを含む合金からなる強磁性層72、74が存在し、これらの強磁性層72、74に接してトンネルバリア73と反対側の界面にCoおよびMnを含むフルホイスラー合金からなる強磁性層71、75が存在する積層構造となっている。

これらの第1および第2強磁性層の膜厚が強磁性層71、72、74、75の膜厚に比べて厚いため、磁気抵抗効果素子としての機能には問題がない。

次に、本発明の第11実施形態によるスピン注入書き込み型のMRAMについて説明する。本実施形態のMRAMは複数のメモリセルを有しており、各メモリセルは、記憶素子として第10実施形態の磁気抵抗効果素子70を備えている。

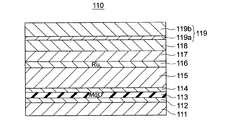

本発明の実施例1は強磁性積層膜であって、その断面を図34に示す。本実施例の強磁性積層膜111は、図示しないCrからなる下地電極上に、膜厚が10nmのCo2MnSi層111/膜厚が2nmの第1強磁性層112/膜厚が0.6nmのMg層(図示せず)/膜厚が0.5nmのMgOからなるトンネルバリア113/膜厚が2nmの第2強磁性層114/膜厚が5nmのCo2MnSi層115/膜厚が0.9nmのRu層116/膜厚が3nmのCoFe層117/膜厚が10nmのIrMn層118/膜厚が5nmのRu層119a/膜厚が50nmのTa層119bが、この順序で積層された構成となっている。なお、Ru層119aおよびTa層119bがキャップ層119となる。

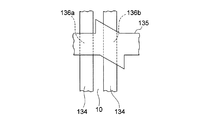

本発明の実施例2は、図3に示す第1実施形態のn型スピンMOSFETであって、ソース部15aと、ドレイン部15bの強磁性積層膜の面積を変えた構成を有している。半導体基板2としてインプラしたSi基板を用いている。ソース部15aおよびドレイン部15bの強磁性積層膜の面積が異なるスピンMOSFETは、以下のようにして形成される。まず図37に示したように、半導体基板2に離間してソース領域5aおよびドレイン領域5bを形成し、ソース領域5aとドレイン領域5bとの間の半導体基板2上にゲート絶縁膜9を形成し、このゲート絶縁膜9上にゲート10を形成する。なお、ゲート絶縁膜9およびゲート10を形成した後に、ソース領域5およびドレイン領域5bを形成してもよい。その後、ゲート10を覆うように、SiO2からなる層間絶縁膜130を堆積する。続いて、この層間絶縁膜130に異なる面積の穴132a、132bを開ける。その後、高圧RFスパッタを用いて、強磁性積層膜を堆積し、穴132a、132bを埋め込む。続いて、CMP(Chemical Mechanical Polishing)を用いて、層間絶縁膜130の上面に付着した強磁性積層膜を除去する。これにより、ソース部およびドレイン部の強磁性積層膜の膜面面積が異なるスピンMOSFETが形成される。

本発明の実施例3は、Ge基板上に形成されたn型スピンMOSFETであって、Ge基板上に形成されるソース部およびドレイン部として、実施例1で説明した強磁性積層膜を用いる。強磁性積層膜の作製方法は実施例1と同様である。すなわち、本実施例によるスピンMOSFETの強磁性積層膜は、Ge基板上に、膜厚が0.5nmのGeOx層/膜厚が0.5nmのMgOからなるトンネルバリア/膜厚が3nmの強磁性層/膜厚が10nmのCo2MnSi層/膜厚が20nmのRu層および膜厚が50nmのTa層からなるキャップ層が、この順序で積層された積層構造を有している。

本発明の実施例4は、GaAs基板上に形成されたn型スピンMOSFETであって、GaAs基板上に形成されるソース部およびドレイン部として、実施例1で説明した強磁性積層膜を用いる。強磁性積層膜の作製方法は実施例1と同様である。すなわち、本実施例によるスピンMOSFETの強磁性積層膜は、GaAs基板上に、膜厚が1.5nmのInGaAs層/膜厚が0.5nmのMgOからなるトンネルバリア/膜厚が3nmの強磁性層/膜厚が10nmのCo2MnSi層/膜厚が20nmのRu層および膜厚が50nmのTa層からなるキャップ層が、この順序で積層された積層構造を有している。

本発明の実施例5は、半導体基板2としてSi基板を用いた図14に示す第5実施形態のn型スピンMOSFETである。本実施例によるスピンMOSFETの強磁性積層膜は、図14,図15に示すように、Si基板上に、膜厚が0.5nmのSiO2層(図示せず)/膜厚0.5nmのMgOからなるトンネルバリア13a、13b/膜厚が3nmの第1強磁性層231/膜厚が10nmのCo2MnSi層232/膜厚が3nmの第2強磁性層233/膜厚が0.9nmのRu層234/膜厚が10nmのCo2MnSi層235/膜厚が3nmの第3強磁性層236/膜厚が0.95nmのMgOからなるトンネルバリア24/膜厚が3nmの第4強磁性層251/膜厚が5nmのCo2MnSi層252/膜厚が0.9nmのRu層253/膜厚が3nmのCoFe層254/膜厚が10nmのIrMn層26/ 膜厚が10nmのRu層および膜厚が50nmのTa層からなるキャップ層20が、この順序で積層された積層構造を有している。

本発明の実施例6は、半導体基板2としてSi基板を用いた図17に示す第6実施形態のn型スピンMOSFETである。本実施例によるスピンMOSFETは、ソース領域5a、ドレイン領域5b上の強磁性積層膜を作製する際に、強磁性積層構造を変えるため磁化固着層18aを作製したのちにMTJ構造22bを作製する。

本発明の実施例7は、半導体基板2としてSi基板を用いた図22に示す第8実施形態のn型スピンMOSFETである。本実施例によるスピンMOSFETは、ソース領域5a、ドレイン領域5b上の強磁性積層膜を作製する際に、強磁性積層構造を変えるため磁化固定層34を作製したのちにMTJ構造30bを作製する。

3 素子領域

4 素子分離領域

5a ソース領域

5b ドレイン領域

6a n型不純物拡散領域

6b n型不純物拡散領域

7b n+不純物拡散領域

8 チャネル領域

9 ゲート絶縁膜

10 ゲート電極

12 ゲート側壁

13a 誘電体層

13b 誘電体層

14a トンネルバリア

14b トンネルバリア

15a ソース部

15b ドレイン部

Claims (16)

- 半導体基板上に離間して設けられたソース部およびドレイン部であって、前記ソース部およびドレイン部はそれぞれ、CoおよびFeを含む合金からなる第1強磁性層と、前記第1強磁性層上に形成されたCoおよびMnを含むフルホイスラー合金からなる第2強磁性層とを有する強磁性積層膜を含む、ソース部およびドレイン部と、

前記ソース部と前記ドレイン部との間の前記半導体基板上に設けられるゲート絶縁膜と、

前記ゲート絶縁膜上に設けられたゲート電極と、

を備えたことを特徴とするスピントランジスタ。 - 前記半導体基板と、前記ソース部およびドレイン部の強磁性積層膜との間にそれぞれトンネルバリアが設けられていることを特徴とする請求項1記載のスピントランジスタ。

- 前記ソース部およびドレイン部のうちの少なくとも一方の前記強磁性積層膜上に、CoおよびFeを含む合金からなる強磁性層/トンネルバリア/CoおよびFeを含む合金からなる強磁性層/CoおよびMnを含むフルホイスラー合金からなる強磁性層が、この順序で積層された積層膜が設けられていることを特徴とする請求項1または2記載のスピントランジスタ。

- 前記ソース部およびドレイン部のうちの少なくとも一方の前記強磁性積層膜上に、非磁性層/CoおよびFeを含む合金からなる強磁性層/反強磁性層が、この順序で積層された積層膜を有し、前記非磁性層はRu,Rh,Irまたはこれら合金からなることを特徴とする請求項1または2記載のスピントランジスタ。

- 前記ソース部およびドレイン部のそれぞれの前記強磁性積層膜上に、CoおよびFeを含む合金からなる強磁性層/トンネルバリア/CoおよびFeを含む合金からなる強磁性層/CoおよびMnを含む合金からなる強磁性層が、この順序で積層された第1および第2積層膜を有し、前記第1および第2積層膜の膜面の面積が異なることを特徴とする請求項1または2記載のスピントランジスタ。

- 前記第1および第2積層膜の膜面の形状が異なることを特徴とする請求項5記載のスピントランジスタ。

- 前記CoおよびFeを含む合金からなる強磁性層は、体心立方格子のCoおよびFeを含む合金、またはCoおよびFeを含むフルホイスラー合金からなる強磁性層であることを特徴とする請求項1乃至6のいずれかに記載のスピントランジスタ。

- 前記ソース部およびドレイン部の下の前記半導体基板に不純物が導入されたソース領域およびドレイン領域が設けられ、前記ソース領域およびドレイン領域はそれぞれ、第1不純物領域と、前記第1不純物領域と前記ソース部およびドレイン部との間に設けられ、前記第1不純物領域よりも不純物の濃度が高い第2不純物領域とを備えていることを特徴とする請求項1乃至7のいずれかに記載のスピントランジスタ。

- 前記トンネルバリアは、酸化マグネシウム、酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ゲルマニウム、窒化ゲルマニウム、希土類酸化物、および希土類窒化物のいずれか、またはこれら積層膜を含むことを特徴とする請求項1乃至8のいずれかに記載のスピントランジスタ。

- 前記ソース部およびドレイン部のそれぞれの前記強磁性積層膜の強磁性層のスピンの磁化容易軸が膜面に対して略垂直であることを特徴とする請求項1乃至9のいずれかに記載のスピントランジスタ。

- 前記ソース部およびドレイン部のそれぞれの前記強磁性積層膜の強磁性層は、Fe−Pd層、Fe−Pt層、Fe−Pd−Pt層、Co/Niの積層膜、Fe/Pdの積層膜、Fe/Ptの積層膜のいずれかを含むことを特徴とする請求項10記載のスピントランジスタ。

- 2つの電界効果トランジスタを備え、前記2つの電界効果トランジスタのうちの少なくとも一方が請求項1乃至11のいずれかに記載のスピントランジスタであり、前記2つの電界効果トランジスタには共通のフローティングゲートが設けられていることを特徴とするリコンフィギャラブル論理回路。

- CoおよびMnを含むフルホイスラー合金からなる第1強磁性層と、

前記第1強磁性層上に設けられたCoおよびFeを含む合金からなる第2強磁性層と、

前記第2強磁性層上に設けられたトンネルバリアと、

前記トンネルバリア上に設けられたCoおよびFeを含む合金からなる第3強磁性層と、

前記第3強磁性層上に設けられたCoおよびMnを含むフルホイスラー合金からなる第4強磁性層と、

を備えていることを特徴とする磁気抵抗効果素子。 - 前記第2および第3強磁性層は、体心立方格子のCoおよびFeを含む合金、またはCoおよびFeを含むフルホイスラー合金からなる強磁性層であることを特徴とする請求項13記載の磁気抵抗効果素子。

- 請求項13または14に記載の磁気抵抗効果素子をメモリセルに備えていることを特徴とする磁気メモリ。

- 請求項13または14に記載の磁気抵抗効果素子と、一端が前記磁気抵抗効果素子の一端と直列接続されたトランジスタと、を含むメモリセルと、

前記磁気抵抗効果素子の他端と接続された第1書き込み電流回路と、

前記トランジスタの他端と接続され、前記第1書き込み電流回路とともに前記磁気抵抗効果素子の一端から他端または他端から一端に向かう電流を供給する第2書き込み電流回路と、

を備えていることを特徴とする磁気メモリ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008192507A JP4997194B2 (ja) | 2008-07-25 | 2008-07-25 | スピントランジスタ、およびリコンフィギャラブル論理回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008192507A JP4997194B2 (ja) | 2008-07-25 | 2008-07-25 | スピントランジスタ、およびリコンフィギャラブル論理回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010034152A true JP2010034152A (ja) | 2010-02-12 |

| JP4997194B2 JP4997194B2 (ja) | 2012-08-08 |

Family

ID=41738314

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008192507A Expired - Fee Related JP4997194B2 (ja) | 2008-07-25 | 2008-07-25 | スピントランジスタ、およびリコンフィギャラブル論理回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4997194B2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102194848A (zh) * | 2010-03-19 | 2011-09-21 | 株式会社东芝 | 自旋存储器和自旋晶体管 |

| US20120168838A1 (en) * | 2009-09-18 | 2012-07-05 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing the same |

| EP2987190A1 (en) * | 2013-04-16 | 2016-02-24 | Headway Technologies, Inc. | Fully compensated synthetic antiferromagnet for spintronics applications |

| JP2016513374A (ja) * | 2013-02-27 | 2016-05-12 | サントル・ナショナル・ドゥ・ラ・レシェルシュ・サイエンティフィーク−セ・エン・エール・エス− | 磁気構造体の処理方法 |

| US9842635B2 (en) | 2015-03-20 | 2017-12-12 | Kabushiki Kaisha Toshiba | Spin transistor memory |

| CN113130736A (zh) * | 2016-10-27 | 2021-07-16 | Tdk株式会社 | 自旋轨道转矩型磁化反转元件、磁存储器及高频磁性器件 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005019484A (ja) * | 2003-06-24 | 2005-01-20 | Hitachi Ltd | 磁気抵抗効果素子及び磁気ヘッド |

| JP2005150482A (ja) * | 2003-11-18 | 2005-06-09 | Sony Corp | 磁気抵抗効果素子及び磁気メモリ装置 |

| JP2006286726A (ja) * | 2005-03-31 | 2006-10-19 | Toshiba Corp | スピン注入fet |

| JP2007088068A (ja) * | 2005-09-20 | 2007-04-05 | Toshiba Corp | 磁気素子及びこれを用いた磁気信号処理装置 |

| JP2007150265A (ja) * | 2005-10-28 | 2007-06-14 | Toshiba Corp | 磁気抵抗効果素子および磁気記憶装置 |

| JP2007194300A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | スピンfet及びスピンメモリ |

| JP2007273657A (ja) * | 2006-03-31 | 2007-10-18 | Tdk Corp | 磁気抵抗効果素子およびその製造方法、ならびに薄膜磁気ヘッド、ヘッドジンバルアセンブリ、ヘッドアームアセンブリおよび磁気ディスク装置 |

| JP2008066596A (ja) * | 2006-09-08 | 2008-03-21 | Toshiba Corp | スピンmosfet |

-

2008

- 2008-07-25 JP JP2008192507A patent/JP4997194B2/ja not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005019484A (ja) * | 2003-06-24 | 2005-01-20 | Hitachi Ltd | 磁気抵抗効果素子及び磁気ヘッド |

| JP2005150482A (ja) * | 2003-11-18 | 2005-06-09 | Sony Corp | 磁気抵抗効果素子及び磁気メモリ装置 |

| JP2006286726A (ja) * | 2005-03-31 | 2006-10-19 | Toshiba Corp | スピン注入fet |

| JP2007088068A (ja) * | 2005-09-20 | 2007-04-05 | Toshiba Corp | 磁気素子及びこれを用いた磁気信号処理装置 |

| JP2007150265A (ja) * | 2005-10-28 | 2007-06-14 | Toshiba Corp | 磁気抵抗効果素子および磁気記憶装置 |

| JP2007194300A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | スピンfet及びスピンメモリ |

| JP2007273657A (ja) * | 2006-03-31 | 2007-10-18 | Tdk Corp | 磁気抵抗効果素子およびその製造方法、ならびに薄膜磁気ヘッド、ヘッドジンバルアセンブリ、ヘッドアームアセンブリおよび磁気ディスク装置 |

| JP2008066596A (ja) * | 2006-09-08 | 2008-03-21 | Toshiba Corp | スピンmosfet |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20120168838A1 (en) * | 2009-09-18 | 2012-07-05 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing the same |

| US8330196B2 (en) * | 2009-09-18 | 2012-12-11 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing the same |

| CN102194848A (zh) * | 2010-03-19 | 2011-09-21 | 株式会社东芝 | 自旋存储器和自旋晶体管 |

| JP2016513374A (ja) * | 2013-02-27 | 2016-05-12 | サントル・ナショナル・ドゥ・ラ・レシェルシュ・サイエンティフィーク−セ・エン・エール・エス− | 磁気構造体の処理方法 |

| EP2987190A1 (en) * | 2013-04-16 | 2016-02-24 | Headway Technologies, Inc. | Fully compensated synthetic antiferromagnet for spintronics applications |

| EP2987190B1 (en) * | 2013-04-16 | 2022-02-16 | Taiwan Semiconductor Manufacturing Co., Ltd. | Magnetic tunnel junction comprising a fully compensated synthetic antiferromagnet for spintronics applications |

| US9842635B2 (en) | 2015-03-20 | 2017-12-12 | Kabushiki Kaisha Toshiba | Spin transistor memory |

| CN113130736A (zh) * | 2016-10-27 | 2021-07-16 | Tdk株式会社 | 自旋轨道转矩型磁化反转元件、磁存储器及高频磁性器件 |

| CN113130736B (zh) * | 2016-10-27 | 2023-09-12 | Tdk株式会社 | 自旋轨道转矩型磁化反转元件、磁存储器及高频磁性器件 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4997194B2 (ja) | 2012-08-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4693634B2 (ja) | スピンfet | |

| JP4528660B2 (ja) | スピン注入fet | |

| JP4384196B2 (ja) | スピンfet、磁気抵抗効果素子及びスピンメモリ | |

| JP4908540B2 (ja) | スピンmosfetおよびリコンフィギャラブルロジック回路 | |

| JP5150673B2 (ja) | スピンメモリおよびスピントランジスタ | |

| JP4703660B2 (ja) | スピンmos電界効果トランジスタ | |

| JP4455558B2 (ja) | スピンmosfet | |

| US8779538B2 (en) | Magnetic tunneling junction seed, capping, and spacer layer materials | |

| JP4496242B2 (ja) | スピントランジスタ及び磁気メモリ | |

| JP4845937B2 (ja) | スピンmosfetおよびこのスピンmosfetを用いたリコンフィギュラブル論理回路 | |

| JP5711637B2 (ja) | 磁気メモリ素子、磁気メモリ装置、スピントランジスタ、及び集積回路 | |

| CN101452991A (zh) | 具有热辅助写入的磁元件 | |

| CN108780780B (zh) | 非易失性存储器装置和制造非易失性存储器装置的方法 | |

| JP4997194B2 (ja) | スピントランジスタ、およびリコンフィギャラブル論理回路 | |

| JP4764246B2 (ja) | スピンfet | |

| JP4599285B2 (ja) | 電界効果トランジスタ、集積回路、及びメモリ | |

| JP5075863B2 (ja) | スピントランジスタ、このスピントランジスタを備えたリコンフィギャラブル論理回路および磁気メモリ | |

| US8981436B2 (en) | Stacked structure, spin transistor, and reconfigurable logic circuit | |

| JP5421325B2 (ja) | スピンmosfetおよびリコンフィギャラブルロジック回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110204 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110418 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111118 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120420 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120514 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150518 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150518 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |