JP2010028507A - 発振器 - Google Patents

発振器 Download PDFInfo

- Publication number

- JP2010028507A JP2010028507A JP2008188226A JP2008188226A JP2010028507A JP 2010028507 A JP2010028507 A JP 2010028507A JP 2008188226 A JP2008188226 A JP 2008188226A JP 2008188226 A JP2008188226 A JP 2008188226A JP 2010028507 A JP2010028507 A JP 2010028507A

- Authority

- JP

- Japan

- Prior art keywords

- oscillator

- piezoelectric

- oscillation

- circuit

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Oscillators With Electromechanical Resonators (AREA)

Abstract

【解決手段】複数の発振回路の出力を1つの出力ノードN1に束ね、圧電素子X1,X2の一端を、それぞれ各圧電素子に対応する増幅器の入力端に接続すると共に、圧電素子X1,X2の他端を出力ノードN1に共通して接続する。そして、選択信号SELによって、選択用トランジスタSM1,SM2及びスイッチSW1,Sw2を制御することで、圧電素子X1,X2の何れか一方を選択し駆動させることで、多入力1出力の発振器を実現する。

【選択図】図1

Description

複数の周波数で発振する発振器としては、オーバートーン発振を利用したデュアルモード水晶発振回路(NDK)が知られている(例えば、特許文献1参照)。ここでは、水晶振動子の基本波振動に対する3次のオーバートーン振動を発振する第1の発振手段と、水晶振動子の基本波振動に対する5次のオーバートーンを発振する第2の発振手段と、第1、第2の発振手段のいずれか一方と水晶振動子との間に5次のオーバートーン振動の干渉を阻止する帯域制限手段と、を備えることで、安定な3次と5次のオーバートーン発振を実現している。

一般に、発振器は、図12に示すように、インバータ回路と、インバータ回路に並列に接続された帰還抵抗と、インバータ回路の入出力と接地間に夫々接続された容量素子とを含む発振回路と、一端がインバータ回路の入力端に接続されると共に他端がインバータ回路の出力端に接続される圧電素子とを備え、1つの発振回路と1つの圧電素子とを電気的に接続するために2つの電極が必要な構成となっている。

そこで、本発明は、回路規模を増大することなく、複数の発振周波数を自由に選択することができる発振器を提供することを目的としている。

また、本発明に係る発振器は、上記において、前記選択回路は、電流源と各増幅器との間にそれぞれ介装されたスイッチング素子により構成されており、各スイッチング素子を制御して、前記電流源から前記複数の増幅器のうち何れか1つに電流供給を行うことで、前記複数の圧電素子のうち何れか1つを駆動することを特徴としている。

さらに、本発明に係る発振器は、上記において、前記複数の圧電素子の他端が1つに束ねられた共通ノードと前記出力ノードとの間に、伸長用コイルが接続されていることを特徴としている。

これにより、発振器の周波数感度を向上させることができる。

これにより、圧電素子を除く回路部を完全なるIC化とすることができる。さらに、伸長用コイルを設ける場合にも、これをICチップに内蔵することで、外付けする場合と比較して寄生の影響を受けないようにすることができ、特性を出し易くすることができる。

さらに、本発明に係る発振器は、上記において、前記各増幅器の入出力端と接地との間に夫々配置された容量素子を備え、前記複数の容量素子の少なくとも1つが可変容量素子であることを特徴としている。

これにより、容量素子の容量値を調整することが可能となり、周波数出力を容易に目的とする周波数に調整することができる。

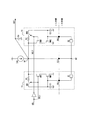

図1は、本発明の第1の実施形態に係る発振器を示す図である。

本実施形態における発振器は、IC内部に配置された発振回路とIC外部に配置された圧電素子との組からなる圧電発振回路11,12を備える。

図中NM1,NM2はインバータとして機能するトランジスタであり、トランジスタNM1,NM2の各ゲートは、夫々圧電素子X1,X2の一端と電極EL1,EL2を介して電気的に接続されている。

圧電発振回路11,12の出力は、図示の通り出力ノードN1で1つに束ねられており、出力ノードN1と圧電素子X1,X2の他端を1つに束ねた共通ノードN2とが、電極EL3を介して電気的に接続された構成となっている。

つまり、この発振器は、2個のインバータを持つために2個の入力を持つが、出力はすべて束ねて1つで実現できる、2入力1出力の回路構成を有している。

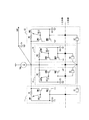

この図2に示すように、各圧電発振回路は、インバータ回路の入力端と出力端との間に帰還抵抗を接続した増幅器をそれぞれ有し、各出力が1つの出力ノードに束ねられている。また、各圧電素子の一端はそれぞれ対応するインバータ回路の入力端に接続され、各圧電素子の他端は共通して上記出力ノードに接続されている。

ところで、N個の異なる発振周波数を得るために、図12に示す構成の発振器をN個持たせる場合、N個の圧電発振回路をそのまま接続すると図13に示すような構成となり、回路規模は単純にN倍となる。また、1組の発振回路と圧電素子とを電気的に接続するためには電極が2個必要であり、N個の圧電発振回路を持つ場合には2×N個の電極が必要となる。

これに対して、本実施形態では、図2に示すように、各発振回路の出力を1つの出力ノードに束ね、各圧電素子の他端を共通して当該出力ノードに接続することで、出力の本数を1本としている。そのため、N個の圧電発振回路を持つ場合でも、電極の数は(N+1)個となり、図13に示す構成と比較して回路規模を抑えることができる。

このとき、集積した発振回路に、所望の周波数の圧電素子を上述したように接続することで、自由に基本波発振を選択することができる発振器とすることができる。

このように、回路規模や部品点数の増大を抑制しつつ、1つの発振器で複数の発振周波数を自由に選択することができる。

なお、上記第1の実施形態においては、2入力1出力の発振回路について説明したが、入力はいくつであってもよい。例えば、4入力1出力の発振回路とした場合の回路構成は図3に示すようになる。この場合、選択信号SEL1〜SEL4は、圧電発振回路11〜14のうち何れか1つがオンするように制御される。仮に、SEL1=Hレベル、SEL2=Lレベル、SEL3=Lレベル、SEL4=Lレベルとすると、トランジスタSM1およびスイッチSW1のみがオンとなり、トランジスタSM2〜SM4およびスイッチSW2〜SW4がオフとなるので、圧電発振回路11のみが動作する状態とすることができる。

この第2の実施形態は、前述した第1の実施形態において、伸長用コイルを追加したものである。

図4は、第2の実施形態に係る2入力1出力の発振器を示す図である。

この図4に示すように、第2の実施形態の発振器は、前述した図1の発振器において、発振器の出力ノードN1と圧電素子の共通ノードN2との間に伸長コイルLsが挿入されていることを除いては、図1の発振器と同様の構成を有する。

次に、伸長コイルの機能について以下に詳述する。

図5は、伸長コイルの機能を説明するための等価回路である。等価容量をCtとすると、CL1,CL2,Lsの直列インピーダンスは以下のようになる。

1/Ct =(1/CL1+1/CL2)−ω2*Ls ………(1)

ここで、ωは角周波数である。また、1/CL=1/CL1+1/CL2とすると、上記(1)式より以下の式が導出される。

1/Ct=1/CL−ω2*Ls

=(1−ω2*Ls*CL )/CL

∴ Ct=CL/(1−ω2*Ls*CL) ………(2)

また、圧電素子の発振周波数fは、直列共振周波数fsを用いると、

f=fs*{1+C1/(2*(C0+Ct))}

=fs*(1+Δ) ………(3)

で表される。ここで、Δ=C1/(2*(C0+Ct))、fs=1/{2*π*√(L1*C1)}である。

このとき、上記(2)式からも明らかなように、

ω2*Ls*CL>1

Ls>1/(ω2*CL) ………(4)

を満たす伸長コイルではCtは負の容量として動作する。この領域では、上記(3)式が示すようにΔが大きくなるので、周波数可変範囲は大きくなる傾向になる。一方、Ctが正の領域ではΔは小さくなるので、周波数可変範囲は伸長コイルがあっても小さくなる傾向になる。

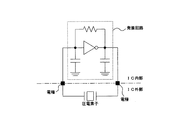

図6は、本実施形態の概念図である。なお、ここではN個の圧電発振回路を備えた例を示している。

この図6に示すように、各圧電発振回路は、インバータ回路の入力端と出力端との間に帰還抵抗を接続した増幅器をそれぞれ有し、各出力が1つの出力ノードに束ねられている。また、各圧電素子の一端はそれぞれ対応するインバータ回路の入力端に接続され、各圧電素子の他端は1つの共通ノードに束ねられ、伸長コイルを介して上記出力ノードに接続されている。

ところで、N個の異なる発振周波数を得るために、図14に示す構成の発振器をN個持たせる場合、N個の圧電発振回路をそのまま接続すると図15に示すような構成となり、回路規模は単純にN倍となる。また、1組の発振回路と圧電素子とを電気的に接続するためには電極が2個必要であり、さらには伸長コイルを接続するための電極も必要となるため、N個の圧電発振回路を持つ場合には3×N個の電極が必要となる。

これに対して、本実施形態では、図4に示すように、各発振回路の出力を1つの出力ノードに束ね、各圧電素子の他端を共通して当該出力ノードに接続することで、出力の本数を1本とするので、挿入する伸長コイルは出力の本数と同じ1個だけで済み、大きな回路規模の増大を伴わない。また、伸長コイルを上記出力ノードと圧電素子の共通ノードとの間に挿入することにより、伸長コイルの挿入による電極の追加を伴わない。

また、伸長コイルを発振器の出力ノードと圧電素子の共通ノードとの間に挿入するので、1個の伸長コイルを各発振回路で共通に使うことができるため、部品点数の削減効果があると共に、回路規模の増大を抑制することができる。

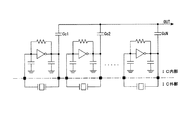

この第3の実施形態は、前述した第1の実施形態において、容量素子C1,C2,Cxを可変容量素子としたものである。

図8は、第3の実施形態に係る2入力1出力の発振器を示す図である。

この図8に示すように、第3の実施形態の発振器は、前述した図1の発振器において、容量素子C1が可変容量素子C1´に置換され、容量素子C2が可変容量素子C2´に置換され、容量素子Cxが可変容量素子Cx´に置換されていることを除いては、図1の発振器と同様の構成を有する。

このような構成により、前述した第1の実施形態と同様に、選択信号SELで閉ループを切替えることで1つの回路で発振周波数が異なる発振回路を構成することができる。さらに、発振回路を構成するC1´、C2´及びCx´は可変容量素子であるので、各容量素子の容量値を変更することで、前記(3)式で示される範囲で周波数を調整することができる。

このように、上記第3の実施形態では、各増幅器の入出力端と接地との間に夫々配置された容量素子を可変容量素子とするので、容易に目的とする周波数に調整することができる。

この第4の実施形態は、前述した第3の実施形態において、伸長コイルを追加したものである。

図9は、第4の実施形態に係る2入力1出力の発振器を示す図である。

この図9に示すように、第4の実施形態の発振器は、前述した図8の発振器において、発振器の出力ノードN1と圧電素子の共通ノードN2との間に伸長コイルLsが挿入されていることを除いては、図8の発振器と同様の構成を有する。

伸長コイルLsは、周波数感度を向上させるために設けられるものであり、ここではICチップ外部に配置するものとする。

この第5の実施形態は、前述した第4の実施形態において、伸長コイルLsをICチップ内部に配置するようにしたものである。

図10は、第5の実施形態に係る2入力1出力の発振器を示す図である。

この図10に示すように、第5の実施形態の発振器は、前述した図9の発振器において、伸長コイルLsが、発振器の出力ノードN1と圧電素子の共通ノードN2との間で、且つICチップ内部に挿入されていることを除いては、図9の発振器と同様の構成を有する。

例えば、発振周波数f=2GHz、CL=10pFとした場合、前記(4)式より、

Ls>0.63[nH]

を得る。この程度の数値ならば、伸長コイルLsを十分内蔵可能である。

なお、上記第3〜第5の実施形態においては、容量C1´、C2´、Cx´をすべて可変容量素子で構成する場合について説明したが、仕様によっては全部を可変容量素子で構成する必要はない。

この第6の実施形態は、前述した第1〜第5の実施形態における発振器をセンサ発振器として適用するようにしたものである。

図11は、第6の実施形態に係る2入力1出力のセンサ発振器を示す図である。ここでは、図1に示す発振器の構成を適用して説明する。

本実施形態では、圧電素子X1を、外部環境を遮断する実装にし、圧電素子X2を、窓あけするなどして外部環境に曝される実装にすることで、圧電素子X1を基準発振器として機能させ、圧電素子X2をセンサ発振器として機能させる。

なお、図11では第1の実施形態の発振器の構成を用いて説明したが、達成したい仕様にあわせて第2〜第5の実施形態の発振器の構成を適用することができる。

21,22 圧電発振回路

C1〜C4,Cx 容量素子

C1´,C2´,Cx´ 可変容量素子

EL1〜EL3 電極

NM1〜NM4 増幅用トランジスタ

SM1〜SM4 選択用トランジスタ

SW1〜SW4 選択用スイッチ

X1〜X4 圧電素子

Claims (5)

- 所定の周波数で励振される圧電素子と、増幅器を有し前記圧電素子に電流を流して当該圧電素子を励振駆動する発振回路と、をそれぞれ含む複数の圧電発振回路を備える発振器であって、

前記複数の発振回路の出力が1つの出力ノードに束ねられ、

前記複数の圧電素子の一端が、それぞれ各圧電素子に対応する前記増幅器の入力端に接続されると共に、前記複数の圧電素子の他端が前記出力ノードに共通して接続されており、

前記複数の圧電素子のうち何れか1つを選択的に駆動する選択回路を備えることを特徴とする発振器。 - 前記選択回路は、電流源と各増幅器との間にそれぞれ介装されたスイッチング素子により構成されており、各スイッチング素子を制御して、前記電流源から前記複数の増幅器のうち何れか1つに電流供給を行うことで、前記複数の圧電素子のうち何れか1つを駆動することを特徴とする請求項1に記載の発振器。

- 前記複数の圧電素子の他端が1つに束ねられた共通ノードと前記出力ノードとの間に、伸長用コイルが接続されていることを特徴とする請求項1又は2に記載の発振器。

- 前記圧電素子を除く回路部をワンチップICで構成したことを特徴とする請求項1〜3の何れか1項に記載の発振器。

- 前記各増幅器の入出力端と接地との間に夫々配置された容量素子を備え、前記複数の容量素子の少なくとも1つが可変容量素子であることを特徴とする請求項1〜4の何れか1項に記載の発振器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008188226A JP5060416B2 (ja) | 2008-07-22 | 2008-07-22 | 発振器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008188226A JP5060416B2 (ja) | 2008-07-22 | 2008-07-22 | 発振器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012156367A Division JP5346110B2 (ja) | 2012-07-12 | 2012-07-12 | センサ発振器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010028507A true JP2010028507A (ja) | 2010-02-04 |

| JP5060416B2 JP5060416B2 (ja) | 2012-10-31 |

Family

ID=41733898

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008188226A Expired - Fee Related JP5060416B2 (ja) | 2008-07-22 | 2008-07-22 | 発振器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5060416B2 (ja) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5711504A (en) * | 1980-06-24 | 1982-01-21 | Sony Corp | Oscillating circuit |

| JPS57168308U (ja) * | 1981-04-17 | 1982-10-23 | ||

| JPS63144716U (ja) * | 1987-03-13 | 1988-09-22 | ||

| JPH01228305A (ja) * | 1988-03-09 | 1989-09-12 | Fujitsu Ltd | 多周波切換発振回路 |

| JP2008060840A (ja) * | 2006-08-30 | 2008-03-13 | Nippon Dempa Kogyo Co Ltd | 2波切替型圧電発振器 |

-

2008

- 2008-07-22 JP JP2008188226A patent/JP5060416B2/ja not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5711504A (en) * | 1980-06-24 | 1982-01-21 | Sony Corp | Oscillating circuit |

| JPS57168308U (ja) * | 1981-04-17 | 1982-10-23 | ||

| JPS63144716U (ja) * | 1987-03-13 | 1988-09-22 | ||

| JPH01228305A (ja) * | 1988-03-09 | 1989-09-12 | Fujitsu Ltd | 多周波切換発振回路 |

| JP2008060840A (ja) * | 2006-08-30 | 2008-03-13 | Nippon Dempa Kogyo Co Ltd | 2波切替型圧電発振器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5060416B2 (ja) | 2012-10-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9112512B2 (en) | Circuit device, oscillation device, and electronic apparatus | |

| JP6106018B2 (ja) | 半導体装置、発振回路及び信号処理システム | |

| JP4977220B2 (ja) | 基本波/オーバートーン水晶発振器 | |

| US20080211593A1 (en) | Oscillation circuit | |

| WO2010084838A1 (ja) | 発振回路 | |

| JP5060416B2 (ja) | 発振器 | |

| JP2014007678A (ja) | 発振器 | |

| JP5346110B2 (ja) | センサ発振器 | |

| JP2012095284A (ja) | 発振器 | |

| JP6509810B2 (ja) | 水晶発振器及び水晶発振器の製造方法 | |

| JP6191952B2 (ja) | パルス信号発生回路およびicチップ | |

| JP6220618B2 (ja) | 共振回路及び発振回路 | |

| JP5098979B2 (ja) | 圧電発振器 | |

| JP2009124530A (ja) | 圧電発振器 | |

| CN114430251B (zh) | 振荡电路、振荡器和振荡电路的控制方法 | |

| JP2008072553A (ja) | 電圧制御水晶発振器 | |

| JP4346948B2 (ja) | 周波数切替水晶発振器 | |

| JP2013141172A (ja) | デュアルレート水晶発振器 | |

| JP2004179706A (ja) | 二周波切替型の水晶発振器 | |

| JP2008312000A (ja) | 圧電発振器 | |

| JP2005130209A (ja) | 圧電発振回路 | |

| JP2005109980A (ja) | スイッチング回路及びそれを有する電圧制御発振装置 | |

| JP2008004977A (ja) | 発振回路 | |

| JP2005159573A (ja) | 周波数切替式発振器 | |

| JP2012253830A (ja) | 圧電発振器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100120 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120712 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120731 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120803 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150810 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |