JP2010010400A - 半導体集積回路装置の製造方法 - Google Patents

半導体集積回路装置の製造方法 Download PDFInfo

- Publication number

- JP2010010400A JP2010010400A JP2008168058A JP2008168058A JP2010010400A JP 2010010400 A JP2010010400 A JP 2010010400A JP 2008168058 A JP2008168058 A JP 2008168058A JP 2008168058 A JP2008168058 A JP 2008168058A JP 2010010400 A JP2010010400 A JP 2010010400A

- Authority

- JP

- Japan

- Prior art keywords

- wafer

- manufacturing

- integrated circuit

- semiconductor integrated

- circuit device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10P30/204—

-

- H10P30/21—

-

- H10P30/212—

-

- H10P50/287—

-

- H10P95/90—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H10D30/0227—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate having both lightly-doped source and drain extensions and source and drain regions self-aligned to the sides of the gate, e.g. lightly-doped drain [LDD] MOSFET or double-diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/017—Manufacturing their source or drain regions, e.g. silicided source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0172—Manufacturing their gate conductors

- H10D84/0177—Manufacturing their gate conductors the gate conductors having different materials or different implants

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Drying Of Semiconductors (AREA)

- Element Separation (AREA)

Abstract

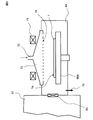

【解決手段】イオン注入101等で硬化したレジストを除去するために、被処理ウエハを、常圧下でベーク102した後、実質的に酸素ガスからなる酸素単ガス雰囲気下において、摂氏300度前後の高温領域でプラズマ・アッシング処理103,104するものである。

【選択図】図1

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

(a)ウエハの第1の主面上に、レジスト膜パターンを形成する工程;

(b)前記レジスト膜パターンがある状態で、前記ウエハの前記第1の主面側に対して、高濃度イオン注入処理を実施する工程;

(c)前記工程(b)の後、常圧下において、摂氏265度以上350度未満のウエハ温度範囲において、前記レジスト膜パターンに対してベーク処理を実施する工程;

(d)前記工程(c)の後、酸素単ガス雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、第1のプラズマ・アッシング処理を実行する工程;

(e)前記工程(d)の後、酸素単ガス雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1のプラズマ・アッシング処理よりも高いRF電力を印加して、第2のプラズマ・アッシング処理を実行する工程。

(f)前記工程(e)の後、前記ウエハの前記第1の主面に対して、ウエット洗浄処理を実行する工程。

(a)ウエハの第1の主面上に、レジスト膜パターンを形成する工程;

(b)前記レジスト膜パターンがある状態で、前記ウエハの前記第1の主面側に対して、高濃度イオン注入処理を実施する工程;

(c)前記工程(b)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハの前記第1の主面に対して、第1のプラズマ・アッシング処理を実行する工程;

(d)前記工程(c)の後、前記ウエハの前記第1の主面の近傍に、実質的にプラズマ雰囲気がない状態に保持する工程;

(e)前記工程(d)の後、前記工程(c)とほぼ同一の気圧下の酸素ガスを主要な成分とする雰囲気中で、前記ウエハの前記第1の主面に対して、第2のプラズマ・アッシング処理を実行する工程。

(f)前記工程(e)の後、前記工程(d)および(e)を所定の繰り返し回数だけ、更に実行する工程。

(g)前記工程(e)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1及び第2のプラズマ・アッシング処理よりも高いRF電力を印加して、第3のプラズマ・アッシング処理を実行する工程。

(g)前記工程(f)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1及び第2のプラズマ・アッシング処理よりも高いRF電力を印加して、第3のプラズマ・アッシング処理を実行する工程。

(h)前記工程(b)と(c)の間において、常圧下において、前記レジスト膜パターンに対してベーク処理を実施する工程。

(i)前記工程(g)の後、前記ウエハの前記第1の主面に対して、ウエット洗浄処理を実行する工程。

(a)ウエハの第1の主面上に、レジスト膜パターンを形成する工程;

(b)前記レジスト膜パターンがある状態で、前記ウエハの前記第1の主面側に対して、高濃度イオン注入処理を実施する工程;

(c)前記工程(b)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハの前記第1の主面に対して、第1のプラズマ・アッシング処理を実行する工程;

(d)前記工程(c)の後、前記ウエハの前記第1の主面の近傍に、実質的にプラズマ雰囲気がない状態に保持する工程;

(e)前記工程(d)の後、酸素ガスを主要な成分とする雰囲気中で、前記ウエハの前記第1の主面に対して、第2のプラズマ・アッシング処理を実行する工程;

(f)前記工程(e)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1及び第2のプラズマ・アッシング処理よりも高いRF電力を印加して、第3のプラズマ・アッシング処理を実行する工程。

(g)前記工程(e)の後で前記工程(f)の前に、前記工程(d)および(e)を所定の繰り返し回数だけ、更に実行する工程。

(h)前記工程(b)と(c)の間において、常圧下において、前記レジスト膜パターンに対してベーク処理を実施する工程。

(i)前記工程(f)の後、前記ウエハの前記第1の主面に対して、ウエット洗浄処理を実行する工程。

(a)ウエハの第1の主面上に、レジスト膜パターンを形成する工程;

(b)前記レジスト膜パターンがある状態で、前記ウエハの前記第1の主面側に対して、高濃度イオン注入処理を実施する工程;

(c)前記工程(b)の後、常圧下において、摂氏265度以上350度未満のウエハ温度範囲において、前記レジスト膜パターンに対してベーク処理を実施する工程;

(d)前記工程(c)の後、酸素単ガス雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、第1のプラズマ・アッシング処理を実行する工程。

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

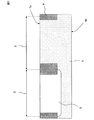

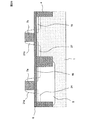

図4は本願の一実施の形態の半導体装置の製造方法における各種のレジスト除去プロセスに使用するベーク・アッシング装置の全体平面構造図である。図5は本願の一実施の形態の半導体装置の製造方法における各種のレジスト除去プロセスに使用するベーク・アッシング装置の要部断面図(図4のX−X’断面)である。ここで使用可能な装置には、たとえばPSK社のTIGMA−4がある。これらに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法における各アッシング処理に使用する装置を説明する。

ここで説明するレジスト除去プロセスは、広くレジスト膜パターン(全面レジスト膜を含む)の除去に適用できる。具体的には、セクション3の図6等で説明するレジスト除去工程155、157、162,164,166,171,173等(図1のイオン注入工程101)に適用して有効である。このうち、高濃度イオン注入後のレジスト除去工程155、157、166,171,173等に適用して有効である。

図1は本願の一実施の形態の半導体装置の製造方法におけるレジスト除去プロセス(高温酸素単ガス・アッシング処理)の流れを示すプロセス・ブロック・フロー図である。図2は本願の一実施の形態の半導体装置の製造方法におけるレジスト除去プロセス中のベーク&アッシング処理の流れを示すプロセス・タイム・チャートである。これらに基づいて、高温酸素単ガス・プロセスを説明する。

(1)摂氏23度程度のAPM洗浄液(アンモニア、過酸化水素、水)をノズルでウエハ・スピン・ステージ上で自転するウエハ1のデバイス面1aへ供給される。処理時間は、たとえば30秒程度である。

(2)ウエハを水洗する。

(3)摂氏23度程度のHPM洗浄液(塩酸、過酸化水素、水)をノズルでウエハ・スピン・ステージ上で自転するウエハ1のデバイス面1aへ供給される。処理時間は、たとえば30秒程度である。

(4)ウエハを水洗する。

(5)摂氏130度程度のSPM洗浄液(アンモニア、過酸化水素、水)をノズルでウエハ・スピン・ステージ上で自転するウエハ1のデバイス面1aへ供給される。処理時間は、たとえば300秒程度である。

(6)ウエハを水洗する。

(7)摂氏65度程度のAPM洗浄液(アンモニア、過酸化水素、水)をノズルでウエハ・スピン・ステージ上で自転するウエハ1のデバイス面1aへ供給される。処理時間は、たとえば300秒程度である。

(8)ウエハを水洗する。

(9)ウエハ1のデバイス面1aに対して水洗および乾燥処理する。

ここに説明するプラズマ中断ソフト・アッシング・プロセスは、サブ・セクション(2−1)の高温酸素単ガス・プロセスのソフト・アッシング・プロセスの改良として説明している。従って、以下に説明しない事項は、サブ・セクション(2−1)をほぼそのまま援用する。しかし、要素処理としてのプラズマ中断ソフト・アッシング・プロセス自体は、広い気圧範囲(プラズマが励起可能な範囲)、広い温度範囲(低温域を含み、摂氏110度から350度程度まで有効である)および酸素を主要な成分とする広範なガス雰囲気(酸素以外の添加ガス、すなわち窒素、フォーミング・ガス(水素を窒素で薄めた混合ガス、通常、窒素100に対して水素3程度の割合)、またはエッチング・ガス(SF系ガス等の弗素含有ガス)等を含む雰囲気)において効果があるため、温度設定またはガス雰囲気を変更することで、先行するベーク処理(たとえば低温域でアッシングする場合等)および後続のハード・アッシング処理の一方または両方は必ずしも必要ではない。ただし、ハード・アッシング処理をしない場合には、その分、ソフト・アッシング工程の時間を延長する等の対応が必要となることは言うまでもない。なお、アッシング処理の際のウエハ・ステージの温度(ウエハ温度)を摂氏265度未満にする場合には、酸素単ガス雰囲気ではなく、スパッタ効果やエッチング性のあるガスを添加することが望ましい。添加率はいずれの場合も、5%程度以上、30%未満の範囲が実用的である。

ここでは、セクション2で説明したアッシング処理を含む一連の半導体ウエハ処理プロセス(90nmテクノロジー・ノードの相補型MISFET型、すんわち、CMIS型のLSIプロセス)の主要部の一例を説明する。

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

1a ウエハのデバイス面(第1の主面)

8,11,14,17,22,25 レジスト膜パターン

102 ベーク処理

103 予備プラズマ・アッシング処理(第1のプラズマ・アッシング処理)

104 主プラズマ・アッシング処理(第2のプラズマ・アッシング処理)

154,156,163,165,169,172 高濃度イオン注入処理

Claims (20)

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)ウエハの第1の主面上に、レジスト膜パターンを形成する工程;

(b)前記レジスト膜パターンがある状態で、前記ウエハの前記第1の主面側に対して、高濃度イオン注入処理を実施する工程;

(c)前記工程(b)の後、常圧下において、摂氏265度以上350度未満のウエハ温度範囲において、前記レジスト膜パターンに対してベーク処理を実施する工程;

(d)前記工程(c)の後、酸素単ガス雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、第1のプラズマ・アッシング処理を実行する工程;

(e)前記工程(d)の後、酸素単ガス雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1のプラズマ・アッシング処理よりも高いRF電力を印加して、第2のプラズマ・アッシング処理を実行する工程。 - 前記1項の半導体集積回路装置の製造方法において、前記ウエハ温度範囲の下限は、摂氏270度である。

- 前記1項の半導体集積回路装置の製造方法において、前記ウエハ温度範囲の下限は、摂氏280度である。

- 前記1項の半導体集積回路装置の製造方法において、前記工程(d)および(e)の前記酸素単ガス雰囲気の添加率は、2体積%未満である。

- 前記1項の半導体集積回路装置の製造方法において、前記工程(d)および(e)の前記酸素単ガス雰囲気の添加率は、1体積%未満である。

- 前記1項の半導体集積回路装置の製造方法において、前記ベーク処理と前記第1のプラズマ・アッシング処理は、同一の処理室の同一のウエハ・ステージ上で行われる。

- 前記1項の半導体集積回路装置の製造方法において、前記第1のプラズマ・アッシング処理と前記第2のプラズマ・アッシング処理は、同一の処理室の同一のウエハ・ステージ上で行われる。

- 前記1項の半導体集積回路装置の製造方法において、前記工程(c)から(e)は、同一の処理室の同一のウエハ・ステージ上で行われる。

- 前記1項の半導体集積回路装置の製造方法において、前記工程(c)から(e)は、同一の処理室内の、ほぼ一定の温度に設定した同一のウエハ・ステージ上で行われる。

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)ウエハの第1の主面上に、レジスト膜パターンを形成する工程;

(b)前記レジスト膜パターンがある状態で、前記ウエハの前記第1の主面側に対して、高濃度イオン注入処理を実施する工程;

(c)前記工程(b)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハの前記第1の主面に対して、第1のプラズマ・アッシング処理を実行する工程;

(d)前記工程(c)の後、前記ウエハの前記第1の主面の近傍に、実質的にプラズマ雰囲気がない状態に保持する工程;

(e)前記工程(d)の後、前記工程(c)とほぼ同一の気圧下の酸素ガスを主要な成分とする雰囲気下で、前記ウエハの前記第1の主面に対して、第2のプラズマ・アッシング処理を実行する工程。 - 前記10項の半導体集積回路装置の製造方法において、更に以下の工程を含む:

(f)前記工程(e)の後、前記工程(d)および(e)を所定の繰り返し回数だけ、更に実行する工程。 - 前記10項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(g)前記工程(e)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1及び第2のプラズマ・アッシング処理よりも高いRF電力を印加して、第3のプラズマ・アッシング処理を実行する工程。 - 前記11項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(g)前記工程(f)の後、酸素ガスを主要な成分とする雰囲気下で、前記ウエハ温度範囲において、前記ウエハの前記第1の主面に対して、前記第1及び第2のプラズマ・アッシング処理よりも高いRF電力を印加して、第3のプラズマ・アッシング処理を実行する工程。 - 前記10項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(h)前記工程(b)と(c)の間において、常圧下において、前記レジスト膜パターンに対してベーク処理を実施する工程。 - 前記10項の半導体集積回路装置の製造方法において、前記工程(c)から(e)は、同一の処理室の同一のウエハ・ステージ上で行われる。

- 前記10項の半導体集積回路装置の製造方法において、前記工程(c)から(e)は、実質的に雰囲気を変更せずに行われる。

- 前記10項の半導体集積回路装置の製造方法において、前記工程(c)から(e)は、同一の処理室内の、ほぼ一定の温度に設定した同一のウエハ・ステージ上で行われる。

- 前記10項の半導体集積回路装置の製造方法において、前記工程(c)から(f)は、同一の処理室の同一のウエハ・ステージ上で行われる。

- 前記10項の半導体集積回路装置の製造方法において、前記工程(c)から(g)は、同一の処理室の同一のウエハ・ステージ上で行われる。

- 前記10項の半導体集積回路装置の製造方法において、前記工程(c)から(h)は、同一の処理室の同一のウエハ・ステージ上で行われる。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168058A JP5027066B2 (ja) | 2008-06-27 | 2008-06-27 | 半導体集積回路装置の製造方法 |

| US12/474,529 US7923361B2 (en) | 2008-06-27 | 2009-05-29 | Method for manufacturing a semiconductor integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008168058A JP5027066B2 (ja) | 2008-06-27 | 2008-06-27 | 半導体集積回路装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010400A true JP2010010400A (ja) | 2010-01-14 |

| JP5027066B2 JP5027066B2 (ja) | 2012-09-19 |

Family

ID=41447964

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008168058A Expired - Fee Related JP5027066B2 (ja) | 2008-06-27 | 2008-06-27 | 半導体集積回路装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7923361B2 (ja) |

| JP (1) | JP5027066B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8999824B2 (en) | 2013-06-25 | 2015-04-07 | Fuji Electric Co., Ltd. | Method for manufacturing semiconductor device by performing multiple ion implantation processes |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9306010B2 (en) | 2012-03-14 | 2016-04-05 | Infineon Technologies Ag | Semiconductor arrangement |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001274139A (ja) * | 2000-03-23 | 2001-10-05 | Nec Corp | アッシング装置およびアッシング方法 |

| JP2005523586A (ja) * | 2002-04-19 | 2005-08-04 | ピーエスケー・インコーポレーテッド | 半導体ウェーハアッシング方法 |

| JP2006059848A (ja) * | 2004-08-17 | 2006-03-02 | Rohm Co Ltd | レジスト除去方法及び半導体装置の製造方法 |

| WO2006106871A1 (ja) * | 2005-03-30 | 2006-10-12 | Matsushita Electric Industrial Co., Ltd. | アッシング装置、アッシング方法および不純物ドーピング装置 |

| JP2008027798A (ja) * | 2006-07-24 | 2008-02-07 | Canon Inc | プラズマ処理装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06204162A (ja) * | 1992-12-28 | 1994-07-22 | Mitsubishi Electric Corp | 半導体装置の製造方法および該方法に用いられるレジスト組成物 |

| JP2001044178A (ja) | 1999-07-30 | 2001-02-16 | Matsushita Electronics Industry Corp | 基板処理方法および基板処理装置 |

| US6800512B1 (en) * | 1999-09-16 | 2004-10-05 | Matsushita Electric Industrial Co., Ltd. | Method of forming insulating film and method of fabricating semiconductor device |

| JP2003188151A (ja) | 2001-12-19 | 2003-07-04 | Hitachi Ltd | 半導体集積回路装置の製造方法 |

| JP2007103509A (ja) | 2005-09-30 | 2007-04-19 | Canon Inc | レジスト処理装置 |

-

2008

- 2008-06-27 JP JP2008168058A patent/JP5027066B2/ja not_active Expired - Fee Related

-

2009

- 2009-05-29 US US12/474,529 patent/US7923361B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001274139A (ja) * | 2000-03-23 | 2001-10-05 | Nec Corp | アッシング装置およびアッシング方法 |

| JP2005523586A (ja) * | 2002-04-19 | 2005-08-04 | ピーエスケー・インコーポレーテッド | 半導体ウェーハアッシング方法 |

| JP2006059848A (ja) * | 2004-08-17 | 2006-03-02 | Rohm Co Ltd | レジスト除去方法及び半導体装置の製造方法 |

| WO2006106871A1 (ja) * | 2005-03-30 | 2006-10-12 | Matsushita Electric Industrial Co., Ltd. | アッシング装置、アッシング方法および不純物ドーピング装置 |

| JP2008027798A (ja) * | 2006-07-24 | 2008-02-07 | Canon Inc | プラズマ処理装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8999824B2 (en) | 2013-06-25 | 2015-04-07 | Fuji Electric Co., Ltd. | Method for manufacturing semiconductor device by performing multiple ion implantation processes |

| US9484343B2 (en) | 2013-06-25 | 2016-11-01 | Fuji Electric Co., Ltd. | Insulated gate bipolar transistor with a free wheeling diode |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5027066B2 (ja) | 2012-09-19 |

| US20090325368A1 (en) | 2009-12-31 |

| US7923361B2 (en) | 2011-04-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5358165B2 (ja) | 半導体集積回路装置の製造方法 | |

| JP4598639B2 (ja) | 半導体装置の製造方法 | |

| JP5595481B2 (ja) | 選択的窒素化の方法 | |

| US20110212610A1 (en) | Methods of forming dual gate of semiconductor device | |

| CN100541718C (zh) | 形成半导体器件精细图形的方法及用其形成接触的方法 | |

| CN104183477B (zh) | 一种制作半导体器件的方法 | |

| KR100786923B1 (ko) | 반도체장치의 제조방법 | |

| JP2000332245A (ja) | 半導体装置の製造方法及びp形半導体素子の製造方法 | |

| JP2007511086A (ja) | トランジスタ製造プロセスにおいて、high−kゲート絶縁体を組み入れる方法 | |

| KR20050085415A (ko) | 다층 게이트 스택 | |

| CN104795362B (zh) | 一种制作半导体器件的方法 | |

| JP5027066B2 (ja) | 半導体集積回路装置の製造方法 | |

| JP2004152862A (ja) | 半導体装置の製造方法 | |

| WO2012141122A1 (ja) | 半導体集積回路装置および半導体集積回路装置の製造方法 | |

| KR20050012611A (ko) | 폴리/텅스텐 게이트 전극을 갖는 반도체 소자의 제조방법 | |

| TWI697031B (zh) | 圖案化方法 | |

| JP4283017B2 (ja) | 半導体装置の製造方法 | |

| JP2007096002A (ja) | 半導体装置の製造方法および半導体装置 | |

| CN119384029A (zh) | 一种半导体结构的制作方法 | |

| JP2004047699A (ja) | 半導体装置の製造方法 | |

| JP4946017B2 (ja) | 半導体装置の製造方法 | |

| US20090104743A1 (en) | Nitrogen Profile in High-K Dielectrics Using Ultrathin Disposable Capping Layers | |

| JP2007234667A (ja) | 半導体装置の製造方法 | |

| JP2005277146A (ja) | 半導体装置の製造方法 | |

| KR101039143B1 (ko) | p형 폴리게이트 형성방법 및 이를 이용한 듀얼 폴리게이트 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110614 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120418 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120426 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120528 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120614 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120621 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150629 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |