JP2010010278A - 半導体装置の製造方法、エッチング幅の補正方法、半導体装置およびmos型トランジスタ - Google Patents

半導体装置の製造方法、エッチング幅の補正方法、半導体装置およびmos型トランジスタ Download PDFInfo

- Publication number

- JP2010010278A JP2010010278A JP2008165896A JP2008165896A JP2010010278A JP 2010010278 A JP2010010278 A JP 2010010278A JP 2008165896 A JP2008165896 A JP 2008165896A JP 2008165896 A JP2008165896 A JP 2008165896A JP 2010010278 A JP2010010278 A JP 2010010278A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- film

- opening

- semiconductor device

- element isolation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Drying Of Semiconductors (AREA)

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

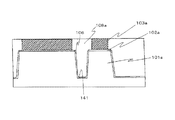

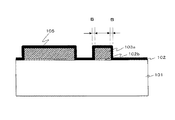

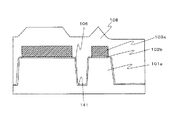

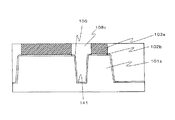

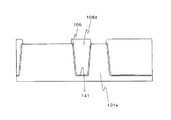

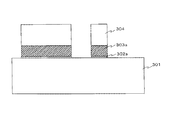

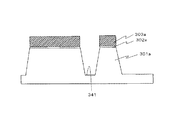

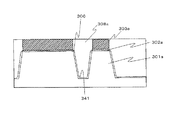

【解決手段】開口部が形成されたシリコン窒化膜と、このシリコン窒化膜の側面を覆う側壁保護膜とをマスクとして、シリコン酸化膜およびシリコン基板の一部をエッチングすることにより、シリコン基板に素子分離用トレンチを形成する(S108)。側壁保護膜は、シリコン窒化膜に関して開口部に隣接する隣接部の幅の計測値に基づいて膜厚調整して形成された酸化膜の一部からなる。

【選択図】図1

Description

半導体基板を準備する工程と、

上記半導体基板の表面上に第1の絶縁膜を形成する工程と、

上記第1の絶縁膜の表面上に第2の絶縁膜を形成する工程と、

上記第2の絶縁膜の表面上に、素子分離用トレンチを形成のための窓部を有するフォトレジストを形成する工程と、

上記フォトレジストをマスクとして、上記第2の絶縁膜の一部を除去することにより、上記第2の絶縁膜に、上記第1の絶縁膜の表面の一部を露出させる開口部を形成する工程と、

上記フォトレジストを除去した後、上記開口部が形成された第2の絶縁膜に関して上記開口部に隣接する隣接部の幅を、上記半導体基板の表面側から見て計測する工程と、

上記開口部から露出した上記第1の絶縁膜の一部と、上記開口部が形成された第2の絶縁膜の側面および表面とを覆う第3の膜を、上記隣接部の幅の計測値に基づいて膜厚調整して形成する工程と、

上記開口部が形成された第2の絶縁膜の側面を覆う上記第3の膜の一部が残るようにエッチングを行うことにより、上記第3の膜の一部からなる側壁保護膜を形成する工程と、

上記開口部が形成された第2の絶縁膜と、上記側壁保護膜とをマスクとして、上記第1の絶縁膜および上記半導体基板の一部をエッチングすることにより、上記半導体基板に上記素子分離用トレンチを形成する工程と

を備えたことを特徴としている。

半導体基板を準備する工程と、

上記半導体基板の表面上に第1の絶縁膜を形成する工程と、

上記第1の絶縁膜の表面上に第2の絶縁膜を形成する工程と、

上記第2の絶縁膜の表面上に、素子分離用トレンチを形成のための窓部を有するフォトレジストを形成する工程と、

上記フォトレジストをマスクとして、上記第2の絶縁膜および上記第1の絶縁膜の一部を除去することにより、上記第2の絶縁膜および上記第1の絶縁膜に、上記半導体基板の表面の一部を露出させる開口部を形成する工程と、

上記フォトレジストを除去した後、上記開口部が形成された第2の絶縁膜に関して上記開口部に隣接する隣接部の幅を、上記半導体基板の表面側から見て計測する工程と、

上記開口部から露出した上記半導体基板の一部と、上記開口部が形成された第1の絶縁膜の側面と、上記開口部が形成された第2の絶縁膜の側面および表面とを覆う第3の膜を、上記隣接部の幅の計測値に基づいて膜厚調整して形成する工程と、

上記開口部が形成された第1の絶縁膜の側面と、上記開口部が形成された第2の絶縁膜の側面とを覆う上記第3の膜の一部が残るようにエッチングを行うことにより、上記第3の膜の一部からなる側壁保護膜を形成する工程と、

上記開口部が形成された第2の絶縁膜と、上記側壁保護膜とをマスクとして、上記半導体基板の一部をエッチングすることにより、上記半導体基板に上記素子分離用トレンチを形成する工程と

を備えたことを特徴としている。

上記フォトレジストを除去した後、上記開口部が形成された第1の絶縁膜に関して上記開口部に隣接する隣接部の幅を、上記半導体基板の表面側から見て計測する工程を備える。

上記第3の膜は、シリコン酸化膜、シリコン窒化膜、SiON膜およびポリシリコン膜のうちのいずれか1つである。

上記第3の膜の膜厚は5〜50nmである。

上記第3の膜の形成は化学蒸気堆積法で行う。

上記第2の絶縁膜はシリコン窒化膜である

上記実施形態の半導体装置の製造方法によれば、上記第2の絶縁膜をシリコン窒化膜とするので、LSI製造工程上、容易に用いることが出来る材料であり、シリコン酸化膜に対して選択的に除去できる。

半導体基板上に形成され、パターニングされた絶縁膜のパターン幅を計測し、

上記パターン幅の計測値と設計基準値との差分を算出し、

上記差分から算出した膜厚を有する補正用絶縁膜を、上記絶縁膜の側面に形成し、

上記絶縁膜および上記補正用絶縁膜をマスクにして、上記半導体基板の一部をエッチングすることを特徴としている。

上記補正用絶縁膜の膜厚は上記差分の0.8〜1.5倍に設定される。

上記絶縁膜のパターン幅と、上記補正用絶縁膜の膜厚を2倍したものとを合わせた値は、半導体素子が有する活性領域の幅に等しい。

上記補正用絶縁膜はサイドウォール状に形成される。

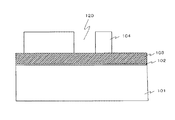

本発明の半導体装置の製造方法を用いて製造された半導体装置であって、

上記素子分離用トレンチと、この素子分離用トレンチで画定された活性領域とを有する半導体基板と、

上記素子分離用トレンチ内に埋め込まれた埋め込み絶縁膜と、

上記活性領域上に形成されたゲート絶縁膜と、

上記ゲート絶縁膜上に形成されたゲート電極と

を備え、

上記埋め込み絶縁膜が上記素子分離用トレンチの側壁の全部を覆っていることを特徴としている。

本発明の半導体装置の製造方法を用いて製造されたMOS型トランジスタであって、

上記素子分離用トレンチと、この素子分離用トレンチで画定された活性領域とを有する半導体基板と、

上記素子分離用トレンチ内に埋め込まれた埋め込み絶縁膜と、

上記活性領域上に形成されたゲート絶縁膜と、

上記ゲート絶縁膜上に形成されたゲート電極と

を備え、

上記埋め込み絶縁膜が上記素子分離用トレンチの側壁の全部を覆っていることを特徴としている。

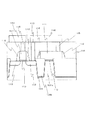

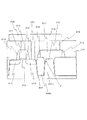

図1は、本発明の第1実施形態のCMOS型トランジスタの製造方法の処理フローを示す図である。この処理フローはステップS101〜S109,S111〜S113を有している。

図3は、本発明の第2実施形態の半導体装置の製造方法の処理フローを示す図である。この処理フローはステップS201〜S209,S211〜S213を有している。

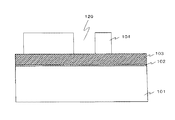

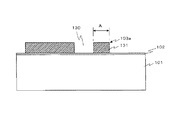

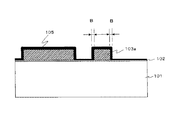

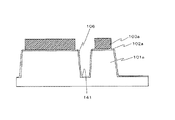

102,102a,102b シリコン酸化膜

103,103a シリコン窒化膜

104 レジストパターン

105 酸化膜

105a,105b 側壁保護膜

108,108a,108b,108c,108d 素子分離用埋め込み絶縁膜

120 窓部

130,230 開口部

131 隣接部

Claims (13)

- 半導体基板を準備する工程と、

上記半導体基板の表面上に第1の絶縁膜を形成する工程と、

上記第1の絶縁膜の表面上に第2の絶縁膜を形成する工程と、

上記第2の絶縁膜の表面上に、素子分離用トレンチを形成のための窓部を有するフォトレジストを形成する工程と、

上記フォトレジストをマスクとして、上記第2の絶縁膜の一部を除去することにより、上記第2の絶縁膜に、上記第1の絶縁膜の表面の一部を露出させる開口部を形成する工程と、

上記フォトレジストを除去した後、上記開口部が形成された第2の絶縁膜に関して上記開口部に隣接する隣接部の幅を、上記半導体基板の表面側から見て計測する工程と、

上記開口部から露出した上記第1の絶縁膜の一部と、上記開口部が形成された第2の絶縁膜の側面および表面とを覆う第3の膜を、上記隣接部の幅の計測値に基づいて膜厚調整して形成する工程と、

上記開口部が形成された第2の絶縁膜の側面を覆う上記第3の膜の一部が残るようにエッチングを行うことにより、上記第3の膜の一部からなる側壁保護膜を形成する工程と、

上記開口部が形成された第2の絶縁膜と、上記側壁保護膜とをマスクとして、上記第1の絶縁膜および上記半導体基板の一部をエッチングすることにより、上記半導体基板に上記素子分離用トレンチを形成する工程と

を備えたことを特徴とする半導体装置の製造方法。 - 半導体基板を準備する工程と、

上記半導体基板の表面上に第1の絶縁膜を形成する工程と、

上記第1の絶縁膜の表面上に第2の絶縁膜を形成する工程と、

上記第2の絶縁膜の表面上に、素子分離用トレンチを形成のための窓部を有するフォトレジストを形成する工程と、

上記フォトレジストをマスクとして、上記第2の絶縁膜および上記第1の絶縁膜の一部を除去することにより、上記第2の絶縁膜および上記第1の絶縁膜に、上記半導体基板の表面の一部を露出させる開口部を形成する工程と、

上記フォトレジストを除去した後、上記開口部が形成された第2の絶縁膜に関して上記開口部に隣接する隣接部の幅を、上記半導体基板の表面側から見て計測する工程と、

上記開口部から露出した上記半導体基板の一部と、上記開口部が形成された第1の絶縁膜の側面と、上記開口部が形成された第2の絶縁膜の側面および表面とを覆う第3の膜を、上記隣接部の幅の計測値に基づいて膜厚調整して形成する工程と、

上記開口部が形成された第1の絶縁膜の側面と、上記開口部が形成された第2の絶縁膜の側面とを覆う上記第3の膜の一部が残るようにエッチングを行うことにより、上記第3の膜の一部からなる側壁保護膜を形成する工程と、

上記開口部が形成された第2の絶縁膜と、上記側壁保護膜とをマスクとして、上記半導体基板の一部をエッチングすることにより、上記半導体基板に上記素子分離用トレンチを形成する工程と

を備えたことを特徴とする半導体装置の製造方法。 - 請求項2に記載の半導体装置の製造方法において、

上記フォトレジストを除去した後、上記開口部が形成された第1の絶縁膜に関して上記開口部に隣接する隣接部の幅を、上記半導体基板の表面側から見て計測する工程を備えたことを特徴とする半導体装置の製造方法。 - 請求項1から3までのいずれか一項に記載の半導体装置の製造方法において、

上記第3の膜は、シリコン酸化膜、シリコン窒化膜、SiON膜およびポリシリコン膜のうちのいずれか1つであることを特徴とする半導体装置の製造方法。 - 請求項1から4までのいずれか一項に記載の半導体装置の製造方法において、

上記第3の膜の膜厚は5〜50nmであることを特徴とする半導体装置の製造方法。 - 請求項1から5までのいずれか一項に記載の半導体装置の製造方法において、

上記第3の膜の形成は化学蒸気堆積法で行うことを特徴とする半導体装置の製造方法。 - 請求項1から6までのいずれか一項に記載の半導体装置の製造方法において、

上記第2の絶縁膜はシリコン窒化膜であることを特徴とする半導体装置の製造方法。 - 半導体基板上に形成され、パターニングされた絶縁膜のパターン幅を計測し、

上記パターン幅の計測値と設計基準値との差分を算出し、

上記差分から算出した膜厚を有する補正用絶縁膜を、上記絶縁膜の側面に形成し、

上記絶縁膜および上記補正用絶縁膜をマスクにして、上記半導体基板の一部をエッチングすることを特徴とするエッチング幅の補正方法。 - 請求項8に記載のエッチング幅の補正方法において、

上記補正用絶縁膜の膜厚は上記差分の0.8〜1.5倍に設定されることを特徴とするエッチング幅の補正方法。 - 請求項8または9に記載のエッチング幅の補正方法において、

上記絶縁膜のパターン幅と、上記補正用絶縁膜の膜厚を2倍したものとを合わせた値は、半導体素子が有する活性領域の幅に等しいことを特徴とするエッチング幅の補正方法。 - 請求項8から10までのいずれか一項に記載のエッチング幅の補正方法において、

上記補正用絶縁膜はサイドウォール状に形成されることを特徴とするエッチング幅の補正方法。 - 請求項1から7までのいずれか一項に記載の半導体装置の製造方法を用いて製造された半導体装置であって、

上記素子分離用トレンチと、この素子分離用トレンチで画定された活性領域とを有する半導体基板と、

上記素子分離用トレンチ内に埋め込まれた埋め込み絶縁膜と、

上記活性領域上に形成されたゲート絶縁膜と、

上記ゲート絶縁膜上に形成されたゲート電極と

を備え、

上記埋め込み絶縁膜が上記素子分離用トレンチの側壁の全部を覆っていることを特徴とする半導体装置。 - 請求項1から7までのいずれか一項に記載の半導体装置の製造方法を用いて製造されたMOS型トランジスタであって、

上記素子分離用トレンチと、この素子分離用トレンチで画定された活性領域とを有する半導体基板と、

上記素子分離用トレンチ内に埋め込まれた埋め込み絶縁膜と、

上記活性領域上に形成されたゲート絶縁膜と、

上記ゲート絶縁膜上に形成されたゲート電極と

を備え、

上記埋め込み絶縁膜が上記素子分離用トレンチの側壁の全部を覆っていることを特徴とするMOS型トランジスタ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008165896A JP5419395B2 (ja) | 2008-06-25 | 2008-06-25 | 半導体装置の製造方法、半導体装置およびmos型トランジスタ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008165896A JP5419395B2 (ja) | 2008-06-25 | 2008-06-25 | 半導体装置の製造方法、半導体装置およびmos型トランジスタ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010278A true JP2010010278A (ja) | 2010-01-14 |

| JP5419395B2 JP5419395B2 (ja) | 2014-02-19 |

Family

ID=41590436

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008165896A Expired - Fee Related JP5419395B2 (ja) | 2008-06-25 | 2008-06-25 | 半導体装置の製造方法、半導体装置およびmos型トランジスタ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5419395B2 (ja) |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6122630A (ja) * | 1984-07-10 | 1986-01-31 | Sony Corp | 半導体装置の製造方法 |

| JPH04158515A (ja) * | 1990-10-23 | 1992-06-01 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPH06244157A (ja) * | 1993-02-12 | 1994-09-02 | Nippon Steel Corp | 半導体装置の製造方法 |

| JPH11145274A (ja) * | 1997-11-10 | 1999-05-28 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2003209105A (ja) * | 2002-01-17 | 2003-07-25 | Mitsubishi Electric Corp | 半導体装置の製造方法、その制御装置およびその制御方法 |

| JP2004228557A (ja) * | 2002-06-24 | 2004-08-12 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2009267111A (ja) * | 2008-04-25 | 2009-11-12 | Tokyo Electron Ltd | 半導体デバイスの製造方法、製造装置、コンピュータプログラム、及びコンピュータ可読記憶媒体 |

-

2008

- 2008-06-25 JP JP2008165896A patent/JP5419395B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6122630A (ja) * | 1984-07-10 | 1986-01-31 | Sony Corp | 半導体装置の製造方法 |

| JPH04158515A (ja) * | 1990-10-23 | 1992-06-01 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPH06244157A (ja) * | 1993-02-12 | 1994-09-02 | Nippon Steel Corp | 半導体装置の製造方法 |

| JPH11145274A (ja) * | 1997-11-10 | 1999-05-28 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2003209105A (ja) * | 2002-01-17 | 2003-07-25 | Mitsubishi Electric Corp | 半導体装置の製造方法、その制御装置およびその制御方法 |

| JP2004228557A (ja) * | 2002-06-24 | 2004-08-12 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2009267111A (ja) * | 2008-04-25 | 2009-11-12 | Tokyo Electron Ltd | 半導体デバイスの製造方法、製造装置、コンピュータプログラム、及びコンピュータ可読記憶媒体 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5419395B2 (ja) | 2014-02-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6939777B2 (en) | Method for manufacturing semiconductor device | |

| US7528031B2 (en) | Semiconductor device and method for manufacturing the same | |

| US20120049253A1 (en) | Semiconductor device and method for fabricating the same | |

| JP2009158813A (ja) | 半導体装置の製造方法、及び半導体装置 | |

| KR101078726B1 (ko) | 반도체 소자 및 그의 제조방법 | |

| KR100827514B1 (ko) | 반도체 소자 및 반도체 소자의 형성 방법 | |

| KR100464229B1 (ko) | 반도체장치의 제조방법 | |

| JP5419395B2 (ja) | 半導体装置の製造方法、半導体装置およびmos型トランジスタ | |

| KR20010107707A (ko) | Sti 구조를 갖는 반도체 장치를 제조하기 위한 방법 | |

| JP2006024605A (ja) | 半導体集積回路装置の製造方法 | |

| KR100762870B1 (ko) | 반도체 소자의 제조방법 | |

| KR100557967B1 (ko) | 반도체 소자의 제조방법 | |

| CN114446812B (zh) | 测试结构及其制作方法 | |

| KR20100074479A (ko) | 반도체 소자 및 그 제조 방법 | |

| JP2009059770A (ja) | 半導体装置及びその製造方法 | |

| JP5266833B2 (ja) | 半導体装置及びその製造方法 | |

| CN120769515A (zh) | 沟槽型mosfet器件及其制作方法 | |

| JP2007048781A (ja) | 半導体装置の製造方法 | |

| KR100660337B1 (ko) | 반도체 소자의 트랜지스터 형성방법 | |

| KR100713937B1 (ko) | 리세스 게이트를 갖는 반도체 소자의 제조방법 | |

| KR100832712B1 (ko) | 반도체 소자의 제조 방법 | |

| KR20090099411A (ko) | 반도체 소자의 형성 방법 | |

| KR20070007468A (ko) | 반도체 장치의 제조 방법. | |

| JP2008042045A (ja) | 半導体装置の製造方法 | |

| KR20090081249A (ko) | 반도체 소자 및 그 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100826 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120911 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121106 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130806 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131004 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131029 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131119 |

|

| LAPS | Cancellation because of no payment of annual fees |