JP2010009711A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2010009711A JP2010009711A JP2008170235A JP2008170235A JP2010009711A JP 2010009711 A JP2010009711 A JP 2010009711A JP 2008170235 A JP2008170235 A JP 2008170235A JP 2008170235 A JP2008170235 A JP 2008170235A JP 2010009711 A JP2010009711 A JP 2010009711A

- Authority

- JP

- Japan

- Prior art keywords

- resistance

- reference voltage

- memory cell

- circuit

- resistance element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

- G11C2013/0054—Read is performed on a reference element, e.g. cell, and the reference sensed value is used to compare the sensed value of the selected cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/563—Multilevel memory reading aspects

- G11C2211/5631—Concurrent multilevel reading of more than one cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

Abstract

【解決手段】メモリセルアレイMAは、整流素子Diと可変抵抗素子VRとを直列接続してなるメモリセルMCを複数のビット線及びワード線の交差部に配置してなる。センスアンプS/Aは、選択メモリセルMCに流れる電流により生じる電圧を参照電圧と比較する。参照電圧発生回路は、可変抵抗素子VRの最大の抵抗値R11と略等しい抵抗値を有する第1の抵抗素子、及び可変抵抗素子VRの最小の抵抗値r00と略等しい抵抗値を有する第2の抵抗素子を並列に接続してなる抵抗回路と、第1の抵抗素子及び前記第2に抵抗素子に定電流を供給する定電流回路とを備える。

【選択図】図4

Description

次に、抵抗変化メモリ装置の回路構成について、図4〜図12を参照して説明する。ここで、図4に示すメモリセルアレイMAは、ビット線BLの長手方向に例えば2Kbit(2048個)、ワード線WLの長手方向に例えば512bitの単位メモリセルMCが配置されている。これにより、1つのメモリセルアレイMA内に1Mbit(約106個)の単位メモリセルMCが配置されている場合を例として説明する。図4は、抵抗変化メモリ装置のカラム制御回路及びロウ制御回路の配置例を示すブロック図である。

図4及び図5に示されるように、ロウデコーダ10には256対のメインワード線MWLx及びMWLbx(x=<255:0>)のいずれか一対、ロウ電源線VRow並びに書き込み駆動線WDRV<7:0>が接続されている。また、ロウデコーダ10には、ワード線群WLx<7:0>が接続されており、このワード線群WLx<7:0>は一列に並んで設けられた複数のメモリセルMCに接続されている。前述のように、1つのロウデコーダ10に接続されるワード線群WLx<7:0>は、ワード線WLx0〜ワード線WLx7までの8本の配線からなる。同様に、書き込み駆動線WDRV<7:0>は、WDRV0〜WDRV7までの8本の配線からなる配線である。

図4及び図6に示されるように、メインロウデコーダ11には256対のメインワード線MWLx及びMWLbx(x=<255:0>)、並びにアドレス信号線が接続されている。本実施の形態に係る抵抗変化メモリ装置のワード線WLは階層化構造を有している。メインロウデコーダ11はプリデコーダである。一組のメインワード線MWLx、MWLbxは1つのロウデコーダ10内の8つのトランジスタ対(図5のQN1、QN2)にそれぞれ接続され、1つのロウデコーダ10は8本のワード線WLx<7:0>のいずれか1本を選択することができる。メインロウデコーダ11は、図6に示すような回路を、1対のメインワード線MWLx、MWLbxごとに有している。

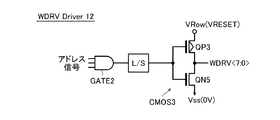

図4及び図7に示されるように、書き込み駆動線ドライバ12には、ロウ電源線VRow及びアドレス信号線が接続されている。ここで、書き込み駆動線ドライバ12も、プリデコーダである。

図4及び図8に示されるように、ロウ電源線ドライバ13には、ロウ電源線VRow及び制御信号線が接続されている。ロウ電源線ドライバ13において、電源VSETHはNMOSトランジスタQN6のドレイン及びゲートに接続される。トランジスタQN6のソースがPMOSトランジスタQP6を介してロウ電源線VRowに接続されている。トランジスタQP6のゲートには制御信号SETonが供給される。

図4及び図9に示されるように、カラムスイッチ20には128対のカラム選択線CSLy及びCSLby(y=<127:0>)のいずれか一対及びローカルデータ線LDQ<3:0>が接続されている。また、カラムスイッチ20には、ビット線群BLy<3:0>が接続されており、このビット線群BLy<3:0>は一列に並んで設けられた複数のメモリセルMCに接続されている。前述のように、1つのカラムスイッチ20に接続されるビット線群BLy<3:0>はビット線BLy0〜ビット線BLy3までの4本の配線からなる。同様に、ローカルデータ線LDQ<3:0>は、LDQ0〜LDQ3までの4本の配線からなる配線である。

図4及び図10に示されるように、カラムデコーダ21には128対のカラム選択線CSLy及びCSLby(y=<127:0>)、並びにカラムアドレス信号CAが入力されるアドレス信号線が接続されている。本実施の形態に係る抵抗変化メモリ装置において、一組のカラム選択線CSLy、CSLbyは1つのカラムスイッチ20内の4つのトランジスタ対(図9のQN11、QN12)にそれぞれ接続され、1つのカラムスイッチ20は4本のビット線群BLy<3:0>を選択駆動することができる。カラムデコーダ21は、図10に示すような回路を、一対のカラム選択線CSLy、CSLbyごとに有している。

図4及び図11に示されるように、センスアンプ/書き込みバッファ22には、カラム電源線VCol1、ローカルデータ線LDQ<3:0>及びデータ入出力線IO<3:0>が接続されている。まず、書き込みバッファ部分について、その構成を説明する。センスアンプ/書き込みバッファ22に接続されたデータ入出力線IO<3:0>は、レベルシフタL/Sを介してPMOSトランジスタQP13及びNMOSトランジスタQN15からなるCMOSインバータCMOS13に接続される。トランジスタQP13のソースにはカラム電源線VCol1が接続されている。カラム電源線VCol1には後述するようにリセット電圧VRESETが印加されている。また、トランジスタQN15のソースは接地されている。そして、トランジスタQP13及びQN15のドレインはともにスイッチSW1を介して、ローカルデータ線LDQ<3:0>に接続されている。

図4及び図12に示されるように、カラム電源線ドライバ23には、カラム電源線VCol1及び制御信号線が接続されている。カラム電源線ドライバ23において、電源VSETHがNMOSトランジスタQN16のドレイン及びゲートに接続され、トランジスタQN16のソースはPMOSトランジスタQP14を介してカラム電源線VCol1に接続されている。トランジスタQP14のゲートには制御信号SETonが供給される。

センスアンプS/Aは、図13に示すように、3つの差動増幅器221〜223、論理回路224、及び3つの参照電圧発生回路225〜227を備えている。

6つの抵抗素子230に流れる電流は平均化され、次の数式が成り立つ。

Claims (5)

- 4種類以上の抵抗値をとり得る可変抵抗素子を含むメモリセルが複数の第1配線及び複数の第2配線の交差部に配置されたメモリセルアレイと、

前記第1配線及び前記第2配線を選択的に駆動する制御回路と、

前記制御回路により選択に駆動された前記第1配線及び前記第2配線の交差部に配置された選択メモリセルに流れる電流により生じる電圧を参照電圧と比較するセンスアンプ回路と、

前記参照電圧を生成する参照電圧発生回路と

を備え、

前記参照電圧発生回路は、

前記可変抵抗素子の最大の抵抗値と略等しい抵抗値を有する第1の抵抗素子、及び前記可変抵抗素子の最小の抵抗値と略等しい抵抗値を有する第2の抵抗素子を並列に接続してなる抵抗回路と、

前記第1の抵抗素子及び前記第2の抵抗素子に流れる電流を等しくする電流調整回路と

を備えたことを特徴とする半導体記憶装置。 - 前記電流調整回路は、ドレイン端子が互いに接続され且つダイオード接続された複数のMOSトランジスタであることを特徴とする請求項1記載の半導体記憶装置。

- 複数個の前記参照電圧発生回路を有し、

1つの前記参照電圧発生回路の中に含まれる前記第1の抵抗素子の数と前記第2の抵抗素子の数との割合が、他の前記参照電圧発生回路における割合とは異なることを特徴とする請求項1記載の半導体記憶装置。 - 前記第1の抵抗素子又は前記第2に抵抗素子に直列に接続され前記第1の抵抗素子又は前記第2の抵抗素子に印加される電圧を制限するクランプ回路を更に備えたことを特徴とする請求項1記載の半導体記憶装置。

- 前記メモリセルは、前記可変抵抗素子と整流素子とを直列接続して構成されることを特徴とする請求項1記載の半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008170235A JP5086919B2 (ja) | 2008-06-30 | 2008-06-30 | 半導体記憶装置 |

| US12/409,958 US7869260B2 (en) | 2008-06-30 | 2009-03-24 | Semiconductor storage device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008170235A JP5086919B2 (ja) | 2008-06-30 | 2008-06-30 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010009711A true JP2010009711A (ja) | 2010-01-14 |

| JP5086919B2 JP5086919B2 (ja) | 2012-11-28 |

Family

ID=41447203

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008170235A Expired - Fee Related JP5086919B2 (ja) | 2008-06-30 | 2008-06-30 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7869260B2 (ja) |

| JP (1) | JP5086919B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011249358A (ja) * | 2010-05-21 | 2011-12-08 | Toshiba Corp | 抵抗変化メモリ |

| US9460785B2 (en) | 2014-03-06 | 2016-10-04 | Kabushiki Kaisha Toshiba | Semiconductor storage device |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8379437B2 (en) | 2009-08-31 | 2013-02-19 | Sandisk 3D, Llc | Flexible multi-pulse set operation for phase-change memories |

| US8125822B2 (en) * | 2009-08-31 | 2012-02-28 | Sandisk 3D Llc | Reducing programming time of a memory cell |

| US9218867B2 (en) | 2013-08-23 | 2015-12-22 | Kabushiki Kaisha Toshiba | Memory device and memory system with sensor |

| US20150055405A1 (en) | 2013-08-23 | 2015-02-26 | Kabushiki Kaisha Toshiba | Memory device and memory system with sensor |

| KR102292643B1 (ko) * | 2015-02-17 | 2021-08-23 | 삼성전자주식회사 | 저항성 메모리 장치, 저항성 메모리 시스템 및 저항성 메모리 시스템의 동작 방법 |

| US9941003B2 (en) * | 2015-11-16 | 2018-04-10 | The Regents Of The University Of Michigan | Multi-level resistive memory structure |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003109375A (ja) * | 2001-09-28 | 2003-04-11 | Canon Inc | 磁気メモリ装置の読み出し回路 |

| JP2004234707A (ja) * | 2002-12-04 | 2004-08-19 | Sharp Corp | 半導体記憶装置及びメモリセルの書き込み並びに消去方法 |

| JP2009020998A (ja) * | 2007-07-12 | 2009-01-29 | Samsung Electronics Co Ltd | 読み出しエラーを減らすことができるマルチレベル相変化メモリ装置及びその読み出し方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3420133B2 (ja) * | 1999-10-13 | 2003-06-23 | Necエレクトロニクス株式会社 | 半導体記憶装置 |

| US6317376B1 (en) * | 2000-06-20 | 2001-11-13 | Hewlett-Packard Company | Reference signal generation for magnetic random access memory devices |

| US6577525B2 (en) * | 2001-08-28 | 2003-06-10 | Micron Technology, Inc. | Sensing method and apparatus for resistance memory device |

| US7262628B2 (en) * | 2004-07-02 | 2007-08-28 | Primarion, Inc. | Digital calibration with lossless current sensing in a multiphase switched power converter |

| US6600690B1 (en) * | 2002-06-28 | 2003-07-29 | Motorola, Inc. | Sense amplifier for a memory having at least two distinct resistance states |

| US7345512B2 (en) * | 2004-05-04 | 2008-03-18 | Silicon Storage Technology, Inc. | Sense amplifier for low voltage high speed sensing |

| JP4153901B2 (ja) | 2004-06-15 | 2008-09-24 | シャープ株式会社 | 半導体記憶装置 |

-

2008

- 2008-06-30 JP JP2008170235A patent/JP5086919B2/ja not_active Expired - Fee Related

-

2009

- 2009-03-24 US US12/409,958 patent/US7869260B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003109375A (ja) * | 2001-09-28 | 2003-04-11 | Canon Inc | 磁気メモリ装置の読み出し回路 |

| JP2004234707A (ja) * | 2002-12-04 | 2004-08-19 | Sharp Corp | 半導体記憶装置及びメモリセルの書き込み並びに消去方法 |

| JP2009020998A (ja) * | 2007-07-12 | 2009-01-29 | Samsung Electronics Co Ltd | 読み出しエラーを減らすことができるマルチレベル相変化メモリ装置及びその読み出し方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011249358A (ja) * | 2010-05-21 | 2011-12-08 | Toshiba Corp | 抵抗変化メモリ |

| US9460785B2 (en) | 2014-03-06 | 2016-10-04 | Kabushiki Kaisha Toshiba | Semiconductor storage device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5086919B2 (ja) | 2012-11-28 |

| US7869260B2 (en) | 2011-01-11 |

| US20090323395A1 (en) | 2009-12-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5106297B2 (ja) | 半導体記憶装置 | |

| JP5100555B2 (ja) | 半導体記憶装置 | |

| JP5178472B2 (ja) | 半導体記憶装置 | |

| JP4856202B2 (ja) | 半導体記憶装置 | |

| JP4806046B2 (ja) | 半導体記憶装置 | |

| JP5086919B2 (ja) | 半導体記憶装置 | |

| JP5127665B2 (ja) | 半導体記憶装置 | |

| US7986575B2 (en) | Semiconductor memory device and redundancy method therefor | |

| JP4846813B2 (ja) | 不揮発性半導体記憶装置 | |

| US8310858B2 (en) | Nonvolatile semiconductor memory device with no decrease in read margin and method of reading the same | |

| US7548467B2 (en) | Bias voltage generator and method generating bias voltage for semiconductor memory device | |

| JP2009266312A (ja) | 半導体記憶装置 | |

| JP5214693B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2011204302A (ja) | 半導体記憶装置 | |

| US8582345B2 (en) | Nonvolatile semiconductor memory device | |

| US20140126270A1 (en) | Semiconductor memory device | |

| JP2010123820A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100915 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120809 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120814 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120907 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |