JP2010004048A - 積層チップパッケージおよびその製造方法 - Google Patents

積層チップパッケージおよびその製造方法 Download PDFInfo

- Publication number

- JP2010004048A JP2010004048A JP2009148252A JP2009148252A JP2010004048A JP 2010004048 A JP2010004048 A JP 2010004048A JP 2009148252 A JP2009148252 A JP 2009148252A JP 2009148252 A JP2009148252 A JP 2009148252A JP 2010004048 A JP2010004048 A JP 2010004048A

- Authority

- JP

- Japan

- Prior art keywords

- main body

- chip package

- electrodes

- semiconductor chip

- substructure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10P72/74—

-

- H10W46/00—

-

- H10W70/093—

-

- H10W72/0198—

-

- H10W90/00—

-

- H10P72/743—

-

- H10W46/101—

-

- H10W46/301—

-

- H10W72/07554—

-

- H10W72/536—

-

- H10W72/547—

-

- H10W72/834—

-

- H10W74/00—

-

- H10W90/22—

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

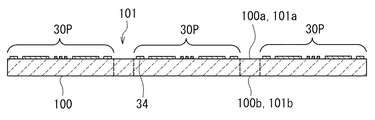

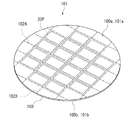

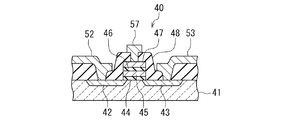

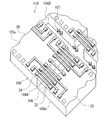

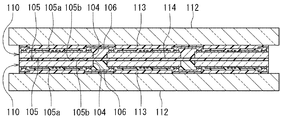

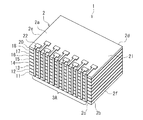

【解決手段】積層チップパッケージ1は、複数の階層部分11〜18を含む本体2と、本体2の側面に配置された配線3A,3Bを備えている。各階層部分は、半導体チップと、半導体チップの少なくとも1つの側面を覆う絶縁部と、半導体チップに接続された複数の電極を含んでいる。絶縁部は、配線3A,3Bが配置された本体2の側面に配置された端面を有している。各電極は、配線3A,3Bが配置された本体2の側面に配置され且つ絶縁部によって囲まれた端面を有している。積層チップパッケージ1を製造する際には、半導体ウェハを処理して、配列された複数の半導体チップ予定部を形成し、少なくとも1つの半導体チップ予定部に隣接するように延びる1以上の溝を形成し、この溝を埋めるように絶縁層を形成し、更に複数の電極を形成して、基礎構造物を作製する。

【選択図】図1

Description

積層チップパッケージの複数の階層部分にそれぞれ対応する複数の基礎構造物であって、各々が対応する階層部分を複数含み、後にそれら対応する階層部分のうちの隣接するもの同士の境界位置で切断される複数の基礎構造物を作製する工程と、

複数の基礎構造物を用いて本体を作製すると共に、本体に対して配線を形成して、積層チップパッケージを完成させる工程とを備えている。

互いに反対側を向いた第1および第2の面を有する1つの半導体ウェハにおける第1の面に処理を施すことによって、それぞれデバイスを含む複数の半導体チップ予定部が配列され、且つ半導体ウェハの第1および第2の面に対応する第1および第2の面を有する基礎構造物前ウェハを作製する工程と、

基礎構造物前ウェハに対して、少なくとも1つの半導体チップ予定部に隣接するように延び、且つ基礎構造物前ウェハの第1の面において開口する1以上の溝を形成する工程と、

1以上の溝を埋めるように、後に絶縁部の一部となる絶縁層を形成する工程と、

一部が絶縁層の上に配置されるように、複数の電極を形成する工程とを含んでいる。

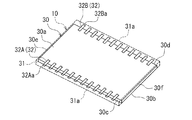

以下、本発明の実施の形態について図面を参照して詳細に説明する。始めに、図1を参照して、本発明の第1の実施の形態に係る積層チップパッケージの構成について説明する。図1は、本実施の形態に係る積層チップパッケージの斜視図である。図1に示したように、本実施の形態に係る積層チップパッケージ1は、直方体形状の本体2を備えている。本体2は、上面2a、下面2b、互いに反対側を向いた第1の側面2cおよび第2の側面2d、ならびに互いに反対側を向いた第3の側面2eおよび第4の側面2fを有している。

次に、本発明の第2の実施の形態について説明する。本実施の形態に係る積層チップパッケージ1の外観は、第1の実施の形態と同様に、図1に示したようになる。

次に、本発明の第3の実施の形態について説明する。図35は、本実施の形態に係る積層チップパッケージ1の斜視図である。図35に示したように、本実施の形態に係る積層チップパッケージ1は、本体2の少なくとも1つの側面に配置された配線3として、本体2の第1の側面2cに配置された配線3Aのみを備え、第1および第2の実施の形態では本体2の第2の側面2dに配置されていた配線3B(図1参照)は備えていない。また、本実施の形態では、端子層20に含まれる複数のパッド状端子22は、全て、本体2の側面2cに配置された端面を有するものになっている。複数のパッド状端子22の端面には、配線3Aが接続されている。

Claims (18)

- 上面、下面および4つの側面を有する本体と、

前記本体の少なくとも1つの側面に配置された配線とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面および4つの側面を有する半導体チップと、前記半導体チップの4つの側面のうちの少なくとも1つの側面を覆う絶縁部と、前記半導体チップに接続された複数の電極とを含み、

前記絶縁部は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置された少なくとも1つの端面を有し、

前記複数の電極の各々は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記配線は、前記複数の階層部分における複数の電極の端面に接続されている積層チップパッケージを製造する方法であって、

前記積層チップパッケージの複数の階層部分にそれぞれ対応する複数の基礎構造物であって、各々が対応する階層部分を複数含み、後にそれら対応する階層部分のうちの隣接するもの同士の境界位置で切断される複数の基礎構造物を作製する工程と、

前記複数の基礎構造物を用いて前記本体を作製すると共に、前記本体に対して前記配線を形成して、積層チップパッケージを完成させる工程とを備え、

前記複数の基礎構造物を作製する工程は、各基礎構造物を作製するための一連の工程として、

互いに反対側を向いた第1および第2の面を有する1つの半導体ウェハにおける前記第1の面に処理を施すことによって、それぞれデバイスを含む複数の半導体チップ予定部が配列され、且つ前記半導体ウェハの第1および第2の面に対応する第1および第2の面を有する基礎構造物前ウェハを作製する工程と、

前記基礎構造物前ウェハに対して、少なくとも1つの半導体チップ予定部に隣接するように延び、且つ前記基礎構造物前ウェハの第1の面において開口する1以上の溝を形成する工程と、

前記1以上の溝を埋めるように、後に前記絶縁部の一部となる絶縁層を形成する工程と、

一部が前記絶縁層の上に配置されるように、前記複数の電極を形成する工程とを含み、

前記積層チップパッケージを完成させる工程において、前記溝が延びる方向に沿って切断面が形成されるように前記絶縁層を切断し、これにより、前記絶縁層の前記切断面によって前記絶縁部の前記少なくとも1つの端面の一部が形成され、且つ前記複数の電極の端面が露出することを特徴とする積層チップパッケージの製造方法。 - 前記積層チップパッケージを完成させる工程は、

前記複数の基礎構造物を用いて、前記複数の階層部分の積層方向と直交する一方向に配列され、それぞれ後に前記本体となる複数の本体予定部を含む本体集合体を作製する工程と、

前記本体集合体における各本体予定部に対してそれぞれ前記配線を形成する工程と、

前記配線の形成後、複数の本体予定部が互いに分離されてそれぞれ前記本体となることによって複数の前記積層チップパッケージが形成されるように、前記本体集合体を切断する工程とを含むことを特徴とする請求項1記載の積層チップパッケージの製造方法。 - 前記本体集合体を作製する工程は、

前記複数の基礎構造物を、前記積層チップパッケージの複数の階層部分の積層の順序に対応させて積層して、積層基礎構造物を作製する工程と、

前記本体集合体が形成されるように、前記積層基礎構造物を切断する工程とを含み、

前記積層基礎構造物を切断する工程において前記絶縁層が切断されることを特徴とする請求項2記載の積層チップパッケージの製造方法。 - 前記複数の電極を形成する工程では、前記複数の電極の形成と同時に、前記絶縁層の上にアライメントマークを形成し、

前記積層基礎構造物を作製する工程では、前記アライメントマークを利用して、積層する前記複数の基礎構造物の位置合わせを行うことを特徴とする請求項3記載の積層チップパッケージの製造方法。 - 前記絶縁層は透明であることを特徴とする請求項4記載の積層チップパッケージの製造方法。

- 前記基礎構造物前ウェハに対して1以上の溝を形成する工程では、前記1以上の溝の底部が前記基礎構造物前ウェハの第2の面に達しないように前記1以上の溝を形成し、

前記積層基礎構造物を作製する工程は、前記複数の基礎構造物の各々に対して、前記1以上の溝が露出するまで、前記基礎構造物前ウェハの第2の面に対応する面から研磨を行う工程を含むことを特徴とする請求項3記載の積層チップパッケージの製造方法。 - 前記本体集合体を作製する工程は、

前記複数の基礎構造物をそれぞれ切断して、後に積層されることによって前記本体集合体を構成することになる複数の要素を作製する工程と、

前記本体集合体が形成されるように、前記複数の要素を積層する工程とを含み、

前記複数の要素を作製する工程において前記絶縁層が切断されることを特徴とする請求項2記載の積層チップパッケージの製造方法。 - 前記複数の電極を形成する工程では、前記複数の電極の形成と同時に、前記絶縁層の上にアライメントマークを形成し、

前記複数の要素を積層する工程では、前記アライメントマークを利用して、積層する前記複数の要素の位置合わせを行うことを特徴とする請求項7記載の積層チップパッケージの製造方法。 - 前記絶縁層は透明であることを特徴とする請求項8記載の積層チップパッケージの製造方法。

- 前記配線を形成する工程では、前記複数の本体集合体を、前記複数の階層部分の積層方向に並べた後、この複数の本体集合体における各本体予定部に対してそれぞれ前記配線を形成することを特徴とする請求項2記載の積層チップパッケージの製造方法。

- 前記複数の電極を形成する工程では、前記複数の電極の形成と同時に、前記絶縁層の上にアライメントマークを形成し、

前記配線を形成する工程では、前記アライメントマークを利用して、前記複数の階層部分の積層方向に並べる前記複数の本体集合体の位置合わせを行うことを特徴とする請求項10記載の積層チップパッケージの製造方法。 - 前記絶縁層は透明であることを特徴とする請求項11記載の積層チップパッケージの製造方法。

- 前記半導体チップの4つの側面のうちの1つの側面のみが前記絶縁部によって覆われ、他の3つの側面は、それぞれ、前記本体の3つの側面に配置されることを特徴とする請求項1記載の積層チップパッケージの製造方法。

- 前記半導体チップの4つの側面のうちの、互いに反対側を向いた2つの側面のみが前記絶縁部によって覆われ、他の2つの側面は、それぞれ、前記本体の2つの側面に配置されることを特徴とする請求項1記載の積層チップパッケージの製造方法。

- 前記半導体チップの4つの側面が前記絶縁部によって覆われ、

前記基礎構造物前ウェハに対して1以上の溝を形成する工程では、複数の第1の溝と複数の第2の溝とを形成し、前記複数の第1の溝と複数の第2の溝は、互いに直交する方向に延びることを特徴とする請求項1記載の積層チップパッケージの製造方法。 - 上面、下面、互いに反対側を向いた第1および第2の側面、ならびに互いに反対側を向いた第3および第4の側面を有する本体と、

前記本体の前記第1の側面に配置された配線とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面、互いに反対側を向いた第1および第2の側面、ならびに互いに反対側を向いた第3および第4の側面を有する半導体チップを含み、

前記半導体チップの第2ないし第4の側面は、それぞれ、前記本体の第2ないし第4の側面に配置され、

前記半導体チップの第1の側面は、前記本体の第1の側面に向き、

前記複数の階層部分の各々は、更に、前記半導体チップの第1の側面を覆う絶縁部と、前記半導体チップに接続された複数の電極とを含み、

前記絶縁部は、前記本体の第1の側面に配置された端面を有し、

前記複数の電極の各々は、前記本体の第1の側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記配線は、前記複数の階層部分における複数の電極の端面に接続されていることを特徴とする積層チップパッケージ。 - 上面、下面、互いに反対側を向いた第1および第2の側面、ならびに互いに反対側を向いた第3および第4の側面を有する本体と、

前記本体の前記第1の側面に配置された第1の配線と、

前記本体の前記第2の側面に配置された第2の配線とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面、互いに反対側を向いた第1および第2の側面、ならびに互いに反対側を向いた第3および第4の側面を有する半導体チップを含み、

前記半導体チップの第3および第4の側面は、それぞれ、前記本体の第3および第4の側面に配置され、

前記半導体チップの第1および第2の側面は、それぞれ、前記本体の第1および第2の側面に向き、

前記複数の階層部分の各々は、更に、前記半導体チップの第1および第2の側面を覆う絶縁部と、前記半導体チップに接続された複数の第1の電極および複数の第2の電極とを含み、

前記絶縁部は、前記本体の第1の側面に配置された第1の端面と前記本体の第2の側面に配置された第2の端面とを有し、

前記複数の第1の電極の各々は、前記本体の第1の側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記複数の第2の電極の各々は、前記本体の第2の側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記第1の配線は、前記複数の階層部分における複数の第1の電極の端面に接続され、

前記第2の配線は、前記複数の階層部分における複数の第2の電極の端面に接続されていることを特徴とする積層チップパッケージ。 - 上面、下面および4つの側面を有する本体と、

前記本体の少なくとも1つの側面に配置された配線とを備え、

前記本体は、積層された複数の階層部分を含み、

前記複数の階層部分の各々は、上面、下面および4つの側面を有する半導体チップと、前記半導体チップの4つの側面のうちの少なくとも1つの側面を覆う絶縁部と、前記半導体チップに接続された複数の電極とを含み、

前記絶縁部は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置された少なくとも1つの端面を有し、

前記複数の電極の各々は、前記配線が配置された前記本体の前記少なくとも1つの側面に配置され且つ前記絶縁部によって囲まれた端面を有し、

前記配線は、前記複数の階層部分における複数の電極の端面に接続されている積層チップパッケージを製造するために用いられ、

前記積層チップパッケージの複数の階層部分の1つに対応し、対応する階層部分を複数含み、後にそれら対応する階層部分のうちの隣接するもの同士の境界位置で切断される積層チップパッケージ用基礎構造物であって、

互いに反対側を向いた第1および第2の面を有する1つの半導体ウェハにおける前記第1の面に処理を施すことによって作製され、それぞれデバイスを含む複数の半導体チップ予定部が配列された基礎構造物本体を備え、

前記基礎構造物本体は、前記半導体ウェハの第1および第2の面に対応する第1および第2の面と、少なくとも1つの半導体チップ予定部に隣接するように延び、且つ前記基礎構造物本体の第1の面において開口する1以上の溝とを有し、

前記1以上の溝は、前記基礎構造物本体の第2の面に達しない底部を有し、

積層チップパッケージ用基礎構造物は、更に、

前記1以上の溝を埋め、後に前記絶縁部の一部となる絶縁層と、

一部が前記絶縁層の上に配置された前記複数の電極とを備えたことを特徴とする積層チップパッケージ用基礎構造物。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/213,645 | 2008-06-23 | ||

| US12/213,645 US7846772B2 (en) | 2008-06-23 | 2008-06-23 | Layered chip package and method of manufacturing same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004048A true JP2010004048A (ja) | 2010-01-07 |

| JP5432604B2 JP5432604B2 (ja) | 2014-03-05 |

Family

ID=41430372

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009148252A Expired - Fee Related JP5432604B2 (ja) | 2008-06-23 | 2009-06-23 | 積層チップパッケージの製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7846772B2 (ja) |

| JP (1) | JP5432604B2 (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011159949A (ja) * | 2010-01-29 | 2011-08-18 | Headway Technologies Inc | 半導体基板、積層チップパッケージおよび半導体プレート並びにこれらの製造方法 |

| JP2011166111A (ja) * | 2010-02-04 | 2011-08-25 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2011166109A (ja) * | 2010-02-04 | 2011-08-25 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2012060102A (ja) * | 2010-09-03 | 2012-03-22 | Headway Technologies Inc | 積層チップパッケージおよびその製造方法 |

| JP2013070021A (ja) * | 2011-09-22 | 2013-04-18 | Headway Technologies Inc | 複合型積層チップパッケージ |

| US11705445B2 (en) | 2021-03-15 | 2023-07-18 | Kioxia Corporation | Semiconductor device manufacturing method and semiconductor device |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0615967Y2 (ja) | 1989-10-25 | 1994-04-27 | 鹿島建設株式会社 | 揚重装置 |

| JP2010135545A (ja) * | 2008-12-04 | 2010-06-17 | Elpida Memory Inc | 半導体装置 |

| US7968374B2 (en) * | 2009-02-06 | 2011-06-28 | Headway Technologies, Inc. | Layered chip package with wiring on the side surfaces |

| US8274165B2 (en) * | 2009-02-10 | 2012-09-25 | Headway Technologies, Inc. | Semiconductor substrate, laminated chip package, semiconductor plate and method of manufacturing the same |

| US8525167B2 (en) * | 2009-10-26 | 2013-09-03 | Headway Technologies, Inc. | Laminated chips package, semiconductor substrate and method of manufacturing the laminated chips package |

| CN102237324A (zh) * | 2010-04-29 | 2011-11-09 | 国碁电子(中山)有限公司 | 集成电路封装结构及方法 |

| US8492175B1 (en) * | 2011-11-28 | 2013-07-23 | Applied Micro Circuits Corporation | System and method for aligning surface mount devices on a substrate |

| US9299670B2 (en) | 2013-03-14 | 2016-03-29 | Freescale Semiconductor, Inc. | Stacked microelectronic packages having sidewall conductors and methods for the fabrication thereof |

| US9524950B2 (en) | 2013-05-31 | 2016-12-20 | Freescale Semiconductor, Inc. | Stacked microelectronic packages having sidewall conductors and methods for the fabrication thereof |

| JP6257291B2 (ja) * | 2013-12-04 | 2018-01-10 | 株式会社ディスコ | パッケージ基板の加工方法 |

| US9305911B2 (en) * | 2013-12-05 | 2016-04-05 | Freescale Semiconductor, Inc. | Devices and stacked microelectronic packages with package surface conductors and adjacent trenches and methods of their fabrication |

| US10388607B2 (en) | 2014-12-17 | 2019-08-20 | Nxp Usa, Inc. | Microelectronic devices with multi-layer package surface conductors and methods of their fabrication |

| US10923456B2 (en) * | 2018-12-20 | 2021-02-16 | Cerebras Systems Inc. | Systems and methods for hierarchical exposure of an integrated circuit having multiple interconnected die |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002050737A (ja) * | 2000-08-02 | 2002-02-15 | Fujitsu Ltd | 半導体素子積層体、半導体素子積層体の製造方法、及び半導体装置 |

| WO2007066409A1 (ja) * | 2005-12-09 | 2007-06-14 | Spansion Llc | 半導体装置およびその製造方法 |

| WO2007071696A1 (fr) * | 2005-12-23 | 2007-06-28 | 3D Plus | Procede de fabrication collective de modules electroniques 3d |

Family Cites Families (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6355976B1 (en) | 1992-05-14 | 2002-03-12 | Reveo, Inc | Three-dimensional packaging technology for multi-layered integrated circuits |

| WO1995025341A1 (en) | 1994-03-15 | 1995-09-21 | Irvine Sensors Corporation | 3d stack of ic chips having leads reached by vias through passivation covering access plane |

| MY114888A (en) | 1994-08-22 | 2003-02-28 | Ibm | Method for forming a monolithic electronic module by stacking planar arrays of integrated circuit chips |

| US5648684A (en) | 1995-07-26 | 1997-07-15 | International Business Machines Corporation | Endcap chip with conductive, monolithic L-connect for multichip stack |

| US5691248A (en) | 1995-07-26 | 1997-11-25 | International Business Machines Corporation | Methods for precise definition of integrated circuit chip edges |

| US5952725A (en) | 1996-02-20 | 1999-09-14 | Micron Technology, Inc. | Stacked semiconductor devices |

| US5953588A (en) * | 1996-12-21 | 1999-09-14 | Irvine Sensors Corporation | Stackable layers containing encapsulated IC chips |

| US7127802B1 (en) * | 1997-11-21 | 2006-10-31 | Fonar Corporation | Method of fabricating a composite plate |

| US6706546B2 (en) | 1998-10-09 | 2004-03-16 | Fujitsu Limited | Optical reflective structures and method for making |

| US20020096760A1 (en) | 2001-01-24 | 2002-07-25 | Gregory Simelgor | Side access layer for semiconductor chip or stack thereof |

| US6734370B2 (en) * | 2001-09-07 | 2004-05-11 | Irvine Sensors Corporation | Multilayer modules with flexible substrates |

| US6611052B2 (en) * | 2001-11-16 | 2003-08-26 | Micron Technology, Inc. | Wafer level stackable semiconductor package |

| KR100486832B1 (ko) * | 2002-02-06 | 2005-05-03 | 삼성전자주식회사 | 반도체 칩과 적층 칩 패키지 및 그 제조 방법 |

| AU2003255254A1 (en) | 2002-08-08 | 2004-02-25 | Glenn J. Leedy | Vertical system integration |

| KR100774775B1 (ko) | 2002-09-17 | 2007-11-07 | 앤터온 비.브이. | 카메라 디바이스, 카메라 디바이스 제조 방법, 웨이퍼스케일 패키지 및 광학 어셈블리 |

| US6936913B2 (en) | 2002-12-11 | 2005-08-30 | Northrop Grumman Corporation | High performance vias for vertical IC packaging |

| KR100541393B1 (ko) | 2003-04-26 | 2006-01-10 | 삼성전자주식회사 | 멀티칩 bga 패키지 |

| US7572373B2 (en) * | 2004-02-11 | 2009-08-11 | Filtertech Inc. | Oil filtration vessel |

| JP4205613B2 (ja) | 2004-03-01 | 2009-01-07 | エルピーダメモリ株式会社 | 半導体装置 |

| US20090115042A1 (en) | 2004-06-04 | 2009-05-07 | Zycube Co., Ltd. | Semiconductor device having three-dimensional stacked structure and method of fabricating the same |

| US7491288B2 (en) | 2004-06-07 | 2009-02-17 | Fujitsu Limited | Method of cutting laminate with laser and laminate |

| KR100575591B1 (ko) * | 2004-07-27 | 2006-05-03 | 삼성전자주식회사 | 웨이퍼 레벨 적층 패키지용 칩 스케일 패키지 및 그 제조 방법 |

| KR100753528B1 (ko) | 2006-01-04 | 2007-08-30 | 삼성전자주식회사 | 웨이퍼 레벨 패키지 및 이의 제조 방법 |

| JP4726640B2 (ja) | 2006-01-20 | 2011-07-20 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8581380B2 (en) | 2006-07-10 | 2013-11-12 | Stats Chippac Ltd. | Integrated circuit packaging system with ultra-thin die |

| US8432026B2 (en) | 2006-08-04 | 2013-04-30 | Stats Chippac Ltd. | Stackable multi-chip package system |

| US7829438B2 (en) * | 2006-10-10 | 2010-11-09 | Tessera, Inc. | Edge connect wafer level stacking |

| US8513789B2 (en) | 2006-10-10 | 2013-08-20 | Tessera, Inc. | Edge connect wafer level stacking with leads extending along edges |

| KR100840788B1 (ko) | 2006-12-05 | 2008-06-23 | 삼성전자주식회사 | 칩 적층 패키지 및 그 제조 방법 |

| JP5014853B2 (ja) | 2007-03-23 | 2012-08-29 | 株式会社日立製作所 | 半導体装置の製造方法 |

| US7883938B2 (en) | 2007-05-22 | 2011-02-08 | United Test And Assembly Center Ltd. | Stacked die semiconductor package and method of assembly |

| US8367471B2 (en) | 2007-06-15 | 2013-02-05 | Micron Technology, Inc. | Semiconductor assemblies, stacked semiconductor devices, and methods of manufacturing semiconductor assemblies and stacked semiconductor devices |

| US8093102B2 (en) | 2007-06-28 | 2012-01-10 | Freescale Semiconductor, Inc. | Process of forming an electronic device including a plurality of singulated die |

| US20090051046A1 (en) | 2007-08-24 | 2009-02-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method for the same |

| US7676912B2 (en) * | 2007-09-05 | 2010-03-16 | Headway Technologies, Inc. | Method of manufacturing electronic component package |

| KR100975652B1 (ko) | 2007-10-05 | 2010-08-17 | 한국과학기술원 | 아연 및 아연합금을 이용한 비아 및 그의 형성 방법, 그를3차원 다중 칩 스택 패키지 제조 방법 |

| JP4828559B2 (ja) | 2008-03-24 | 2011-11-30 | 新光電気工業株式会社 | 配線基板の製造方法及び電子装置の製造方法 |

| KR101458958B1 (ko) | 2008-06-10 | 2014-11-13 | 삼성전자주식회사 | 반도체 칩, 반도체 패키지 및 반도체 칩의 제조 방법 |

| US7745259B2 (en) * | 2008-06-30 | 2010-06-29 | Headway Technologies, Inc. | Layered chip package and method of manufacturing same |

| US7767494B2 (en) * | 2008-06-30 | 2010-08-03 | Headway Technologies, Inc. | Method of manufacturing layered chip package |

| US7993941B2 (en) | 2008-12-05 | 2011-08-09 | Stats Chippac, Ltd. | Semiconductor package and method of forming Z-direction conductive posts embedded in structurally protective encapsulant |

| EP2406821A2 (en) | 2009-03-13 | 2012-01-18 | Tessera, Inc. | Stacked microelectronic assemblies having vias extending through bond pads |

-

2008

- 2008-06-23 US US12/213,645 patent/US7846772B2/en not_active Expired - Fee Related

-

2009

- 2009-06-23 JP JP2009148252A patent/JP5432604B2/ja not_active Expired - Fee Related

-

2010

- 2010-09-02 US US12/923,118 patent/US8134229B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002050737A (ja) * | 2000-08-02 | 2002-02-15 | Fujitsu Ltd | 半導体素子積層体、半導体素子積層体の製造方法、及び半導体装置 |

| WO2007066409A1 (ja) * | 2005-12-09 | 2007-06-14 | Spansion Llc | 半導体装置およびその製造方法 |

| WO2007071696A1 (fr) * | 2005-12-23 | 2007-06-28 | 3D Plus | Procede de fabrication collective de modules electroniques 3d |

| JP2009521116A (ja) * | 2005-12-23 | 2009-05-28 | トロワデー、プリュ | 3d電子モジュールを集積的に製造する方法 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011159949A (ja) * | 2010-01-29 | 2011-08-18 | Headway Technologies Inc | 半導体基板、積層チップパッケージおよび半導体プレート並びにこれらの製造方法 |

| JP2011166111A (ja) * | 2010-02-04 | 2011-08-25 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| JP2011166109A (ja) * | 2010-02-04 | 2011-08-25 | Headway Technologies Inc | 積層チップパッケージの製造方法 |

| US8298862B2 (en) | 2010-02-04 | 2012-10-30 | Headway Technologies, Inc. | Method of manufacturing layered chip package |

| JP2012060102A (ja) * | 2010-09-03 | 2012-03-22 | Headway Technologies Inc | 積層チップパッケージおよびその製造方法 |

| JP2013070021A (ja) * | 2011-09-22 | 2013-04-18 | Headway Technologies Inc | 複合型積層チップパッケージ |

| US11705445B2 (en) | 2021-03-15 | 2023-07-18 | Kioxia Corporation | Semiconductor device manufacturing method and semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100327464A1 (en) | 2010-12-30 |

| JP5432604B2 (ja) | 2014-03-05 |

| US7846772B2 (en) | 2010-12-07 |

| US8134229B2 (en) | 2012-03-13 |

| US20090315189A1 (en) | 2009-12-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5432604B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5275915B2 (ja) | 積層チップパッケージ | |

| JP5461077B2 (ja) | 積層チップパッケージ | |

| JP5451204B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5535560B2 (ja) | メモリデバイスを実現する積層チップパッケージ | |

| JP5102339B2 (ja) | 積層チップパッケージの製造方法 | |

| JP5491802B2 (ja) | ヒートシンクを備えた積層チップパッケージ | |

| JP5275941B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5550872B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5154667B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5004311B2 (ja) | 積層チップパッケージおよびその製造方法 | |

| JP5769293B2 (ja) | 積層チップパッケージの製造方法 | |

| JP4927194B2 (ja) | 積層チップパッケージの製造方法 | |

| JP4948635B2 (ja) | 積層チップパッケージの製造方法 | |

| JP2011097009A (ja) | 複合型積層チップパッケージおよびその製造方法 | |

| JP5228068B2 (ja) | 積層チップパッケージおよびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120217 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130117 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130122 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130418 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131203 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131206 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5432604 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |