JP2009086702A - メモリ制御装置および半導体装置 - Google Patents

メモリ制御装置および半導体装置 Download PDFInfo

- Publication number

- JP2009086702A JP2009086702A JP2007251591A JP2007251591A JP2009086702A JP 2009086702 A JP2009086702 A JP 2009086702A JP 2007251591 A JP2007251591 A JP 2007251591A JP 2007251591 A JP2007251591 A JP 2007251591A JP 2009086702 A JP2009086702 A JP 2009086702A

- Authority

- JP

- Japan

- Prior art keywords

- command

- control device

- register

- memory control

- sdram

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000015654 memory Effects 0.000 title claims abstract description 36

- 239000004065 semiconductor Substances 0.000 title claims abstract description 19

- 238000000034 method Methods 0.000 claims description 11

- 239000000872 buffer Substances 0.000 description 27

- 238000010586 diagram Methods 0.000 description 11

- 238000006243 chemical reaction Methods 0.000 description 6

- 230000004044 response Effects 0.000 description 6

- 230000008859 change Effects 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 230000003111 delayed effect Effects 0.000 description 2

- 238000012795 verification Methods 0.000 description 2

- 230000006835 compression Effects 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000002779 inactivation Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1689—Synchronisation and timing concerns

Abstract

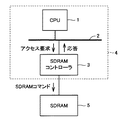

【解決手段】このSDRAMコントローラ3は、発行すべきコマンドとコマンドを発行してから次のコマンドを発行するまでの最小間隔(待機時間)とがCPU1によって書き込まれるレジスタ部6と、レジスタ部6に書き込まれたコマンドを発行した後、レジスタ部6に書き込まれた最小間隔が経過するまで次のコマンドの発行を停止するコマンド発行部9とを備える。したがって、CPU1用のソフトウェアを変更することにより複数種類のSDRAM5に柔軟に対応できる。

【選択図】図3

Description

Claims (10)

- 一連のコマンドを発行して半導体メモリを制御するメモリ制御装置であって、

発行すべきコマンドと該コマンドを発行してから次のコマンドを発行するまで待機すべき時間とが外部制御装置によって書き込まれるレジスタと、

前記レジスタに書き込まれたコマンドを発行した後、前記レジスタに書き込まれた待機すべき時間が経過するまで次のコマンドの発行を停止するコマンド発行部とを備える、メモリ制御装置。 - 前記コマンド発行部は、前記半導体メモリに何もせずに待機することを命令するNOPコマンドも発行する、請求項1に記載のメモリ制御装置。

- 前記待機すべき時間は浮動小数点方式で示されている、請求項1または請求項2に記載のメモリ制御装置。

- 前記コマンド発行部は、前記待機すべき時間として予め定められた値が書き込まれた場合、前記レジスタに書き込まれたコマンドによって決まる時間が経過するまで次のコマンドの発行を停止する、請求項1から請求項3までのいずれかに記載のメモリ制御装置。

- さらに、前記レジスタに書き込まれたコマンドの発行が完了したか否かを判定する判定部を備える、請求項1から請求項4までのいずれかに記載のメモリ制御装置。

- 前記外部制御装置から特定アドレスへのアクセス要求があった場合、前記コマンドの発行が完了するまで応答しない、請求項5に記載のメモリ制御装置。

- 前記判定部は、前記外部制御装置から前記コマンドの発行が完了したか否かの問合せがあった場合、前記コマンドの発行が完了したか否かを応答する、請求項5に記載のメモリ制御装置。

- 前記判定部は、前記外部制御装置からの問合せの有無に関係なく、前記コマンドの発行が完了したか否かを示す信号を前記外部制御装置に出力する、請求項5に記載のメモリ制御装置。

- システムバスと、

前記システムバスに接続されたCPUと、

前記システムバスに接続され、前記CPUからのコマンド情報と、このコマンド情報の次のコマンド情報を外部の半導体メモリに発行するまで待機すべき時間間隔を規定する時間間隔情報とを受けるメモリ制御装置とを備え、

前記メモリ制御装置は、前記コマンド情報と前記時間間隔情報とを格納するレジスタを備え、

前記レジスタは、前記システムバスに出力された前記コマンドと前記時間間隔情報とを受けて、結合された状態で保持する、半導体装置。 - 前記コマンドと前記時間間隔情報は、前記CPUから結合された状態で前記システムバスに出力されることを特徴とする、請求項9に記載の半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007251591A JP5103663B2 (ja) | 2007-09-27 | 2007-09-27 | メモリ制御装置 |

| TW097127156A TW200921671A (en) | 2007-09-27 | 2008-07-17 | Memory control device and semiconductor processing apparatus |

| CNA2008101313510A CN101398793A (zh) | 2007-09-27 | 2008-08-06 | 存储器控制设备和半导体处理装置 |

| US12/237,208 US8151065B2 (en) | 2007-09-27 | 2008-09-24 | Memory control device and semiconductor processing apparatus |

| US13/406,262 US8397036B2 (en) | 2007-09-27 | 2012-02-27 | Memory control device and semiconductor processing apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007251591A JP5103663B2 (ja) | 2007-09-27 | 2007-09-27 | メモリ制御装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009086702A true JP2009086702A (ja) | 2009-04-23 |

| JP5103663B2 JP5103663B2 (ja) | 2012-12-19 |

Family

ID=40509695

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007251591A Active JP5103663B2 (ja) | 2007-09-27 | 2007-09-27 | メモリ制御装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8151065B2 (ja) |

| JP (1) | JP5103663B2 (ja) |

| CN (1) | CN101398793A (ja) |

| TW (1) | TW200921671A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010286899A (ja) * | 2009-06-09 | 2010-12-24 | Canon Inc | メモリ制御回路 |

| JP2013218404A (ja) * | 2012-04-05 | 2013-10-24 | Seiko Epson Corp | 電子機器、及びメモリー制御方法 |

| JP2014135067A (ja) * | 2010-07-29 | 2014-07-24 | Renesas Electronics Corp | 半導体装置及びマイクロコンピュータ |

| JP2017097618A (ja) * | 2015-11-24 | 2017-06-01 | キヤノン株式会社 | コントローラおよび制御方法 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101008990B1 (ko) | 2008-12-05 | 2011-01-17 | 주식회사 하이닉스반도체 | 버퍼인에이블신호 생성회로 및 이를 이용한 입력회로 |

| CN102522113B (zh) * | 2011-09-28 | 2014-09-17 | 华为技术有限公司 | 一种sdram桥接电路 |

| WO2012163019A1 (zh) * | 2011-10-25 | 2012-12-06 | 华为技术有限公司 | 降低数据类芯片外挂ddr功耗的方法及数据类芯片系统 |

| CN102609378B (zh) * | 2012-01-18 | 2016-03-30 | 中国科学院计算技术研究所 | 一种消息式内存访问装置及其访问方法 |

| WO2013165350A1 (en) * | 2012-04-30 | 2013-11-07 | Intel Corporation | Mirroring memory commands to memory devices |

| CN103150272B (zh) * | 2013-03-21 | 2017-05-24 | 珠海市杰理科技股份有限公司 | Sdram的数据存取电路及sdram的数据存取系统 |

| TWI524181B (zh) | 2014-10-13 | 2016-03-01 | 晨星半導體股份有限公司 | 記憶體管理裝置及記憶體管理方法 |

| CN105589656B (zh) * | 2014-10-20 | 2018-10-09 | 晨星半导体股份有限公司 | 存储器管理装置及存储器管理方法 |

| CN105243033B (zh) * | 2015-09-28 | 2018-05-25 | 北京联想核芯科技有限公司 | 数据处理方法及电子设备 |

| US10467157B2 (en) * | 2015-12-16 | 2019-11-05 | Rambus Inc. | Deterministic operation of storage class memory |

| US10719237B2 (en) * | 2016-01-11 | 2020-07-21 | Micron Technology, Inc. | Apparatuses and methods for concurrently accessing multiple partitions of a non-volatile memory |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001034530A (ja) * | 1999-07-16 | 2001-02-09 | Mitsubishi Electric Corp | マイクロコンピュータおよびメモリアクセス制御方法 |

| JP2002526861A (ja) * | 1998-10-02 | 2002-08-20 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 被制御メモリ記憶装置のタイミング・パラメータに基づいてパフォーマンスをチューニングするためのプログラマブル遅延カウンタを備えたメモリ・コントローラ |

| JP2002324009A (ja) * | 2001-04-24 | 2002-11-08 | Nec Corp | メモリ制御方法及びメモリ制御システム |

| JP2003051194A (ja) * | 2001-08-07 | 2003-02-21 | Sharp Corp | 同期型半導体記憶装置モジュールおよびその制御方法、情報機器 |

| JP2004252960A (ja) * | 2003-01-27 | 2004-09-09 | Matsushita Electric Ind Co Ltd | メモリ制御装置 |

| WO2005114669A2 (en) * | 2004-05-21 | 2005-12-01 | Rambus Inc. | System and method for improving performance in computer memory systems supporting multiple memory access latencies |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03210649A (ja) * | 1990-01-12 | 1991-09-13 | Fujitsu Ltd | マイクロコンピュータおよびそのバスサイクル制御方法 |

| JP2000010856A (ja) | 1998-06-19 | 2000-01-14 | Asahi Chem Ind Co Ltd | メモリ制御装置 |

| WO2000011554A1 (en) * | 1998-08-19 | 2000-03-02 | Boris Nikolaevich Vilkov | A system and method for identification of transformation of memory device addresses |

| JP4534336B2 (ja) * | 2000-10-13 | 2010-09-01 | ソニー株式会社 | メモリ装置におけるデータ管理方法 |

| KR100392382B1 (ko) * | 2001-07-27 | 2003-07-23 | 한국전자통신연구원 | 동적 크기 변경 및 메타 데이터 양의 최소화를 위한 논리볼륨 관리 방법 |

| KR100494980B1 (ko) * | 2002-12-02 | 2005-06-13 | 주식회사 넥서스칩스 | 범위선택 가능한 어드레스 디코더와 이를 이용한 고속그래픽 처리용 프레임 메모리 장치 |

-

2007

- 2007-09-27 JP JP2007251591A patent/JP5103663B2/ja active Active

-

2008

- 2008-07-17 TW TW097127156A patent/TW200921671A/zh unknown

- 2008-08-06 CN CNA2008101313510A patent/CN101398793A/zh active Pending

- 2008-09-24 US US12/237,208 patent/US8151065B2/en active Active

-

2012

- 2012-02-27 US US13/406,262 patent/US8397036B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002526861A (ja) * | 1998-10-02 | 2002-08-20 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 被制御メモリ記憶装置のタイミング・パラメータに基づいてパフォーマンスをチューニングするためのプログラマブル遅延カウンタを備えたメモリ・コントローラ |

| JP2001034530A (ja) * | 1999-07-16 | 2001-02-09 | Mitsubishi Electric Corp | マイクロコンピュータおよびメモリアクセス制御方法 |

| JP2002324009A (ja) * | 2001-04-24 | 2002-11-08 | Nec Corp | メモリ制御方法及びメモリ制御システム |

| JP2003051194A (ja) * | 2001-08-07 | 2003-02-21 | Sharp Corp | 同期型半導体記憶装置モジュールおよびその制御方法、情報機器 |

| JP2004252960A (ja) * | 2003-01-27 | 2004-09-09 | Matsushita Electric Ind Co Ltd | メモリ制御装置 |

| WO2005114669A2 (en) * | 2004-05-21 | 2005-12-01 | Rambus Inc. | System and method for improving performance in computer memory systems supporting multiple memory access latencies |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010286899A (ja) * | 2009-06-09 | 2010-12-24 | Canon Inc | メモリ制御回路 |

| JP2014135067A (ja) * | 2010-07-29 | 2014-07-24 | Renesas Electronics Corp | 半導体装置及びマイクロコンピュータ |

| JP2016012362A (ja) * | 2010-07-29 | 2016-01-21 | ルネサスエレクトロニクス株式会社 | マイクロコンピュータ及びデータ処理システム |

| JP2013218404A (ja) * | 2012-04-05 | 2013-10-24 | Seiko Epson Corp | 電子機器、及びメモリー制御方法 |

| JP2017097618A (ja) * | 2015-11-24 | 2017-06-01 | キヤノン株式会社 | コントローラおよび制御方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200921671A (en) | 2009-05-16 |

| US8151065B2 (en) | 2012-04-03 |

| US20120159002A1 (en) | 2012-06-21 |

| US20090089517A1 (en) | 2009-04-02 |

| JP5103663B2 (ja) | 2012-12-19 |

| CN101398793A (zh) | 2009-04-01 |

| US8397036B2 (en) | 2013-03-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5103663B2 (ja) | メモリ制御装置 | |

| JP3843145B2 (ja) | 同期型半導体記憶装置 | |

| KR100816053B1 (ko) | 셀프 카피 기능을 가지는 메모리 장치, 메모리 시스템 및듀얼 포트 메모리 장치 | |

| US7675800B2 (en) | Semiconductor memory, memory controller, system, and operating method of semiconductor memory | |

| EP2972914B1 (en) | Apparatuses and methods for variable latency memory operations | |

| JP4507186B2 (ja) | モードレジスタにおけるバースト長設定の変更を行わずに、異なるバースト長のアクセスをサポートするdram | |

| US20060104150A1 (en) | Semiconductor memory device | |

| JP5391833B2 (ja) | メモリコントローラ、システムおよび半導体メモリのアクセス制御方法 | |

| TW517236B (en) | Synchronous semiconductor memory device and method for controlling input circuit of synchronous semiconductor memory device | |

| US8069303B2 (en) | Method and apparatus for controlling memory precharge operation | |

| US7788414B2 (en) | Memory controller and method of controlling a memory | |

| US7254090B2 (en) | Semiconductor memory device | |

| JP2007087375A (ja) | メモリ制御システムおよびメモリ制御回路 | |

| US7180822B2 (en) | Semiconductor memory device without decreasing performance thereof even if refresh operation or word line changing operation occur during burst operation | |

| JP2006059489A (ja) | 半導体記憶装置とテスト回路及び方法 | |

| US20070162713A1 (en) | Memory having status register read function | |

| JP4759717B2 (ja) | 同期型不揮発性メモリおよびメモリシステム | |

| JP2000067576A (ja) | 半導体記憶装置 | |

| JP4628319B2 (ja) | 同期型半導体記憶装置 | |

| JP3489497B2 (ja) | メモリコントローラ | |

| JP2009217310A (ja) | メモリアクセス方法及びメモリアクセス装置 | |

| KR100903387B1 (ko) | 전력 소모를 줄이는 반도체 메모리 장치 | |

| JP2002207541A (ja) | マイクロコンピュータ及びデータ処理装置 | |

| JP3563340B2 (ja) | メモリコントローラ | |

| US20070189084A1 (en) | Reduced pin count synchronous dynamic random access memory interface |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100218 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100602 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120615 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120626 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120809 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120904 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120912 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5103663 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151012 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |