JP2007201435A - 半導体装置、及び半導体装置の作製方法 - Google Patents

半導体装置、及び半導体装置の作製方法 Download PDFInfo

- Publication number

- JP2007201435A JP2007201435A JP2006342255A JP2006342255A JP2007201435A JP 2007201435 A JP2007201435 A JP 2007201435A JP 2006342255 A JP2006342255 A JP 2006342255A JP 2006342255 A JP2006342255 A JP 2006342255A JP 2007201435 A JP2007201435 A JP 2007201435A

- Authority

- JP

- Japan

- Prior art keywords

- conductive layer

- layer

- organic compound

- memory element

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 247

- 238000000034 method Methods 0.000 title claims abstract description 130

- 238000004519 manufacturing process Methods 0.000 title claims description 40

- 238000003860 storage Methods 0.000 claims abstract description 32

- 230000015654 memory Effects 0.000 claims description 442

- 150000002894 organic compounds Chemical class 0.000 claims description 248

- 230000002093 peripheral effect Effects 0.000 claims description 40

- 230000008569 process Effects 0.000 abstract description 15

- 239000010410 layer Substances 0.000 description 912

- 239000000758 substrate Substances 0.000 description 94

- 239000010408 film Substances 0.000 description 64

- 239000000463 material Substances 0.000 description 52

- 238000005192 partition Methods 0.000 description 37

- 230000015572 biosynthetic process Effects 0.000 description 34

- -1 nickel carbonate (NiCO 3 ) Carbonates Chemical class 0.000 description 34

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 24

- 239000007789 gas Substances 0.000 description 22

- 230000006870 function Effects 0.000 description 21

- 229920005989 resin Polymers 0.000 description 21

- 239000011347 resin Substances 0.000 description 21

- 229910052782 aluminium Inorganic materials 0.000 description 20

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 20

- 230000008859 change Effects 0.000 description 18

- 239000000956 alloy Substances 0.000 description 17

- 238000002425 crystallisation Methods 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 17

- 239000010936 titanium Substances 0.000 description 17

- 230000009471 action Effects 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 15

- 229910045601 alloy Inorganic materials 0.000 description 15

- 230000008025 crystallization Effects 0.000 description 15

- 230000003287 optical effect Effects 0.000 description 15

- 239000010949 copper Substances 0.000 description 14

- 239000012212 insulator Substances 0.000 description 14

- 238000007639 printing Methods 0.000 description 14

- 229910052710 silicon Inorganic materials 0.000 description 14

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 238000010438 heat treatment Methods 0.000 description 13

- 239000010703 silicon Substances 0.000 description 13

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 12

- 239000010931 gold Substances 0.000 description 12

- 239000011159 matrix material Substances 0.000 description 12

- 230000007246 mechanism Effects 0.000 description 12

- 229910052719 titanium Inorganic materials 0.000 description 12

- 229910052759 nickel Inorganic materials 0.000 description 11

- 238000004544 sputter deposition Methods 0.000 description 11

- 238000005530 etching Methods 0.000 description 10

- 239000001257 hydrogen Substances 0.000 description 10

- 229910052739 hydrogen Inorganic materials 0.000 description 10

- 239000012535 impurity Substances 0.000 description 10

- 238000007740 vapor deposition Methods 0.000 description 10

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical group C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 9

- 239000004417 polycarbonate Substances 0.000 description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 9

- 238000000926 separation method Methods 0.000 description 9

- 239000010409 thin film Substances 0.000 description 9

- 229910052721 tungsten Inorganic materials 0.000 description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 8

- 229910021417 amorphous silicon Inorganic materials 0.000 description 8

- 229910052802 copper Inorganic materials 0.000 description 8

- 238000010168 coupling process Methods 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 229910052750 molybdenum Inorganic materials 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N nitrogen Substances N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 8

- 229910052697 platinum Inorganic materials 0.000 description 8

- 230000002829 reductive effect Effects 0.000 description 8

- 239000010937 tungsten Substances 0.000 description 8

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 7

- 150000001875 compounds Chemical class 0.000 description 7

- 230000005669 field effect Effects 0.000 description 7

- 229910052737 gold Inorganic materials 0.000 description 7

- 239000011572 manganese Substances 0.000 description 7

- 239000011733 molybdenum Substances 0.000 description 7

- 229920000728 polyester Polymers 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 229910052709 silver Inorganic materials 0.000 description 7

- 239000000126 substance Substances 0.000 description 7

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 239000004020 conductor Substances 0.000 description 6

- 230000005674 electromagnetic induction Effects 0.000 description 6

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 6

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 6

- 230000001678 irradiating effect Effects 0.000 description 6

- 229910052760 oxygen Inorganic materials 0.000 description 6

- 239000001301 oxygen Substances 0.000 description 6

- 229920000123 polythiophene Polymers 0.000 description 6

- 238000012545 processing Methods 0.000 description 6

- 239000004332 silver Substances 0.000 description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 6

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- YMWUJEATGCHHMB-UHFFFAOYSA-N Dichloromethane Chemical compound ClCCl YMWUJEATGCHHMB-UHFFFAOYSA-N 0.000 description 5

- 229910000846 In alloy Inorganic materials 0.000 description 5

- 239000004952 Polyamide Substances 0.000 description 5

- 239000004743 Polypropylene Substances 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 5

- 239000012790 adhesive layer Substances 0.000 description 5

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 5

- 229910017052 cobalt Inorganic materials 0.000 description 5

- 239000010941 cobalt Substances 0.000 description 5

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 5

- 230000008878 coupling Effects 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 239000010419 fine particle Substances 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 5

- 238000007689 inspection Methods 0.000 description 5

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical compound C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 5

- 229910052757 nitrogen Inorganic materials 0.000 description 5

- 229910052763 palladium Inorganic materials 0.000 description 5

- 239000002245 particle Substances 0.000 description 5

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 5

- 229920002647 polyamide Polymers 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 239000002861 polymer material Substances 0.000 description 5

- 229920001155 polypropylene Polymers 0.000 description 5

- 230000001737 promoting effect Effects 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 229910000679 solder Inorganic materials 0.000 description 5

- IYZMXHQDXZKNCY-UHFFFAOYSA-N 1-n,1-n-diphenyl-4-n,4-n-bis[4-(n-phenylanilino)phenyl]benzene-1,4-diamine Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 IYZMXHQDXZKNCY-UHFFFAOYSA-N 0.000 description 4

- SPDPTFAJSFKAMT-UHFFFAOYSA-N 1-n-[4-[4-(n-[4-(3-methyl-n-(3-methylphenyl)anilino)phenyl]anilino)phenyl]phenyl]-4-n,4-n-bis(3-methylphenyl)-1-n-phenylbenzene-1,4-diamine Chemical group CC1=CC=CC(N(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=CC(=CC=2)N(C=2C=C(C)C=CC=2)C=2C=C(C)C=CC=2)C=2C=C(C)C=CC=2)=C1 SPDPTFAJSFKAMT-UHFFFAOYSA-N 0.000 description 4

- DHDHJYNTEFLIHY-UHFFFAOYSA-N 4,7-diphenyl-1,10-phenanthroline Chemical compound C1=CC=CC=C1C1=CC=NC2=C1C=CC1=C(C=3C=CC=CC=3)C=CN=C21 DHDHJYNTEFLIHY-UHFFFAOYSA-N 0.000 description 4

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical compound CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 4

- 239000004695 Polyether sulfone Substances 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- 229920000265 Polyparaphenylene Polymers 0.000 description 4

- FAPWRFPIFSIZLT-UHFFFAOYSA-M Sodium chloride Chemical compound [Na+].[Cl-] FAPWRFPIFSIZLT-UHFFFAOYSA-M 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- 239000007983 Tris buffer Substances 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 4

- XJHCXCQVJFPJIK-UHFFFAOYSA-M caesium fluoride Chemical compound [F-].[Cs+] XJHCXCQVJFPJIK-UHFFFAOYSA-M 0.000 description 4

- 239000011575 calcium Substances 0.000 description 4

- 229910052799 carbon Inorganic materials 0.000 description 4

- 238000010549 co-Evaporation Methods 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 239000003822 epoxy resin Substances 0.000 description 4

- 235000013305 food Nutrition 0.000 description 4

- 229910052738 indium Inorganic materials 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 239000011777 magnesium Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 229910044991 metal oxide Inorganic materials 0.000 description 4

- 150000004706 metal oxides Chemical class 0.000 description 4

- YRZZLAGRKZIJJI-UHFFFAOYSA-N oxyvanadium phthalocyanine Chemical compound [V+2]=O.C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 YRZZLAGRKZIJJI-UHFFFAOYSA-N 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 229920006393 polyether sulfone Polymers 0.000 description 4

- 229920002098 polyfluorene Polymers 0.000 description 4

- IOLCXVTUBQKXJR-UHFFFAOYSA-M potassium bromide Chemical compound [K+].[Br-] IOLCXVTUBQKXJR-UHFFFAOYSA-M 0.000 description 4

- NLKNQRATVPKPDG-UHFFFAOYSA-M potassium iodide Chemical compound [K+].[I-] NLKNQRATVPKPDG-UHFFFAOYSA-M 0.000 description 4

- 239000011241 protective layer Substances 0.000 description 4

- 238000007650 screen-printing Methods 0.000 description 4

- 230000008054 signal transmission Effects 0.000 description 4

- 229910021332 silicide Inorganic materials 0.000 description 4

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229920002554 vinyl polymer Polymers 0.000 description 4

- JIAARYAFYJHUJI-UHFFFAOYSA-L zinc dichloride Chemical compound [Cl-].[Cl-].[Zn+2] JIAARYAFYJHUJI-UHFFFAOYSA-L 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- FQJQNLKWTRGIEB-UHFFFAOYSA-N 2-(4-tert-butylphenyl)-5-[3-[5-(4-tert-butylphenyl)-1,3,4-oxadiazol-2-yl]phenyl]-1,3,4-oxadiazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=C(C=CC=2)C=2OC(=NN=2)C=2C=CC(=CC=2)C(C)(C)C)O1 FQJQNLKWTRGIEB-UHFFFAOYSA-N 0.000 description 3

- ZVFQEOPUXVPSLB-UHFFFAOYSA-N 3-(4-tert-butylphenyl)-4-phenyl-5-(4-phenylphenyl)-1,2,4-triazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C(N1C=2C=CC=CC=2)=NN=C1C1=CC=C(C=2C=CC=CC=2)C=C1 ZVFQEOPUXVPSLB-UHFFFAOYSA-N 0.000 description 3

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 3

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 3

- WCUXLLCKKVVCTQ-UHFFFAOYSA-M Potassium chloride Chemical compound [Cl-].[K+] WCUXLLCKKVVCTQ-UHFFFAOYSA-M 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 229910006404 SnO 2 Inorganic materials 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- BZHJMEDXRYGGRV-UHFFFAOYSA-N Vinyl chloride Chemical compound ClC=C BZHJMEDXRYGGRV-UHFFFAOYSA-N 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 229920000547 conjugated polymer Polymers 0.000 description 3

- 150000004696 coordination complex Chemical class 0.000 description 3

- 238000007599 discharging Methods 0.000 description 3

- 238000005566 electron beam evaporation Methods 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 230000008020 evaporation Effects 0.000 description 3

- 239000002657 fibrous material Substances 0.000 description 3

- 238000007667 floating Methods 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- 230000036541 health Effects 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 229910052748 manganese Inorganic materials 0.000 description 3

- 229910052754 neon Inorganic materials 0.000 description 3

- 238000004806 packaging method and process Methods 0.000 description 3

- 230000035699 permeability Effects 0.000 description 3

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical compound N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920001197 polyacetylene Polymers 0.000 description 3

- 229920000515 polycarbonate Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 239000010948 rhodium Substances 0.000 description 3

- 239000000523 sample Substances 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 239000011734 sodium Substances 0.000 description 3

- 239000002904 solvent Substances 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- 229920003002 synthetic resin Polymers 0.000 description 3

- 239000000057 synthetic resin Substances 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 3

- 229910001887 tin oxide Inorganic materials 0.000 description 3

- 239000003981 vehicle Substances 0.000 description 3

- 239000011701 zinc Substances 0.000 description 3

- STTGYIUESPWXOW-UHFFFAOYSA-N 2,9-dimethyl-4,7-diphenyl-1,10-phenanthroline Chemical compound C=12C=CC3=C(C=4C=CC=CC=4)C=C(C)N=C3C2=NC(C)=CC=1C1=CC=CC=C1 STTGYIUESPWXOW-UHFFFAOYSA-N 0.000 description 2

- UOCMXZLNHQBBOS-UHFFFAOYSA-N 2-(1,3-benzoxazol-2-yl)phenol zinc Chemical compound [Zn].Oc1ccccc1-c1nc2ccccc2o1.Oc1ccccc1-c1nc2ccccc2o1 UOCMXZLNHQBBOS-UHFFFAOYSA-N 0.000 description 2

- HONWGFNQCPRRFM-UHFFFAOYSA-N 2-n-(3-methylphenyl)-1-n,1-n,2-n-triphenylbenzene-1,2-diamine Chemical compound CC1=CC=CC(N(C=2C=CC=CC=2)C=2C(=CC=CC=2)N(C=2C=CC=CC=2)C=2C=CC=CC=2)=C1 HONWGFNQCPRRFM-UHFFFAOYSA-N 0.000 description 2

- PZLZJGZGJHZQAU-UHFFFAOYSA-N 3-(4-tert-butylphenyl)-4-(4-ethylphenyl)-5-(4-phenylphenyl)-1,2,4-triazole Chemical compound C1=CC(CC)=CC=C1N1C(C=2C=CC(=CC=2)C(C)(C)C)=NN=C1C1=CC=C(C=2C=CC=CC=2)C=C1 PZLZJGZGJHZQAU-UHFFFAOYSA-N 0.000 description 2

- FCNCGHJSNVOIKE-UHFFFAOYSA-N 9,10-diphenylanthracene Chemical compound C1=CC=CC=C1C(C1=CC=CC=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 FCNCGHJSNVOIKE-UHFFFAOYSA-N 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- VTYYLEPIZMXCLO-UHFFFAOYSA-L Calcium carbonate Chemical compound [Ca+2].[O-]C([O-])=O VTYYLEPIZMXCLO-UHFFFAOYSA-L 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- HEDRZPFGACZZDS-UHFFFAOYSA-N Chloroform Chemical compound ClC(Cl)Cl HEDRZPFGACZZDS-UHFFFAOYSA-N 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 2

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 244000126211 Hericium coralloides Species 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- UQSXHKLRYXJYBZ-UHFFFAOYSA-N Iron oxide Chemical compound [Fe]=O UQSXHKLRYXJYBZ-UHFFFAOYSA-N 0.000 description 2

- CSNNHWWHGAXBCP-UHFFFAOYSA-L Magnesium sulfate Chemical compound [Mg+2].[O-][S+2]([O-])([O-])[O-] CSNNHWWHGAXBCP-UHFFFAOYSA-L 0.000 description 2

- 239000004640 Melamine resin Substances 0.000 description 2

- 229920000877 Melamine resin Polymers 0.000 description 2

- ZCQWOFVYLHDMMC-UHFFFAOYSA-N Oxazole Chemical compound C1=COC=N1 ZCQWOFVYLHDMMC-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229920000282 Poly(3-cyclohexylthiophene) Polymers 0.000 description 2

- 229920000291 Poly(9,9-dioctylfluorene) Polymers 0.000 description 2

- 229910003902 SiCl 4 Inorganic materials 0.000 description 2

- 229910021612 Silver iodide Inorganic materials 0.000 description 2

- CDBYLPFSWZWCQE-UHFFFAOYSA-L Sodium Carbonate Chemical compound [Na+].[Na+].[O-]C([O-])=O CDBYLPFSWZWCQE-UHFFFAOYSA-L 0.000 description 2

- FZWLAAWBMGSTSO-UHFFFAOYSA-N Thiazole Chemical compound C1=CSC=N1 FZWLAAWBMGSTSO-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- FIKZYNUYDIQYGA-UHFFFAOYSA-N [O-2].[Zn+2].[In+3].[W+2]=O Chemical compound [O-2].[Zn+2].[In+3].[W+2]=O FIKZYNUYDIQYGA-UHFFFAOYSA-N 0.000 description 2

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 2

- VSCWAEJMTAWNJL-UHFFFAOYSA-K aluminium trichloride Chemical compound Cl[Al](Cl)Cl VSCWAEJMTAWNJL-UHFFFAOYSA-K 0.000 description 2

- RDOXTESZEPMUJZ-UHFFFAOYSA-N anisole Chemical compound COC1=CC=CC=C1 RDOXTESZEPMUJZ-UHFFFAOYSA-N 0.000 description 2

- MWPLVEDNUUSJAV-UHFFFAOYSA-N anthracene Chemical compound C1=CC=CC2=CC3=CC=CC=C3C=C21 MWPLVEDNUUSJAV-UHFFFAOYSA-N 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- 150000004982 aromatic amines Chemical class 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- GQVWHWAWLPCBHB-UHFFFAOYSA-L beryllium;benzo[h]quinolin-10-olate Chemical compound [Be+2].C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21.C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21 GQVWHWAWLPCBHB-UHFFFAOYSA-L 0.000 description 2

- UFVXQDWNSAGPHN-UHFFFAOYSA-K bis[(2-methylquinolin-8-yl)oxy]-(4-phenylphenoxy)alumane Chemical compound [Al+3].C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC([O-])=CC=C1C1=CC=CC=C1 UFVXQDWNSAGPHN-UHFFFAOYSA-K 0.000 description 2

- 229910052797 bismuth Inorganic materials 0.000 description 2

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 2

- 239000000872 buffer Substances 0.000 description 2

- XZCJVWCMJYNSQO-UHFFFAOYSA-N butyl pbd Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=CC(=CC=2)C=2C=CC=CC=2)O1 XZCJVWCMJYNSQO-UHFFFAOYSA-N 0.000 description 2

- 229910052793 cadmium Inorganic materials 0.000 description 2

- LYQFWZFBNBDLEO-UHFFFAOYSA-M caesium bromide Chemical compound [Br-].[Cs+] LYQFWZFBNBDLEO-UHFFFAOYSA-M 0.000 description 2

- XQPRBTXUXXVTKB-UHFFFAOYSA-M caesium iodide Chemical compound [I-].[Cs+] XQPRBTXUXXVTKB-UHFFFAOYSA-M 0.000 description 2

- WUKWITHWXAAZEY-UHFFFAOYSA-L calcium difluoride Chemical compound [F-].[F-].[Ca+2] WUKWITHWXAAZEY-UHFFFAOYSA-L 0.000 description 2

- OSGAYBCDTDRGGQ-UHFFFAOYSA-L calcium sulfate Chemical compound [Ca+2].[O-]S([O-])(=O)=O OSGAYBCDTDRGGQ-UHFFFAOYSA-L 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- MVPPADPHJFYWMZ-UHFFFAOYSA-N chlorobenzene Chemical compound ClC1=CC=CC=C1 MVPPADPHJFYWMZ-UHFFFAOYSA-N 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 2

- VPUGDVKSAQVFFS-UHFFFAOYSA-N coronene Chemical compound C1=C(C2=C34)C=CC3=CC=C(C=C3)C4=C4C3=CC=C(C=C3)C4=C2C3=C1 VPUGDVKSAQVFFS-UHFFFAOYSA-N 0.000 description 2

- ZYGHJZDHTFUPRJ-UHFFFAOYSA-N coumarin Chemical compound C1=CC=C2OC(=O)C=CC2=C1 ZYGHJZDHTFUPRJ-UHFFFAOYSA-N 0.000 description 2

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 2

- 239000003814 drug Substances 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 125000005678 ethenylene group Chemical group [H]C([*:1])=C([H])[*:2] 0.000 description 2

- 238000010304 firing Methods 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- 238000005247 gettering Methods 0.000 description 2

- 238000007646 gravure printing Methods 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 230000006698 induction Effects 0.000 description 2

- 230000001939 inductive effect Effects 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- 239000003446 ligand Substances 0.000 description 2

- IIPYXGDZVMZOAP-UHFFFAOYSA-N lithium nitrate Chemical compound [Li+].[O-][N+]([O-])=O IIPYXGDZVMZOAP-UHFFFAOYSA-N 0.000 description 2

- YIXJRHPUWRPCBB-UHFFFAOYSA-N magnesium nitrate Chemical compound [Mg+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O YIXJRHPUWRPCBB-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 239000000696 magnetic material Substances 0.000 description 2

- 239000002923 metal particle Substances 0.000 description 2

- 239000013081 microcrystal Substances 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 238000010606 normalization Methods 0.000 description 2

- 229920003986 novolac Polymers 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229920000301 poly(3-hexylthiophene-2,5-diyl) polymer Polymers 0.000 description 2

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 2

- 229920001230 polyarylate Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- SCVFZCLFOSHCOH-UHFFFAOYSA-M potassium acetate Chemical compound [K+].CC([O-])=O SCVFZCLFOSHCOH-UHFFFAOYSA-M 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- YYMBJDOZVAITBP-UHFFFAOYSA-N rubrene Chemical compound C1=CC=CC=C1C(C1=C(C=2C=CC=CC=2)C2=CC=CC=C2C(C=2C=CC=CC=2)=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 YYMBJDOZVAITBP-UHFFFAOYSA-N 0.000 description 2

- ADZWSOLPGZMUMY-UHFFFAOYSA-M silver bromide Chemical compound [Ag]Br ADZWSOLPGZMUMY-UHFFFAOYSA-M 0.000 description 2

- REYHXKZHIMGNSE-UHFFFAOYSA-M silver monofluoride Chemical compound [F-].[Ag+] REYHXKZHIMGNSE-UHFFFAOYSA-M 0.000 description 2

- SQGYOTSLMSWVJD-UHFFFAOYSA-N silver(1+) nitrate Chemical compound [Ag+].[O-]N(=O)=O SQGYOTSLMSWVJD-UHFFFAOYSA-N 0.000 description 2

- 239000011780 sodium chloride Substances 0.000 description 2

- VWDWKYIASSYTQR-UHFFFAOYSA-N sodium nitrate Chemical compound [Na+].[O-][N+]([O-])=O VWDWKYIASSYTQR-UHFFFAOYSA-N 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- UBXAKNTVXQMEAG-UHFFFAOYSA-L strontium sulfate Chemical compound [Sr+2].[O-]S([O-])(=O)=O UBXAKNTVXQMEAG-UHFFFAOYSA-L 0.000 description 2

- IOWOAQVVLHHFTL-UHFFFAOYSA-N technetium(vii) oxide Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[O-2].[Tc+7].[Tc+7] IOWOAQVVLHHFTL-UHFFFAOYSA-N 0.000 description 2

- QDZRBIRIPNZRSG-UHFFFAOYSA-N titanium nitrate Chemical compound [O-][N+](=O)O[Ti](O[N+]([O-])=O)(O[N+]([O-])=O)O[N+]([O-])=O QDZRBIRIPNZRSG-UHFFFAOYSA-N 0.000 description 2

- 230000017105 transposition Effects 0.000 description 2

- TVIVIEFSHFOWTE-UHFFFAOYSA-K tri(quinolin-8-yloxy)alumane Chemical compound [Al+3].C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1.C1=CN=C2C([O-])=CC=CC2=C1 TVIVIEFSHFOWTE-UHFFFAOYSA-K 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 239000011592 zinc chloride Substances 0.000 description 2

- 235000005074 zinc chloride Nutrition 0.000 description 2

- GWDUZCIBPDVBJM-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzothiazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1 GWDUZCIBPDVBJM-UHFFFAOYSA-L 0.000 description 2

- QEPMORHSGFRDLW-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzoxazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1 QEPMORHSGFRDLW-UHFFFAOYSA-L 0.000 description 2

- OERNJTNJEZOPIA-UHFFFAOYSA-N zirconium nitrate Chemical compound [Zr+4].[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O OERNJTNJEZOPIA-UHFFFAOYSA-N 0.000 description 2

- 229910000859 α-Fe Inorganic materials 0.000 description 2

- BNGXYYYYKUGPPF-UHFFFAOYSA-M (3-methylphenyl)methyl-triphenylphosphanium;chloride Chemical compound [Cl-].CC1=CC=CC(C[P+](C=2C=CC=CC=2)(C=2C=CC=CC=2)C=2C=CC=CC=2)=C1 BNGXYYYYKUGPPF-UHFFFAOYSA-M 0.000 description 1

- DTZWGKCFKSJGPK-VOTSOKGWSA-N (e)-2-(2-methyl-6-(2-(1,1,7,7-tetramethyl-1,2,3,5,6,7-hexahydropyrido[3,2,1-ij]quinolin-9-yl)vinyl)-4h-pyran-4-ylidene)malononitrile Chemical compound O1C(C)=CC(=C(C#N)C#N)C=C1\C=C\C1=CC(C(CCN2CCC3(C)C)(C)C)=C2C3=C1 DTZWGKCFKSJGPK-VOTSOKGWSA-N 0.000 description 1

- ZXSQEZNORDWBGZ-UHFFFAOYSA-N 1,3-dihydropyrrolo[2,3-b]pyridin-2-one Chemical compound C1=CN=C2NC(=O)CC2=C1 ZXSQEZNORDWBGZ-UHFFFAOYSA-N 0.000 description 1

- RYHBNJHYFVUHQT-UHFFFAOYSA-N 1,4-Dioxane Chemical compound C1COCCO1 RYHBNJHYFVUHQT-UHFFFAOYSA-N 0.000 description 1

- OCJBOOLMMGQPQU-UHFFFAOYSA-N 1,4-dichlorobenzene Chemical compound ClC1=CC=C(Cl)C=C1 OCJBOOLMMGQPQU-UHFFFAOYSA-N 0.000 description 1

- IVYAYAWSXINSEF-UHFFFAOYSA-N 1-tert-butylperylene Chemical group C1=CC(C=2C(C(C)(C)C)=CC=C3C=2C2=CC=C3)=C3C2=CC=CC3=C1 IVYAYAWSXINSEF-UHFFFAOYSA-N 0.000 description 1

- UVAMFBJPMUMURT-UHFFFAOYSA-N 2,3,4,5,6-pentafluorobenzenethiol Chemical compound FC1=C(F)C(F)=C(S)C(F)=C1F UVAMFBJPMUMURT-UHFFFAOYSA-N 0.000 description 1

- BFTIPCRZWILUIY-UHFFFAOYSA-N 2,5,8,11-tetratert-butylperylene Chemical group CC(C)(C)C1=CC(C2=CC(C(C)(C)C)=CC=3C2=C2C=C(C=3)C(C)(C)C)=C3C2=CC(C(C)(C)C)=CC3=C1 BFTIPCRZWILUIY-UHFFFAOYSA-N 0.000 description 1

- MUNFOTHAFHGRIM-UHFFFAOYSA-N 2,5-dinaphthalen-1-yl-1,3,4-oxadiazole Chemical compound C1=CC=C2C(C3=NN=C(O3)C=3C4=CC=CC=C4C=CC=3)=CC=CC2=C1 MUNFOTHAFHGRIM-UHFFFAOYSA-N 0.000 description 1

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 1

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 1

- JKFYKCYQEWQPTM-UHFFFAOYSA-N 2-azaniumyl-2-(4-fluorophenyl)acetate Chemical compound OC(=O)C(N)C1=CC=C(F)C=C1 JKFYKCYQEWQPTM-UHFFFAOYSA-N 0.000 description 1

- POAOYUHQDCAZBD-UHFFFAOYSA-N 2-butoxyethanol Chemical compound CCCCOCCO POAOYUHQDCAZBD-UHFFFAOYSA-N 0.000 description 1

- LNILPZLJSRHNPD-UHFFFAOYSA-N 3,4-dicyclohexylthiophene Chemical compound C1CCCCC1C1=CSC=C1C1CCCCC1 LNILPZLJSRHNPD-UHFFFAOYSA-N 0.000 description 1

- YEWTUGLUENRXFN-UHFFFAOYSA-N 3-(4-octylphenyl)-2-thiophen-2-ylthiophene Chemical compound C1=CC(CCCCCCCC)=CC=C1C1=C(C=2SC=CC=2)SC=C1 YEWTUGLUENRXFN-UHFFFAOYSA-N 0.000 description 1

- CHMILGIDWWDNMF-UHFFFAOYSA-N 3-(4-octylphenyl)thiophene Chemical compound C1=CC(CCCCCCCC)=CC=C1C1=CSC=C1 CHMILGIDWWDNMF-UHFFFAOYSA-N 0.000 description 1

- OGGKVJMNFFSDEV-UHFFFAOYSA-N 3-methyl-n-[4-[4-(n-(3-methylphenyl)anilino)phenyl]phenyl]-n-phenylaniline Chemical group CC1=CC=CC(N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)=C1 OGGKVJMNFFSDEV-UHFFFAOYSA-N 0.000 description 1

- HXWWMGJBPGRWRS-CMDGGOBGSA-N 4- -2-tert-butyl-6- -4h-pyran Chemical compound O1C(C(C)(C)C)=CC(=C(C#N)C#N)C=C1\C=C\C1=CC(C(CCN2CCC3(C)C)(C)C)=C2C3=C1 HXWWMGJBPGRWRS-CMDGGOBGSA-N 0.000 description 1

- SCZWJXTUYYSKGF-UHFFFAOYSA-N 5,12-dimethylquinolino[2,3-b]acridine-7,14-dione Chemical compound CN1C2=CC=CC=C2C(=O)C2=C1C=C1C(=O)C3=CC=CC=C3N(C)C1=C2 SCZWJXTUYYSKGF-UHFFFAOYSA-N 0.000 description 1

- AIXZBGVLNVRQSS-UHFFFAOYSA-N 5-tert-butyl-2-[5-(5-tert-butyl-1,3-benzoxazol-2-yl)thiophen-2-yl]-1,3-benzoxazole Chemical compound CC(C)(C)C1=CC=C2OC(C3=CC=C(S3)C=3OC4=CC=C(C=C4N=3)C(C)(C)C)=NC2=C1 AIXZBGVLNVRQSS-UHFFFAOYSA-N 0.000 description 1

- VIZUPBYFLORCRA-UHFFFAOYSA-N 9,10-dinaphthalen-2-ylanthracene Chemical compound C12=CC=CC=C2C(C2=CC3=CC=CC=C3C=C2)=C(C=CC=C2)C2=C1C1=CC=C(C=CC=C2)C2=C1 VIZUPBYFLORCRA-UHFFFAOYSA-N 0.000 description 1

- SXGIRTCIFPJUEQ-UHFFFAOYSA-N 9-anthracen-9-ylanthracene Chemical group C1=CC=CC2=CC3=CC=CC=C3C(C=3C4=CC=CC=C4C=C4C=CC=CC4=3)=C21 SXGIRTCIFPJUEQ-UHFFFAOYSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 101710134784 Agnoprotein Proteins 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- KLZUFWVZNOTSEM-UHFFFAOYSA-K Aluminium flouride Chemical compound F[Al](F)F KLZUFWVZNOTSEM-UHFFFAOYSA-K 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- 229910018575 Al—Ti Inorganic materials 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- JRLALOMYZVOMRI-UHFFFAOYSA-N BPPC Chemical compound BPPC JRLALOMYZVOMRI-UHFFFAOYSA-N 0.000 description 1

- 229910016036 BaF 2 Inorganic materials 0.000 description 1

- GOFLEYUWXFJWHT-UHFFFAOYSA-N Bc1cccc2cc3ccccc3cc12 Chemical compound Bc1cccc2cc3ccccc3cc12 GOFLEYUWXFJWHT-UHFFFAOYSA-N 0.000 description 1

- LTPBRCUWZOMYOC-UHFFFAOYSA-N Beryllium oxide Chemical compound O=[Be] LTPBRCUWZOMYOC-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- MSDMPJCOOXURQD-UHFFFAOYSA-N C545T Chemical compound C1=CC=C2SC(C3=CC=4C=C5C6=C(C=4OC3=O)C(C)(C)CCN6CCC5(C)C)=NC2=C1 MSDMPJCOOXURQD-UHFFFAOYSA-N 0.000 description 1

- 229910004261 CaF 2 Inorganic materials 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- UXVMQQNJUSDDNG-UHFFFAOYSA-L Calcium chloride Chemical compound [Cl-].[Cl-].[Ca+2] UXVMQQNJUSDDNG-UHFFFAOYSA-L 0.000 description 1

- UNMYWSMUMWPJLR-UHFFFAOYSA-L Calcium iodide Chemical compound [Ca+2].[I-].[I-] UNMYWSMUMWPJLR-UHFFFAOYSA-L 0.000 description 1

- ODINCKMPIJJUCX-UHFFFAOYSA-N Calcium oxide Chemical compound [Ca]=O ODINCKMPIJJUCX-UHFFFAOYSA-N 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229940126062 Compound A Drugs 0.000 description 1

- XDTMQSROBMDMFD-UHFFFAOYSA-N Cyclohexane Chemical compound C1CCCCC1 XDTMQSROBMDMFD-UHFFFAOYSA-N 0.000 description 1

- 239000004641 Diallyl-phthalate Substances 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 1

- NLDMNSXOCDLTTB-UHFFFAOYSA-N Heterophylliin A Natural products O1C2COC(=O)C3=CC(O)=C(O)C(O)=C3C3=C(O)C(O)=C(O)C=C3C(=O)OC2C(OC(=O)C=2C=C(O)C(O)=C(O)C=2)C(O)C1OC(=O)C1=CC(O)=C(O)C(O)=C1 NLDMNSXOCDLTTB-UHFFFAOYSA-N 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 229910013553 LiNO Inorganic materials 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910021380 Manganese Chloride Inorganic materials 0.000 description 1

- GLFNIEUTAYBVOC-UHFFFAOYSA-L Manganese chloride Chemical compound Cl[Mn]Cl GLFNIEUTAYBVOC-UHFFFAOYSA-L 0.000 description 1

- CERQOIWHTDAKMF-UHFFFAOYSA-N Methacrylic acid Chemical compound CC(=C)C(O)=O CERQOIWHTDAKMF-UHFFFAOYSA-N 0.000 description 1

- 101100496858 Mus musculus Colec12 gene Proteins 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 241000080590 Niso Species 0.000 description 1

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 1

- XURCIPRUUASYLR-UHFFFAOYSA-N Omeprazole sulfide Chemical compound N=1C2=CC(OC)=CC=C2NC=1SCC1=NC=C(C)C(OC)=C1C XURCIPRUUASYLR-UHFFFAOYSA-N 0.000 description 1

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 1

- YNPNZTXNASCQKK-UHFFFAOYSA-N Phenanthrene Natural products C1=CC=C2C3=CC=CC=C3C=CC2=C1 YNPNZTXNASCQKK-UHFFFAOYSA-N 0.000 description 1

- 239000004693 Polybenzimidazole Substances 0.000 description 1

- 239000004697 Polyetherimide Substances 0.000 description 1

- 239000004721 Polyphenylene oxide Substances 0.000 description 1

- 239000004734 Polyphenylene sulfide Substances 0.000 description 1

- 239000004954 Polyphthalamide Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910018503 SF6 Inorganic materials 0.000 description 1

- 229910000676 Si alloy Inorganic materials 0.000 description 1

- 229910003691 SiBr Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 229910001128 Sn alloy Inorganic materials 0.000 description 1

- PMZURENOXWZQFD-UHFFFAOYSA-L Sodium Sulfate Chemical compound [Na+].[Na+].[O-]S([O-])(=O)=O PMZURENOXWZQFD-UHFFFAOYSA-L 0.000 description 1

- PPBRXRYQALVLMV-UHFFFAOYSA-N Styrene Chemical compound C=CC1=CC=CC=C1 PPBRXRYQALVLMV-UHFFFAOYSA-N 0.000 description 1

- UCKMPCXJQFINFW-UHFFFAOYSA-N Sulphide Chemical compound [S-2] UCKMPCXJQFINFW-UHFFFAOYSA-N 0.000 description 1

- WYURNTSHIVDZCO-UHFFFAOYSA-N Tetrahydrofuran Chemical compound C1CCOC1 WYURNTSHIVDZCO-UHFFFAOYSA-N 0.000 description 1

- 229910001069 Ti alloy Inorganic materials 0.000 description 1

- 229910010413 TiO 2 Inorganic materials 0.000 description 1

- FMRLDPWIRHBCCC-UHFFFAOYSA-L Zinc carbonate Chemical compound [Zn+2].[O-]C([O-])=O FMRLDPWIRHBCCC-UHFFFAOYSA-L 0.000 description 1

- DGEZNRSVGBDHLK-UHFFFAOYSA-N [1,10]phenanthroline Chemical compound C1=CN=C2C3=NC=CC=C3C=CC2=C1 DGEZNRSVGBDHLK-UHFFFAOYSA-N 0.000 description 1

- WLQXPAUZYVXSNE-UHFFFAOYSA-N [Ca].O[N+]([O-])=O Chemical compound [Ca].O[N+]([O-])=O WLQXPAUZYVXSNE-UHFFFAOYSA-N 0.000 description 1

- ZYQHAXROJBXMOB-UHFFFAOYSA-N [Cr].[In] Chemical compound [Cr].[In] ZYQHAXROJBXMOB-UHFFFAOYSA-N 0.000 description 1

- JHYLKGDXMUDNEO-UHFFFAOYSA-N [Mg].[In] Chemical compound [Mg].[In] JHYLKGDXMUDNEO-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 239000003905 agrochemical Substances 0.000 description 1

- 229920000109 alkoxy-substituted poly(p-phenylene vinylene) Polymers 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- DIZPMCHEQGEION-UHFFFAOYSA-H aluminium sulfate (anhydrous) Chemical compound [Al+3].[Al+3].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O DIZPMCHEQGEION-UHFFFAOYSA-H 0.000 description 1

- 229910000379 antimony sulfate Inorganic materials 0.000 description 1

- MVMLTMBYNXHXFI-UHFFFAOYSA-H antimony(3+);trisulfate Chemical compound [Sb+3].[Sb+3].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O MVMLTMBYNXHXFI-UHFFFAOYSA-H 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- ITHZDDVSAWDQPZ-UHFFFAOYSA-L barium acetate Chemical compound [Ba+2].CC([O-])=O.CC([O-])=O ITHZDDVSAWDQPZ-UHFFFAOYSA-L 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- NKQIMNKPSDEDMO-UHFFFAOYSA-L barium bromide Chemical compound [Br-].[Br-].[Ba+2] NKQIMNKPSDEDMO-UHFFFAOYSA-L 0.000 description 1

- AYJRCSIUFZENHW-UHFFFAOYSA-L barium carbonate Chemical compound [Ba+2].[O-]C([O-])=O AYJRCSIUFZENHW-UHFFFAOYSA-L 0.000 description 1

- WDIHJSXYQDMJHN-UHFFFAOYSA-L barium chloride Chemical compound [Cl-].[Cl-].[Ba+2] WDIHJSXYQDMJHN-UHFFFAOYSA-L 0.000 description 1

- 229910001626 barium chloride Inorganic materials 0.000 description 1

- OYLGJCQECKOTOL-UHFFFAOYSA-L barium fluoride Chemical compound [F-].[F-].[Ba+2] OYLGJCQECKOTOL-UHFFFAOYSA-L 0.000 description 1

- 229910001632 barium fluoride Inorganic materials 0.000 description 1

- SGUXGJPBTNFBAD-UHFFFAOYSA-L barium iodide Chemical compound [I-].[I-].[Ba+2] SGUXGJPBTNFBAD-UHFFFAOYSA-L 0.000 description 1

- IWOUKMZUPDVPGQ-UHFFFAOYSA-N barium nitrate Chemical compound [Ba+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O IWOUKMZUPDVPGQ-UHFFFAOYSA-N 0.000 description 1

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 1

- TZCXTZWJZNENPQ-UHFFFAOYSA-L barium sulfate Chemical compound [Ba+2].[O-]S([O-])(=O)=O TZCXTZWJZNENPQ-UHFFFAOYSA-L 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- WZJYKHNJTSNBHV-UHFFFAOYSA-N benzo[h]quinoline Chemical group C1=CN=C2C3=CC=CC=C3C=CC2=C1 WZJYKHNJTSNBHV-UHFFFAOYSA-N 0.000 description 1

- DAMJCWMGELCIMI-UHFFFAOYSA-N benzyl n-(2-oxopyrrolidin-3-yl)carbamate Chemical compound C=1C=CC=CC=1COC(=O)NC1CCNC1=O DAMJCWMGELCIMI-UHFFFAOYSA-N 0.000 description 1

- LWBPNIJBHRISSS-UHFFFAOYSA-L beryllium dichloride Chemical compound Cl[Be]Cl LWBPNIJBHRISSS-UHFFFAOYSA-L 0.000 description 1

- JZKFIPKXQBZXMW-UHFFFAOYSA-L beryllium difluoride Chemical compound F[Be]F JZKFIPKXQBZXMW-UHFFFAOYSA-L 0.000 description 1

- 235000013361 beverage Nutrition 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- QUDWYFHPNIMBFC-UHFFFAOYSA-N bis(prop-2-enyl) benzene-1,2-dicarboxylate Chemical compound C=CCOC(=O)C1=CC=CC=C1C(=O)OCC=C QUDWYFHPNIMBFC-UHFFFAOYSA-N 0.000 description 1

- 229910000416 bismuth oxide Inorganic materials 0.000 description 1

- 229910000380 bismuth sulfate Inorganic materials 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 150000001649 bromium compounds Chemical class 0.000 description 1

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- VSGNNIFQASZAOI-UHFFFAOYSA-L calcium acetate Chemical compound [Ca+2].CC([O-])=O.CC([O-])=O VSGNNIFQASZAOI-UHFFFAOYSA-L 0.000 description 1

- 239000001639 calcium acetate Substances 0.000 description 1

- 235000011092 calcium acetate Nutrition 0.000 description 1

- 229960005147 calcium acetate Drugs 0.000 description 1

- 229910000019 calcium carbonate Inorganic materials 0.000 description 1

- 229910001634 calcium fluoride Inorganic materials 0.000 description 1

- 229910001640 calcium iodide Inorganic materials 0.000 description 1

- 229940046413 calcium iodide Drugs 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 125000000609 carbazolyl group Chemical class C1(=CC=CC=2C3=CC=CC=C3NC12)* 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000007809 chemical reaction catalyst Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 150000001805 chlorine compounds Chemical class 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- UFMZWBIQTDUYBN-UHFFFAOYSA-N cobalt dinitrate Chemical compound [Co+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O UFMZWBIQTDUYBN-UHFFFAOYSA-N 0.000 description 1

- KTVIXTQDYHMGHF-UHFFFAOYSA-L cobalt(2+) sulfate Chemical compound [Co+2].[O-]S([O-])(=O)=O KTVIXTQDYHMGHF-UHFFFAOYSA-L 0.000 description 1

- ZOTKGJBKKKVBJZ-UHFFFAOYSA-L cobalt(2+);carbonate Chemical compound [Co+2].[O-]C([O-])=O ZOTKGJBKKKVBJZ-UHFFFAOYSA-L 0.000 description 1

- OOMOMODKLPLOKW-UHFFFAOYSA-H cobalt(3+);trisulfate Chemical compound [Co+3].[Co+3].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O OOMOMODKLPLOKW-UHFFFAOYSA-H 0.000 description 1

- IVMYJDGYRUAWML-UHFFFAOYSA-N cobalt(ii) oxide Chemical compound [Co]=O IVMYJDGYRUAWML-UHFFFAOYSA-N 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 229910000365 copper sulfate Inorganic materials 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- OXBLHERUFWYNTN-UHFFFAOYSA-M copper(I) chloride Chemical compound [Cu]Cl OXBLHERUFWYNTN-UHFFFAOYSA-M 0.000 description 1

- XTVVROIMIGLXTD-UHFFFAOYSA-N copper(II) nitrate Chemical compound [Cu+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O XTVVROIMIGLXTD-UHFFFAOYSA-N 0.000 description 1

- ARUVKPQLZAKDPS-UHFFFAOYSA-L copper(II) sulfate Chemical compound [Cu+2].[O-][S+2]([O-])([O-])[O-] ARUVKPQLZAKDPS-UHFFFAOYSA-L 0.000 description 1

- GEZOTWYUIKXWOA-UHFFFAOYSA-L copper;carbonate Chemical compound [Cu+2].[O-]C([O-])=O GEZOTWYUIKXWOA-UHFFFAOYSA-L 0.000 description 1

- 229960000956 coumarin Drugs 0.000 description 1

- 235000001671 coumarin Nutrition 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000012217 deletion Methods 0.000 description 1

- 230000037430 deletion Effects 0.000 description 1

- 239000000412 dendrimer Substances 0.000 description 1

- 229920000736 dendritic polymer Polymers 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 150000004985 diamines Chemical class 0.000 description 1

- TYIXMATWDRGMPF-UHFFFAOYSA-N dibismuth;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Bi+3].[Bi+3] TYIXMATWDRGMPF-UHFFFAOYSA-N 0.000 description 1

- BEQZMQXCOWIHRY-UHFFFAOYSA-H dibismuth;trisulfate Chemical compound [Bi+3].[Bi+3].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O BEQZMQXCOWIHRY-UHFFFAOYSA-H 0.000 description 1

- JNTDLFKBNBKNRI-UHFFFAOYSA-L dichloroantimony Chemical compound Cl[Sb]Cl JNTDLFKBNBKNRI-UHFFFAOYSA-L 0.000 description 1

- 229940117389 dichlorobenzene Drugs 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- BKMIWBZIQAAZBD-UHFFFAOYSA-N diindenoperylene Chemical compound C12=C3C4=CC=C2C2=CC=CC=C2C1=CC=C3C1=CC=C2C3=CC=CC=C3C3=CC=C4C1=C32 BKMIWBZIQAAZBD-UHFFFAOYSA-N 0.000 description 1

- XUCJHNOBJLKZNU-UHFFFAOYSA-M dilithium;hydroxide Chemical compound [Li+].[Li+].[OH-] XUCJHNOBJLKZNU-UHFFFAOYSA-M 0.000 description 1

- FZFYOUJTOSBFPQ-UHFFFAOYSA-M dipotassium;hydroxide Chemical compound [OH-].[K+].[K+] FZFYOUJTOSBFPQ-UHFFFAOYSA-M 0.000 description 1

- 239000002270 dispersing agent Substances 0.000 description 1

- 235000012489 doughnuts Nutrition 0.000 description 1

- 229940079593 drug Drugs 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005672 electromagnetic field Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000001017 electron-beam sputter deposition Methods 0.000 description 1

- RAQDACVRFCEPDA-UHFFFAOYSA-L ferrous carbonate Chemical compound [Fe+2].[O-]C([O-])=O RAQDACVRFCEPDA-UHFFFAOYSA-L 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 239000007849 furan resin Substances 0.000 description 1

- 229910000078 germane Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- QBHWPVJPWQGYDS-UHFFFAOYSA-N hexaphenylbenzene Chemical compound C1=CC=CC=C1C(C(=C(C=1C=CC=CC=1)C(C=1C=CC=CC=1)=C1C=2C=CC=CC=2)C=2C=CC=CC=2)=C1C1=CC=CC=C1 QBHWPVJPWQGYDS-UHFFFAOYSA-N 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 229920001519 homopolymer Polymers 0.000 description 1

- IXCSERBJSXMMFS-UHFFFAOYSA-N hydrogen chloride Substances Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 1

- 229910000041 hydrogen chloride Inorganic materials 0.000 description 1

- XMBWDFGMSWQBCA-UHFFFAOYSA-N hydrogen iodide Chemical compound I XMBWDFGMSWQBCA-UHFFFAOYSA-N 0.000 description 1

- RXPAJWPEYBDXOG-UHFFFAOYSA-N hydron;methyl 4-methoxypyridine-2-carboxylate;chloride Chemical compound Cl.COC(=O)C1=CC(OC)=CC=N1 RXPAJWPEYBDXOG-UHFFFAOYSA-N 0.000 description 1

- BDAGIHXWWSANSR-NJFSPNSNSA-N hydroxyformaldehyde Chemical compound O[14CH]=O BDAGIHXWWSANSR-NJFSPNSNSA-N 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- RPQDHPTXJYYUPQ-UHFFFAOYSA-N indium arsenide Chemical compound [In]#[As] RPQDHPTXJYYUPQ-UHFFFAOYSA-N 0.000 description 1

- RHZWSUVWRRXEJF-UHFFFAOYSA-N indium tin Chemical compound [In].[Sn] RHZWSUVWRRXEJF-UHFFFAOYSA-N 0.000 description 1

- 229910000337 indium(III) sulfate Inorganic materials 0.000 description 1

- XGCKLPDYTQRDTR-UHFFFAOYSA-H indium(iii) sulfate Chemical compound [In+3].[In+3].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O XGCKLPDYTQRDTR-UHFFFAOYSA-H 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- RBTARNINKXHZNM-UHFFFAOYSA-K iron trichloride Chemical compound Cl[Fe](Cl)Cl RBTARNINKXHZNM-UHFFFAOYSA-K 0.000 description 1

- BAUYGSIQEAFULO-UHFFFAOYSA-L iron(2+) sulfate (anhydrous) Chemical compound [Fe+2].[O-]S([O-])(=O)=O BAUYGSIQEAFULO-UHFFFAOYSA-L 0.000 description 1

- MVFCKEFYUDZOCX-UHFFFAOYSA-N iron(2+);dinitrate Chemical compound [Fe+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O MVFCKEFYUDZOCX-UHFFFAOYSA-N 0.000 description 1

- VCJMYUPGQJHHFU-UHFFFAOYSA-N iron(3+);trinitrate Chemical compound [Fe+3].[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O VCJMYUPGQJHHFU-UHFFFAOYSA-N 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- AMXOYNBUYSYVKV-UHFFFAOYSA-M lithium bromide Chemical compound [Li+].[Br-] AMXOYNBUYSYVKV-UHFFFAOYSA-M 0.000 description 1

- XGZVUEUWXADBQD-UHFFFAOYSA-L lithium carbonate Chemical compound [Li+].[Li+].[O-]C([O-])=O XGZVUEUWXADBQD-UHFFFAOYSA-L 0.000 description 1

- KWGKDLIKAYFUFQ-UHFFFAOYSA-M lithium chloride Chemical compound [Li+].[Cl-] KWGKDLIKAYFUFQ-UHFFFAOYSA-M 0.000 description 1

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 1

- INHCSSUBVCNVSK-UHFFFAOYSA-L lithium sulfate Inorganic materials [Li+].[Li+].[O-]S([O-])(=O)=O INHCSSUBVCNVSK-UHFFFAOYSA-L 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- UEGPKNKPLBYCNK-UHFFFAOYSA-L magnesium acetate Chemical compound [Mg+2].CC([O-])=O.CC([O-])=O UEGPKNKPLBYCNK-UHFFFAOYSA-L 0.000 description 1

- 239000011654 magnesium acetate Substances 0.000 description 1

- 235000011285 magnesium acetate Nutrition 0.000 description 1

- 229940069446 magnesium acetate Drugs 0.000 description 1

- ZLNQQNXFFQJAID-UHFFFAOYSA-L magnesium carbonate Chemical compound [Mg+2].[O-]C([O-])=O ZLNQQNXFFQJAID-UHFFFAOYSA-L 0.000 description 1

- ORUIBWPALBXDOA-UHFFFAOYSA-L magnesium fluoride Chemical compound [F-].[F-].[Mg+2] ORUIBWPALBXDOA-UHFFFAOYSA-L 0.000 description 1

- 229910052943 magnesium sulfate Inorganic materials 0.000 description 1

- 235000019341 magnesium sulphate Nutrition 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 239000011565 manganese chloride Substances 0.000 description 1

- 235000002867 manganese chloride Nutrition 0.000 description 1

- 229940099607 manganese chloride Drugs 0.000 description 1

- MIVBAHRSNUNMPP-UHFFFAOYSA-N manganese(2+);dinitrate Chemical compound [Mn+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O MIVBAHRSNUNMPP-UHFFFAOYSA-N 0.000 description 1

- SQQMAOCOWKFBNP-UHFFFAOYSA-L manganese(II) sulfate Chemical compound [Mn+2].[O-]S([O-])(=O)=O SQQMAOCOWKFBNP-UHFFFAOYSA-L 0.000 description 1

- XMWCXZJXESXBBY-UHFFFAOYSA-L manganese(ii) carbonate Chemical compound [Mn+2].[O-]C([O-])=O XMWCXZJXESXBBY-UHFFFAOYSA-L 0.000 description 1

- SRVINXWCFNHIQZ-UHFFFAOYSA-K manganese(iii) fluoride Chemical compound [F-].[F-].[F-].[Mn+3] SRVINXWCFNHIQZ-UHFFFAOYSA-K 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- UZKWTJUDCOPSNM-UHFFFAOYSA-N methoxybenzene Substances CCCCOC=C UZKWTJUDCOPSNM-UHFFFAOYSA-N 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- WQGTYCVOVMYEQV-UHFFFAOYSA-N n-(3-methylphenyl)-n,2-diphenylaniline Chemical group CC1=CC=CC(N(C=2C=CC=CC=2)C=2C(=CC=CC=2)C=2C=CC=CC=2)=C1 WQGTYCVOVMYEQV-UHFFFAOYSA-N 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- LGQLOGILCSXPEA-UHFFFAOYSA-L nickel sulfate Chemical compound [Ni+2].[O-]S([O-])(=O)=O LGQLOGILCSXPEA-UHFFFAOYSA-L 0.000 description 1

- 229910000363 nickel(II) sulfate Inorganic materials 0.000 description 1

- KBJMLQFLOWQJNF-UHFFFAOYSA-N nickel(ii) nitrate Chemical compound [Ni+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O KBJMLQFLOWQJNF-UHFFFAOYSA-N 0.000 description 1

- 150000002823 nitrates Chemical class 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- HBEQXAKJSGXAIQ-UHFFFAOYSA-N oxopalladium Chemical compound [Pd]=O HBEQXAKJSGXAIQ-UHFFFAOYSA-N 0.000 description 1

- UFQXGXDIJMBKTC-UHFFFAOYSA-N oxostrontium Chemical compound [Sr]=O UFQXGXDIJMBKTC-UHFFFAOYSA-N 0.000 description 1

- JMOHEPRYPIIZQU-UHFFFAOYSA-N oxygen(2-);tantalum(2+) Chemical compound [O-2].[Ta+2] JMOHEPRYPIIZQU-UHFFFAOYSA-N 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- PIBWKRNGBLPSSY-UHFFFAOYSA-L palladium(II) chloride Chemical compound Cl[Pd]Cl PIBWKRNGBLPSSY-UHFFFAOYSA-L 0.000 description 1

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 1

- 125000002080 perylenyl group Chemical group C1(=CC=C2C=CC=C3C4=CC=CC5=CC=CC(C1=C23)=C45)* 0.000 description 1

- CSHWQDPOILHKBI-UHFFFAOYSA-N peryrene Natural products C1=CC(C2=CC=CC=3C2=C2C=CC=3)=C3C2=CC=CC3=C1 CSHWQDPOILHKBI-UHFFFAOYSA-N 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 229920000052 poly(p-xylylene) Polymers 0.000 description 1

- 229920002492 poly(sulfone) Polymers 0.000 description 1

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000412 polyarylene Polymers 0.000 description 1

- 229920002480 polybenzimidazole Polymers 0.000 description 1

- 229920001601 polyetherimide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920002495 polyphenylene ethynylene polymer Polymers 0.000 description 1

- 229920006380 polyphenylene oxide Polymers 0.000 description 1

- 229920000069 polyphenylene sulfide Polymers 0.000 description 1

- 229920006375 polyphtalamide Polymers 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- 235000011056 potassium acetate Nutrition 0.000 description 1

- BWHMMNNQKKPAPP-UHFFFAOYSA-L potassium carbonate Chemical compound [K+].[K+].[O-]C([O-])=O BWHMMNNQKKPAPP-UHFFFAOYSA-L 0.000 description 1

- 239000001103 potassium chloride Substances 0.000 description 1

- 235000011164 potassium chloride Nutrition 0.000 description 1

- NROKBHXJSPEDAR-UHFFFAOYSA-M potassium fluoride Chemical compound [F-].[K+] NROKBHXJSPEDAR-UHFFFAOYSA-M 0.000 description 1

- FGIUAXJPYTZDNR-UHFFFAOYSA-N potassium nitrate Chemical compound [K+].[O-][N+]([O-])=O FGIUAXJPYTZDNR-UHFFFAOYSA-N 0.000 description 1

- OTYBMLCTZGSZBG-UHFFFAOYSA-L potassium sulfate Chemical compound [K+].[K+].[O-]S([O-])(=O)=O OTYBMLCTZGSZBG-UHFFFAOYSA-L 0.000 description 1

- 229910052939 potassium sulfate Inorganic materials 0.000 description 1

- 235000011151 potassium sulphates Nutrition 0.000 description 1

- 125000002943 quinolinyl group Chemical group N1=C(C=CC2=CC=CC=C12)* 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 238000005096 rolling process Methods 0.000 description 1

- AHLATJUETSFVIM-UHFFFAOYSA-M rubidium fluoride Chemical compound [F-].[Rb+] AHLATJUETSFVIM-UHFFFAOYSA-M 0.000 description 1

- CWBWCLMMHLCMAM-UHFFFAOYSA-M rubidium(1+);hydroxide Chemical compound [OH-].[Rb+].[Rb+] CWBWCLMMHLCMAM-UHFFFAOYSA-M 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- YBCAZPLXEGKKFM-UHFFFAOYSA-K ruthenium(iii) chloride Chemical compound [Cl-].[Cl-].[Cl-].[Ru+3] YBCAZPLXEGKKFM-UHFFFAOYSA-K 0.000 description 1

- 229910021481 rutherfordium Inorganic materials 0.000 description 1

- YGPLJIIQQIDVFJ-UHFFFAOYSA-N rutherfordium atom Chemical compound [Rf] YGPLJIIQQIDVFJ-UHFFFAOYSA-N 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- HYXGAEYDKFCVMU-UHFFFAOYSA-N scandium oxide Chemical compound O=[Sc]O[Sc]=O HYXGAEYDKFCVMU-UHFFFAOYSA-N 0.000 description 1

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- AIFMYMZGQVTROK-UHFFFAOYSA-N silicon tetrabromide Chemical compound Br[Si](Br)(Br)Br AIFMYMZGQVTROK-UHFFFAOYSA-N 0.000 description 1

- FDNAPBUWERUEDA-UHFFFAOYSA-N silicon tetrachloride Chemical compound Cl[Si](Cl)(Cl)Cl FDNAPBUWERUEDA-UHFFFAOYSA-N 0.000 description 1

- JHGCXUUFRJCMON-UHFFFAOYSA-J silicon(4+);tetraiodide Chemical compound [Si+4].[I-].[I-].[I-].[I-] JHGCXUUFRJCMON-UHFFFAOYSA-J 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- LKZMBDSASOBTPN-UHFFFAOYSA-L silver carbonate Substances [Ag].[O-]C([O-])=O LKZMBDSASOBTPN-UHFFFAOYSA-L 0.000 description 1

- 229910001958 silver carbonate Inorganic materials 0.000 description 1

- 229940096017 silver fluoride Drugs 0.000 description 1

- 229940045105 silver iodide Drugs 0.000 description 1

- HKZLPVFGJNLROG-UHFFFAOYSA-M silver monochloride Chemical compound [Cl-].[Ag+] HKZLPVFGJNLROG-UHFFFAOYSA-M 0.000 description 1

- 229910001961 silver nitrate Inorganic materials 0.000 description 1

- YPNVIBVEFVRZPJ-UHFFFAOYSA-L silver sulfate Chemical compound [Ag+].[Ag+].[O-]S([O-])(=O)=O YPNVIBVEFVRZPJ-UHFFFAOYSA-L 0.000 description 1

- VFWRGKJLLYDFBY-UHFFFAOYSA-N silver;hydrate Chemical compound O.[Ag].[Ag] VFWRGKJLLYDFBY-UHFFFAOYSA-N 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 229910000029 sodium carbonate Inorganic materials 0.000 description 1

- PUZPDOWCWNUUKD-UHFFFAOYSA-M sodium fluoride Chemical compound [F-].[Na+] PUZPDOWCWNUUKD-UHFFFAOYSA-M 0.000 description 1

- FVAUCKIRQBBSSJ-UHFFFAOYSA-M sodium iodide Chemical compound [Na+].[I-] FVAUCKIRQBBSSJ-UHFFFAOYSA-M 0.000 description 1

- 239000004317 sodium nitrate Substances 0.000 description 1

- 235000010344 sodium nitrate Nutrition 0.000 description 1

- KKCBUQHMOMHUOY-UHFFFAOYSA-N sodium oxide Chemical compound [O-2].[Na+].[Na+] KKCBUQHMOMHUOY-UHFFFAOYSA-N 0.000 description 1

- 229910052938 sodium sulfate Inorganic materials 0.000 description 1

- 235000011152 sodium sulphate Nutrition 0.000 description 1

- 238000003980 solgel method Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000011425 standardization method Methods 0.000 description 1

- 229910000018 strontium carbonate Inorganic materials 0.000 description 1

- AHBGXTDRMVNFER-UHFFFAOYSA-L strontium dichloride Chemical compound [Cl-].[Cl-].[Sr+2] AHBGXTDRMVNFER-UHFFFAOYSA-L 0.000 description 1

- FVRNDBHWWSPNOM-UHFFFAOYSA-L strontium fluoride Chemical compound [F-].[F-].[Sr+2] FVRNDBHWWSPNOM-UHFFFAOYSA-L 0.000 description 1

- 229910001637 strontium fluoride Inorganic materials 0.000 description 1

- DHEQXMRUPNDRPG-UHFFFAOYSA-N strontium nitrate Chemical compound [Sr+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O DHEQXMRUPNDRPG-UHFFFAOYSA-N 0.000 description 1

- RXSHXLOMRZJCLB-UHFFFAOYSA-L strontium;diacetate Chemical compound [Sr+2].CC([O-])=O.CC([O-])=O RXSHXLOMRZJCLB-UHFFFAOYSA-L 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- 150000003467 sulfuric acid derivatives Chemical class 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 1

- RBTVSNLYYIMMKS-UHFFFAOYSA-N tert-butyl 3-aminoazetidine-1-carboxylate;hydrochloride Chemical compound Cl.CC(C)(C)OC(=O)N1CC(N)C1 RBTVSNLYYIMMKS-UHFFFAOYSA-N 0.000 description 1

- IEXRMSFAVATTJX-UHFFFAOYSA-N tetrachlorogermane Chemical compound Cl[Ge](Cl)(Cl)Cl IEXRMSFAVATTJX-UHFFFAOYSA-N 0.000 description 1

- 229910052716 thallium Inorganic materials 0.000 description 1

- BKVIYDNLLOSFOA-UHFFFAOYSA-N thallium Chemical compound [Tl] BKVIYDNLLOSFOA-UHFFFAOYSA-N 0.000 description 1

- GBECUEIQVRDUKB-UHFFFAOYSA-M thallium monochloride Chemical compound [Tl]Cl GBECUEIQVRDUKB-UHFFFAOYSA-M 0.000 description 1

- CMJCEVKJYRZMIA-UHFFFAOYSA-M thallium(i) iodide Chemical compound [Tl]I CMJCEVKJYRZMIA-UHFFFAOYSA-M 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 229920002803 thermoplastic polyurethane Polymers 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- OBBXFSIWZVFYJR-UHFFFAOYSA-L tin(2+);sulfate Chemical compound [Sn+2].[O-]S([O-])(=O)=O OBBXFSIWZVFYJR-UHFFFAOYSA-L 0.000 description 1

- FAKFSJNVVCGEEI-UHFFFAOYSA-J tin(4+);disulfate Chemical compound [Sn+4].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O FAKFSJNVVCGEEI-UHFFFAOYSA-J 0.000 description 1

- HPGGPRDJHPYFRM-UHFFFAOYSA-J tin(iv) chloride Chemical compound Cl[Sn](Cl)(Cl)Cl HPGGPRDJHPYFRM-UHFFFAOYSA-J 0.000 description 1

- XJDNKRIXUMDJCW-UHFFFAOYSA-J titanium tetrachloride Chemical compound Cl[Ti](Cl)(Cl)Cl XJDNKRIXUMDJCW-UHFFFAOYSA-J 0.000 description 1

- NLLZTRMHNHVXJJ-UHFFFAOYSA-J titanium tetraiodide Chemical compound I[Ti](I)(I)I NLLZTRMHNHVXJJ-UHFFFAOYSA-J 0.000 description 1

- SOBXOQKKUVQETK-UHFFFAOYSA-H titanium(3+);trisulfate Chemical compound [Ti+3].[Ti+3].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O SOBXOQKKUVQETK-UHFFFAOYSA-H 0.000 description 1

- YONPGGFAJWQGJC-UHFFFAOYSA-K titanium(iii) chloride Chemical compound Cl[Ti](Cl)Cl YONPGGFAJWQGJC-UHFFFAOYSA-K 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- YQMWDQQWGKVOSQ-UHFFFAOYSA-N trinitrooxystannyl nitrate Chemical compound [Sn+4].[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O.[O-][N+]([O-])=O YQMWDQQWGKVOSQ-UHFFFAOYSA-N 0.000 description 1

- AAAQKTZKLRYKHR-UHFFFAOYSA-N triphenylmethane Chemical compound C1=CC=CC=C1C(C=1C=CC=CC=1)C1=CC=CC=C1 AAAQKTZKLRYKHR-UHFFFAOYSA-N 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

- 235000012431 wafers Nutrition 0.000 description 1

- 230000003313 weakening effect Effects 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 239000008096 xylene Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011667 zinc carbonate Substances 0.000 description 1

- 235000004416 zinc carbonate Nutrition 0.000 description 1

- 229910000010 zinc carbonate Inorganic materials 0.000 description 1

- ONDPHDOFVYQSGI-UHFFFAOYSA-N zinc nitrate Chemical compound [Zn+2].[O-][N+]([O-])=O.[O-][N+]([O-])=O ONDPHDOFVYQSGI-UHFFFAOYSA-N 0.000 description 1

- NWONKYPBYAMBJT-UHFFFAOYSA-L zinc sulfate Chemical compound [Zn+2].[O-]S([O-])(=O)=O NWONKYPBYAMBJT-UHFFFAOYSA-L 0.000 description 1

- 229910000368 zinc sulfate Inorganic materials 0.000 description 1

- 229960001763 zinc sulfate Drugs 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

- DUNKXUFBGCUVQW-UHFFFAOYSA-J zirconium tetrachloride Chemical compound Cl[Zr](Cl)(Cl)Cl DUNKXUFBGCUVQW-UHFFFAOYSA-J 0.000 description 1

- ZXAUZSQITFJWPS-UHFFFAOYSA-J zirconium(4+);disulfate Chemical compound [Zr+4].[O-]S([O-])(=O)=O.[O-]S([O-])(=O)=O ZXAUZSQITFJWPS-UHFFFAOYSA-J 0.000 description 1

Images

Landscapes

- Semiconductor Memories (AREA)

Abstract

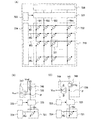

【解決手段】記憶素子の形状として周辺に凹凸部を有するような矩形、単数または複数の屈曲部を有するジグザグ形状、櫛形、内部に開口(空間)を有するような輪状などの形状を用いる。また、短辺の長さに対する長辺の長さの比が大きい長方形、短径に対する長径の比が大きい楕円形なども用いることができる。

【選択図】図1

Description

本実施の形態では、本発明を適用した記憶素子を、図1を用いて説明する。

本実施の形態では、本発明の半導体装置が有する記憶素子の一構成例に関して図面を用いて説明する。より具体的には、半導体装置の構成がパッシブマトリクス型の場合に関して示す。

本実施の形態では、上記実施の形態2とは異なる構成を有する半導体装置について説明する。具体的には、半導体装置の構成がアクティブマトリクス型の場合に関して示す。本実施の形態における記憶素子は実施の形態1と同様の材料、構成で作製することができる。よって材料等詳しい説明は省略する。

本実施の形態では、上記実施の形態で示す半導体装置の一例に関して図面を用いて説明する。

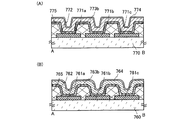

本実施の形態では、上記実施の形態で示す記憶素子を有する半導体装置の一例に関して図面を用いて説明する。本実施の形態の半導体装置の上面図を図14(A)に、図14(A)における線X−Yの断面図を図14(B)に示す。

本実施の形態では、上記構成を有する半導体装置において、データの読み込みまたは書き込みについて説明する。

本実施形態の半導体装置の構成について、図12を参照して説明する。図12に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調又は変調回路13、他の回路を制御する制御回路14、インターフェイス回路15、記憶回路16、データバス17、アンテナ(アンテナコイル)18、センサ21、センサ回路22を有する。

本発明によりプロセッサ回路を有するチップ(以下、プロセッサチップ、無線チップ、無線プロセッサ、無線メモリ、無線タグともよぶ)として機能する半導体装置を形成することができる。本発明の半導体装置の用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。

Claims (21)

- 第1の導電層と第2の導電層との間に、有機化合物層を含む記憶素子を有し、

前記第1の導電層及び前記第2の導電層のうち少なくとも一方の上面形状は屈曲していることを特徴とする半導体装置。 - 第1の導電層と第2の導電層との間に、有機化合物層を含む記憶素子を有し、

前記第1の導電層及び前記第2の導電層のうち少なくとも一方の上面形状は櫛歯状であることを特徴とする半導体装置。 - 第1の導電層と第2の導電層との間に、有機化合物層を含む記憶素子を有し、

前記第1の導電層及び前記第2の導電層のうち少なくとも一方の上面形状は輪状であることを特徴とする半導体装置。 - 第1の導電層と第2の導電層との間に、有機化合物層を含む記憶素子を有し、

前記第1の導電層及び前記第2の導電層のうち少なくとも一方の上面形状は切り込みを有する矩形形状であることを特徴とする半導体装置。 - 第1の導電層と、前記第1の導電層上に開口を有する絶縁層と、前記第1の導電層上の前記開口に有機化合物層と、前記有機化合物層上に第2の導電層とを含む記憶素子を有し、

前記開口の上面形状は屈曲していることを特徴とする半導体装置。 - 第1の導電層と、前記第1の導電層上に開口を有する絶縁層と、前記第1の導電層上の前記開口に有機化合物層と、前記有機化合物層上に第2の導電層とを含む記憶素子を有し、

前記開口の上面形状は櫛歯状であることを特徴とする半導体装置。 - 第1の導電層と、前記第1の導電層上に開口を有する絶縁層と、前記第1の導電層上の前記開口に有機化合物層と、前記有機化合物層上に第2の導電層とを含む記憶素子を有し、

前記開口の上面形状は輪状であることを特徴とする半導体装置。 - 第1の導電層と、前記第1の導電層上に開口を有する絶縁層と、前記第1の導電層上の前記開口に有機化合物層と、前記有機化合物層上に第2の導電層とを含む記憶素子を有し、

前記開口の上面形状は切り込みを有する矩形形状であることを特徴とする半導体装置。 - 請求項1乃至8のいずれか一項において、前記記憶素子と同じ面積、かつ同じ周辺の長さの長方形の長辺と短辺との比は3以上であることを特徴とする半導体装置。

- 請求項1乃至8のいずれか一項において、前記記憶素子の面積と、前記記憶素子と同じ周辺の長さの正方形の面積との比は0.75以下であることを特徴とする半導体装置。

- 請求項1乃至10のいずれか一項において、前記第1の導電層と前記有機化合物層との間に絶縁層を有することを特徴とする半導体装置。

- 上面形状が屈曲している第1の導電層を形成し、

前記屈曲している第1の導電層上に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が屈曲している記憶素子を作製することを特徴とする半導体装置の作製方法。 - 上面形状が櫛歯状の第1の導電層を形成し、

前記櫛歯状の第1の導電層上に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が櫛歯状の記憶素子を作製することを特徴とする半導体装置の作製方法。 - 上面形状が輪状の第1の導電層を形成し、

前記輪状の第1の導電層上に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が輪状の記憶素子を作製することを特徴とする半導体装置の作製方法。 - 上面形状が切り込みを有する矩形形状の第1の導電層を形成し、

前記切り込みを有する矩形形状の第1の導電層上に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が切り込みを有する矩形形状の記憶素子を作製することを特徴とする半導体装置の作製方法。 - 第1の導電層を形成し、

前記第1の導電層上に上面形状が屈曲している開口を有する絶縁層を形成し、

前記第1の導電層上の前記屈曲している開口に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が屈曲している記憶素子を作製することを特徴とする半導体装置の作製方法。 - 第1の導電層を形成し、

前記第1の導電層上に上面形状が櫛歯状の開口を有する絶縁層を形成し、

前記第1の導電層上の櫛歯状の開口に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が櫛歯状の記憶素子を作製することを特徴とする半導体装置の作製方法。 - 第1の導電層を形成し、

前記第1の導電層上に上面形状が輪状の開口を有する絶縁層を形成し、

前記第1の導電層上の前記開口に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が輪状の記憶素子を作製することを特徴とする半導体装置の作製方法。 - 第1の導電層を形成し、

前記第1の導電層上に上面形状が切り込みを有する矩形形状の開口を有する絶縁層を形成し、

前記第1の導電層上の前記開口に有機化合物層を形成し、

前記有機化合物層上に第2の導電層を形成して上面形状が切り込みを有する矩形形状の記憶素子を作製することを特徴とする半導体装置の作製方法。 - 請求項12乃至19のいずれか一項において、前記記憶素子と同じ面積、かつ同じ周辺の長さの長方形の長辺と短辺との比が3以上である前記記憶素子を形成することを特徴とする半導体装置の作製方法。

- 請求項12乃至19のいずれか一項において、前記記憶素子の面積と、前記記憶素子と同じ周辺の長さの正方形の面積との比が0.75以下である前記記憶素子を形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)