本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

(実施の形態1)

本実施の形態では、本発明の記憶装置が有する記憶素子の一構成例に関して図面を用いて説明する。

本発明の記憶素子とその動作機構を、図1を用いて説明する。本発明では、記憶装置に含まれる記憶素子を構成する有機化合物層を挟んで形成される一対の導電層において少なくとも一方の導電層との間に複数の絶縁物が存在するように、一対の導電層において少なくとも一方の導電層が複数の絶縁物を含むように形成する。複数の絶縁物を導電層と有機化合物層との間に介在させることで、記憶素子の特性がバラつかずに安定化し、正常な書き込みを行うことができる。

絶縁物は、導電性材料との共蒸着や、導電層中へ添加(ドーピング、イオン注入法などによる)、導電層の表面への改質処理などによって、導電層中に含まれる。絶縁物の導電層内での存在形状は、その材料、作製方法によって異なり、その材料や形成方法によって、層中の絶縁物の濃度を制御することができる。

図1(A)に示す記憶素子は本発明の記憶素子の一例であり、絶縁物51を含む第1の導電層50上に、有機化合物層52が形成され、有機化合物層52上に第2の導電層53が形成されている。絶縁物51は、第1の導電層50中の第1の導電層50と有機化合物層52の界面に位置している。

図1(B)に示す記憶素子は本発明の記憶素子の一例であり、絶縁物61を含む第1の導電層60上に、有機化合物層62が形成され、有機化合物層62上に第2の導電層63が形成されている。絶縁物61は、第2の導電層63中の第2の導電層63と有機化合物層62の界面に位置している。

図1(C)に示す記憶素子は本発明の記憶素子の一例であり、第1の絶縁物71を含む第1の導電層70上に、有機化合物層72が形成され、有機化合物層72上に第2の絶縁物74を含む第2の導電層73が形成されている。絶縁物71は、第1の導電層70中の第1の導電層70と有機化合物層72の界面に位置しており、絶縁物74は、第2の導電層73中の第2の導電層73と有機化合物層72の界面に位置している。

図1(A)(B)(C)の記憶素子において、第1の導電層50、第1の導電層70、第2の導電層63、第2の導電層73中にそれぞれ含まれる絶縁物51、絶縁物61、絶縁物71、絶縁物74は混入していることを明確に示すために、球状の粒子で表している。しかし、絶縁物はこの形状に限定されず、絶縁物の形状は、粒状、柱状、針状、板状などどのような形状でも良く、複数の絶縁物が凝集し、単体として集合体を形成してもよい。

第1の導電層50、第1の導電層60、第1の導電層70、第2の導電層53、第2の導電層63、及び第2の導電層73の材料には導電性の高い元素や化合物等を用いる。本実施の形態において有機化合物層52、有機化合物層62、及び有機化合物層72の材料には電気的作用により、結晶状態や導電性、形状が変化する物質を用いる。上記構成を有する記憶素子は電圧印加前後で導電性が変化するので、「初期状態」と「導電性変化後」とに対応した2つの値を記憶させることができる。電圧印加前後での記憶素子の導電性の変化について説明する。

本実施の形態では、記憶装置に含まれる記憶素子を構成する第1の導電層50に絶縁物51を含んで形成し、第1の導電層50及び絶縁物51に接して、有機化合物層52を形成する。第1の導電層50と第2の導電層53との間に電圧を印加すると、有機化合物層52に電流が流れて熱が発生する。そして、有機化合物層の温度が、ガラス転移温度まで上昇すると、有機化合物層52を形成する材料は、流動性を有する組成物となる。流動性を有する組成物は固体状態の形状を維持せずに、流動する。よって、ジュール熱や高電界の影響により有機化合物層の膜厚は不均一となり、有機化合物層が変形し、第1の導電層50と第2の導電層53とが接してしまい、結果第1の導電層50と第2の導電層53とが短絡する。よって、電圧印加前後での記憶素子の導電性が変化する。

有機化合物層52と第1の導電層50との界面に存在する絶縁物51により、第1の導電層50から有機化合物層52へのキャリアのトンネル注入が可能になる。よって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。

また、複数の絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で複数の絶縁物を導電層と有機化合物層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、歩留まりが向上する。更に、複数の絶縁物を導電層中に混入させた状態、あるいは複数の絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

図1(B)のように、第2の導電層63中に絶縁物61を混在させ、有機化合物層62との界面に存在させてもよい。図1(A)の記憶素子と同様に、有機化合物層62と第2の導電層63との界面に存在する絶縁物61により、有機化合物層62から第2の導電層63へのキャリアのトンネル注入が可能になる。

また、図1(C)のように、第1の導電層70及び第2の導電層73両方にそれぞれ絶縁物71、絶縁物74を混在させ、第1の導電層70と有機化合物層72との界面、有機化合物層72と第2の導電層73との界面にそれぞれ存在させてもよい。図1(A)の記憶素子と同様に、第1の導電層70と有機化合物層72との界面に存在する絶縁物71により、第1の導電層70から有機化合物層72へのキャリアのトンネル注入が可能になり、図1(B)の記憶素子と同様に、有機化合物層72と第2の導電層73との界面に存在する絶縁物74により、有機化合物層72から第2の導電層73へのキャリアのトンネル注入が可能になる。第1の導電層70中に含まれる絶縁物71と、第2の導電層73中に含まれる絶縁物74とは同一材料を用いてもよく、それぞれ異なる材料を用いてもよい。

なお、本発明の記憶素子に印加する電圧は、第2の導電層より第1の導電層により高い電圧をかけてもよいし、第1の導電層より第2の導電層により高い電圧をかけてもよい。記憶素子が整流性を有する場合も、順バイアス方向に電圧が印加されるように、第1の導電層と第2の導電層との間に電位差を設けてもよいし、逆バイアス方向に電圧が印加されるように、第1の導電層と第2の導電層との間に電位差を設けてもよい。

本発明では、有機化合物層を挟んで設けられる一対の導電層のうち、少なくとも一つの導電層に複数の絶縁物を混入させた、複数の絶縁物を含む導電層を記憶素子の電極として用いる。導電層中への複数の絶縁物の混入状態は、用いる材料や形成方法などによって異なる。図1で示す複数の絶縁物を含む導電層は、導電層内に粒子状の複数の絶縁物が分散している例であり、導電層と有機化合物層の界面に複数の絶縁物が存在している。図1では、導電層中に粒子状の複数の絶縁物を混入させることで複数の絶縁物を含む導電層を形成する例を示した。絶縁物混入領域を有する導電層を記憶素子に用いる例を、図17を用いて説明する。

図17(A)、(B)、(C)における記憶素子は、導電層中に絶縁物混入領域を有する例である。図17(A)、図17(C)では、第1の導電層表面に絶縁物混入領域を有しており、このような場合共蒸着法やスパッタ法などで一工程により、絶縁物混入領域を有する導電層を形成することもできるし、あるいは導電層を形成後、導電層の表面を改質処理することによって、絶縁物混入領域を有する導電層を形成することもできる。導電層中の複数の絶縁物は、有機化合物層との界面に存在して、トンネル注入を行う効果がある。よって、導電層の表面に改質処理を行って、導電層表面に絶縁物混入領域を設けるようにすると、その上に形成する有機化合物層との界面に絶縁物混入領域を形成することができる。導電層の表面処理として、空気酸化、酸素雰囲気下での酸化、薬液によるフッ素化などを行えばよい。

図17(A)に示す記憶素子は本発明の記憶素子の一例であり、絶縁物混入領域56を有する第1の導電層55上に、有機化合物層57が形成され、有機化合物層57上に第2の導電層58が形成されている。導電層55内において混入する絶縁物は濃度勾配を有しており、複数の絶縁物は導電層55内に不均一に存在している。絶縁物混入領域56は、有機化合物層57と第1の導電層55との界面付近に有している。よって絶縁物の濃度は有機化合物層57と第1の導電層55との界面が最も高い。絶縁物混入領域は非絶縁物混入領域と明確な界面を有さずに、第1の導電層55内で膜厚方向に有機化合物層57から遠のくにつれ徐々に絶縁物の濃度が低く変化する。

図17(B)に示す記憶素子は本発明の記憶素子の一例であり、第1の導電層65上に、有機化合物層67が形成され、有機化合物層67上に絶縁物混入領域66を有する第2の導電層68が形成されている。有機化合物層67内において混入する絶縁物は濃度勾配を有しており、複数の絶縁物は第2の導電層68内に不均一に存在している。よって絶縁物の濃度は有機化合物層67と第2の導電層68との界面が最も高い。絶縁物混入領域66は、有機化合物層67と第2の導電層68との界面付近に有している。絶縁物混入領域は非絶縁物混入領域と明確な界面を有さずに、第2の導電層68内で膜厚方向に有機化合物層67から遠のくにつれ徐々に絶縁物の濃度が低く変化する。

図17(C)に示す記憶素子は本発明の記憶素子の一例であり、絶縁物混入領域76を有する第1の導電層75上に、有機化合物層77が形成され、有機化合物層77上に絶縁物混入領域79を有する第2の導電層78が形成されている。第1の導電層75内及び第2の導電層78それぞれにおいて混入する絶縁物は濃度勾配を有しており、複数の絶縁物は第1の導電層75内及び第2の導電層78内に不均一に存在している。第1の導電層75内において、有機化合物層77との界面付近に絶縁物混入領域76を有し、第2の導電層78内において、有機化合物層77との界面付近に絶縁物混入領域79を有している。よって絶縁物の濃度は有機化合物層77と第1の導電層75との界面、及び有機化合物層77と第2の導電層78との界面が最も高い。絶縁物混入領域は非絶縁物混入領域と明確な界面を有さずに、徐々に濃度は変化しており、第1の導電層75内及び第2の導電層78内で膜厚方向に有機化合物層77に遠のくにつれ絶縁物の濃度は低く変化する。

複数の絶縁物を含む導電層は、複数の絶縁物と導電性材料とを混入させて、一工程で複数の絶縁物を含む導電層を形成しても良く、どちらか一方を先に形成し、他の一方を別工程で導入(添加)してもよい。一工程で形成する場合、共蒸着法やスパッタリング法などのドライプロセスで形成しても良く、塗布法などの湿式法で複数の絶縁物と導電性材料との混合材料を用いて、膜状に形成しても良い。導電層内の絶縁物の分布は、上記形成方法を用いて、所望の濃度に制御することができる。

絶縁物を含む導電層は、電子ビーム蒸着法、共蒸着などの蒸着法、スパッタリング法、CVD法や、混合溶液を用いたスピンコート法など塗布法、ゾル−ゲル法を用いることができる。絶縁物を含む導電層は各々の材料を同時に成膜することにより形成することができ、抵抗加熱蒸着同士による共蒸着法、電子ビーム蒸着同士による共蒸着法、抵抗加熱蒸着と電子ビーム蒸着による共蒸着法、抵抗加熱蒸着とスパッタリングによる成膜、電子ビーム蒸着とスパッタリングによる成膜など、同種、異種の方法を組み合わせて形成することができる。また、特定の目的に調合された組成物の液滴を選択的に吐出(噴出)して所定のパターンに形成することが可能な、液滴吐出(噴出)法(その方式によっては、インクジェット法とも呼ばれる。)、ディスペンサ法、物体が所望のパターンに転写、または描写できる方法、例えば各種印刷法(スクリーン(孔版)印刷、オフセット(平版)印刷、凸版印刷やグラビア(凹版)印刷など所望なパターンで形成される方法)なども用いることができる。また、同時に形成するのではなく、導電層を形成した後に、イオン注入法やドーピング法などによって複数の絶縁物を導入し、複数の絶縁物と導電物との混合層を形成してもよい。導電層を形成後、表面を改質処理することによって絶縁物混入領域を有する導電層を形成してもよい。

絶縁物混入領域を有する導電層を形成後、その表面をドライエッチングやウェットエッチングなどのエッチングにより、所望の形状に加工してもよいし、表面を削るなどの加工を行ってもよい。絶縁物混入領域を所望の形状に加工することによって、有機化合物層との界面に存在し、有機化合物層と接する絶縁物の量や濃度を制御することができる。本発明でも用いることのできる絶縁物を含む導電層の形状について、図16を用いて説明する。図16(A1)(A2)において、基板80上に絶縁物混入領域82を有する第1の導電層81が形成されている。図16(A1)(A2)のように、第1の導電層81中に選択的に絶縁物混入領域を形成し、絶縁物混入領域が膜として連続性を有さずに、不連続な島状の形状となる場合がある。図16(A1)(A2)において、第1の導電層81中の絶縁物混入領域82は、無秩序な形状の島状で、無規則な位置に形成され、上面図である図16(A1)における線Y−Zの断面図である図16(A2)で確認できるように、個々の島状の絶縁物混入領域82を有する第1の導電層81は膜厚分布を有しており、その表面に凹凸形状を有する場合もある。

図16(B1)(B2)は、絶縁物混入領域87が秩序を有する島状の層で規則的な位置に形成される例である。図16(B1)は上面図であり、図16(B2)は、図16(B1)における線Y−Zの断面図である。図16(B1)(B2)において、基板85上に、絶縁物混入領域87を有する第1の導電層86が形成されている。図16(B1)(B2)のように、絶縁物混入領域87を、平坦性を有する秩序ある島状の形状とし、規則的な位置に形成してもよい。

勿論上記のようなエッチング加工を行わずに選択的に導電層中に絶縁物混入領域を形成する方法でもよい。

本発明において絶縁物を含む導電層とは、少なくとも一種類以上の絶縁物が導電層表面に混入していればよい。よって層中の複数の絶縁物と導電性材料との混合比や、混合の状態は、用いる材料や必要とされる機能に応じて、適宜設定すればよい。例えば、複数の絶縁物と導電性材料とが、混合層中において、均一に混合されていてもよいし、混合率に分布を有し不均一に混合されていてもよい。また、本発明の絶縁物を含む導電層中の絶縁物混入領域は、不連続な島状の形状となる場合があるが、この場合、島状の層ごとに絶縁物と導電性材料との混合状態、濃度が異なっていてもよい。

また、本発明の記憶素子は、複数の絶縁物を含む導電層上に絶縁物と接するように有機化合物層を積層するという構造を有する。このような積層構造において、絶縁物を含む導電層と有機化合物層との界面が、連続的な界面として明確でなくてもよい。例えば、表面に凹凸形状を有する絶縁物を含む導電層の凹凸を埋めるように、有機化合物層が形成されるような界面でもよい。

本発明において、導電層に混入する複数の絶縁物は、熱的及び化学的に安定で、キャリア注入されない無機絶縁物又は有機化合物を用いる。好ましくは、有機化合物層に混入する絶縁物は、電気伝導率が10−10s/m以下、より好ましくは10−10以上10−14s/m以下のものを用いることができる。以下に絶縁物に用いることのできる、無機絶縁物と有機化合物との具体例を述べる。

本発明において、導電層に混入する絶縁物に用いることのできる無機絶縁物として、酸化リチウム(Li2O)、酸化ナトリウム(Na2O)、酸化カリウム(K2O)、酸化ルビジウム(Rb2O)、酸化ベリリウム(BeO)、酸化マグネシウム(MgO)、酸化カルシウム(CaO)、酸化ストロンチウム(SrO)、酸化バリウム(BaO)、酸化スカンジウム(Sc2O3)、酸化ジルコニウム(ZrO2)、酸化ハフニウム(HfO2)、酸化ラザホージウム(RfO2)、酸化タンタル(TaO)、酸化テクネチウム(TcO)、酸化鉄(Fe2O3)、酸化コバルト(CoO)、酸化パラジウム(PdO)、酸化銀(Ag2O)、酸化アルミニウム(Al2O3)、酸化ガリウム(Ga2O3)、酸化ビスマス(Bi2O3)などの酸化物を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、フッ化リチウム(LiF)、フッ化ナトリウム(NaF)、フッ化カリウム(KF)、フッ化ルビジウム(RbF)、フッ化ベリリウム(BeF2)、フッ化マグネシウム(MgF2)、フッ化カルシウム(CaF2)、フッ化ストロンチウム(SrF2)、フッ化バリウム(BaF2)、フッ化アルミニウム(AlF3)、三フッ化窒素(NF3)、六フッ化硫黄(SF6)、フッ化銀(AgF)、フッ化マンガン(MnF3)などのフッ化物を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、塩化リチウム(LiCl)、塩化ナトリウム(NaCl)、塩化カリウム(KCl)、塩化ベリリウム(BeCl2)、塩化カルシウム(CaCl2)、塩化バリウム(BaCl2)、塩化アルミニウム(AlCl3)、塩化珪素(SiCl4)、塩化ゲルマニウム(GeCl4)、塩化スズ(SnCl4)、塩化銀(AgCl)、塩化亜鉛(ZnCl)、四塩化チタン(TiCl4)、三塩化チタン(TiCl3)、塩化ジルコニウム(ZrCl4)、塩化鉄(FeCl3)、塩化パラジウム(PdCl2)、三塩化アンチモン(SbCl3)、二塩化アンチモン(SbCl2)、塩化ストロンチウム(SrCl2)、塩化タリウム(TlCl)、塩化銅(CuCl)、塩化マンガン(MnCl2)、塩化ルテニウム(RuCl2)などの塩化物を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、臭化カリウム(KBr)、臭化セシウム(CsBr)、臭化銀(AgBr)、臭化バリウム(BaBr2)、臭化珪素(SiBr4)、臭化リチウム(LiBr)などの臭化物を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、ヨウ化ナトリウム(NaI)、ヨウ化カリウム(KI)、ヨウ化バリウム(BaI2)、ヨウ化タリウム(TlI)、ヨウ化銀(AgI)、ヨウ化チタン(TiI4)、ヨウ化カルシウム(CaI2)、ヨウ化珪素(SiI4)、ヨウ化セシウム(CsI)などのヨウ化物を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、炭酸リチウム(Li2CO3)、炭酸カリウム(K2CO3)、炭酸ナトリウム(Na2CO3)、炭酸マグネシウム(MgCO3)、炭酸カルシウム(CaCO3)、炭酸ストロンチウム(SrCO3)、炭酸バリウム(BaCO3)、炭酸マンガン(MnCO3)、炭酸鉄(FeCO3)、炭酸コバルト(CoCO3)、炭酸ニッケル(NiCO3)、炭酸銅(CuCO3)、炭酸銀(Ag2CO3)、炭酸亜鉛(ZnCO3)などの炭酸塩を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、硫酸リチウム(Li2SO4)、硫酸カリウム(K2SO4)、硫酸ナトリウム(Na2SO4)、硫酸マグネシウム(MgSO4)、硫酸カルシウム(CaSO4)、硫酸ストロンチウム(SrSO4)、硫酸バリウム(BaSO4)、硫酸チタン(Ti2(SO4)3)、硫酸ジルコニウム(Zr(SO4)2)、硫酸マンガン(MnSO4)、硫酸鉄(FeSO4)、三硫酸二鉄(Fe2(SO4)3)、硫酸コバルト(CoSO4)、硫酸コバルト(Co2(SO4)3)、硫酸ニッケル(NiSO4)、硫酸銅(CuSO4)、硫酸銀(Ag2SO4)、硫酸亜鉛(ZnSO4)、硫酸アルミニウム(Al2(SO4)3)、硫酸インジウム(In2(SO4)3)、硫酸スズ(SnSO4)、硫酸スズ(Sn(SO4)2)、硫酸アンチモン(Sb2(SO4)3)、硫酸ビスマス(Bi2(SO4)3)などの硫酸塩を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、硝酸リチウム(LiNO3)、硝酸カリウム(KNO3)、硝酸ナトリウム(NaNO3)、硝酸マグネシウム(Mg(NO3)2)、硝酸カルシウム(Ca(NO3)2)、硝酸ストロンチウム(Sr(NO3)2)、硝酸バリウム(Ba(NO3)2)、硝酸チタン(Ti(NO3)4)、硝酸ストロンチウムSr(NO3)2)、硝酸バリウム(Ba(NO3)2)、硝酸ジルコニウム(Zr(NO3)4)、硝酸マンガン(Mn(NO3)2)、硝酸鉄(Fe(NO3)2)、硝酸鉄(Fe(NO3)3)、硝酸コバルト(Co(NO3)2)、硝酸ニッケル(Ni(NO3)2)、硝酸銅(Cu(NO3)2)、硝酸銀(AgNO3)、硝酸亜鉛(Zn(NO3)2)、硝酸アルミニウム(Al(NO3)3)、硝酸インジウム(In(NO3)3)、硝酸スズ(Sn(NO3)2)、硝酸ビスマス(Bi(NO3)3)などの硝酸塩を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる他の無機絶縁物として、窒化アルミニウム(AlN)、窒化珪素(SiN)などの窒化物、カルボン酸リチウム(CH3COOLi)、酢酸カリウム(CH3COOK)、酢酸ナトリウム(CH3COONa)、酢酸マグネシウム(Mg(CH3COO)2)、酢酸カルシウム(Ca(CH3COO)2)、酢酸ストロンチウム(Sr(CH3COO)2)、酢酸バリウム(Ba(CH3COO)2)などのカルボン酸塩を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる無機絶縁物は、上記無機絶縁物の一種、または複数種を用いることができる。

本発明において、導電層に混入する絶縁物に用いることのできる有機化合物は、キャリア注入されにくいもの、バンドギャップが3.5eV以上、好ましくは4eV以上6eV以下ものを用いることができる。例えば、ポリイミド、アクリル、ポリアミド、ベンゾシクロブテン、ポリエステル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、珪素樹脂、フラン樹脂、ジアリルフタレート樹脂、シロキサン樹脂を用いることができる。なお、シロキサン樹脂とは、Si−O−Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

本発明において、導電層に混入する絶縁物に用いることのできる有機化合物は、上記有機化合物の一種、または複数種を用いることができる。

本発明において、導電層に混入する絶縁物は、上記無機絶縁物及び上記有機化合物の一種または複数種を用いることができる。

また、第1の導電層50、第1の導電層60、第1の導電層70、第2の導電層53、第2の導電層63、第2の導電層73には、導電性の高い元素や化合物等用いる。代表的には、金(Au)、銀(Ag)、白金(Pt)、ニッケル(Ni)、タングステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、炭素(C)、アルミニウム(Al)、マンガン(Mn)、チタン(Ti)、タンタル(Ta)等から選ばれた一種の元素または当該元素を複数含む合金からなる単層または積層構造を用いることができる。上記元素を複数含んだ合金としては、例えば、AlとTiを含んだ合金Al、TiとCを含んだ合金、AlとNiを含んだ合金、AlとCを含んだ合金、AlとNiとCを含んだ合金またはAlとMoを含んだ合金等を用いることができる。

絶縁物を含む導電層を積層構造で形成する場合、積層する複数の導電層全てに絶縁物を混入させてもよいし、少なくとも有機化合物層に接する導電層に絶縁物を混入させればよい。例えば、第1の導電層50を2層の導電層を積層した積層構造とした場合、有機化合物層52と接する一番上層の導電層のみに絶縁物を混入し、その下層の導電層には絶縁物を混入しない構造とすることができる。この場合、上層の導電層には酸化されやすい導電性材料を用いて、その表面に絶縁物混入領域を形成し、下層の導電層に低抵抗な導電性材料を用いて電極、配線として電気的特性を満たすように設計することができる。

第1の導電層50、第1の導電層60、第1の導電層70、第1の導電層55、第1の導電層65、第1の導電層75、第2の導電層53、第2の導電層63、第2の導電層73、第2の導電層58、第2の導電層68、第2の導電層78は、蒸着法、スパッタ法、CVD法、印刷法、ディスペンサ法、または液滴吐出法を用いて形成することができる。

また、第1の導電層50、第1の導電層60、第1の導電層70、第1の導電層55、第1の導電層65、第1の導電層75、第2の導電層53、第2の導電層63、第2の導電層73、第2の導電層58、第2の導電層68、第2の導電層78のうち、一方または両方が透光性を有するように設けてもよい。透光性を有する導電層は、透明な導電性材料を用いて形成するか、または、透明な導電性材料でなくても光を透過する厚さで形成する。透明な導電性材料としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、又は酸化チタンを含むインジウム錫酸化物などその他の透光性酸化物導電材料を用いることが可能である。ITO及び酸化珪素を含む酸化インジウムスズ(以下、ITSOと記す)や、酸化珪素を含んだ酸化インジウムに2〜20wt%の酸化亜鉛(ZnO)を混合したターゲットを用いて形成された酸化物導電性材料を用いても良い。

有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77は、有機化合物、電気的作用により導電性が変化する有機化合物、又は有機化合物と無機化合物とが混合してなる層で形成する。

上記有機化合物と無機化合物との混合層を構成することが可能な無機化合物としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等を用いることができる。

有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77を構成することが可能な有機化合物としては、ポリイミド、アクリル、ポリアミド、ベンゾシクロブテン、エポキシ等に代表される有機樹脂を用いることができる。

また、有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77を構成することが可能な、電気的作用により導電性が変化する有機化合物としては、正孔輸送性を有する有機化合物材料又は電子輸送性を有する有機化合物材料を用いることができる。

正孔輸送性を有する有機化合物材料としては、4,4’−ビス[N−(1−ナフチル)−N−フェニル−アミノ]−ビフェニル(略称:α−NPD)や4,4’−ビス[N−(3−メチルフェニル)−N−フェニル−アミノ]−ビフェニル(略称:TPD)や4,4’,4’’−トリス(N,N−ジフェニル−アミノ)−トリフェニルアミン(略称:TDATA)、4,4’,4’’−トリス[N−(3−メチルフェニル)−N−フェニル−アミノ]−トリフェニルアミン(略称:MTDATA)や4,4’−ビス(N−(4−(N,N−ジ−m−トリルアミノ)フェニル)−N−フェニルアミノ)ビフェニル(略称:DNTPD)などの芳香族アミン系(即ち、ベンゼン環−窒素の結合を有する)の化合物やフタロシアニン(略称:H2Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)等のフタロシアニン化合物を用いることができる。ここに述べた物質は、主に10−6cm2/Vs以上、より好ましくは10−6cm2/Vs以上10−2cm2/Vs以下の正孔移動度を有する物質である。

電子輸送性を有する有機化合物材料としては、トリス(8−キノリノラト)アルミニウム(略称:Alq3)、トリス(4−メチル−8−キノリノラト)アルミニウム(略称:Almq3)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(略称:BeBq2)、ビス(2−メチル−8−キノリノラト)−4−フェニルフェノラト−アルミニウム(略称:BAlq)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料を用いることができる。また、この他、ビス[2−(2−ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称:Zn(BOX)2)、ビス[2−(2−ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称:Zn(BTZ)2)などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,3,4−オキサジアゾール(略称:PBD)、1,3−ビス[5−(p−tert−ブチルフェニル)−1,3,4−オキサジアゾール−2−イル]ベンゼン(略称:OXD−7)、3−(4−tert−ブチルフェニル)−4−フェニル−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:TAZ)、3−(4−tert−ブチルフェニル)−4−(4−エチルフェニル)−5−(4−ビフェニリル)−1,2,4−トリアゾール(略称:p−EtTAZ)、バソフェナントロリン(略称:BPhen)、バソキュプロイン(略称:BCP)等を用いることができる。ここに述べた物質は、主に10−6cm2/Vs以上、より好ましくは10−6cm2/Vs以上10−2cm2/Vs以下の電子移動度を有する物質である。

本発明において、有機化合物層に用いることのできる有機化合物材料は、上記有機化合物材料の一種、または複数種を用いることができる。

なお、有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77は、電気的作用により記憶素子の導電性が変化する膜厚で形成する。

第1の導電層50、第1の導電層60、第1の導電層70、第1の導電層55、第1の導電層65、第1の導電層75を介して有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77と反対側に、整流性を有する素子を設けてもよい。例えば、第3の導電層及び半導体層で構成されるダイオードを第1の導電層50、第1の導電層60、第1の導電層70、第1の導電層55、第1の導電層65、第1の導電層75に接して設ければよい。なお、第2の導電層を介して有機化合物層と反対側に整流性を有する素子を設けてもよい。また、第1の導電層50、第1の導電層60、第1の導電層70、第1の導電層55、第1の導電層65、第1の導電層75と有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77との間に、整流性を有する素子を設けてもよい。整流性を有する素子とは、ゲート電極とドレイン電極を接続したトランジスタ、又はダイオードである。例えば、N型半導体層およびP型半導体層を積層させて設けられたPN接合ダイオードを用いることができる。このように、整流性があるダイオードを設けることにより、1つの方向にしか電流が流れないために、誤差が減少し、読み出しマージンが向上する。なお、ダイオードを設ける場合、PN接合を有するダイオードではなく、PIN接合を有するダイオードやアバランシェダイオード等の、他の構成のダイオードを用いてもよい。なお、上記整流性を有する素子は、有機化合物層52、有機化合物層62、有機化合物層72、有機化合物層57、有機化合物層67、有機化合物層77と第2の導電層53、第2の導電層63、第2の導電層73、第2の導電層58、第2の導電層68、第2の導電層78との間に設けてもよい。上記整流性を有する素子を設ける場合でも、有機化合物層に接して複数の絶縁物が存在するように、有機化合物層と接する一対の導電層のうち少なくとも一方には絶縁物を混入し、複数の絶縁物を導電層と有機化合物層との界面に有する構造とする必要がある。

本発明によって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、複数の絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で複数の絶縁物を導電層と有機化合物層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

(実施の形態2)

本実施の形態では、本発明の記憶装置が有する記憶素子の一構成例に関して図面を用いて説明する。より具体的には、記憶装置の構成がパッシブマトリクス型の場合に関して示す。

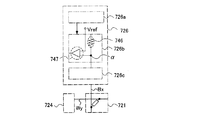

図3に示したのは本発明の記憶装置が有する一構成例であり、メモリセル721がマトリクス状に設けられたメモリセルアレイ722、カラムデコーダ726aと読み出し回路726bとセレクタ726cを有するビット線駆動回路726、ロウデコーダ724aとレベルシフタ724bを有するワード線駆動回路724、書き込み回路等を有し外部とのやりとりを行うインターフェイス723を有している。なお、ここで示す記憶装置716の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の他の回路を有していてもよいし、書き込み回路をビット線駆動回路に設けてもよい。

メモリセル721は、ワード線Wy(1≦y≦n)を構成する第1の導電層と、ビット線Bx(1≦x≦m)を構成する第2の導電層と、有機化合物層とを有する。有機化合物層は、第1の導電層と第2の導電層の間に単層または積層して設けられている。

メモリセルアレイ722の上面図を図2(A)に、図2(A)における線A−Bの断面図を図2(B)、及び図2(C)に示す。また、図2(A)には、絶縁層754は省略され図示されていないが、図2(B)で示すようにそれぞれ設けられている。

メモリセルアレイ722は、第1の方向に延びた複数の絶縁物756aを含む第1の導電層751a、複数の絶縁物756bを含む第1の導電層751b、及び複数の絶縁物756cを含む第1の導電層751cと、複数の絶縁物756aを含む第1の導電層751a、複数の絶縁物756bを含む第1の導電層751b、及び複数の絶縁物756cを含む第1の導電層751cを覆って設けられた有機化合物層752と、第1の方向と垂直な第2の方向に延びた第2の導電層753a、第2の導電層753b、第2の導電層753aとを有している(図2(A)参照。)。複数の絶縁物756aは第1の導電層751aと有機化合物層752との界面に存在し、複数の絶縁物756bは第1の導電層751bと有機化合物層752との界面に存在し、複数の絶縁物756cは第1の導電層751cと有機化合物層752との界面にそれぞれ存在している。また、第2の導電層753a、第2の導電層753b、第2の導電層753aを覆うように、保護膜として機能する絶縁層754を設けている(図2(B)参照。)。なお、隣接する各々のメモリセル間において横方向への電界の影響が懸念される場合は、各メモリセルに設けられた有機化合物層752を分離してもよい。

図2(C)は、図2(B)の変形例であり、基板790上に、絶縁物混入領域796aを有する第1の導電層791a、絶縁物混入領域796bを有する第1の導電層791b、絶縁物混入領域796cを有する第1の導電層791c、有機化合物層792、第2の導電層793b、保護層である絶縁層794を有している。図2(C)の絶縁物混入領域796aを有する第1の導電層791a、絶縁物混入領域796bを有する第1の導電層791b、絶縁物混入領域796cを有する第1の導電層791cのように、第1の導電層は、テーパーを有する形状でもよく、曲率半径が連続的に変化する形状でもよい。絶縁物混入領域796aを有する第1の導電層791a、絶縁物混入領域796bを有する第1の導電層791b、絶縁物混入領域796cを有する第1の導電層791cのような形状は、液滴吐出法などを用いて形成することができる。このような曲率を有する曲面であると、積層する絶縁層や導電層のカバレッジがよい。また、図2(C)における記憶素子を構成する第1の導電層は、第1の導電層を形成後、表面を改質処理し絶縁物混入領域を設ける例を示している。

本実施の形態における有機化合物層中における複数の絶縁物の混入状態は一例であり、複数の絶縁物として用いる材料の性質や大きさ、導電層として用いる材料、形成方法によって図17で示したように絶縁物の濃度などを適宜制御することができる。また、図1(B)(C)、及び図17(B)(C)のように、絶縁物を第2の導電層中に混入し、複数の絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよいし、第1の導電層及び第2の導電層両方に複数の絶縁物を混入し、複数の絶縁物を含む第1の導電層(絶縁物混入領域を有する第1の導電層)及び複数の絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよい。

また、第1の導電層の端部を覆うように隔壁(絶縁層)を形成してもよい。隔壁(絶縁層)は、他の記憶素子間を隔てる壁のような役目を果たす。図8(A)(B)に第1の導電層の端部を隔壁(絶縁層)で覆う構造を示す。図8(A)(B)も、図2(B)(C)と同様に図2(A)における線A−Bの断面図に対応している。

図8(A)に示す記憶素子の一例は、隔壁となる隔壁(絶縁層)775が、複数の絶縁物776aを含む第1の導電層771a、複数の絶縁物776bを含む第1の導電層771b、複数の絶縁物776cを含む第1の導電層771cの端部を覆うようにテーパーを有する形状で形成されている。基板770上に設けられた複数の絶縁物776aを含む第1の導電層771a、複数の絶縁物776bを含む第1の導電層771b、複数の絶縁物776cを含む第1の導電層771c上に、隔壁(絶縁層)775を形成し、有機化合物層772、第2の導電層773b、絶縁層774を形成する。

図8(B)に示す記憶素子の一例は、隔壁(絶縁層)765が曲率を有し、その曲率半径が連続的に変化する形状である。基板760上に設けられた絶縁物混入領域766aを有する第1の導電層761a、絶縁物混入領域766bを有する第1の導電層761b、絶縁物混入領域766cを有する第1の導電層761c、有機化合物層762、第2の導電層763b、絶縁層764が形成される。絶縁物混入領域766a、絶縁物混入領域766b、絶縁物混入領域766cは導電層表面に改質処理を行うことによって形成する他、絶縁物と導電性材料とを共蒸着法によって形成する方法、スパッタ法などで形成することができる。

上記メモリセルの構成において、基板750、基板760、基板770、基板780としては、ガラス基板や可撓性基板の他、石英基板、シリコン基板、金属基板、ステンレス基板等を用いることができる。可撓性基板とは、折り曲げることができる(フレキシブル)基板のことであり、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルフォン等からなるプラスチック基板等が挙げられる。また、貼り合わせフィルム(ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなる)、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)などを用いることもできる。また、この他にも、Si等の半導体基板上に形成された電界効果トランジスタ(FET)の上部や、ガラス等の基板上に形成された薄膜トランジスタ(TFT)の上部にメモリセルアレイ722を設けることができる。

本実施の形態で示した第1の導電層751a〜751c、第1の導電層761a〜761c、第1の導電層771a〜771c、第1の導電層791a〜791c、第2の導電層753a〜753c、第2の導電層763a〜763c、第2の導電層773a〜773c、第2の導電層793a〜793cの材料および形成方法は、上記実施の形態1で示した第1の導電層50、第2の導電層53の材料および形成方法のいずれかを用いて同様に行うことができる。

また、絶縁物756a〜756c、絶縁物776a〜776c、絶縁物混入領域766a〜766c中の絶縁物、絶縁物混入領域796a〜796c中の絶縁物、有機化合物層752、有機化合物層762、有機化合物層772、有機化合物層792は、上記実施の形態1で示した絶縁物、有機化合物層と同様の材料および形成方法を用いて設けることができる。

第1の導電層751a〜751c、第1の導電層761a〜761c、第1の導電層771a〜771c、第1の導電層791a〜791cを介して有機化合物層752、有機化合物層762、有機化合物層772、有機化合物層792と反対側に、整流性を有する素子を設けてもよい。例えば、第3の導電層及び半導体層で構成されるダイオードを第1の導電層751a〜751c、第1の導電層761a〜761c、第1の導電層771a〜771c、第1の導電層791a〜791cに接して設ければよい。なお、第2の導電層を介して有機化合物層と反対側に整流性を有する素子を設けてもよい。また、第1の導電層751a〜751c、第1の導電層761a〜761c、第1の導電層771a〜771c、第1の導電層791a〜791cと有機化合物層752、有機化合物層762、有機化合物層772、有機化合物層792との間に、整流性を有する素子を設けてもよい。なお、上記整流性を有する素子は、有機化合物層752、有機化合物層762、有機化合物層772、有機化合物層792と第2の導電層753a〜753c、第2の導電層763a〜763c、第2の導電層773a〜773c、第2の導電層793a〜793cとの間に設けてもよい。上記整流性を有する素子を設ける場合でも、有機化合物層に接して複数の絶縁物が存在するように、有機化合物層と接する一対の導電層のうち少なくとも一方には複数の絶縁物を混入し、複数の絶縁物を導電層と有機化合物層との界面に有する構造とする必要がある。

隔壁(絶縁層)765、隔壁(絶縁層)775としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又はシロキサン樹脂を用いてもよい。また、ポリビニルアルコール、ポリビニルブチラールなどのビニル樹脂、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フッ化アリレンエーテル、ポリイミドなどの有機材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いてもよい。作製法としては、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いることができる。また、液滴吐出法や、ディスペンサ法、印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)を用いることもできる。塗布法で得られるTOF膜やSOG膜なども用いることができる。

また、液滴吐出法により、導電層、絶縁層などを、組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしたりしてもよい。プレスする時に、加熱工程を行っても良い。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。

本発明によって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、複数の絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

(実施の形態3)

本実施の形態では、上記実施の形態2とは異なる構成を有する記憶装置について説明する。具体的には、記憶装置の構成がアクティブマトリクス型の場合に関して示す。

図5に示したのは本実施の形態で示す記憶装置の一構成例であり、メモリセル231がマトリクス状に設けられたメモリセルアレイ232、カラムデコーダ226aと読み出し回路226bとセレクタ226cを有するビット線駆動回路226、ロウデコーダ224aとレベルシフタ224bを有するワード線駆動回路224、書き込み回路等を有し外部とのやりとりを行うインターフェイス223を有している。なお、ここで示す記憶装置217の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の他の回路を有していてもよいし、書き込み回路をビット線駆動回路に設けてもよい。

メモリセル231は、ワード線Wy(1≦y≦n)を構成する第1の配線と、ビット線Bx(1≦x≦m)を構成する第2の配線と、トランジスタ210aと、記憶素子215bと、メモリセル231とを有する。記憶素子215bは、一対の導電層の間に、絶縁層が挟まれた構造を有する。

メモリセルアレイ232の上面図を図4(A)に、図4(A)における線E−Fの断面図を図4(B)に示す。また、図4(A)には、有機化合物層212、第2の導電層213及び絶縁層214は省略され図示されていないが、図4(B)で示すようにそれぞれ設けられている。

メモリセルアレイ232は、第1の方向に延びた第1の配線205a及び第1の配線205bと、第1の方向と垂直な第2の方向に延びた第2の配線202とがマトリクス状に設けられている。また、第1の配線はトランジスタ210a及びトランジスタ210bのソース電極又はドレイン電極に接続されており、第2の配線はトランジスタ210a及びトランジスタ210bのゲート電極に接続されている。さらに、第1の配線と接続されていないトランジスタ210a及びトランジスタ210bのソースまたはドレイン電極に、それぞれ複数の絶縁物216aを含む第1の導電層206a、及び複数の絶縁物216bを含む第1の導電層206bが接続され、それぞれ複数の絶縁物216aを含む第1の導電層206a、及び複数の絶縁物216bを含む第1の導電層206b、有機化合物層212、第2の導電層213の積層構造によって記憶素子215a、記憶素子215bが設けられている。隣接する各々のメモリセル231の間に隔壁(絶縁層)207を設けて、複数の絶縁物216aを含む第1の導電層206a、及び複数の絶縁物216bを含む第1の導電層206bと隔壁(絶縁層)207上に有機化合物層212および第2の導電層213を積層して設けている。また、第2の導電層213上に保護層となる絶縁層214を有している。図4においてはトランジスタ210a、トランジスタ210bとして、薄膜トランジスタを用いている(図4(B)参照。)。

図4(B)の記憶装置は基板200上に設けられており、絶縁層201a、絶縁層201b、絶縁層208、絶縁層209、絶縁層211、トランジスタ210aを構成する半導体層204a、ゲート電極層202a、ソース電極層又はドレイン電極層を兼ねる配線205a、トランジスタ210bを構成する半導体層204b、ゲート電極層202bを有している。絶縁物216aを含む第1の導電層206a、絶縁物216bを含む第1の導電層206b、隔壁(絶縁層)207上に有機化合物層212、第2の導電層213が形成されている。

本実施の形態における第1の導電層206a、第1の導電層206b中における絶縁物の混入状態は一例であり、絶縁物として用いる材料の性質や大きさ、導電層として用いる材料、形成方法によって図17で示したように絶縁物の濃度などを適宜制御することができる。また、図1(B)(C)、及び図17(B)(C)のように、絶縁物を第2の導電層中に混入し、絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよいし、第1の導電層及び第2の導電層両方に絶縁物を混入し、絶縁物を含む第1の導電層(絶縁物混入領域を有する第1の導電層)及び絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよい。図4における記憶素子215a、記憶素子215bでは、導電膜を所望の形状に加工し、第1の配線205a、第1の配線205b、第1の導電層206a、及び第1の導電層206bを形成した後、第1の導電層206a、第1の導電層206b中に絶縁物216a、絶縁物216bを選択的に混入する例を示す。絶縁物の混入は、導電膜を所望の形状に加工する前に行っても良く、その場合、第1の配線205a、第1の配線205bにも絶縁物が混入する構成となる。

本実施の形態では、記憶装置に含まれる記憶素子を構成する有機化合物層212を、絶縁物を含む第1の導電層上に形成する。第1の導電層と第2の導電層との間に電圧を印加すると、有機化合物層212に電流が流れて熱が発生する。こうした熱や高電界の影響により、有機化合物層の膜厚は不均一となり、有機化合物層が変形し、第1の導電層と第2の導電層とが接してしまい、結果第1の導電層と第2の導電層とが短絡する。よって、電圧印加前後での記憶素子の導電性が変化する。

有機化合物層212と第1の導電層206a、第1の導電層206bとの界面に存在する絶縁物216a、絶縁物216bにより、第1の導電層206a、第1の導電層206bから有機化合物層212へのキャリアのトンネル注入が可能になる。よって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

また、図6に示すように、単結晶半導体基板250上に設けられた電界効果トランジスタ260a、電界効果トランジスタ260bに記憶素子265a、記憶素子265bが接続されていてもよい。ここでは、電界効果トランジスタ260a及び電界効果トランジスタ260bのソース電極層又はドレイン電極層255a〜255dを覆うように絶縁層270を設け、絶縁層270上に絶縁物混入領域266aを含む第1の導電層256a、絶縁物混入領域266bを含む第1の導電層256b、隔壁(絶縁層)267、有機化合物層262a、有機化合物層262b、第2の導電層263で記憶素子265a、記憶素子265bを構成する。具体的には、絶縁物混入領域266aを含む第1の導電層256a、絶縁物混入領域266bを含む第1の導電層256b、隔壁267上に有機化合物層262a、有機化合物層262bが形成され、有機化合物層262a及び有機化合物層262b上に第2の導電層263が形成されている。有機化合物層262a、有機化合物層262bのように有機化合物層は、各メモリセルのみに、マスク等を用いて選択的に設けてもよい。また、図6に示す記憶装置は、素子分離領域268、絶縁層269、絶縁層261、絶縁層264も有している。

図6に示す第1の導電層256a、第1の導電層256b中における複数の絶縁物の混入状態は一例であり、絶縁物として用いる材料の性質や大きさ、導電層として用いる材料、形成方法によって図17で示したように絶縁物の濃度などを適宜制御することができる。また、図1(B)(C)、及び図17(B)(C)のように、絶縁物を第2の導電層中に混入し、絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよいし、第1の導電層及び第2の導電層両方に絶縁物を混入し、絶縁物を含む第1の導電層(絶縁物混入領域を有する第1の導電層)及び絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよい。

図6の記憶素子265a、記憶素子265b構成する第1の導電層256a、第1の導電層256bは導電層を、Alなどを用いて形成後、その表面に酸化するなどの改質処理を行い、絶縁物混入領域266a、絶縁物混入領域266bを設ける例である。酸化処理によって表面に絶縁物混入領域を形成する場合、導電層とし金属(例えばAl)や半導体(例えばSi)などの比較的酸化されやすい材料を用いるとよい。また、導電層を形成したのち、Siなどをドーピング法によって導電層中に添加し、その後加熱処理などを行い酸化することで選択的に導電層中に絶縁物混入領域を形成することもできる。

図6に示す記憶装置においては、記憶装置に含まれる記憶素子を構成する有機化合物層262a及び有機化合物層262bを、絶縁物混入領域266aを有する第1の導電層256a、絶縁物混入領域266bを有する第1の導電層256b上に形成する。第1の導電層と第2の導電層との間に電圧を印加すると、有機化合物層262a及び有機化合物層262bに電流が流れて熱が発生する。こうした熱や高電界の影響により、有機化合物層の膜厚は不均一となり、有機化合物層が変形し、第1の導電層と第2の導電層とが接してしまい、結果第1の導電層と第2の導電層とが短絡する。よって、電圧印加前後での記憶素子の導電性が変化する。

有機化合物層262a、有機化合物層262bと第1の導電層との界面にそれぞれ存在する絶縁物混入領域266a中の複数の絶縁物、絶縁物混入領域266b中の複数の絶縁物により、第1の導電層から有機化合物層262a、有機化合物層262bへのキャリアのトンネル注入が可能になる。よって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

また、絶縁層270を設けて記憶素子を形成することによって第1の導電層を自由に配置することができる。つまり、図4(B)の構成では、トランジスタ210a、トランジスタ210bのソース電極層又はドレイン電極層を避けた領域に記憶素子215a、記憶素子215bを設ける必要があったが、上記構成とすることによって、例えば、トランジスタ210a、トランジスタ210bの上方に記憶素子215a、記憶素子215bを形成することが可能となる。その結果、記憶装置をより高集積化することが可能となる。

トランジスタ210a、トランジスタ210bはスイッチング素子として機能し得るものであれば、どのような構成で設けてもよい。半導体層も非晶質半導体、結晶性半導体、多結晶半導体、微結晶半導体など様々な半導体を用いることができ、有機化合物を用いて有機トランジスタを形成してもよい。図4(A)では、絶縁性を有する基板上にプレーナ型の薄膜トランジスタを設けた例を示しているが、スタガ型や逆スタガ型等の構造でトランジスタを形成することも可能である。

図7に、逆スタガ型の構造の薄膜トランジスタを用いた例を示す。基板280上に、逆スタガ型の構造の薄膜トランジスタであるトランジスタ290a、トランジスタ290bが設けられている。トランジスタ290aは、絶縁層288、ゲート電極層281、非晶質半導体層282、一導電型を有する半導体層283a、一導電型を有する半導体層283b、ソース電極層又はドレイン電極層285を有し、もう一方のソース電極層又はドレイン電極層は記憶素子を構成する第1の導電層286aが兼ねている。第1の導電層286a、第1の導電層286bの端部を覆うように隔壁(絶縁層)287を積層し、複数の絶縁物296aを含む第1の導電層286a、複数の絶縁物296bを含む第1の導電層286b、隔壁(絶縁層)287上に有機化合物層292、第2の導電層293、保護層である絶縁層294が形成され、記憶素子295a、記憶素子295bを構成している。複数の絶縁物296a、複数の絶縁物296bは、第1の導電層286a、第1の導電層286bにおいて、第2の導電層293と重畳する記憶素子295a、記憶素子295bの領域に選択的に添加されている。このように、複数の絶縁物は第1の導電層中に選択的に混入されていてもよく、本実施の形態の図7の記憶装置では、第1の導電層286a、第1の導電層286bに選択的に複数の絶縁物296a、複数の絶縁物296bをドーピング法、イオン注入法などを用いて添加して作製する。

図7に示す第1の導電層256a、第1の導電層256b中における絶縁物の混入状態は一例であり、絶縁物として用いる材料の性質や大きさ、導電層として用いる材料、形成方法によって図17で示したように絶縁物の濃度などを適宜制御することができる。また、図1(B)(C)、及び図17(B)(C)のように、絶縁物を第2の導電層中に混入し、絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよいし、第1の導電層及び第2の導電層両方に絶縁物を混入し、絶縁物を含む第1の導電層(絶縁物混入領域を有する第1の導電層)及び絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよい。

本実施の形態の図7の記憶装置では、記憶装置に含まれる記憶素子を構成する有機化合物層292を、絶縁物296a、絶縁物296bを含む第1の導電層286a、第1の導電層286b上に形成する。第1の導電層と第2の導電層との間に電圧を印加すると、有機化合物層292に電流が流れて熱が発生する。こうした熱や高電界の影響によって有機化合物層の温度が、ガラス転移温度まで上昇すると、有機化合物層292を形成する材料は、流動性を有する組成物となる。流動性を有する組成物は固体状態の形状を維持せずに、流動する。よって、有機化合物層の膜厚は不均一となり、有機化合物層が変形し、第1の導電層と第2の導電層とが接してしまい、結果第1の導電層と第2の導電層とが短絡する。よって、電圧印加前後での記憶素子の導電性が変化する。

有機化合物層292と第1の導電層との界面にそれぞれ存在する絶縁物296a、絶縁物296bにより、第1の導電層から有機化合物層292へのキャリアのトンネル注入が可能になる。よって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

図7に示す記憶装置は、ゲート電極層281、ソース電極層又はドレイン電極層285、第1の導電層286a、第1の導電層286b、隔壁(絶縁層)287を液滴吐出法を用いて形成する。液滴吐出法とは流動体である構成物形成材料を含む組成物を、液滴として吐出(噴出)し、所望なパターン形状に形成する方法である。構成物の被形成領域に、構成物形成材料を含む液滴を吐出し、焼成、乾燥等を行って固定化し所望なパターンの構成物を形成する。

液滴吐出法に用いる液滴吐出装置の一態様を図15に示す。液滴吐出手段1403の個々のヘッド1405、ヘッド1412は制御手段1407に接続され、それがコンピュータ1410で制御することにより予めプログラミングされたパターンに描画することができる。描画するタイミングは、例えば、基板1400上に形成されたマーカー1411を基準に行えば良い。或いは、基板1400の縁を基準にして基準点を確定させても良い。これを撮像手段1404で検出し、画像処理手段1409にてデジタル信号に変換したものをコンピュータ1410で認識して制御信号を発生させて制御手段1407に送る。撮像手段1404としては、電荷結合素子(CCD)や相補型金属酸化物半導体(CMOS)を利用したイメージセンサなどを用いることができる。勿論、基板1400上に形成されるべきパターン形状の情報は記憶媒体1408に格納されたものであり、この情報を基にして制御手段1407に制御信号を送り、液滴吐出手段1403の個々のヘッド1405、ヘッド1412を個別に制御することができる。吐出する材料は、材料供給源1413、材料供給源1414より配管を通してヘッド1405、ヘッド1412にそれぞれ供給される。

ヘッド1405内部は、点線1406が示すように液状の材料を充填する空間と、吐出口であるノズルを有する構造となっている。図示しないが、ヘッド1412もヘッド1405と同様な内部構造を有する。ヘッド1405とヘッド1412のノズルを異なるサイズで設けると、異なる材料を異なる幅で同時に描画することができる。一つのヘッドで、導電性材料や有機、無機材料などをそれぞれ吐出し、描画することができ、層間膜のような広領域に描画する場合は、スループットを向上させるため複数のノズルより同材料を同時に吐出し、描画することができる。大型基板を用いる場合、ヘッド1405、ヘッド1412は基板上を、矢印の方向に自在に走査し、描画する領域を自由に設定することができ、同じパターンを一枚の基板に複数描画することができる。

液滴吐出法を用いて導電層を形成する場合、粒子状に加工された導電性材料を含む組成物を吐出し、焼成によって融合や融着接合させ固化することで導電層を形成する。このように導電性材料を含む組成物を吐出し、焼成することによって形成された導電層(または絶縁層)においては、スパッタ法などで形成した導電層(または絶縁層)が、多くは柱状構造を示すのに対し、多くの粒界を有する多結晶状態を示すことが多い。

また、トランジスタに含まれる半導体層の構造もどのようなものを用いてもよく、例えば不純物領域(ソース領域、ドレイン領域、LDD領域を含む)を形成してもよいし、pチャネル型またはnチャネル型のどちらで形成してもよい。また、ゲート電極の側面と接するように絶縁層(サイドウォール)を形成してもよいし、ソース、ドレイン領域とゲート電極の一方または両方にシリサイド層を形成してもよい。シリサイド層の材料としては、ニッケル、タングステン、モリブデン、コバルト、白金等を用いることができる。

本実施の形態で示した第1の導電層206a、206b、256a、256b、286a、286bと第2の導電層213、263、293の材料および形成方法は、上記実施の形態1で示した材料および形成方法のいずれかを用いて同様に行うことができる。

また、絶縁物216a、216b、296a、296b、絶縁物混入領域266a、266b中の絶縁物、有機化合物層212、262a、262b、292は、上記実施の形態1で示した絶縁物、有機化合物層と同様の材料および形成方法を用いて設けることができる。

第1の導電層206a、206b、256a、256b、286a、286bを介して有機化合物層212、262a、262b、292と反対側に、整流性を有する素子を設けてもよい(図2(C))。例えば、第3の導電層及び半導体層で構成されるダイオードを第1の導電層206a、206b、256a、256b、286a、286bに接して設ければよい。なお、第2の導電層を介して有機化合物層と反対側に整流性を有する素子を設けてもよい。さらには、第1の導電層206a、206b、256a、256b、286a、286bと有機化合物層212、262a、262b、292との間に、整流性を有する素子を設けてもよい。整流性を有する素子とは、ゲート電極とドレイン電極を接続したトランジスタ、又はダイオードである。例えば、N型半導体層およびP型半導体層を積層させて設けられたPN接合ダイオードを用いることができる。このように、整流性があるダイオードを設けることにより、1つの方向にしか電流が流れないために、誤差が減少し、読み出しマージンが向上する。なお、ダイオードを設ける場合、PN接合を有するダイオードではなく、PIN接合を有するダイオードやアバランシェダイオード等の、他の構成のダイオードを用いてもよい。なお、上記整流性を有する素子は、有機化合物層212、262a、262b、292と第2の導電層213、263、293との間に設けてもよい。上記整流性を有する素子を設ける場合でも、有機化合物層に接して絶縁物が存在するように、有機化合物層と接する一対の導電層のうち少なくとも一方には絶縁物を混入し、絶縁物を導電層と有機化合物層との界面に有する構造とする必要がある。

本発明によって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

(実施の形態4)

本実施の形態では、上記実施の形態で示す記憶装置を有する半導体装置の一例に関して図面を用いて説明する。

本実施の形態で示す半導体装置は、非接触でデータの読み出しと書き込みが可能であることを特徴としており、データの伝送形式は、一対のコイルを対向に配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別されるが、いずれの方式を用いてもよい。また、データの伝送に用いるアンテナは2通りの設け方があり、1つは複数の素子および記憶素子が設けられた基板上にアンテナを設ける場合、もう1つは複数の素子および記憶素子が設けられた基板に端子部を設け、当該端子部に別の基板に設けられたアンテナを接続して設ける場合がある。

まず、複数の素子および記憶素子が設けられた基板上にアンテナを設ける場合の半導体装置の一構成例を、図10を用いて説明する。

図10はアクティブマトリクス型で構成される記憶装置を有する半導体装置を示しており、基板300上にトランジスタ310a、310bを有するトランジスタ部330、トランジスタ320a、トランジスタ320bを有するトランジスタ部340、絶縁層301a、301b、308、311、316、334を含む素子形成層335が設けられ、素子形成層335の上方に記憶素子部325とアンテナとして機能する導電層343が設けられている。

なお、ここでは素子形成層335の上方に記憶素子部325またはアンテナとして機能する導電層343を設けた場合を示しているが、この構成に限られず記憶素子部325またはアンテナとして機能する導電層343を、素子形成層335の下方や同一の層に設けることも可能である。

記憶素子部325は、記憶素子315a、315bで構成され、記憶素子315aは複数の絶縁物326aを含む第1の導電層306a上に、隔壁(絶縁層)307a、隔壁(絶縁層)307b、有機化合物層312及び第2の導電層313が積層して構成され、記憶素子315bは、複数の絶縁物326bを含む第1の導電層306b上に、隔壁(絶縁層)307b、隔壁(絶縁層)307c、有機化合物層312及び第2の導電層313が積層して設けられている。また、第2の導電層313を覆って保護膜として機能する絶縁層314が形成されている。また、複数の記憶素子315a、315bが形成される第1の導電層306a、第1の導電層306bは、トランジスタ310a、トランジスタ310bそれぞれのソース電極層又はドレイン電極層に、接続されている。すなわち、記憶素子はそれぞれひとつのトランジスタに接続されている。また、有機化合物層312が複数の絶縁物326aを含む第1の導電層306a、複数の絶縁物326bを含む第1の導電層306bおよび隔壁(絶縁層)307a、307b、307cを覆うように全面に形成されているが、各メモリセルに選択的に形成されていてもよい。なお、記憶素子315a、315bは上記実施の形態で示した材料または作製方法を用いて形成することができる。

図10に示す第1の導電層306a、第1の導電層306b中における複数の絶縁物の混入状態は一例であり、絶縁物として用いる材料の性質や大きさ、導電層として用いる材料、形成方法によって図17で示したように絶縁物の濃度などを適宜制御することができる。また、図1(B)(C)、及び図17(B)(C)のように、絶縁物を第2の導電層中に混入し、絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよいし、第1の導電層及び第2の導電層両方に絶縁物を混入し、絶縁物を含む第1の導電層(絶縁物混入領域を有する第1の導電層)及び絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよい。

本実施の形態の図10の記憶装置では、記憶装置に含まれる記憶素子を構成する有機化合物層312を、絶縁物326aを含む第1の導電層306a及び絶縁物326bを含む第1の導電層306b上に形成する。第1の導電層と第2の導電層との間に電圧を印加すると、有機化合物層312に電流が流れて熱が発生する。こうした熱や高電界の影響によって、有機化合物層の膜厚は不均一となり、有機化合物層が変形し、第1の導電層と第2の導電層とが接してしまい、結果第1の導電層と第2の導電層とが短絡する。よって、電圧印加前後での記憶素子の導電性が変化する。

有機化合物層312と第1の導電層306a、第1の導電層306bとの界面にそれぞれ存在する絶縁物326a、絶縁物326bにより、第1の導電層306a、第1の導電層306bから有機化合物層312へのキャリアのトンネル注入が可能になる。よって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

第1の導電層306a、第1の導電層306bを介して有機化合物層312と反対側に、整流性を有する素子を設けてもよい。例えば、第3の導電層及び半導体層で構成されるダイオードを第1の導電層306a、第1の導電層306bに接して設ければよい。なお、第2の導電層を介して有機化合物層と反対側に整流性を有する素子を設けてもよい。また、記憶素子315aにおいて、絶縁物326aを含む第1の導電層306aと有機化合物層312との間、または有機化合物層312と第2の導電層313との間に整流性を有する素子を設けてもよい。整流性を有する素子も上述したものを用いることが可能である。なお、記憶素子315bにおいても同様である。

ここでは、アンテナとして機能する導電層343は第2の導電層313と同一の層で形成された導電層342上に設けられている。なお、第2の導電層313と同一の層でアンテナとして機能する導電層を形成してもよい。

アンテナとして機能する導電層343の材料としては、金(Au)、白金(Pt)、ニッケル(Ni)、タングステン(W)、モリブデン(Mo)、コバルト(Co)、銅(Cu)、アルミニウム(Al)、マンガン(Mn)、チタン(Ti)等から選ばれた一種の元素または当該元素を複数含む合金等を用いることができる。また、アンテナとして機能する導電層343の形成方法は、蒸着、スパッタ、CVD法、スクリーン印刷やグラビア印刷等の各種印刷法、ディスペンサ法、または液滴吐出法等を用いることができる。

素子形成層335に含まれるトランジスタ310a、310b、310c、310dは、pチャネル型TFT、nチャネル型TFTまたはこれらを組み合わせたCMOSで設けることができる。また、トランジスタ310a、310b、310c、310dに含まれる半導体層の構造もどのようなものを用いてもよく、例えば不純物領域(ソース領域、ドレイン領域、LDD領域を含む)を形成してもよいし、pチャネル型またはnチャネル型のどちらで形成してもよい。また、ゲート電極の側面と接するように絶縁層(サイドウォール)を形成してもよいし、ソース、ドレイン領域とゲート電極の一方または両方にシリサイド層を形成してもよい。シリサイド層の材料としては、ニッケル、タングステン、モリブデン、コバルト、白金等を用いることができる。

また、素子形成層335に含まれるトランジスタ310a、310b、310c、310dは、当該トランジスタを構成する半導体層を有機化合物で形成する有機トランジスタで設けてもよい。この場合、基板300としてプラスチック等の可撓性を有する基板上に、直接印刷法や液滴吐出法等を用いて有機トランジスタからなる素子形成層335を形成することができる。印刷法や液滴吐出法等を用いて形成することによってより低コストで半導体装置を作製することが可能となる。

また、素子形成層335、記憶素子315a、315b、アンテナとして機能する導電層343は、上述したように蒸着、スパッタ法、CVD法、印刷法、ディスペンサ法、または液滴吐出法等を用いて形成することができる。なお、各場所によって異なる方法を用いて形成してもかまわない。例えば、高速動作が必要とされるトランジスタは基板上にSi等からなる半導体層を形成した後に熱処理により結晶化させて設け、その後、素子形成層の上方にスイッチング素子として機能するトランジスタを印刷法や液滴吐出法を用いて有機トランジスタとして設けることができる。

なお、トランジスタに接続するセンサを設けてもよい。センサとしては、温度、湿度、照度、ガス(気体)、重力、圧力、音(振動)、加速度、その他の特性を物理的又は化学的手段により検出する素子が挙げられる。センサは、代表的には抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの半導体素子で形成される。

次に、複数の素子および記憶素子が設けられた基板に端子部を設け、当該端子部に別の基板に設けられたアンテナを接続して設ける場合の半導体装置の一構成例に関して図11を用いて説明する。

図11はパッシブマトリクス型の記憶装置を有する半導体装置を示しており、基板350上にトランジスタ360a、360bを有するトランジスタ部380、トランジスタ370a、トランジスタ370bを有するトランジスタ部390、絶縁層351a、351b、358、361、366、384を含む素子形成層385が設けられ、素子形成層385の上方に記憶素子部375が設けられ、基板396に設けられたアンテナとして機能する導電層393が素子形成層385と接続するように設けられている。なお、ここでは素子形成層385の上方に記憶素子部375またはアンテナとして機能する導電層393を設けた場合を示しているが、この構成に限られず記憶素子部375を素子形成層385の下方や同一の層に、またはアンテナとして機能する導電層393を素子形成層385の下方に設けることも可能である。

記憶素子部375は、記憶素子365a、365bで構成され、記憶素子365aは絶縁物混入領域376を有する第1の導電層356上に、隔壁(絶縁層)357a、隔壁(絶縁層)357b、有機化合物層362a及び第2の導電層363aが積層して構成され、記憶素子365bは、絶縁物混入領域376を有する第1の導電層356上に、隔壁(絶縁層)357b、隔壁(絶縁層)357c、有機化合物層362b及び第2の導電層363bが積層して設けられている。また、第2の導電層363a、363bを覆って保護膜として機能する絶縁層364が形成されている。また、複数の記憶素子365a、365bが形成される絶縁物混入領域376を有する第1の導電層356は、トランジスタ360bひとつのソース電極層又はドレイン電極層に、接続されている。すなわち、記憶素子は同じひとつのトランジスタに接続されている。また、有機化合物層362a、有機化合物層362bはメモリセルごとに有機化合物層を分離するための隔壁(絶縁層)357a、357b、357cを設けているが、隣接するメモリセルにおいて横方向への電界の影響が懸念されない場合は、全面に形成してもよい。なお、記憶素子365a、365bは上記実施の形態で示した材料または作製方法を用いて形成することができる。

図11に示す第1の導電層356中における複数の絶縁物の混入状態は一例であり、絶縁物として用いる材料の性質や大きさ、導電層として用いる材料、形成方法によって図17で示したように絶縁物の濃度などを適宜制御することができる。また、図1(B)(C)、及び図17(B)(C)のように、絶縁物を第2の導電層中に混入し、絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよいし、第1の導電層及び第2の導電層両方に絶縁物を混入し、絶縁物を含む第1の導電層(絶縁物混入領域を有する第1の導電層)及び絶縁物を含む第2の導電層(絶縁物混入領域を有する第2の導電層)としてもよい。

本実施の形態の図11の記憶装置では、記憶装置に含まれる記憶素子を構成する有機化合物層362a及び有機化合物層362bを、絶縁物混入領域376を有する第1の導電層356上に形成する。第1の導電層と第2の導電層との間に電圧を印加すると、有機化合物層362a、有機化合物層362bに電流が流れて熱が発生する。こうした熱や高電界の影響によって、有機化合物層の膜厚は不均一となり、有機化合物層が変形し、第1の導電層と第2の導電層とが接してしまい、結果第1の導電層と第2の導電層とが短絡する。よって、電圧印加前後での記憶素子の導電性が変化する。

有機化合物層362a、有機化合物層362bと、第1の導電層356との界面にそれぞれ存在する複数の絶縁物により、第1の導電層356から有機化合物層362a、有機化合物層362bへのキャリアのトンネル注入が可能になる。よって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、絶縁物を、導電層中に混入させた形態で設ける方が、導電層上に絶縁物単層を形成した形態で設けるより、物理的衝撃に強いため、膜剥がれや膜の形状不良などが作製工程中に生じにくい。よって、安定した状態で絶縁物を導電層と絶縁層との界面に設けることができるため、初期状態において導電層間で短絡(ショート)するような不良な素子の作製を防止でき、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

更に、絶縁物を導電層中に混入させた状態、あるいは絶縁物を導電層と複合化して形成した形態であるので、膜が損傷を受けにくく選択できる工程の自由度が拡大する。よって、記憶素子、記憶装置を作製する工程をより効率よく設定することができ、生産コストの削減、生産性の向上などが達成できる。

第1の導電層356を介して有機化合物層362a、有機化合物層362bと反対側に、整流性を有する素子を設けてもよい。例えば、第3の導電層及び半導体層で構成されるダイオードを第1の導電層356に接して設ければよい。なお、第2の導電層を介して有機化合物層と反対側に整流性を有する素子を設けてもよい。

また、素子形成層385と記憶素子部375とを含む基板と、アンテナとして機能する導電層393が設けられた基板396は、接着性を有する樹脂395により貼り合わされている。そして、素子形成層385と導電層393とは樹脂395中に含まれる導電性微粒子394を介して電気的に接続されている。また、銀ペースト、銅ペースト、カーボンペースト等の導電性接着剤や半田接合を行う方法を用いて素子形成層385と記憶素子部375を含む基板と、アンテナとして機能する導電層393が設けられた基板396とを貼り合わせてもよい。

このように、記憶装置およびアンテナを備えた半導体装置を形成することができる。また、本実施の形態では、基板上に薄膜トランジスタを形成して素子形成層を設けることもできるし、基板としてSi等の半導体基板を用いて、基板上に電界効果トランジスタを形成することによって素子形成層を設けてもよい。また、基板としてSOI基板を用いて、その上に素子形成層を設けてもよい。この場合、SOI基板はウェハの貼り合わせによる方法や酸素イオンをSi基板内に打ち込むことにより内部に絶縁層を形成するSIMOXと呼ばれる方法を用いて形成すればよい。

さらには、記憶素子部を、アンテナとして機能する導電層が設けられた基板に設けてもよい。またトランジスタに接続するセンサを設けてもよい。

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。また本実施の形態で作製した半導体装置を、基板より公知の剥離工程により剥離し、フレキシブルな基板上に接着することで、フレキシブルな基体上に設けることができ、可撓性を有する半導体装置を得ることができる。フレキシブルな基体とは、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどに相当する。フィルムは、熱圧着により、被処理体と加熱処理と加圧処理が行われるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により接着する。また、基体に接着層が設けられていてもよいし、接着層が設けられていなくてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。

本発明の記憶素子によって、記憶素子の書き込み電圧などの特性がばらつくことなく安定し、各素子において正常な書き込みを行うことが可能である。また、無機絶縁物と有機化合物との混合層のトンネル電流によってキャリア注入性が向上するため、絶縁層を厚膜化できる。よって記憶素子が通電前の初期状態でショートするという不良を防止できる。この結果、高信頼性な記憶装置及び半導体装置を、歩留まりよく提供することができる。

(実施の形態5)

本実施の形態では、上記構成を有する半導体装置において、データの読み込みまたは書き込みについて説明する。

上記構成を有する半導体装置へのデータの書き込みは、電気的作用を加えることにより行うことができる。電気的作用を加えることによりデータの書き込みを行う場合について説明する(図3参照。)。

電気的作用を加えることによりデータの書き込みを行う場合、ロウデコーダ724a、カラムデコーダ726a、セレクタ726cにより、1つのメモリセル721を選択し、その後、書き込み回路を用いて、当該メモリセル721にデータを書き込む。具体的には、所望する部分の有機化合物層752に選択的に大きい電圧を印加して大電流を流し、第1の導電層751bと第2の導電層753bの間をショート(短絡)させる。

ショートした部分は他の部分と比較すると電気抵抗が大幅に小さくなる。このように、電気的作用を加えることにより、2つの導電層間の電気抵抗が変化することを利用してデータの書き込みを行う。例えば、電気的作用を加えていない絶縁層を「0」のデータとする場合、「1」のデータを書き込む際は、所望の部分の絶縁層に選択的に大きい電圧を印加して大電流を流すことによって、ショートさせて電気抵抗を小さくする。

続いて、記憶素子からデータの読み出しを行う際の動作について説明する(図9参照。)。ここでは、読み出し回路726bは、抵抗素子746とセンスアンプ747を含む構成とする。但し、読み出し回路726bの構成は上記構成に制約されず、どのような構成を有していてもよい。

データの読み出しは、第1の導電層751bと第2の導電層753bの間に電圧を印加して、有機化合物層752の電気抵抗を読み取ることにより行う。例えば、上述したように、電気的作用を加えるによりデータの書き込みを行う場合、電気的作用を加えていないときの抵抗値Ra1と、電気的作用を加えて2つの導電膜間をショートしたときの抵抗値Rb1は、Ra1>Rb1を満たす。このような抵抗値の相違を電気的に読み取ることにより、データの読み出しを行う。

例えば、メモリセルアレイ722が含む複数のメモリセル721から、x列目y行目に配置されたメモリセル721のデータの読み出しを行う場合、まず、ロウデコーダ724a、カラムデコーダ726a、セレクタ726cにより、x列目のビット線Bxと、y行目のワード線Wyを選択する。そうすると、メモリセル721が含む絶縁層と、抵抗素子746とは、直列に接続された状態となる。このように、直列に接続された2つの抵抗素子の両端に電圧が印加されると、ノードαの電位は、有機化合物層752の抵抗値Ra又はRbに従って、抵抗分割された電位となる。そして、ノードαの電位は、センスアンプ47に供給され、当該センスアンプ747において、「0」と「1」のどちらの情報を有しているかを判別される。その後、センスアンプ747において判別された「0」と「1」の情報を含む信号が外部に供給される。

上記の方法によると、絶縁層の電気抵抗の状態は、抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。しかしながら、電流値を比較する方法でもよい。これは、例えば、絶縁層に電気的作用を加えていないときの電流値Ia1と、電気的作用を加えて2つの導電膜間をショートしたときの抵抗値Ib1は、Ia1<Ib1を満たすことを利用するものである。このように電流値の相違を電気的に読み取ることにより、データの読み出しを行ってもよい。

上記構成を有する記憶素子および当該記憶素子を備えた半導体装置は、不揮発性メモリであるため、データを保持するための電池を内蔵する必要がなく、小型、薄型、軽量の半導体装置の提供することができる。また、上記実施の形態で用いる絶縁性材料を絶縁層として用いることによって、データの書き込み(追記)は可能であるが、データの書き換えを行うことはできない。従って、偽造を防止し、セキュリティを確保した半導体装置を提供することができる。

なお、本実施の形態では、記憶回路の構成が単純であるパッシブマトリクス型の記憶素子および当該記憶素子を備えた半導体装置を例に挙げて説明を行ったが、アクティブマトリクス型の記憶回路を有する場合であっても、同様にデータの書き込みまたは読み出しを行うことができる。

ここで、アクティブマトリクス型の場合において、電気的作用により記憶素子部のデータを読み出す場合に関して図14に具体例を挙げて説明する。

図14は、記憶素子部に「0」のデータの書き込みを行った記憶素子部の電流電圧特性951と、「1」のデータの書き込みを行った記憶素子部電流電圧特性952と、抵抗素子246の電流電圧特性953を示しており、ここでは抵抗素子246としてトランジスタを用いた場合を示す。また、データを読み出す際の動作電圧として、第1の導電層243と第2の導電層245の間に3Vを印加した場合について説明する。

図14において、「0」のデータの書き込みが行われた記憶素子部を有するメモリセルでは、記憶素子部の電流電圧特性951とトランジスタの電流電圧特性953との交点954が動作点となり、このときのノードαの電位はV1(V)となる。ノードαの電位はセンスアンプ247に供給され、当該センスアンプ247において、上記メモリセルが記憶するデータは、「0」と判別される。

一方、「1」のデータの書き込みが行われた記憶素子部を有するメモリセルでは、記憶素子部の電流電圧特性952とトランジスタの電流電圧特性953との交点955が動作点となり、このときのノードαの電位はV2(V)(V1>V2)となる。ノードαの電位はセンスアンプ247に供給され、当該センスアンプ247において、上記メモリセルが記憶するデータは、「1」と判別される。

このように、記憶素子部241の抵抗値に従って、抵抗分割された電位を読み取ることによって、メモリセルに記憶されたデータを判別することができる。

なお、本実施の形態は、上記実施の形態に示した記憶素子および当該記憶素子を備えた半導体装置の構成と自由に組み合わせて行うことができる。

(実施の形態6)

本実施形態の半導体装置の構成について、図12を参照して説明する。図12に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の回路を制御する制御回路14、インターフェイス回路15、記憶回路16、データバス17、アンテナ(アンテナコイル)18、センサ21、センサ回路22を有する。

電源回路11は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種電源を生成する回路である。クロック発生回路12は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種クロック信号を生成する回路である。データ復調/変調回路13は、リーダライタ19と交信するデータを復調/変調する機能を有する。制御回路14は、記憶回路16を制御する機能を有する。アンテナ18は、電磁界或いは電波の送受信を行う機能を有する。リーダライタ19は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、半導体装置は上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウエアといった他の要素を追加した構成であってもよい。

記憶回路16は、一対の導電層間に絶縁層又は相変化層が挟まれた記憶素子を有することを特徴とする。なお、記憶回路16は、一対の導電層間に絶縁層又は相変化層が挟まれた記憶素子のみを有していてもよいし、他の構成の記憶回路を有していてもよい。他の構成の記憶回路とは、例えば、DRAM、SRAM、FeRAM、マスクROM、PROM、EPROM、EEPROM及びフラッシュメモリから選択される1つ又は複数に相当する。

センサ21は抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの半導体素子で形成される。センサ回路22はインピーダンス、リアクタンス、インダクタンス、電圧又は電流の変化を検出し、アナログ/デジタル変換(A/D変換)して制御回路14に信号を出力する。

(実施の形態7)

本発明によりプロセッサチップ(無線チップ、無線プロセッサ、無線メモリ、無線タグともよぶ)として機能する半導体装置を形成することができる。本発明の半導体装置の用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの(金券)、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指し、プロセッサチップ90を設けることができる(図13(A)参照)。証書類とは、運転免許証、住民票等を指し、プロセッサチップ91を設けることができる(図13(B)参照)。身の回り品とは、鞄、眼鏡等を指し、プロセッサチップ97を設けることができる(図13(C)参照)。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指し、プロセッサチップ93を設けることができる(図13(D)参照)。書籍類とは、書物、本等を指し、プロセッサチップ94を設けることができる(図13(E)参照)。記録媒体とは、DVDソフト、ビデオテープ等を指、プロセッサチップ95を設けることができる(図13(F)参照)。乗物類とは、自転車等の車両、船舶等を指し、プロセッサチップ96を設けることができる(図13(G)参照)。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置(テレビ受像機、薄型テレビ受像機)、携帯電話等を指す。

本発明の半導体装置は、プリント基板に実装したり、表面に貼ったり、埋め込んだりして、物品に固定される。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりして、各物品に固定される。本発明の半導体装置は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明の半導体装置を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品システム等のシステムの効率化を図ることができる。

次に、本発明の半導体装置を実装した電子機器の一態様について図面を参照して説明する。ここで例示する電子機器は携帯電話機であり、筐体2700、2706、パネル2701、ハウジング2702、プリント配線基板2703、操作ボタン2704、バッテリ2705を有する(図12(B)参照)。パネル2701はハウジング2702に脱着自在に組み込まれ、ハウジング2702はプリント配線基板2703に嵌着される。ハウジング2702はパネル2701が組み込まれる電子機器に合わせて、形状や寸法が適宜変更される。プリント配線基板2703には、パッケージングされた複数の半導体装置が実装されており、このうちの1つとして、本発明の半導体装置を用いることができる。プリント配線基板2703に実装される複数の半導体装置は、コントローラ、中央処理ユニット(CPU、Central Processing Unit)、メモリ、電源回路、音声処理回路、送受信回路等のいずれかの機能を有する。

パネル2701は、接続フィルム2708を介して、プリント配線基板2703と組合わされる。上記のパネル2701、ハウジング2702、プリント配線基板2703は、操作ボタン2704やバッテリ2705と共に、筐体2700、2706の内部に収納される。パネル2701が含む画素領域2709は、筐体2700に設けられた開口窓から視認できるように配置されている。

上記の通り、本発明の半導体装置は、小型、薄型、軽量であることを特徴としており、上記特徴により、電子機器の筐体2700、2706内部の限られた空間を有効に利用することができる。

また、本発明の半導体装置は、一対の導電層間に絶縁層が挟まれた単純な構造の記憶素子を有するため、安価な半導体装置を用いた電子機器を提供することができる。また、本発明の半導体装置は高集積化が容易なため、大容量の記憶回路を有する半導体装置を用いた電子機器を提供することができる。

また、本発明の半導体装置が有する記憶装置は、電気的作用によりデータの書き込みを行うものであり、不揮発性であって、データの追記が可能であることを特徴とする。上記特徴により、書き換えによる偽造を防止することができ、新たなデータを追加して書き込むことができる。従って、高機能化と高付加価値化を実現した半導体装置を用いた電子機器を提供することができる。

なお、筐体2700、2706は、携帯電話機の外観形状を一例として示したものであり、本実施の形態に係る電子機器は、その機能や用途に応じて様々な態様に変容しうる。

(実施の形態8)

本実施の形態では、上記構成を有する半導体装置において、データの読み込みまたは書き込みについて説明する。

図18に示したのは本発明の半導体装置が有する一構成例であり、メモリセル1721がマトリクス状に設けられたメモリセルアレイ1722、読み出し回路及び書き込み回路を有する回路1726、デコーダ1724、デコーダ1723を有している。なお、ここで示す記憶装置1716の構成はあくまで一例であり、センスアンプ、出力回路、バッファ、外部とのやりとりを行うインターフェイス等の他の回路を有していてもよい。

メモリセル1721は、ビット線Bx(1≦x≦m)に接続される第1の導電層と、ワード線Wy(1≦y≦n)に接続される第2の導電層と、絶縁層とを有する。絶縁層は、第1の導電層と第2の導電層の間に単層または積層して設けられている。

まず、パッシブマトリクス型の記憶装置において記憶素子にデータの書き込みを行う際の動作について図18、図19を用いて説明する。データの書き込みは、光学的作用又は電気的作用により行うが、まず、電気的作用によりデータの書き込みを行う場合について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化させた状態を「1」とする。

メモリセル1721にデータ「1」を書き込む場合、まず、デコーダ1723、1724およびセレクタ1725によってメモリセル1721を選択する。具体的には、デコーダ1724によって、メモリセル1721に接続されるワード線W3に所定の電圧V2を印加する。また、デコーダ1723とセレクタ1725によって、メモリセル1721に接続されるビット線B3を回路1726に接続する。そして、回路1726からビット線B3へ書き込み電圧V1を出力する。こうして、メモリセル1721を構成する第1の導電層と第2の導電層の間には電位(電圧)Vw=V1−V2を印加する。電位Vwを適切に選ぶことで、当該導電層間に設けられた絶縁層を物理的もしくは電気的変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の導電層と第2の導電層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよい。例えば、(V1、V2)=(0V、5〜15V)、あるいは(3〜5V、−12〜−2V)の範囲から適宜選べば良い。電位Vwは5〜15V、あるいは−5〜−15Vとすればよい。

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。例えば、非選択のワード線および非選択のビット線を浮遊状態とすればよい。メモリセルを構成する第1の導電層と第2の導電層の間は、ダイオード特性など、選択性を確保できる特性を有する必要がある。

一方、メモリセル1721にデータ「0」を書き込む場合は、メモリセル1721には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ1723、1724およびセレクタ1725によってメモリセル1721を選択するが、回路1726からビット線B3への出力電位を、選択されたワード線W3の電位あるいは非選択ワード線の電位と同程度とし、メモリセル1721を構成する第1の導電層と第2の導電層の間に、メモリセル1721の電気特性を変化させない程度の電圧(例えばー5〜5V)を印加すればよい。

次に、光学的作用によりデータの書き込みを行う場合について説明する。この場合、第2の導電層はレーザ光を透過させる必要がある。透光性を有する導電層側から、絶縁層にレーザ光を照射することにより行う。ここでは、所望の部分の絶縁層に選択的にレーザ光を照射して絶縁層を破壊する。破壊された絶縁層は、絶縁化するため、他の部分と比較すると電気抵抗が大幅に大きくなる。このように、レーザ光の照射により、絶縁層を挟んで設けられた2つの導電膜間の電気抵抗が変化することを利用してデータの書き込みを行う。例えば、レーザ光を照射していない絶縁層を「0」のデータとする場合、「1」のデータを書き込む際は、所望の部分の絶縁層に選択的にレーザ光を照射して破壊することによって電気抵抗を大きくする。

また、絶縁層として、光を吸収することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いた場合、レーザ光を照射すると、照射された部分だけが導電性が増加し、未照射の部分は導電性を有しない。そのため、所望の部分の絶縁層に選択的にレーザ光を照射することにより、絶縁層の電気抵抗が変化することを利用してデータの書き込みを行う。例えば、レーザ光を照射していない絶縁層を「0」のデータとする場合、「1」のデータを書き込む際は、所望の部分の絶縁層に選択的にレーザ光を照射して導電性を増加させる。

レーザ光の照射によりデータの書き込みを行う本発明の構成は、記憶装置を簡単に大量に作製することができる。従って、安価な記憶装置及び半導体装置を提供することができる。

続いて、パッシブマトリクス型の記憶装置において、記憶素子からデータの読み出しを行う際の動作について説明する(図18参照)。データの読み出しは、メモリセルを構成する第1の導電層と第2の導電層の間の電気特性が、データ「0」を有するメモリセルとデータ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する第1の導電層と第2の導電層の間の実効的な電気抵抗(以下、単にメモリセルの電気抵抗と呼ぶ)が、読み出し電圧においてR0、データ「1」を有するメモリセルの電気抵抗を、読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<<R0とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図18(B)に示す抵抗素子1746と差動増幅器1747を用いた回路1726を考えることができる。抵抗素子1746は抵抗値Rrを有し、R1<Rr<R0であるとする。抵抗素子1746の代わりにトランジスタ1748を用いても良いし、差動増幅器の代わりにクロックドインバータ1749を用いることも可能である(図18(C))。クロックドインバータ1749には、読み出しを行うときにHi、行わないときにLoとなる、信号φ又は反転信号φが入力される。勿論、回路構成は図18に限定されない。

メモリセル1721からデータの読み出しを行う場合、まず、デコーダ1723、1724およびセレクタ1725によってメモリセル1721を選択する。具体的には、デコーダ1724によって、メモリセル1721に接続されるワード線Wyに所定の電圧Vyを印加する。また、デコーダ1723とセレクタ1725によって、メモリセル1721に接続されるビット線Bxを回路1726の端子Pに接続する。その結果、端子Pの電位Vpは、抵抗素子1746(抵抗値Rr)とメモリセル1721(抵抗値R0もしくはR1)による抵抗分割によって決定される値となる。従って、メモリセル1721がデータ「0」を有する場合には、Vp0=Vy+(V0−Vy)×R0/(R0+Rr)となる。また、メモリセル1721がデータ「1」を有する場合には、Vp1=Vy+(V0−Vy)×R1/(R1+Rr)となる。その結果、図18(B)では、VrefをVp0とVp1の間となるように選択することで、図18(C)では、クロックドインバータの変化点をVp0とVp1の間となるように選択することで、出力電位Voutとして、データ「0」/「1」に応じて、Lo/Hi(もしくはHi/Lo)が出力され、読み出しを行うことができる。

例えば、差動増幅器をVdd=3Vで動作させ、Vy=0V、V0=3V、Vref=1.5Vとする。仮に、R0/Rr=Rr/R1=9とすると、メモリセルのデータが「0」の場合、Vp0=2.7VとなりVoutはHiが出力され、メモリセルのデータが「1」の場合、Vp1=0.3VとなりVoutはLoが出力される。こうして、メモリセルの読み出しを行うことができる。

上記の方法によると、絶縁層の電気抵抗の状態は、抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

次に、アクティブマトリクス型の記憶装置において記憶素子にデータの書き込みを行うときの動作について説明する(図19参照。)。

図19に示したのは本実施の形態で示す記憶装置の一構成例であり、メモリセル1231がマトリクス状に設けられたメモリセルアレイ1232、回路1226、デコーダ1224、デコーダ1223を有している。回路1226は読み出し回路及び書き込み回路を有している。なお、ここで示す記憶装置1217の構成はあくまで一例であり、センスアンプ、出力回路、バッファ、外部とのやりとりを行うインターフェイス等の他の回路を有していてもよい。

メモリセル1231は、ビット線Bx(1≦x≦m)に接続する第1の配線と、ワード線Wy(1≦y≦n)に接続する第2の配線と、トランジスタ1210aと、記憶素子1215bとを有する。記憶素子1215bは、一対の導電層の間に、絶縁層が挟まれた構造を有する。トランジスタのゲート電極はワード線と接続され、ソース電極もしくはドレイン電極のいずれか一方はビット線と接続され、残る一方は記憶素子が有する2端子の一方と接続される。記憶素子の残る1端子は共通電極(電位Vcom)と接続される。

まず、電気的作用によりデータの書き込みを行うときの動作について説明する。なお、書き込みはメモリセルの電気特性を変化させることで行うが、メモリセルの初期状態(電気的作用を加えていない状態)をデータ「0」、電気特性を変化させた状態を「1」とする。

ここでは、n行m列目のメモリセル1231にデータを書き込む場合について説明する。メモリセル1231にデータ「1」を書き込む場合、まず、デコーダ1223、1224およびセレクタ1225によってメモリセル1231を選択する。具体的には、デコーダ1224によって、メモリセル1231に接続されるワード線Wnに所定の電圧V22を印加する。また、デコーダ1223とセレクタ1225によって、メモリセル1231に接続されるビット線Bmを読み出し回路及び書き込み回路を有する回路1226に接続する。そして、回路1226からビット線B3へ書き込み電圧V21を出力する。

こうして、メモリセルを構成するトランジスタ1210aをオン状態とし、記憶素子1215bに、ビット線を電気的に接続し、おおむねVw=VcomーV21の電位(電圧)を印加する。なお、記憶素子1215bの一方の電極は電位Vcomの共通電極に接続されている。電位Vwを適切に選ぶことで、当該導電層間に設けられた絶縁層を物理的もしくは電気的変化させ、データ「1」の書き込みを行う。具体的には、読み出し動作電圧において、データ「1」の状態の第1の導電層と第2の導電層の間の電気抵抗が、データ「0」の状態と比して、大幅に小さくなるように変化させるとよく、単に短絡(ショート)させてもよい。なお、電位は、(V21、V22、Vcom)=(5〜15V、5〜15V、0V)、あるいは(−12〜0V、−12〜0V、3〜5V)の範囲から適宜選べば良い。電位Vwは5〜15V、あるいは−5〜−15Vとすればよい。

なお、非選択のワード線および非選択のビット線には、接続されるメモリセルにデータ「1」が書き込まれないよう制御する。具体的には、非選択のワード線には接続されるメモリセルのトランジスタをオフ状態とする電位(例えば0V)を印加し、非選択のビット線は浮遊状態とするか、Vcomと同程度の電位を印加するとよい。

一方、メモリセル1231にデータ「0」を書き込む場合は、メモリセル1231には電気的作用を加えなければよい。回路動作上は、例えば、「1」を書き込む場合と同様に、デコーダ1223、1224およびセレクタ1225によってメモリセル1231を選択するが、回路1226からビット線B3への出力電位をVcomと同程度とするか、ビット線B3を浮遊状態とする。その結果、記憶素子1215bには、小さい電位(例えば−5〜5V)が印加されるか、電圧(電位)が印加されないため、電気特性が変化せず、データ「0」書き込みが実現される。

続いて、光学的作用によりデータの書き込みを行う場合について説明する。この場合、レーザ照射装置により、透光性を有する導電層側から、絶縁層に対して、レーザ光を照射することにより行う。レーザ照射装置はパッシブマトリクス型の記憶装置において、図8を用いて説明したものと同様のものを用いればよい。

絶縁層として、有機化合物材料を用いた場合、レーザ光の照射により、絶縁層が酸化又は炭化して絶縁化する。そうすると、レーザ光が照射された記憶素子の抵抗値は増加し、レーザ光が照射されない記憶素子の抵抗値は変化しない。また、光酸発生剤をドープした共役高分子材料を用いた場合、レーザ光の照射により、絶縁層に導電性が与えられる。つまり、レーザ光が照射された記憶素子には導電性が与えられ、レーザ光が照射されない記憶素子には導電性が与えられない。

次に、電気的作用により、データの読み出しを行う際の動作について説明する。ここでは、回路1226は、抵抗素子1246と差動増幅器1247を含む構成とする。但し、回路1226の構成は上記構成に制約されず、どのような構成を有していてもよい。

次に、アクティブマトリクス型の記憶装置において電気的作用により、データの読み出しを行う際の動作について説明する。データの読み出しは、記憶素子1215bの電気特性が、データ「0」を有するメモリセルとデータ「1」を有するメモリセルとで異なることを利用して行う。例えば、データ「0」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR0、データ「1」を有するメモリセルを構成する記憶素子の電気抵抗が読み出し電圧においてR1とし、電気抵抗の差を利用して読み出す方法を説明する。なお、R1<<R0とする。読み出し/書き込み回路は、読み出し部分の構成として、例えば、図19(B)に示す抵抗素子1246と差動増幅器1247を用いた回路1226を考えることができる。抵抗素子は抵抗値Rrを有し、R1<Rr<R0であるとする。抵抗素子1246の代わりに、トランジスタ1249を用いても良いし、差動増幅器の代わりにクロックドインバータ1248を用いることも可能である(図19(C))。勿論、回路構成は図19に限定されない。

x行y列目メモリセル1231からデータの読み出しを行う場合、まず、デコーダ1223、1224およびセレクタ1225によってメモリセル1231を選択する。具体的には、デコーダ1224によって、メモリセル1231に接続されるワード線Wyに所定の電圧V24を印加し、トランジスタ1210aをオン状態にする。また、デコーダ1223とセレクタ1225によって、メモリセル1231に接続されるビット線Bxを回路1226の端子Pに接続する。その結果、端子Pの電位Vpは、VcomとV0の抵抗素子1246(抵抗値Rr)と記憶素子1215b(抵抗値R0もしくはR1)による抵抗分割によって決定される値となる。従って、メモリセル1231がデータ「0」を有する場合には、Vp0=Vcom+(V0−Vcom)×R0/(R0+Rr)となる。また、メモリセル1231がデータ「1」を有する場合には、Vp1=Vcom+(V0−Vcom)×R1/(R1+Rr)となる。その結果、図19(B)では、VrefをVp0とVp1の間となるように選択することで、図19(C)では、クロックドインバータの変化点をVp0とVp1の間となるように選択することで、出力電位Voutが、データ「0」/「1」に応じて、Lo/Hi(もしくはHi/Lo)が出力され、読み出しを行うことができる。

例えば、差動増幅器をVdd=3Vで動作させ、Vcom=0V、V0=3V、Vref=1.5Vとする。仮に、R0/Rr=Rr/R1=9とし、トランジスタ1210aのオン抵抗を無視できるとすると、メモリセルのデータが「0」の場合、Vp0=2.7VとなりVoutはHiが出力され、メモリセルのデータが「1」の場合、Vp1=0.3VとなりVoutはLoが出力される。こうして、メモリセルの読み出しを行うことができる。

上記の方法によると、記憶素子1215bの抵抗値の相違と抵抗分割を利用して、電圧値で読み取っている。勿論、読み出し方法は、この方法に限定されない。例えば、電気抵抗の差を利用する以外に、電流値の差を利用して読み出しても構わない。また、メモリセルの電気特性が、データ「0」と「1」とで、しきい値電圧が異なるダイオード特性を有する場合には、しきい値電圧の差を利用して読み出しても構わない。

上記構成を有する記憶素子および当該記憶素子を備えた記憶装置は、不揮発性メモリであるため、データを保持するための電池を内蔵する必要がなく、小型、薄型、軽量の記憶装置及び半導体装置の提供することができる。また、上記実施の形態で用いる絶縁性材料を絶縁層として用いることによって、データの書き込み(追記)は可能であるが、データの書き換えを行うことはできない。従って、偽造を防止し、セキュリティを確保した記憶装置及び半導体装置を提供することができる。

なお、本実施の形態は、上記実施の形態に示した記憶素子、当該記憶素子を備えた記憶装置及び半導体装置の構成と自由に組み合わせて行うことができる。