JP2007194337A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2007194337A JP2007194337A JP2006009882A JP2006009882A JP2007194337A JP 2007194337 A JP2007194337 A JP 2007194337A JP 2006009882 A JP2006009882 A JP 2006009882A JP 2006009882 A JP2006009882 A JP 2006009882A JP 2007194337 A JP2007194337 A JP 2007194337A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor substrate

- main surface

- epitaxial film

- transistor

- film formation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

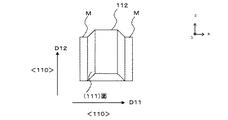

【解決手段】エピタキシャル成膜層112において半導体基板11の主面である(100)面よりも、キャリア移動度として正孔移動度が大きいファセット面である(111)面を含む領域が、チャネル領域21cになるように、p型MOSトランジスタ21を形成する。

【選択図】図1

Description

本発明にかかる実施形態1について説明する。

本発明にかかる実施形態2について説明する。

本発明にかかる実施形態3について説明する。

11,11a…半導体基板(半導体基板)、

21,221,321…p型MOSトランジスタ(トランジスタ,p型トランジスタ)、

31,231,331…n型MOSトランジスタ(トランジスタ,n型トランジスタ)、

111…素子分離層、

112,212,312…エピタキシャル成膜層(エピタキシャル成膜層)、

21c,31c,221c,231c,321c,331c…チャネル領域(チャネル領域)、

21x,31x,221x,231x,321x,331x…ゲート絶縁膜、

21g,31g,221g,231g,321g,331g…ゲート電極、

21sd,31sd,221sd,231sd,321sd,331sd…ソース・ドレイン領域、

21s,31s,221s,231s,321s,331s…側壁スペーサー、

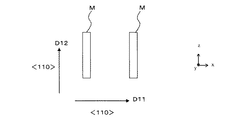

M…マスク層

Claims (22)

- トランジスタが設けられている半導体装置であって、

半導体基板と、

前記トランジスタにおいて前記半導体基板の主面よりもキャリア移動度が大きいファセット面が含まれるように、前記半導体基板の主面に成膜されているエピタキシャル成膜層と

を有し、

前記トランジスタは、前記エピタキシャル成膜層において前記半導体基板の主面よりもキャリア移動度が大きいファセット面を含む領域がチャネル領域として形成されている

半導体装置。 - 前記トランジスタとしてp型トランジスタが形成されており、

前記エピタキシャル成膜層は、前記キャリア移動度として正孔移動度が前記半導体基板の主面よりも大きなファセット面が形成されており、

前記p型トランジスタは、前記エピタキシャル成膜層において前記半導体基板の主面よりも正孔移動度が大きいファセット面を含む領域が、チャネル領域として形成されている

請求項1に記載の半導体装置。 - 前記トランジスタとしてn型トランジスタが形成されており、

前記n型トランジスタは、前記半導体基板の主面に対応する領域がチャネル領域として形成されている

請求項2に記載の半導体装置。 - 前記半導体基板は、前記主面が(100)面であり、

前記エピタキシャル成膜層は、前記半導体基板の(100)面よりも正孔移動度が大きい(111)面が、前記ファセット面として形成されており、

前記p型トランジスタは、前記エピタキシャル成膜層の前記(111)面を含むように、チャネル領域が形成されている

請求項3に記載の半導体装置。 - 前記半導体基板は、前記主面が(100)面であり、

前記エピタキシャル成膜層は、前記半導体基板の(100)面よりも正孔移動度が大きい(311)面が、前記ファセット面として形成されており、

前記p型トランジスタは、前記エピタキシャル成膜層の前記(311)面を含むように、チャネル領域が形成されている

請求項3に記載の半導体装置。 - 前記半導体基板は、前記主面が(100)面であり、

前記エピタキシャル成膜層は、前記半導体基板の(100)面よりも正孔移動度が大きい(110)面が、前記ファセット面として形成されており、

前記p型トランジスタは、前記エピタキシャル成膜層の前記(110)面を含むように、チャネル領域が形成されている

請求項3に記載の半導体装置。 - 前記トランジスタとしてn型トランジスタが形成されており、

前記エピタキシャル成膜層は、前記キャリア移動度として電子移動度が前記半導体基板の主面よりも大きな面が前記ファセット面として形成されており、

前記n型トランジスタは、前記エピタキシャル成膜層において前記半導体基板の主面よりも電子移動度が大きな前記ファセット面を含む領域が、チャネル領域として形成されている

請求項1に記載の半導体装置。 - 前記トランジスタとしてp型トランジスタが形成されており、

前記p型トランジスタは、前記半導体基板の主面に対応する領域がチャネル領域として形成されている

請求項7に記載の半導体装置。 - 前記半導体基板は、前記主面が(110)面であり、

前記エピタキシャル成膜層は、前記半導体基板の(110)面よりも電子移動度が大きい(100)面が、前記ファセット面として形成されており、

前記n型トランジスタは、前記エピタキシャル成膜層の前記(100)面を含むように、チャネル領域が形成されている

請求項8に記載の半導体装置。 - トランジスタを半導体基板の主面に設けるトランジスタ形成工程を含む半導体装置の製造方法であって、

前記トランジスタ形成工程にて形成される前記トランジスタにおいて前記半導体基板の主面よりもキャリア移動度が大きいファセット面が含まれるように、前記半導体基板の主面にエピタキシャル成膜層を成膜するエピタキシャル成膜層形成工程

を有し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層形成工程によって形成された前記エピタキシャル成膜層において前記半導体基板の主面よりもキャリア移動度が大きいファセット面を含む領域がチャネル領域になるように前記トランジスタを形成する

半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記キャリア移動度として正孔移動度が前記半導体基板の主面よりも大きなファセット面が含まれるように前記エピタキシャル成膜層を成膜し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層において前記半導体基板の主面よりも正孔移動度が大きいファセット面を含む領域をチャネル領域とするp型トランジスタを前記トランジスタとして形成する

請求項10に記載の半導体装置の製造方法。 - 前記トランジスタ形成工程においては、前記半導体基板の主面に対応する領域をチャネル領域とするn型トランジスタを前記トランジスタとして形成する

請求項11に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記主面が(100)面である前記半導体基板に、前記半導体基板の(100)面よりも正孔移動度が大きい(111)面が前記ファセット面として形成されるように前記エピタキシャル成膜層を成膜し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層の前記(111)面をチャネル領域が含むように前記p型トランジスタを形成する

請求項12に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記半導体基板の主面において第1の<110>方向に垂直であって、前記第1の<110>方向と異なった第2の<110>方向に沿って延在するように前記半導体基板の主面上にマスク層を形成した後に、前記半導体基板の主面上において前記マスク層が形成された周辺領域にてエピタキシャル成長を実施することによって、(111)面をファセット面として含むように前記エピタキシャル成膜層を形成する

請求項13に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記主面が(100)面である前記半導体基板に、前記半導体基板の(100)面よりも正孔移動度が大きい(311)面が前記ファセット面として形成されるように前記エピタキシャル成膜層を形成し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層の前記(311)面をチャネル領域が含むように前記p型トランジスタを形成する

請求項12に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記半導体基板の主面にて第1の<110>方向に垂直であって、前記第1の<110>方向と異なった第2の<110>方向に沿って延在するように前記半導体基板の主面上にマスク層を形成した後に、前記半導体基板の主面上において前記マスク層が形成された周辺領域にてエピタキシャル成長を実施することによって、(311)面をファセット面として含むように前記エピタキシャル成膜層を形成する

請求項15に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記主面が(100)面である前記半導体基板に、前記半導体基板の(100)面よりも正孔移動度が大きい(110)面が前記ファセット面として形成されるように前記エピタキシャル成膜層を形成し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層の前記(110)面をチャネル領域が含むように前記p型トランジスタを形成する

請求項12に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記半導体基板の主面において<100>方向に垂直であって<100>方向に沿って延在するように前記半導体基板の主面上にマスク層を形成した後に、前記半導体基板の主面上において前記マスク層が形成された周辺領域にてエピタキシャル成長を実施することによって、(110)面をファセット面として含むエピタキシャル成膜層を形成する

請求項15に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記キャリア移動度として電子移動度が前記半導体基板の主面よりも大きなファセット面が含まれるように前記エピタキシャル成膜層を形成し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層において前記半導体基板の主面よりも電子移動度が大きいファセット面を含む領域をチャネル領域とするn型トランジスタを前記トランジスタとして形成する

請求項10に記載の半導体装置の製造方法。 - 前記トランジスタ形成工程においては、前記半導体基板の主面に対応する領域をチャネル領域とするp型トランジスタを前記トランジスタとして形成する

請求項19に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記主面が(110)面である前記半導体基板に、前記半導体基板の(110)面よりも電子移動度が大きい(100)面が前記ファセット面として形成されるように前記エピタキシャル成膜層を形成し、

前記トランジスタ形成工程においては、前記エピタキシャル成膜層の前記(100)面をチャネル領域が含むように前記n型トランジスタを形成する

請求項20に記載の半導体装置の製造方法。 - 前記エピタキシャル成膜層形成工程においては、前記半導体基板の主面において<110>方向に垂直であって<100>方向に沿って延在するように前記半導体基板の主面上にマスク層を形成した後に、前記半導体基板の主面上において前記マスク層が形成された周辺領域にてエピタキシャル成長を実施することによって、(100)面をファセット面として含むように前記エピタキシャル成膜層を形成する

請求項21に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006009882A JP2007194337A (ja) | 2006-01-18 | 2006-01-18 | 半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006009882A JP2007194337A (ja) | 2006-01-18 | 2006-01-18 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007194337A true JP2007194337A (ja) | 2007-08-02 |

| JP2007194337A5 JP2007194337A5 (ja) | 2008-12-04 |

Family

ID=38449800

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006009882A Pending JP2007194337A (ja) | 2006-01-18 | 2006-01-18 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007194337A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009157040A1 (ja) * | 2008-06-25 | 2009-12-30 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP2010206097A (ja) * | 2009-03-05 | 2010-09-16 | Toshiba Corp | 半導体素子及び半導体装置 |

| JP2015512139A (ja) * | 2012-01-13 | 2015-04-23 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 基板上に第iii−v族層を堆積させる方法 |

| US9219077B2 (en) | 2011-03-31 | 2015-12-22 | Sony Corporation | Semiconductor device and fabrication method therefor |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002359293A (ja) * | 2001-05-31 | 2002-12-13 | Toshiba Corp | 半導体装置 |

| JP2005203798A (ja) * | 2004-01-17 | 2005-07-28 | Samsung Electronics Co Ltd | 少なくとも5面チャンネル型finfetトランジスタ及びその製造方法 |

-

2006

- 2006-01-18 JP JP2006009882A patent/JP2007194337A/ja active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002359293A (ja) * | 2001-05-31 | 2002-12-13 | Toshiba Corp | 半導体装置 |

| JP2005203798A (ja) * | 2004-01-17 | 2005-07-28 | Samsung Electronics Co Ltd | 少なくとも5面チャンネル型finfetトランジスタ及びその製造方法 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009157040A1 (ja) * | 2008-06-25 | 2009-12-30 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US8362530B2 (en) | 2008-06-25 | 2013-01-29 | Fujitsu Semiconductor Limited | Semiconductor device including MISFET and its manufacture method |

| JP5158197B2 (ja) * | 2008-06-25 | 2013-03-06 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| JP2010206097A (ja) * | 2009-03-05 | 2010-09-16 | Toshiba Corp | 半導体素子及び半導体装置 |

| US8013396B2 (en) | 2009-03-05 | 2011-09-06 | Kabushiki Kaisha Toshiba | Semiconductor component and semiconductor device |

| US9219077B2 (en) | 2011-03-31 | 2015-12-22 | Sony Corporation | Semiconductor device and fabrication method therefor |

| US9837534B2 (en) | 2011-03-31 | 2017-12-05 | Sony Corporation | Semiconductor device and fabrication method therefor |

| JP2015512139A (ja) * | 2012-01-13 | 2015-04-23 | アプライド マテリアルズ インコーポレイテッドApplied Materials,Incorporated | 基板上に第iii−v族層を堆積させる方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11011518B2 (en) | Semiconductor device and method of manufacturing the same | |

| KR100855977B1 (ko) | 반도체 소자 및 그 제조방법 | |

| JP4345774B2 (ja) | 半導体装置の製造方法 | |

| US7981750B2 (en) | Methods of fabrication of channel-stressed semiconductor devices | |

| JP5107680B2 (ja) | 半導体装置 | |

| JP4561419B2 (ja) | 半導体装置の製造方法 | |

| US20080169490A1 (en) | Semiconductor device and manufacturing method thereof | |

| KR20120047032A (ko) | 반도체 소자 및 이의 제조 방법 | |

| US20070278589A1 (en) | Semiconductor device and fabrication method thereof | |

| US6818938B1 (en) | MOS transistor and method of forming the transistor with a channel region in a layer of composite material | |

| US7391077B2 (en) | Vertical type semiconductor device | |

| JP5092754B2 (ja) | pチャネルMOSトランジスタおよび半導体装置 | |

| JP2007194337A (ja) | 半導体装置およびその製造方法 | |

| US20080105899A1 (en) | Semiconductor device with epitaxially grown layer and fabrication method | |

| CN100479120C (zh) | 金属氧化物半导体晶体管及其制造方法 | |

| US7557414B2 (en) | Semiconductor device and method for manufacturing the same | |

| US20070066023A1 (en) | Method to form a device on a soi substrate | |

| JP4706450B2 (ja) | 半導体装置およびその製造方法 | |

| JP2011199112A (ja) | 半導体装置およびその製造方法 | |

| JP5168140B2 (ja) | 応力印加半導体装置およびその製造方法 | |

| JP4590979B2 (ja) | 半導体装置及びその製造方法 | |

| CN105206576B (zh) | 用于形成嵌入式锗硅源/漏结构的方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081016 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081016 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100831 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120228 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120731 |