JP2007134635A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2007134635A JP2007134635A JP2005328652A JP2005328652A JP2007134635A JP 2007134635 A JP2007134635 A JP 2007134635A JP 2005328652 A JP2005328652 A JP 2005328652A JP 2005328652 A JP2005328652 A JP 2005328652A JP 2007134635 A JP2007134635 A JP 2007134635A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- layer

- substrate

- base layer

- semiconductor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

【課題】強度を高めて、熱ストレスなどによりクラックが入るのを抑制できるハンダバンプを有する半導体装置と、その製造方法を提供する。

【解決手段】電子回路が形成された半導体基板に、電子回路に電気的に接続され、半導体基板の表面から突出して下地層が形成されており、下地層の基板の表面から突出して形成された部分の表面に接合してハンダからなるバンプが形成されている構成とする。

【選択図】図1

【解決手段】電子回路が形成された半導体基板に、電子回路に電気的に接続され、半導体基板の表面から突出して下地層が形成されており、下地層の基板の表面から突出して形成された部分の表面に接合してハンダからなるバンプが形成されている構成とする。

【選択図】図1

Description

本発明は、半導体装置およびその製造方法に関し、特に、ハンダバンプを有する半導体装置およびその製造方法に関する。

デジタルビデオカメラ、デジタル携帯電話、あるいはノートパソコンなど、携帯用電子機器の小型化、薄型化、軽量化に対する要求は強くなる一方であり、これに応えるために近年のVLSIなどの半導体装置においては3年で7割の縮小化を実現してきた一方で、このような半導体装置をプリント配線基板上に実装した電子回路装置としても、実装基板(プリント配線基板)上の部品実装密度をいかに向上させるかが重要な課題として研究および開発がなされてきた。

例えば、半導体装置のパッケージ形態としては、DIP(Dual Inline Package )などのリード挿入型から表面実装型へと移行し、さらには半導体チップのパッド電極にハンダや金などからなるバンプ(突起電極)を設け、フェースダウンでバンプを介して配線基板に接続するフリップチップ実装法が開発された。

上記のようにフリップチップで実装するような半導体装置の小型のパッケージング方法としてCSP(チップサイズパッケージ)が開発されている。

さらにリアルチップサイズのパッケージング方法として、ウェーハレベルのCSP(WL−CSP)が提案されている。ここでは、インターポーザ基板を用いたCSPの代わりに、LSIの外部端子がアクティブエリア上でエリアアレイ状に再配線され、各配線にハンダなどのバンプが形成されている。

上記のようなハンダバンプが形成されてフリップチップで実装するタイプの半導体装置として、例えば、特許文献1に上記のSiP形態の半導体装置が開示されている。

さらにリアルチップサイズのパッケージング方法として、ウェーハレベルのCSP(WL−CSP)が提案されている。ここでは、インターポーザ基板を用いたCSPの代わりに、LSIの外部端子がアクティブエリア上でエリアアレイ状に再配線され、各配線にハンダなどのバンプが形成されている。

上記のようなハンダバンプが形成されてフリップチップで実装するタイプの半導体装置として、例えば、特許文献1に上記のSiP形態の半導体装置が開示されている。

従来技術においては、上記のハンダバンプは、例えば以下のようにして形成される。

まず、図6(a)に示すように、電子回路などの素子が形成された半導体基板100の表面にAlなどからなるパッド電極101が形成されており、化学気相成長(CVD)法などにより全面に窒化シリコンを堆積して保護膜102を形成し、パッド電極101部分を開口する開口部102aをパターン形成する。

まず、図6(a)に示すように、電子回路などの素子が形成された半導体基板100の表面にAlなどからなるパッド電極101が形成されており、化学気相成長(CVD)法などにより全面に窒化シリコンを堆積して保護膜102を形成し、パッド電極101部分を開口する開口部102aをパターン形成する。

次に、図6(b)に示すように、逆スッパタリング法により、開口部102aにおいて露出しているパッド電極101を被覆して全面にシード層となるTi層103を形成し、さらにその上層に同じくシード層となるCu層104aを形成する。

次に、図7(a)に示すように、Cu層104aを被覆して全面に感光性ドライフィルムを貼付け、フォトリソグラフィ工程によりバンプ形成領域を開口するパターンで露光及び現像処理を行い、マスク層105をパターン形成する。

次に、図7(b)に示すように、マスク層105の開口部内において、Ti層103及びCu層104aを一方の電極とする電解メッキ処理により、Cu層104aの上層にCuを堆積させ、厚膜化したCu層104とする。

さらに、電解メッキ処理により、Cu層104の上層にNi層106を形成し、さらにAu層107を形成する。

さらに、電解メッキ処理により、Cu層104の上層にNi層106を形成し、さらにAu層107を形成する。

次に、図8(a)に示すように、溶剤またはアッシング処理により、マスク層105を剥離除去する。

次に、図8(b)に示すように、Au層107をマスクとするエッチング処理により、下層のCu層104及びTi層103を順にAu層107と同じパターンに加工し、洗浄処理を行う。

次に、図9(a)に示すように、スピンコート法によりAu層107の表面を被覆するような膜厚で、ポリイミド(PI)やベンゾシクロブテン(BCB)などの感光性の絶縁樹脂を全面に塗布し、プリベーク処理を行い、バンプ形成領域を開口するパターンで露光及び現像処理を行ってAu層107を露出させ、さらにポストベーク処理及びアッシング処理を行う。これにより、バンプ形成領域において開口するパターンの絶縁樹脂層108を形成する。絶縁樹脂層108の開口部はAu層107の上面よりも狭くなるようなレイアウトとする。

次に、図9(b)に示すように、絶縁樹脂層108に開口した開口部内にフラックスを印刷し、さらにハンダボールを供給する。次に、リフロー処理を行うことで、ハンダボールを一度溶融させ、Au層107の表面とハンダボール表面を接合させて、ハンダバンプ109を形成する。この後、フラックスを除去するための洗浄処理を行う。

以上の方法により、ハンダバンプを形成できる。

以上の方法により、ハンダバンプを形成できる。

しかしながら、上記の従来のハンダバンプは、絶縁樹脂層108の開口部はAu層107の上面よりも狭くなるようなレイアウトであり、ハンダバンプを形成するランドが絶縁層で絞り込まれるような構造となっているため、図9(b)に示すように、絶縁樹脂層との境界部分109rでハンダが括れた状態になり、このバンプが形成されたデバイスを実装基板に実装したとき、この括れた境界部分109rの強度が不十分となり、熱ストレスの影響でクラックが入ってしまう不具合が生じやすくなっていた。

特開2005−175317号公報

本発明の目的は、強度を高めて、熱ストレスなどによりクラックが入るのを抑制できるハンダバンプを有する半導体装置と、その製造方法を提供することである。

上記の課題を解決するため、本発明の半導体装置は、電子回路が形成された半導体基板と、前記電子回路に電気的に接続され、前記半導体基板の表面から突出して形成された下地層と、前記下地層の前記基板の表面から突出して形成された部分の表面に接合して形成されたハンダからなるバンプとを有する。

上記の本発明の半導体装置は、電子回路が形成された半導体基板に、電子回路に電気的に接続され、半導体基板の表面から突出して下地層が形成されており、下地層の基板の表面から突出して形成された部分の表面に接合してハンダからなるバンプが形成されている。

また、上記の課題を解決するため、本発明の半導体装置の製造方法は、電子回路が形成された半導体基板に、前記電子回路に電気的に接続して、前記半導体基板の表面から突出するように下地層を形成する工程と、前記下地層の前記基板の表面から突出して形成された部分の表面に接合して、ハンダからなるバンプを形成する工程とを有する。

上記の本発明の半導体装置の製造方法は、電子回路が形成された半導体基板に、電子回路に電気的に接続して、半導体基板の表面から突出するように下地層を形成する。

次に、下地層の基板の表面から突出して形成された部分の表面に接合して、ハンダからなるバンプを形成する。

次に、下地層の基板の表面から突出して形成された部分の表面に接合して、ハンダからなるバンプを形成する。

本発明の半導体装置は、ハンダバンプの強度が高められており、熱ストレスなどによりクラックが入るのを抑制できる。

本発明の半導体装置の製造方法は、ハンダバンプの強度が高められ、熱ストレスなどによりクラックが入るのを抑制できる半導体装置を製造することができる。

以下に、本発明の半導体装置及びその製造方法の実施の形態について、図面を参照して説明する。

第1実施形態

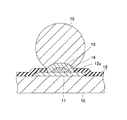

図1は本実施形態に係る半導体装置のバンプ部分の模式断面図である。

例えば、電子回路が形成された半導体基板10に、電子回路に電気的に接続されたAlなどからなるパッド電極11が形成されており、半導体基板10上にパッド電極11の一部を開口するパターンで開口部12aが形成された窒化シリコンなどからなる保護膜12が形成されている。

図1は本実施形態に係る半導体装置のバンプ部分の模式断面図である。

例えば、電子回路が形成された半導体基板10に、電子回路に電気的に接続されたAlなどからなるパッド電極11が形成されており、半導体基板10上にパッド電極11の一部を開口するパターンで開口部12aが形成された窒化シリコンなどからなる保護膜12が形成されている。

上記の開口部12aの中央部において、パッド電極11の上層にAgナノペーストを固化してなる凸状層13が形成されており、凸状層13の上層において開口部12aの縁を外周とするパターンで、Niなどからなる下地層14が保護膜12の表面から突出して形成されている。

さらに、下地層14の保護膜12の表面から突出して形成された部分の表面に接合してハンダからなるバンプ15が形成されている。

さらに、下地層14の保護膜12の表面から突出して形成された部分の表面に接合してハンダからなるバンプ15が形成されている。

本実施形態においては、凸状層13の表面形状が頂部から外周部までなめらかに繋がる曲面を有しており、この凸状層13の表面形状を反映して、下地層14の保護膜12の表面から突出して形成された部分の表面形状が、頂部から外周部までなめらかに繋がる曲面を有している。

上記の構造を有するハンダバンプにおいて、バンプ15が下地層14の頂部から外周部までなめらかに繋がる曲面の全体において接合することにより、下地層14とバンプ15との界面とのせん断応力を大きくできるので、これにより下地層14とバンプ15の接合強度を高めることができる。

また、図9(b)に示す従来例のような、絶縁樹脂層でハンダバンプの下地の層との接合面積を規定してハンダバンプのネックが括れた構造とはならず、球状になることから、ヒートサイクルなどの熱ストレスに対して強い構造となっている。

上記のように、本実施形態に係る半導体装置のハンダバンプは、強度を高めて、熱ストレスなどによりクラックが入るのを抑制できる。

また、図9(b)に示す従来例のような、絶縁樹脂層でハンダバンプの下地の層との接合面積を規定してハンダバンプのネックが括れた構造とはならず、球状になることから、ヒートサイクルなどの熱ストレスに対して強い構造となっている。

上記のように、本実施形態に係る半導体装置のハンダバンプは、強度を高めて、熱ストレスなどによりクラックが入るのを抑制できる。

次に、本実施形態に係る半導体装置の製造方法について説明する。

まず、図2(a)に示すように、例えば、電子回路が形成された半導体基板10に、電子回路に電気的に接続されたAlなどからなるパッド電極11を形成し、さらに例えばCVD法により窒化シリコンなどを堆積して、半導体基板10上にパッド電極11の一部を開口するパターンで開口部12aを形成し、保護膜12を形成する。

まず、図2(a)に示すように、例えば、電子回路が形成された半導体基板10に、電子回路に電気的に接続されたAlなどからなるパッド電極11を形成し、さらに例えばCVD法により窒化シリコンなどを堆積して、半導体基板10上にパッド電極11の一部を開口するパターンで開口部12aを形成し、保護膜12を形成する。

次に、図2(b)に示すように、例えば、開口部12aの中央部の開口部12aより狭い領域において、パッド電極11の上層に、Agナノペーストを印刷し、さらに加熱して固化し、凸状層13を形成する。

本実施形態においては、凸状層13の表面形状が、頂部から外周部までなめらかに繋がる曲面を有するように形成する。

本実施形態においては、凸状層13の表面形状が、頂部から外周部までなめらかに繋がる曲面を有するように形成する。

次に、図3(a)に示すように、例えば、ジンケート処理を行った後、さらにNiの無電解メッキ処理を行い、凸状層13の上層において開口部12aの縁を外周とするパターンで、Niなどからなる下地層14を保護膜12の表面から突出するようにして形成する。

ここでは、凸状層13の表面形状を反映して、下地層14の保護膜12の表面から突出して形成された部分の表面形状が、頂部から外周部までなめらかに繋がる曲面を有して形成される。

ここでは、凸状層13の表面形状を反映して、下地層14の保護膜12の表面から突出して形成された部分の表面形状が、頂部から外周部までなめらかに繋がる曲面を有して形成される。

次に、図3(b)に示すように、下地層14の保護膜12の表面から突出して形成された部分の表面に接合して、ハンダからなるバンプ15を形成する。

以上で図1に示す構成のハンダバンプを有する半導体装置を形成することができる。

以上で図1に示す構成のハンダバンプを有する半導体装置を形成することができる。

上記のようにして形成された半導体装置の下地層は、逆スパッタリング法により形成される従来のシードメタル層を介した構造と比較して、デバイスの端子電極との金属同士の接着が強く、且つ、下地層とハンダバンプとの界面のせん断応力が大きいことから、絶縁樹脂層で周辺部分を抑えるように補強する必要がなく、側面部分も露出した構造が取れる。

また、絶縁樹脂層でハンダバンプと下地層が接合する面積を規定した場合のように、ハンダボールのネックが括れたような形状になることもなく、実装基板に実装した際に、ヒートサイクル等の熱ストレスにも、非常に強い構造となっている。

また、絶縁層の必要もなく、材料費、加工費のコストダウンも可能になる。

また、絶縁層の必要もなく、材料費、加工費のコストダウンも可能になる。

上記のように、本実施形態の半導体装置の製造方法は、ハンダバンプの強度が高められ、熱ストレスなどによりクラックが入るのを抑制できる半導体装置を製造することができる。

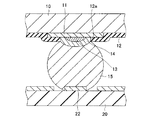

図4は、本実施形態のハンダバンプが形成された半導体装置を実装基板に実装したときのバンプ部分の模式断面図である。

実装基板は、実装基板本体20の表面に、配線21及び電極22などがパターン形成されている。

上記の電極とハンダバンプ15が接合するようにして、本実施形態の半導体装置がフリップチップで実装されている。

実装基板は、実装基板本体20の表面に、配線21及び電極22などがパターン形成されている。

上記の電極とハンダバンプ15が接合するようにして、本実施形態の半導体装置がフリップチップで実装されている。

上記のように、本実施形態の半導体装置は、ハンダバンプの強度が高められ、上記のようにして実装基板に実装されても、熱ストレスなどによりクラックが入るのを抑制できる。

(実施例)

ここで、従来例と本実施形態に係る半導体装置として、□3.0mmの大きさであって0.5mmピッチのハンダバンプが36ピン形成された構成の半導体装置を、それぞれWL−CSPで形成した。

得られた半導体装置を実装基盤(FR−4)に実装し、実装信頼性を調べた。

ここで、従来例と本実施形態に係る半導体装置として、□3.0mmの大きさであって0.5mmピッチのハンダバンプが36ピン形成された構成の半導体装置を、それぞれWL−CSPで形成した。

得られた半導体装置を実装基盤(FR−4)に実装し、実装信頼性を調べた。

(ヒートサイクル試験)

−25℃〜125℃の温度でのヒートサイクル試験、上記の従来例と本実施形態に係る半導体装置を実装した装置の、累積故障率1%となるまでのサイクル数を調べた。

従来例では300サイクルで達してしまったが、本実施形態では700サイクルまでかかり、2倍以上寿命が延びていることが分かった。

−25℃〜125℃の温度でのヒートサイクル試験、上記の従来例と本実施形態に係る半導体装置を実装した装置の、累積故障率1%となるまでのサイクル数を調べた。

従来例では300サイクルで達してしまったが、本実施形態では700サイクルまでかかり、2倍以上寿命が延びていることが分かった。

第2実施形態

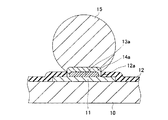

図5は本実施形態に係る半導体装置のバンプ部分の模式断面図である。

実質的に第1実施形態の半導体装置と同様であるが、下地層14aの基板(保護膜12)の表面から突出して形成された部分は、半導体基板10の表面に略平行な平坦な部分を有する上面と半導体基板10の表面に略垂直な外周面とを有している形状であることが異なる。

これは、凸状層13aの形状が半導体基板10の表面に略平行な平坦な部分を有する上面と半導体基板10の表面に略垂直な外周面とを有している形状となっており、この表面形状を反映するように、下地層14aが形成されていることによる。

図5は本実施形態に係る半導体装置のバンプ部分の模式断面図である。

実質的に第1実施形態の半導体装置と同様であるが、下地層14aの基板(保護膜12)の表面から突出して形成された部分は、半導体基板10の表面に略平行な平坦な部分を有する上面と半導体基板10の表面に略垂直な外周面とを有している形状であることが異なる。

これは、凸状層13aの形状が半導体基板10の表面に略平行な平坦な部分を有する上面と半導体基板10の表面に略垂直な外周面とを有している形状となっており、この表面形状を反映するように、下地層14aが形成されていることによる。

本実施形態の半導体装置も、第1実施形態と同様に、ハンダバンプの強度が高められており、熱ストレスなどによりクラックが入るのを抑制できる。

上記の本実施形態に係る半導体装置のハンダバンプは、以下の効果を享受できる。

(1)基板から突出した下地層を有することにより、下地層とハンダバンプの界面とのせん断応力を大きくでき、接合強度を上げることができる。

(2)下地層の頂部や側面などでハンダバンプと接合することにより、接着強度を上げることができる。

(3)ハンダバンプのネックが括れた形状になることがなく、高い接合信頼性を得ることができる。

(4)実装基板との高い接続信頼性を得ることができる。

(5)逆スパッタリング法によるシードメタル形成工程及び絶縁層形成工程を削除することができ、工程の短縮とコストダウンが実現できる。

(1)基板から突出した下地層を有することにより、下地層とハンダバンプの界面とのせん断応力を大きくでき、接合強度を上げることができる。

(2)下地層の頂部や側面などでハンダバンプと接合することにより、接着強度を上げることができる。

(3)ハンダバンプのネックが括れた形状になることがなく、高い接合信頼性を得ることができる。

(4)実装基板との高い接続信頼性を得ることができる。

(5)逆スパッタリング法によるシードメタル形成工程及び絶縁層形成工程を削除することができ、工程の短縮とコストダウンが実現できる。

本発明は上記の説明に限定されない。

例えば、バンプの下地層は、上記の層構成に限らず、Ni層以外の層などが積層した構成としてもよい。また下地層の表面形状に反映される凸状層は、所望の形状に形成できる限り、Agナノペースト以外の材料を用いてもよい。

その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

例えば、バンプの下地層は、上記の層構成に限らず、Ni層以外の層などが積層した構成としてもよい。また下地層の表面形状に反映される凸状層は、所望の形状に形成できる限り、Agナノペースト以外の材料を用いてもよい。

その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

本発明の半導体装置は、フリップチップ実装ができるようにバンプを有する半導体装置に適用できる。

また、本発明の半導体装置の製造方法は、フリップチップ実装ができるようにバンプを有する半導体装置を製造するのに適用できる。

また、本発明の半導体装置の製造方法は、フリップチップ実装ができるようにバンプを有する半導体装置を製造するのに適用できる。

10…半導体基板、11…パッド電極、12…保護膜、12a…開口部、13,13a…凸状層、14,14a…下地層、15…バンプ、20…実装基板本体、21…配線、22…電極、100…半導体基板、101…パッド電極、102…保護膜、102a…開口部、103…Ti層、104,104a…Cu層、105…マスク層、106…Ni層、107…Au層、108…絶縁樹脂層、109…バンプ

Claims (10)

- 電子回路が形成された半導体基板と、

前記電子回路に電気的に接続され、前記半導体基板の表面から突出して形成された下地層と、

前記下地層の前記基板の表面から突出して形成された部分の表面に接合して形成されたハンダからなるバンプと

を有する半導体装置。 - 前記下地層の下層に、前記下地層の表面形状の型となる凸状層が形成されている

請求項1に記載の半導体装置。 - 前記下地層の前記基板の表面から突出して形成された部分は、頂部から外周部までなめらかに繋がる曲面を有する

請求項1に記載の半導体装置。 - 前記下地層の前記基板の表面から突出して形成された部分は、前記半導体基板の表面に略平行な平坦な部分を有する上面と前記半導体基板の表面に略垂直な外周面とを有する

請求項1に記載の半導体装置。 - 前記半導体基板に前記電子回路に電気的に接続されたパッド電極が形成されており、

前記半導体基板上に前記パッド電極の一部を開口するパターンの保護膜が形成されており、

前記下地層は前記保護膜の表面から突出して形成されている

請求項1に記載の半導体装置。 - 電子回路が形成された半導体基板に、前記電子回路に電気的に接続して、前記半導体基板の表面から突出するように下地層を形成する工程と、

前記下地層の前記基板の表面から突出して形成された部分の表面に接合して、ハンダからなるバンプを形成する工程と

を有する半導体装置の製造方法。 - 前記下地層を形成する工程の前に、前記基板に、前記下地層の表面形状の型となる凸状層を形成する工程をさらに有し、

前記下地層を形成する工程において、前記凸状層の上層に前記凸状層の表面形状が前記下地層の表面形状に反映されるようにして、前記下地層を形成する

請求項6に記載の半導体装置の製造方法。 - 前記下地層を形成する工程において、前記下地層の前記基板の表面から突出して形成された部分が、頂部から外周部までなめらかに繋がる曲面を有する形状となるように、形成する

請求項6に記載の半導体装置の製造方法。 - 前記下地層を形成する工程において、前記下地層の前記基板の表面から突出して形成された部分が、前記半導体基板の表面に略平行な平坦な部分を有する上面と前記半導体基板の表面に略垂直な外周面とを有する形状となるように、形成する

請求項6に記載の半導体装置の製造方法。 - 前記下地層を形成する工程の前に、前記半導体基板に前記電子回路に電気的に接続してパッド電極を形成する工程と、前記半導体基板上に前記パッド電極の一部を開口するパターンの保護膜を形成する工程とをさらに有し、

前記下地層を形成する工程において、前記保護膜の表面から突出して前記下地層を形成する

請求項6記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005328652A JP2007134635A (ja) | 2005-11-14 | 2005-11-14 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005328652A JP2007134635A (ja) | 2005-11-14 | 2005-11-14 | 半導体装置及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2007134635A true JP2007134635A (ja) | 2007-05-31 |

Family

ID=38156016

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005328652A Pending JP2007134635A (ja) | 2005-11-14 | 2005-11-14 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007134635A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2017098809A1 (ja) * | 2015-12-11 | 2017-06-15 | 株式会社村田製作所 | 弾性波装置 |

-

2005

- 2005-11-14 JP JP2005328652A patent/JP2007134635A/ja active Pending

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2017098809A1 (ja) * | 2015-12-11 | 2017-06-15 | 株式会社村田製作所 | 弾性波装置 |

| US11444596B2 (en) | 2015-12-11 | 2022-09-13 | Murata Manufacturing Co., Ltd. | Acoustic wave device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7056818B2 (en) | Semiconductor device with under bump metallurgy and method for fabricating the same | |

| JP5764256B2 (ja) | 支持端子パッドを有する半導体チップ | |

| US20150228594A1 (en) | Via under the interconnect structures for semiconductor devices | |

| CN102201351A (zh) | 半导体器件和形成用于无铅凸块连接的双ubm结构的方法 | |

| JP2004048012A (ja) | 細かいピッチの、高アスペクト比を有するチップ配線用構造体及び相互接続方法 | |

| TW200828564A (en) | Multi-chip package structure and method of forming the same | |

| TWI253697B (en) | Method for fabricating a flip chip package | |

| US20060214296A1 (en) | Semiconductor device and semiconductor-device manufacturing method | |

| US20130256871A1 (en) | Semiconductor chip device with fragmented solder structure pads | |

| US20120326299A1 (en) | Semiconductor chip with dual polymer film interconnect structures | |

| US7906424B2 (en) | Conductor bump method and apparatus | |

| US10199345B2 (en) | Method of fabricating substrate structure | |

| JPH11354563A (ja) | 半導体配線の構造 | |

| JP2010161419A (ja) | 半導体装置の製造方法 | |

| TWI223425B (en) | Method for mounting passive component on wafer | |

| US6956293B2 (en) | Semiconductor device | |

| JP2000164617A (ja) | チップサイズパッケージおよびその製造方法 | |

| CN100390982C (zh) | 半导体装置及半导体装置的制造方法 | |

| TWI380425B (en) | Fine pitch bump structure and its manufacturing process | |

| JP2007242783A (ja) | 半導体装置及び電子装置 | |

| JP4812673B2 (ja) | 半導体装置 | |

| JP4631223B2 (ja) | 半導体実装体およびそれを用いた半導体装置 | |

| JP2007134635A (ja) | 半導体装置及びその製造方法 | |

| JP2010092974A (ja) | 半導体装置及びその製造方法、並びに電子装置 | |

| JP5776174B2 (ja) | 電子部品内蔵基板の製造方法 |