JP2006509375A - 多層ゲートスタック - Google Patents

多層ゲートスタック Download PDFInfo

- Publication number

- JP2006509375A JP2006509375A JP2004559293A JP2004559293A JP2006509375A JP 2006509375 A JP2006509375 A JP 2006509375A JP 2004559293 A JP2004559293 A JP 2004559293A JP 2004559293 A JP2004559293 A JP 2004559293A JP 2006509375 A JP2006509375 A JP 2006509375A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- gate

- nitride layer

- semiconductor

- sccm

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 claims abstract description 52

- 150000004767 nitrides Chemical class 0.000 claims abstract description 49

- 238000005530 etching Methods 0.000 claims abstract description 41

- 229920002120 photoresistant polymer Polymers 0.000 claims abstract description 28

- 239000000758 substrate Substances 0.000 claims abstract description 26

- 239000000203 mixture Substances 0.000 claims abstract description 16

- 238000004519 manufacturing process Methods 0.000 claims abstract description 10

- 238000000034 method Methods 0.000 claims description 40

- 229910052751 metal Inorganic materials 0.000 claims description 27

- 239000002184 metal Substances 0.000 claims description 27

- 239000007789 gas Substances 0.000 claims description 19

- 229910052710 silicon Inorganic materials 0.000 claims description 11

- 239000010703 silicon Substances 0.000 claims description 11

- 229910052739 hydrogen Inorganic materials 0.000 claims description 8

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 7

- 239000001257 hydrogen Substances 0.000 claims description 7

- 238000002955 isolation Methods 0.000 claims description 7

- 239000011737 fluorine Substances 0.000 claims description 5

- 229910052731 fluorine Inorganic materials 0.000 claims description 5

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 3

- 229910052799 carbon Inorganic materials 0.000 claims description 3

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 claims 1

- 238000000926 separation method Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 139

- 229910052721 tungsten Inorganic materials 0.000 description 15

- 239000010937 tungsten Substances 0.000 description 15

- 230000015572 biosynthetic process Effects 0.000 description 14

- 238000004140 cleaning Methods 0.000 description 14

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 12

- 230000004888 barrier function Effects 0.000 description 11

- 125000006850 spacer group Chemical group 0.000 description 11

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 11

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 9

- 239000000463 material Substances 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 229910000042 hydrogen bromide Inorganic materials 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 6

- 238000004380 ashing Methods 0.000 description 5

- 239000002019 doping agent Substances 0.000 description 5

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 4

- YCIMNLLNPGFGHC-UHFFFAOYSA-N catechol Chemical compound OC1=CC=CC=C1O YCIMNLLNPGFGHC-UHFFFAOYSA-N 0.000 description 4

- 150000003377 silicon compounds Chemical class 0.000 description 4

- -1 tungsten nitride Chemical class 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 239000008367 deionised water Substances 0.000 description 3

- 229910021641 deionized water Inorganic materials 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 230000005855 radiation Effects 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 238000005406 washing Methods 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 241000282461 Canis lupus Species 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- XPDWGBQVDMORPB-UHFFFAOYSA-N Fluoroform Chemical compound FC(F)F XPDWGBQVDMORPB-UHFFFAOYSA-N 0.000 description 2

- AVXURJPOCDRRFD-UHFFFAOYSA-N Hydroxylamine Chemical compound ON AVXURJPOCDRRFD-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000003599 detergent Substances 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- RWRIWBAIICGTTQ-UHFFFAOYSA-N difluoromethane Chemical compound FCF RWRIWBAIICGTTQ-UHFFFAOYSA-N 0.000 description 2

- 239000004744 fabric Substances 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000001020 plasma etching Methods 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- IHGSAQHSAGRWNI-UHFFFAOYSA-N 1-(4-bromophenyl)-2,2,2-trifluoroethanone Chemical compound FC(F)(F)C(=O)C1=CC=C(Br)C=C1 IHGSAQHSAGRWNI-UHFFFAOYSA-N 0.000 description 1

- BMYNFMYTOJXKLE-UHFFFAOYSA-N 3-azaniumyl-2-hydroxypropanoate Chemical compound NCC(O)C(O)=O BMYNFMYTOJXKLE-UHFFFAOYSA-N 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000009987 spinning Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 229920003051 synthetic elastomer Polymers 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28035—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities

- H01L21/28044—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities the conductor comprising at least another non-silicon conductive layer

- H01L21/28061—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities the conductor comprising at least another non-silicon conductive layer the conductor comprising a metal or metal silicide formed by deposition, e.g. sputter deposition, i.e. without a silicidation reaction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

- H01L21/32136—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

- H01L21/32136—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas

- H01L21/32137—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas of silicon-containing layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32139—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28247—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon passivation or protection of the electrode, e.g. using re-oxidation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

Abstract

Description

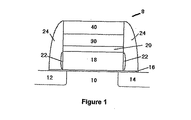

以下の詳細なステップが、分割ゲートを有するゲートスタックを形成するために使用された。

ステップ1:

圧力2ミリトル、温度185度、マイクロ波電力800W、ガスは、3750sccmのO2及び375sccmのN2。

ステップ2:

温度200度、マイクロ波電力1400Wであること以外は同じ値。

ステップ1:

圧力400ミリトル、温度20±5度、RF電力420W、400sccmのO2ガス。

ステップ2:

圧力750ミリトル、温度20±5度、RF電力420W、ガスは、400sccmのN2、400sccmのH2、5sccmのNF3、或いは、その代わりとして、

圧力750ミリトル、温度40±5度、RF電力350W、ガスは、20sccmのCF4、200sccmのN2/5%H2、500sccmのO2。

Claims (20)

- 半導体構造体の製造方法であって、

窒化層をプラズマによりエッチングして、パターン形成された窒化層を形成する工程を含み、

前記窒化層は半導体基板上にあり、

フォトレジスト層が前記窒化層上にあり、

前記プラズマは少なくとも10ミリトルの圧力においてCF4及びCHF3を含むガス混合物から調製される、

ことを特徴とする、前記方法。 - 前記ガス混合物は、CF4:CHF3比が10:1から1:3であることを特徴とする請求項1に記載の方法。

- 前記圧力は15から45ミリトルであることを特徴とする請求項1に記載の方法。

- 前記フォトレジスト層は193ナノメートルのフォトレジストを含むことを特徴とする請求項1に記載の方法。

- 前記パターン形成された窒化層は9ナノメートル以下のラインエッジ粗さを有することを特徴とする請求項1に記載の方法。

- 前記ガス混合物はCF4:CHF3比が8:1から1:2であり、

前記圧力は25から35ミリトルであり、

前記フォトレジスト層は193ナノメートルのフォトレジストを含む、

ことを特徴とする請求項1に記載の方法。 - 半導体構造体の製造方法であって、

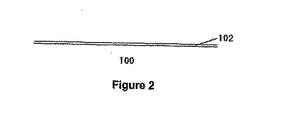

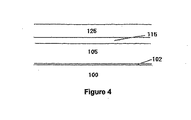

窒化層をプラズマによりエッチングして、パターン形成された窒化層を形成する工程を含み、

前記窒化層はスタック上にあり、

前記スタックは半導体基板上にあり、

前記スタックは、

(i)ケイ素を含むゲート層と、

(ii)前記ゲート層上の金属層と、

を含み、

フォトレジスト層が前記窒化層上にあり、

前記フォトレジスト層は193ナノメートルのフォトレジストを含み、

前記パターン形成された窒化層は8ナノメートル以下のラインエッジ粗さを有し、

前記プラズマは炭素、水素及びフッ素を含む、

ことを特徴とする前記方法。 - 前記パターン形成された窒化層は、6ナノメートル以下のラインエッジ粗さであることを特徴とする請求項7に記載の方法。

- 前記プラズマは、少なくとも15ミリトルの圧力においてガス混合物から調製されることを特徴とする請求項7に記載の方法。

- 前記プラズマは、25から35ミリトルの圧力においてガス混合物から調製されることを特徴とする請求項7に記載の方法。

- 前記ゲート層はP+領域及びN+領域を含み、

前記P+領域及びN+領域は、0.4ミクロン以下の幅を有する前記基板の分離領域上の領域により分離されている、

ことを特徴とする請求項7に記載の方法。 - 請求項1に記載の方法により半導体構造体を形成し、

前記半導体構造体から半導体素子を形成する、

ことを特徴とする半導体素子を製造する方法。 - 請求項12に記載の方法により半導体素子を形成し、

前記半導体素子を有する電子素子を形成する、

ことを特徴とする電子素子を製造する方法。 - 請求項7に記載の方法により半導体構造体を形成し、

前記半導体構造体から半導体素子を形成する、

ことを特徴とする半導体素子を製造する方法。 - 請求項14に記載の方法により半導体素子を形成し、

前記半導体素子を有する電子素子を形成する、

ことを特徴とする電子素子を製造する方法。 - 請求項1に記載の方法により製造された半導体構造体。

- 請求項7に記載の方法により製造された半導体構造体。

- 半導体基板上のパターン形成された窒化層を含み、

前記パターン形成された窒化層は、9ナノメートル以下のラインエッジ粗さであり、

前記基板の分離領域は、0.4ミクロン以下の幅を有する、

ことを特徴とする半導体構造体。 - 前記窒化層と前記半導体構造体との間に更にスタックを有し、

前記スタックは、

(i)ケイ素を含むゲート層と、

(ii)前記ゲート層上の金属層と、

を有し、

前記ゲート層は前記分離領域上にある、

ことを特徴とする請求項18に記載の半導体構造体。 - 前記パターン形成された窒化層は6ナノメートル以下のラインエッジ粗さであることを特徴とする請求項18に記載の半導体構造体。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/314,380 US7229929B2 (en) | 2002-12-06 | 2002-12-06 | Multi-layer gate stack |

| PCT/US2003/038631 WO2004053936A2 (en) | 2002-12-06 | 2003-12-04 | Multi-layer gate stack |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006509375A true JP2006509375A (ja) | 2006-03-16 |

| JP2006509375A5 JP2006509375A5 (ja) | 2007-01-25 |

Family

ID=32468458

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004559293A Pending JP2006509375A (ja) | 2002-12-06 | 2003-12-04 | 多層ゲートスタック |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7229929B2 (ja) |

| JP (1) | JP2006509375A (ja) |

| KR (1) | KR20050085415A (ja) |

| AU (1) | AU2003300819A1 (ja) |

| WO (1) | WO2004053936A2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7229929B2 (en) * | 2002-12-06 | 2007-06-12 | Cypress Semiconductor Corporation | Multi-layer gate stack |

| US20040217006A1 (en) * | 2003-03-18 | 2004-11-04 | Small Robert J. | Residue removers for electrohydrodynamic cleaning of semiconductors |

| US7371637B2 (en) * | 2003-09-26 | 2008-05-13 | Cypress Semiconductor Corporation | Oxide-nitride stack gate dielectric |

| US7153780B2 (en) * | 2004-03-24 | 2006-12-26 | Intel Corporation | Method and apparatus for self-aligned MOS patterning |

| US7351663B1 (en) * | 2004-06-25 | 2008-04-01 | Cypress Semiconductor Corporation | Removing whisker defects |

| KR100753138B1 (ko) * | 2006-09-29 | 2007-08-30 | 주식회사 하이닉스반도체 | 반도체 소자 제조방법 |

| US8252640B1 (en) | 2006-11-02 | 2012-08-28 | Kapre Ravindra M | Polycrystalline silicon activation RTA |

| JP2008218867A (ja) * | 2007-03-07 | 2008-09-18 | Elpida Memory Inc | 半導体装置の製造方法 |

| US7951728B2 (en) * | 2007-09-24 | 2011-05-31 | Applied Materials, Inc. | Method of improving oxide growth rate of selective oxidation processes |

| US9406530B2 (en) | 2014-03-27 | 2016-08-02 | International Business Machines Corporation | Techniques for fabricating reduced-line-edge-roughness trenches for aspect ratio trapping |

| US10204960B2 (en) * | 2015-09-17 | 2019-02-12 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of forming polysilicon gate structure in image sensor device |

| US20170330764A1 (en) * | 2016-05-12 | 2017-11-16 | Lam Research Corporation | Methods and apparatuses for controlling transitions between continuous wave and pulsing plasmas |

| US10566211B2 (en) | 2016-08-30 | 2020-02-18 | Lam Research Corporation | Continuous and pulsed RF plasma for etching metals |

| US9865473B1 (en) * | 2016-11-15 | 2018-01-09 | Globalfoundries Inc. | Methods of forming semiconductor devices using semi-bidirectional patterning and islands |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001051424A (ja) * | 1999-06-02 | 2001-02-23 | Semiconductor Leading Edge Technologies Inc | 微細パターン形成方法 |

| JP2002222868A (ja) * | 2001-01-29 | 2002-08-09 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006505141A (ja) * | 2002-10-31 | 2006-02-09 | アプライド マテリアルズ インコーポレイテッド | シリコン含有誘電物質をエッチングする方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW320749B (ja) * | 1994-09-22 | 1997-11-21 | Tokyo Electron Co Ltd | |

| US5817579A (en) * | 1997-04-09 | 1998-10-06 | Vanguard International Semiconductor Corporation | Two step plasma etch method for forming self aligned contact |

| JP3902835B2 (ja) * | 1997-06-27 | 2007-04-11 | 東京応化工業株式会社 | ポジ型ホトレジスト組成物 |

| US6635185B2 (en) * | 1997-12-31 | 2003-10-21 | Alliedsignal Inc. | Method of etching and cleaning using fluorinated carbonyl compounds |

| US6107135A (en) * | 1998-02-11 | 2000-08-22 | Kabushiki Kaisha Toshiba | Method of making a semiconductor memory device having a buried plate electrode |

| US6342452B1 (en) * | 1999-05-20 | 2002-01-29 | International Business Machines Corporation | Method of fabricating a Si3N4/polycide structure using a dielectric sacrificial layer as a mask |

| US6740566B2 (en) * | 1999-09-17 | 2004-05-25 | Advanced Micro Devices, Inc. | Ultra-thin resist shallow trench process using high selectivity nitride etch |

| US6258677B1 (en) * | 1999-10-01 | 2001-07-10 | Chartered Seminconductor Manufacturing Ltd. | Method of fabricating wedge isolation transistors |

| US6897120B2 (en) * | 2001-01-03 | 2005-05-24 | Micron Technology, Inc. | Method of forming integrated circuitry and method of forming shallow trench isolation in a semiconductor substrate |

| US6624068B2 (en) * | 2001-08-24 | 2003-09-23 | Texas Instruments Incorporated | Polysilicon processing using an anti-reflective dual layer hardmask for 193 nm lithography |

| US6451647B1 (en) * | 2002-03-18 | 2002-09-17 | Advanced Micro Devices, Inc. | Integrated plasma etch of gate and gate dielectric and low power plasma post gate etch removal of high-K residual |

| US7229929B2 (en) * | 2002-12-06 | 2007-06-12 | Cypress Semiconductor Corporation | Multi-layer gate stack |

-

2002

- 2002-12-06 US US10/314,380 patent/US7229929B2/en not_active Expired - Lifetime

-

2003

- 2003-12-04 WO PCT/US2003/038631 patent/WO2004053936A2/en active Application Filing

- 2003-12-04 AU AU2003300819A patent/AU2003300819A1/en not_active Abandoned

- 2003-12-04 KR KR1020057010280A patent/KR20050085415A/ko not_active Application Discontinuation

- 2003-12-04 JP JP2004559293A patent/JP2006509375A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001051424A (ja) * | 1999-06-02 | 2001-02-23 | Semiconductor Leading Edge Technologies Inc | 微細パターン形成方法 |

| JP2002222868A (ja) * | 2001-01-29 | 2002-08-09 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006505141A (ja) * | 2002-10-31 | 2006-02-09 | アプライド マテリアルズ インコーポレイテッド | シリコン含有誘電物質をエッチングする方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2004053936A3 (en) | 2005-03-17 |

| US20040110387A1 (en) | 2004-06-10 |

| KR20050085415A (ko) | 2005-08-29 |

| US7229929B2 (en) | 2007-06-12 |

| AU2003300819A1 (en) | 2004-06-30 |

| WO2004053936A2 (en) | 2004-06-24 |

| AU2003300819A8 (en) | 2004-06-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7396773B1 (en) | Method for cleaning a gate stack | |

| US6667246B2 (en) | Wet-etching method and method for manufacturing semiconductor device | |

| US7256137B2 (en) | Method of forming contact plug on silicide structure | |

| JPH0621018A (ja) | ドライエッチング方法 | |

| US5164331A (en) | Method of forming and etching titanium-tungsten interconnects | |

| US6878646B1 (en) | Method to control critical dimension of a hard masked pattern | |

| US7229929B2 (en) | Multi-layer gate stack | |

| KR100954107B1 (ko) | 반도체 소자의 제조방법 | |

| US6586293B1 (en) | Semiconductor device and method of manufacturing the same | |

| US6943126B1 (en) | Deuterium incorporated nitride | |

| JP2004006902A (ja) | 半導体デバイスおよびその製造方法 | |

| US8445381B2 (en) | Oxide-nitride stack gate dielectric | |

| US7189652B1 (en) | Selective oxidation of gate stack | |

| KR100616498B1 (ko) | 폴리/텅스텐 게이트 전극을 갖는 반도체 소자의 제조방법 | |

| US6680516B1 (en) | Controlled thickness gate stack | |

| JP2003234325A (ja) | 半導体装置の製造方法 | |

| CN111106158B (zh) | 半导体结构及其形成方法 | |

| US6803321B1 (en) | Nitride spacer formation | |

| US6828187B1 (en) | Method for uniform reactive ion etching of dual pre-doped polysilicon regions | |

| JP4082280B2 (ja) | 半導体装置およびその製造方法 | |

| KR20060122578A (ko) | 반도체 메모리 소자의 하드 마스크 형성방법 | |

| KR100596899B1 (ko) | 반도체 소자의 제조 방법 | |

| US6555397B1 (en) | Dry isotropic removal of inorganic anti-reflective coating after poly gate etching | |

| US7256083B1 (en) | Nitride layer on a gate stack | |

| JP2008135765A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061121 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061121 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20090526 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20090526 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20090527 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091214 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091222 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100615 |