JP2006113564A - 表示装置及びその駆動方法 - Google Patents

表示装置及びその駆動方法 Download PDFInfo

- Publication number

- JP2006113564A JP2006113564A JP2005264548A JP2005264548A JP2006113564A JP 2006113564 A JP2006113564 A JP 2006113564A JP 2005264548 A JP2005264548 A JP 2005264548A JP 2005264548 A JP2005264548 A JP 2005264548A JP 2006113564 A JP2006113564 A JP 2006113564A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- thin film

- film transistor

- emitting element

- light emitting

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000000034 method Methods 0.000 title claims abstract description 35

- 239000010409 thin film Substances 0.000 claims abstract description 234

- 239000003990 capacitor Substances 0.000 claims description 48

- 239000004065 semiconductor Substances 0.000 claims description 22

- 238000007599 discharging Methods 0.000 claims 1

- 239000010408 film Substances 0.000 description 90

- 239000010410 layer Substances 0.000 description 67

- 239000000463 material Substances 0.000 description 17

- 239000000758 substrate Substances 0.000 description 12

- 239000010936 titanium Substances 0.000 description 9

- 238000010586 diagram Methods 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 239000012535 impurity Substances 0.000 description 7

- 239000002585 base Substances 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 239000002356 single layer Substances 0.000 description 6

- 125000001424 substituent group Chemical group 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- 238000002425 crystallisation Methods 0.000 description 4

- 125000001153 fluoro group Chemical group F* 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 125000000962 organic group Chemical group 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- -1 Li and Cs Chemical class 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 125000000217 alkyl group Chemical group 0.000 description 2

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- WPYMKLBDIGXBTP-UHFFFAOYSA-N benzoic acid Chemical compound OC(=O)C1=CC=CC=C1 WPYMKLBDIGXBTP-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910052744 lithium Inorganic materials 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000005711 Benzoic acid Substances 0.000 description 1

- 229910004261 CaF 2 Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 235000010233 benzoic acid Nutrition 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052792 caesium Inorganic materials 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- CFBGXYDUODCMNS-UHFFFAOYSA-N cyclobutene Chemical compound C1CC=C1 CFBGXYDUODCMNS-UHFFFAOYSA-N 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- ORQBXQOJMQIAOY-UHFFFAOYSA-N nobelium Chemical compound [No] ORQBXQOJMQIAOY-UHFFFAOYSA-N 0.000 description 1

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 150000002910 rare earth metals Chemical class 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- Y02B20/343—

Abstract

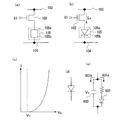

【解決方法】発光素子に直列に接続された薄膜トランジスタのオフを選択したときに、発光素子自体の容量に保持された電荷を放電する。発光素子と直列に接続された薄膜トランジスタにオフ電流が生じても、このオフ電流は発光素子自体の容量が再び所定の電圧を保持するまでこの容量を充電する。よって、薄膜トランジスタのオフ電流は発光に寄与しない。こうして、発光素子の微発光を低減することができる。

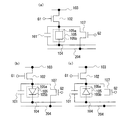

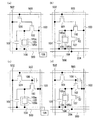

【選択図】 図1

Description

発光素子の第1の電極を陽極とし第2の電極を陰極とした場合には、発光素子と直列に接続された第1の薄膜トランジスタのオフを選択したとき、第1の電極の電位が第2の電極の電位以上であり、且つ第1の電極と第2の電極間に印加される電圧が発光素子のしきい値電圧より小さくなるように、第2の電源線の電位を設定する。

発光素子の第1の電極を陽極とし第2の電極を陰極とした場合には、発光素子と直列に接続された第1の薄膜トランジスタとは別の第2の薄膜トランジスタを設ける。第2の薄膜トランジスタのソース及びドレインの一方は、発光素子の第1の電極に接続され、他方は、電源線に接続する。第1の薄膜トランジスタのオフを選択したとき、第2の薄膜トランジスタのオンを選択し、且つ当該電源線の電位を発光素子の第2の電極の電位以上とし、当該第2の電極の電位に発光素子のしきい値電圧をたした電位よりも低くする。

[第3の手段]

発光素子と並列に接続された容量素子を設ける。

即ち、一方の電極が発光素子の第1の電極と接続され、他方の電極が発光素子の第2の電極と接続されるように容量素子を設ける。

第1の手段と第3の手段を組み合わせた例について、図1を用いて説明する。図1において、105は発光素子、102は薄膜トランジスタ、103は第1の電源線、104は第2の電源線、101は容量素子、106は電位を設定する手段である。電位を設定する手段106が第1の手段に対応する。容量素子101が第3の手段に対応する。発光素子105は、2つの電極を有し、2つの電極間に電流が流れると流れた電流値に応じた輝度で発光する素子である。発光素子105の2つの電極のうち一方を第1の電極105aで示し、他方を第2の電極105bで示す。

第2の手段と第3の手段を組み合わせた例について、図2を用いて説明する。図2において、図1と同じ部分は同じ符号を用いて示し、説明は省略する。107は薄膜トランジスタである。薄膜トランジスタ107及び第3の電源線204が第2の手段に対応する。容量素子101が第3の手段に対応する。

第1の手段と第3の手段を組み合わせた例について、図3を用いて説明する。図3において、図1と同じ部分は同じ符号を用いて示し説明は省略する。

第2の手段と第3の手段を組み合わせた例について、図4を用いて説明する。図4において、図2や図3と同じ部分は同じ符号を用いて示し説明は省略する。

102 薄膜トランジスタ

103 第1の電源線

104 第2の電源線

105 発光素子

105a 第1の電極

105b 第2の電極

106 電位を設定する手段

107 薄膜トランジスタ

108 容量素子

204 第3の電源線

500 画素

501 薄膜トランジスタ

502 信号線

503 走査線

601 薄膜トランジスタ

701 薄膜トランジスタ

702 薄膜トランジスタ

703 薄膜トランジスタ

704 信号線

705 走査線

800 容量

801a 経路

801b 経路

802 ダイオード

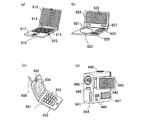

911 本体

912 筐体

913 表示部

914 キーボード

915 外部接続ポート

916 ポインティングパッド

921 本体

922 筐体

923 第1の表示部

924 第2の表示部

925 記録媒体(DVD等)読み込み部

926 操作キー

927 スピーカー部

931 本体

932 音声出力部

933 音声入力部

934 表示部

935 操作スイッチ

936 アンテナ

941 本体

942 表示部

943 筐体

944 外部接続ポート

945 リモコン受信部

946 受像部

947 バッテリー

948 音声入力部

949 操作キー

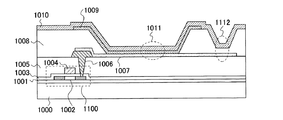

1000 基板

1001 下地膜

1002 半導体層

1003 第1の絶縁膜

1004 ゲート電極

1005 第2の絶縁膜

1006 電極

1007 第1の電極

1008 第3の絶縁膜

1009 発光層

1010 第2の電極

1011 発光素子

1012 容量素子

1100 薄膜トランジスタ

1112 容量素子

1212 容量素子

1213 容量素子

1206a 第1の層

1206b 第2の層

1206c 第3の層

1312 容量素子

1313 容量素子

1400 フォトマスク

1401 第1の光透過部

1402 第2の光透過部

1403 遮光部

1408 絶縁膜

1411 開口部

1412 膜厚の薄い部分

1508a 絶縁膜

1508b 絶縁膜

1511a 第1の開口部

1511b 第3の開口部

1512 第2の開口部

Claims (14)

- 第1の薄膜トランジスタと第1の容量素子と発光素子とを有する画素と、第1の電源線と、第2の電源線とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極及び前記第1の容量素子の一方の電極と接続され、

前記第1の容量素子の他方の電極は、前記第2の電源線に接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

前記第2の電源線の電位を変化させる手段を有することを特徴とする表示装置。 - 第1の薄膜トランジスタと第2の薄膜トランジスタと第1の容量素子と発光素子とを有する画素と、第1の電源線と、第2の電源線とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極及び前記第1の容量素子の一方の電極と接続され、

前記第1の容量素子の他方の電極は、前記第2の電源線に接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

前記第2の薄膜トランジスタのソース及びドレインの一方は、前記第1の電極に接続され、他方は、前記第2の電極に接続されることを特徴とする表示装置。 - 請求項1または請求項2において、

前記第1の薄膜トランジスタは活性層が多結晶半導体でなることを特徴とする表示装置。 - 請求項1乃至請求項3のいずれか一項において、

第2の容量素子を有し、

前記第2の容量素子の一方の電極は、前記第1の薄膜トランジスタのゲートと接続され、他方の電極は、前記第1の薄膜トランジスタのソースと接続されていることを特徴とする表示装置。 - 請求項1乃至請求項4のいずれか一項において、

前記表示装置を用いたことを特徴とする電子機器。 - 第1の薄膜トランジスタと発光素子とを有する画素と、第1の電源線と、第2の電源線とを有し、

前記発光素子は、第1の電極と第2の電極とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極と接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

前記第1の薄膜トランジスタのオンを選択したときには、前記第1の電極の電位が前記第2の電極の電位より高く、且つ前記第1の電極と前記第2の電極間に印加される電圧が前記発光素子のしきい値電圧より大きくなるように、前記第1の電源線の電位及び前記第2の電源線の電位を設定して前記発光素子を発光させ、

前記第1の薄膜トランジスタのオフを選択したときには、前記第1の電極の電位が前記第2の電極の電位以上であり、且つ前記第1の電極と前記第2の電極間に印加される電圧が前記しきい値電圧より小さくなるように、前記第2の電源線の電位を設定して前記発光素子を発光させないことを特徴とする表示装置の駆動方法。 - 第1の薄膜トランジスタと発光素子とを有する画素と、第1の電源線と、第2の電源線とを有し、

前記発光素子は、第1の電極と第2の電極とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極と接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

前記第1の薄膜トランジスタのオンを選択したときには、前記第1の電極の電位が前記第2の電極の電位より低く、且つ前記第1の電極と前記第2の電極間に印加される電圧が前記発光素子のしきい値電圧より大きくなるように、前記第1の電源線の電位及び前記第2の電源線の電位を設定して前記発光素子を発光させ、

前記第1の薄膜トランジスタのオフを選択したときには、前記第1の電極の電位が前記第2の電極の電位以下であり、且つ前記第1の電極と前記第2の電極間に印加される電圧が前記しきい値電圧より小さくなるように、前記第2の電源線の電位を設定して前記発光素子を発光させないことを特徴とする表示装置の駆動方法。 - 第1の薄膜トランジスタと発光素子とを有する画素と、第1の電源線と、第2の電源線と、第3の電源線とを有し、

前記発光素子は、第1の電極と第2の電極とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極と接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

前記第1の薄膜トランジスタとは別の第2の薄膜トランジスタを有し、

前記第2の薄膜トランジスタのソース及びドレインの一方は、前記第1の電極に接続され、他方は、前記第3の電源線に接続され、

前記第1の薄膜トランジスタのオフを選択したとき、前記第2の薄膜トランジスタのオンを選択し、且つ前記第3の電源線の電位を前記第2の電源線の電位以上であり、且つ前記第2の電源線の電位に前記発光素子のしきい値電圧をたした電位よりも低くすることを特徴とする表示装置の駆動方法。 - 第1の薄膜トランジスタと発光素子とを有する画素と、第1の電源線と、第2の電源線と、第3の電源線とを有し、

前記発光素子は、第1の電極と第2の電極とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極と接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

第2の薄膜トランジスタを有し、

前記第2の薄膜トランジスタのソース及びドレインの一方は、前記第1の電極に接続され、他方は、前記第3の電源線に接続され、

前記第1の薄膜トランジスタのオフを選択したとき、前記第2の薄膜トランジスタのオンを選択し、且つ前記第3の電源線の電位を前記第2の電源線の電位以下であり、且つ前記第2の電源線の電位から前記発光素子のしきい値電圧を引いた電位よりも高くすることを特徴とする表示装置の駆動方法。 - 第1の薄膜トランジスタと発光素子とを有する画素と、第1の電源線と、第2の電源線とを有し、

前記発光素子は、第1の電極と第2の電極とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極と接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

第2の薄膜トランジスタを有し、

前記第2の薄膜トランジスタのソース及びドレインの一方は、前記第1の電極に接続され、他方は、前記第2の電極に接続され、

前記第1の薄膜トランジスタのオフを選択したとき、前記第2の薄膜トランジスタのオンを選択することを特徴とする表示装置の駆動方法。 - 請求項6乃至請求項10のいずれか一項において、

前記第1の薄膜トランジスタは活性層が多結晶半導体でなることを特徴とする表示装置の駆動方法。 - 請求項6乃至請求項11のいずれか一項において、

1フレーム期間内に前記発光素子が発光した時間を制御することで階調を表現することを特徴とする表示装置の駆動方法。 - 請求項6乃至請求項12のいずれか一項において、

容量素子を有し、

前記容量素子の一方の電極は、前記第1の薄膜トランジスタのゲートと接続され、他方の電極は、前記第1の薄膜トランジスタのソースと接続されていることを特徴とする表示装置の駆動方法。 - 請求項13において、

前記容量素子に保持された電荷を放電することによって、前記第1の薄膜トランジスタのオフを選択することを特徴とする表示装置の駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005264548A JP2006113564A (ja) | 2004-09-16 | 2005-09-13 | 表示装置及びその駆動方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004270447 | 2004-09-16 | ||

| JP2005264548A JP2006113564A (ja) | 2004-09-16 | 2005-09-13 | 表示装置及びその駆動方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012025697A Division JP2012150479A (ja) | 2004-09-16 | 2012-02-09 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006113564A true JP2006113564A (ja) | 2006-04-27 |

| JP2006113564A5 JP2006113564A5 (ja) | 2008-08-21 |

Family

ID=36382078

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005264548A Withdrawn JP2006113564A (ja) | 2004-09-16 | 2005-09-13 | 表示装置及びその駆動方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006113564A (ja) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008226491A (ja) * | 2007-03-08 | 2008-09-25 | Sony Corp | 有機エレクトロルミネッセンス表示装置 |

| JP2009193063A (ja) * | 2008-01-15 | 2009-08-27 | Semiconductor Energy Lab Co Ltd | 表示装置及び電子機器 |

| US7745827B2 (en) | 2005-09-29 | 2010-06-29 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

| JP2012068662A (ja) * | 2011-11-04 | 2012-04-05 | Sony Corp | 表示装置 |

| JP2012093424A (ja) * | 2010-10-25 | 2012-05-17 | Seiko Epson Corp | 画素回路、その駆動方法、電気光学装置および電子機器 |

| US8217868B2 (en) | 2008-05-13 | 2012-07-10 | Samsung Electronics Co., Ltd. | Display device and method of driving the same |

| CN102592540A (zh) * | 2011-01-06 | 2012-07-18 | 索尼公司 | 有机el显示装置和电子设备 |

| JP2012230393A (ja) * | 2012-06-19 | 2012-11-22 | Sony Corp | 画像表示装置 |

| USRE44563E1 (en) | 2005-10-07 | 2013-10-29 | Sony Corporation | Pixel circuit and display apparatus |

| KR20210012509A (ko) * | 2019-07-25 | 2021-02-03 | 엘지디스플레이 주식회사 | 표시 장치 |

Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0854836A (ja) * | 1994-08-10 | 1996-02-27 | Nec Corp | アクティブマトリクス型電流制御型発光素子の駆動回路 |

| JPH0997925A (ja) * | 1995-09-29 | 1997-04-08 | Pioneer Electron Corp | 発光素子の駆動回路 |

| JP2000122608A (ja) * | 1998-10-13 | 2000-04-28 | Seiko Epson Corp | 表示装置及び電子機器 |

| JP2000276109A (ja) * | 1999-03-25 | 2000-10-06 | Tdk Corp | 薄膜発光素子の駆動方法および駆動回路 |

| JP2000347621A (ja) * | 1999-06-09 | 2000-12-15 | Nec Corp | 画像表示方法および装置 |

| JP2002196706A (ja) * | 1996-11-29 | 2002-07-12 | Sanyo Electric Co Ltd | 単純マトリックス方式の表示装置 |

| JP2002207451A (ja) * | 2001-01-09 | 2002-07-26 | Hitachi Ltd | 有機ledディスプレイおよびその駆動方法 |

| JP2002311898A (ja) * | 2001-02-08 | 2002-10-25 | Semiconductor Energy Lab Co Ltd | 発光装置及びそれを用いた電子機器 |

| JP2003208127A (ja) * | 2001-11-09 | 2003-07-25 | Sanyo Electric Co Ltd | 表示装置 |

| JP2003255895A (ja) * | 2002-02-28 | 2003-09-10 | Semiconductor Energy Lab Co Ltd | 発光装置及びその駆動方法 |

| JP2004309844A (ja) * | 2003-04-08 | 2004-11-04 | Seiko Epson Corp | 電気光学装置、電気光学装置の駆動方法電気光学装置の駆動回路および電子機器 |

| JP2005084119A (ja) * | 2003-09-04 | 2005-03-31 | Nec Corp | 発光素子の駆動回路及び電流制御型発光表示装置 |

| JP2006231911A (ja) * | 2005-01-27 | 2006-09-07 | Seiko Epson Corp | 画素回路、発光装置および電子機器 |

-

2005

- 2005-09-13 JP JP2005264548A patent/JP2006113564A/ja not_active Withdrawn

Patent Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0854836A (ja) * | 1994-08-10 | 1996-02-27 | Nec Corp | アクティブマトリクス型電流制御型発光素子の駆動回路 |

| JPH0997925A (ja) * | 1995-09-29 | 1997-04-08 | Pioneer Electron Corp | 発光素子の駆動回路 |

| JP2002196706A (ja) * | 1996-11-29 | 2002-07-12 | Sanyo Electric Co Ltd | 単純マトリックス方式の表示装置 |

| JP2000122608A (ja) * | 1998-10-13 | 2000-04-28 | Seiko Epson Corp | 表示装置及び電子機器 |

| JP2000276109A (ja) * | 1999-03-25 | 2000-10-06 | Tdk Corp | 薄膜発光素子の駆動方法および駆動回路 |

| JP2000347621A (ja) * | 1999-06-09 | 2000-12-15 | Nec Corp | 画像表示方法および装置 |

| JP2002207451A (ja) * | 2001-01-09 | 2002-07-26 | Hitachi Ltd | 有機ledディスプレイおよびその駆動方法 |

| JP2002311898A (ja) * | 2001-02-08 | 2002-10-25 | Semiconductor Energy Lab Co Ltd | 発光装置及びそれを用いた電子機器 |

| JP2003208127A (ja) * | 2001-11-09 | 2003-07-25 | Sanyo Electric Co Ltd | 表示装置 |

| JP2003255895A (ja) * | 2002-02-28 | 2003-09-10 | Semiconductor Energy Lab Co Ltd | 発光装置及びその駆動方法 |

| JP2004309844A (ja) * | 2003-04-08 | 2004-11-04 | Seiko Epson Corp | 電気光学装置、電気光学装置の駆動方法電気光学装置の駆動回路および電子機器 |

| JP2005084119A (ja) * | 2003-09-04 | 2005-03-31 | Nec Corp | 発光素子の駆動回路及び電流制御型発光表示装置 |

| JP2006231911A (ja) * | 2005-01-27 | 2006-09-07 | Seiko Epson Corp | 画素回路、発光装置および電子機器 |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7745827B2 (en) | 2005-09-29 | 2010-06-29 | Semiconductor Energy Laboratory Co., Ltd. | Memory device |

| USRE44563E1 (en) | 2005-10-07 | 2013-10-29 | Sony Corporation | Pixel circuit and display apparatus |

| USRE45400E1 (en) | 2005-10-07 | 2015-03-03 | Sony Corporation | Pixel circuit and display apparatus |

| JP2008226491A (ja) * | 2007-03-08 | 2008-09-25 | Sony Corp | 有機エレクトロルミネッセンス表示装置 |

| JP2009193063A (ja) * | 2008-01-15 | 2009-08-27 | Semiconductor Energy Lab Co Ltd | 表示装置及び電子機器 |

| KR101531542B1 (ko) * | 2008-01-15 | 2015-06-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 전자 기기 |

| US8217868B2 (en) | 2008-05-13 | 2012-07-10 | Samsung Electronics Co., Ltd. | Display device and method of driving the same |

| JP2012093424A (ja) * | 2010-10-25 | 2012-05-17 | Seiko Epson Corp | 画素回路、その駆動方法、電気光学装置および電子機器 |

| CN102592540A (zh) * | 2011-01-06 | 2012-07-18 | 索尼公司 | 有机el显示装置和电子设备 |

| JP2012141526A (ja) * | 2011-01-06 | 2012-07-26 | Sony Corp | 有機el表示装置及び電子機器 |

| JP2012068662A (ja) * | 2011-11-04 | 2012-04-05 | Sony Corp | 表示装置 |

| JP2012230393A (ja) * | 2012-06-19 | 2012-11-22 | Sony Corp | 画像表示装置 |

| KR20210012509A (ko) * | 2019-07-25 | 2021-02-03 | 엘지디스플레이 주식회사 | 표시 장치 |

| KR102629520B1 (ko) * | 2019-07-25 | 2024-01-25 | 엘지디스플레이 주식회사 | 표시 장치 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7453295B2 (ja) | 表示装置 | |

| US20140118653A1 (en) | Semiconductor device and driving method thereof | |

| JP2006113564A (ja) | 表示装置及びその駆動方法 | |

| EP1729280B1 (en) | Display device, display module, electronic apparatus and driving method of the display device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080708 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080708 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110524 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110613 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120216 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120508 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20120515 |