JP2006032541A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2006032541A JP2006032541A JP2004207205A JP2004207205A JP2006032541A JP 2006032541 A JP2006032541 A JP 2006032541A JP 2004207205 A JP2004207205 A JP 2004207205A JP 2004207205 A JP2004207205 A JP 2004207205A JP 2006032541 A JP2006032541 A JP 2006032541A

- Authority

- JP

- Japan

- Prior art keywords

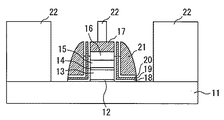

- film

- gate electrode

- nitride film

- semiconductor device

- oxide film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 47

- 150000004767 nitrides Chemical class 0.000 claims abstract description 41

- 239000000758 substrate Substances 0.000 claims abstract description 8

- 230000007423 decrease Effects 0.000 claims description 2

- 238000005530 etching Methods 0.000 abstract description 22

- 229910004298 SiO 2 Inorganic materials 0.000 description 32

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 18

- 229920005591 polysilicon Polymers 0.000 description 18

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 239000000470 constituent Substances 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004207205A JP2006032541A (ja) | 2004-07-14 | 2004-07-14 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004207205A JP2006032541A (ja) | 2004-07-14 | 2004-07-14 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006032541A true JP2006032541A (ja) | 2006-02-02 |

| JP2006032541A5 JP2006032541A5 (enExample) | 2007-08-23 |

Family

ID=35898545

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004207205A Pending JP2006032541A (ja) | 2004-07-14 | 2004-07-14 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2006032541A (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9461138B2 (en) | 2012-02-28 | 2016-10-04 | Seiko Epson Corporation | Non-volatile semiconductor memory with nitride sidewall contacting nitride layer of ONO gate stack and methods for producing the same |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10144787A (ja) * | 1996-11-07 | 1998-05-29 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2002252232A (ja) * | 2001-02-13 | 2002-09-06 | Samsung Electronics Co Ltd | 多重膜よりなるスぺーサを有する半導体素子及びその製造方法 |

-

2004

- 2004-07-14 JP JP2004207205A patent/JP2006032541A/ja active Pending

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10144787A (ja) * | 1996-11-07 | 1998-05-29 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2002252232A (ja) * | 2001-02-13 | 2002-09-06 | Samsung Electronics Co Ltd | 多重膜よりなるスぺーサを有する半導体素子及びその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9461138B2 (en) | 2012-02-28 | 2016-10-04 | Seiko Epson Corporation | Non-volatile semiconductor memory with nitride sidewall contacting nitride layer of ONO gate stack and methods for producing the same |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7723191B2 (en) | Method of manufacturing semiconductor device having buried gate | |

| JP2005531919A (ja) | 集積回路装置およびその製造方法 | |

| KR100454135B1 (ko) | 비휘발성 기억소자의 형성방법 | |

| JP2007013074A (ja) | 半導体素子の製造方法 | |

| US10497786B2 (en) | Manufacturing method of semiconductor device | |

| KR100951559B1 (ko) | 반도체 소자의 게이트 전극 형성 방법 | |

| JP2007180486A (ja) | 5チャネルのフィントランジスタ及びその製造方法 | |

| JP3724648B2 (ja) | 半導体装置の製造方法 | |

| JP5131804B2 (ja) | フラッシュメモリ素子の製造方法 | |

| KR100739656B1 (ko) | 반도체 장치의 제조 방법 | |

| KR100493065B1 (ko) | 트렌치 게이트형 트랜지스터를 구비하는 반도체 소자 및그 제조 방법 | |

| JP2006100790A (ja) | 半導体装置及びその製造方法 | |

| JP2006032541A (ja) | 半導体装置 | |

| JP2004214681A (ja) | 不揮発性メモリ素子の製造方法 | |

| KR100526476B1 (ko) | 스플릿 게이트형 플래쉬 메모리 소자의제조방법 | |

| KR100343471B1 (ko) | 반도체 소자 제조방법 | |

| KR100671603B1 (ko) | 플래시 메모리 소자의 제조 방법 | |

| JP4836730B2 (ja) | 半導体装置、およびその製造方法 | |

| JP4307348B2 (ja) | 蝕刻選択比の大きいバッファ層を利用した自己整列強誘電体ゲートトランジスタの製造方法 | |

| JP2006024605A (ja) | 半導体集積回路装置の製造方法 | |

| KR100854905B1 (ko) | 플래시 메모리 소자의 제조 방법 | |

| JP2007165829A (ja) | フラッシュメモリ素子のゲート形成方法 | |

| JP2009158916A (ja) | 半導体素子のトレンチ形成方法 | |

| JP2006310601A (ja) | 半導体装置およびその製造方法 | |

| KR20030045216A (ko) | 반도체 소자의 트렌치 형성 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070706 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070706 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090310 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100521 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110315 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110726 |