JP2005510871A - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2005510871A JP2005510871A JP2003548292A JP2003548292A JP2005510871A JP 2005510871 A JP2005510871 A JP 2005510871A JP 2003548292 A JP2003548292 A JP 2003548292A JP 2003548292 A JP2003548292 A JP 2003548292A JP 2005510871 A JP2005510871 A JP 2005510871A

- Authority

- JP

- Japan

- Prior art keywords

- surface layer

- amorphous

- semiconductor

- dopant atoms

- radiation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 81

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 12

- 239000002344 surface layer Substances 0.000 claims abstract description 57

- 238000000034 method Methods 0.000 claims abstract description 41

- 230000005855 radiation Effects 0.000 claims abstract description 23

- 239000013078 crystal Substances 0.000 claims abstract description 19

- 238000005280 amorphization Methods 0.000 claims abstract description 10

- 230000004907 flux Effects 0.000 claims abstract description 9

- 239000002019 doping agent Substances 0.000 claims description 39

- 239000000463 material Substances 0.000 claims description 25

- 239000010410 layer Substances 0.000 claims description 15

- 238000004151 rapid thermal annealing Methods 0.000 claims description 11

- 238000010521 absorption reaction Methods 0.000 claims description 10

- 238000002844 melting Methods 0.000 claims description 7

- 230000008018 melting Effects 0.000 claims description 7

- 238000005468 ion implantation Methods 0.000 claims description 6

- 238000001816 cooling Methods 0.000 claims description 4

- 238000005224 laser annealing Methods 0.000 claims description 3

- 239000000155 melt Substances 0.000 claims 1

- 239000007787 solid Substances 0.000 claims 1

- 230000001678 irradiating effect Effects 0.000 abstract 1

- 238000002513 implantation Methods 0.000 description 19

- 238000009792 diffusion process Methods 0.000 description 14

- 230000004913 activation Effects 0.000 description 8

- 238000001953 recrystallisation Methods 0.000 description 8

- 150000002500 ions Chemical class 0.000 description 7

- 230000008569 process Effects 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 229910052732 germanium Inorganic materials 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 5

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 4

- 239000007791 liquid phase Substances 0.000 description 4

- 239000007790 solid phase Substances 0.000 description 4

- 238000000348 solid-phase epitaxy Methods 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 238000000137 annealing Methods 0.000 description 3

- 238000004090 dissolution Methods 0.000 description 3

- 238000004943 liquid phase epitaxy Methods 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 230000002745 absorbent Effects 0.000 description 1

- 239000002250 absorbent Substances 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000005465 channeling Effects 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 230000009849 deactivation Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000005596 ionic collisions Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 238000004781 supercooling Methods 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000012876 topography Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

- H01L21/2652—Through-implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/268—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66575—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate

Abstract

Description

Claims (12)

- 半導体ボディを有する半導体装置の製造方法であって、ドープ領域が、前記半導体ボディに形成され、前記半導体ボディは半導体材料の結晶半導体表面領域を備え、前記結晶半導体表面領域の少なくとも一部分を非晶質化して非晶質表面層を形成する製造方法において、

前記非晶質化は、前記表面への放射パルスの照射を通じて行われ、前記放射パルスは、前記放射パルスの放射が前記結晶表面領域に吸収されるような波長を有し、かつ、前記結晶表面層を溶解するようなエネルギー束を有する、ことを特徴とする製造方法。 - 前記結晶半導体表面領域の溶解した部分が、冷却により凝固して非晶質表面層になった後、ドーパント原子が、イオン注入により前記非晶質表面層に供給されることを特徴とする請求項1に記載の方法。

- 前記ドーパント原子の供給後、前記非晶質表面層が、前記ドーパント原子が活性化する温度まで加熱されることを特徴とする請求項2に記載の方法。

- 前記非晶質表面層が、高速熱アニーリング(RTA)により、前記非晶質半導体材料の融解温度より低い温度まで加熱されて、前記非晶質表面層が再結晶化し、

前記ドーパント原子が、格子サイトに置換的に組み込まれ、これにより前記ドーパント原子が活性化される、ことを特徴とする請求項3に記載の方法。 - 前記非晶質表面層が、レーザーアニーリングにより、前記非晶質半導体材料の前記融解温度より高い温度まで加熱され、その後、前記融解した表面層が再結晶化する温度まで、前記融解した表面層が冷却される、ことを特徴とする請求項3に記載の方法。

- 前記放射パルスは、エキシマーレーザーにより生成されることを特徴とする請求項1に記載の方法。

- 前記表面層は、前記放射パルスのパルス幅およびエネルギー密度により設定された深さまで融解することを特徴とする請求項1または請求項6に記載の方法。

- 前記放射パルスの前記パルス幅は、1nsよりも短いことを特徴とする請求項7に記載の方法。

- 前記放射の前記波長のための吸収層が、照射が行われる前に、前記表面に設けられることを特徴とする請求項1に記載の方法。

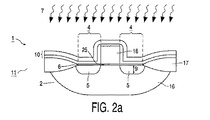

- MOSFETが形成され、

前記非晶質半導体表面層は、前記MOSFETのソースまたはドレインの形成に用いられる、ことを特徴とする請求項1に記載の方法。 - 電気的に活性化したドーパント原子の濃度は、固体溶解限度よりも高いことを特徴とする請求項5に記載の方法。

- 前記請求項のいずれか1つに記載の方法により製造されたことを特徴とする半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP01204625 | 2001-11-30 | ||

| PCT/IB2002/004881 WO2003046967A2 (en) | 2001-11-30 | 2002-11-20 | Method of forming a doped region in a semiconductor body comprising a step of amorphization by irradiation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005510871A true JP2005510871A (ja) | 2005-04-21 |

| JP2005510871A5 JP2005510871A5 (ja) | 2006-01-12 |

Family

ID=8181336

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003548292A Pending JP2005510871A (ja) | 2001-11-30 | 2002-11-20 | 半導体装置の製造方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6982212B2 (ja) |

| EP (1) | EP1459366A2 (ja) |

| JP (1) | JP2005510871A (ja) |

| KR (1) | KR20040054811A (ja) |

| AU (1) | AU2002348835A1 (ja) |

| TW (1) | TWI268576B (ja) |

| WO (1) | WO2003046967A2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009529245A (ja) * | 2006-03-08 | 2009-08-13 | アプライド マテリアルズ インコーポレイテッド | 基板に形成された熱処理構造用の方法および装置 |

| JP2013128030A (ja) * | 2011-12-19 | 2013-06-27 | Sanken Electric Co Ltd | 半導体装置の製造方法、半導体装置 |

| JP2014060423A (ja) * | 2006-03-08 | 2014-04-03 | Applied Materials Inc | 基板に形成された熱処理構造用の方法および装置 |

| WO2018037751A1 (ja) * | 2016-08-25 | 2018-03-01 | パナソニックIpマネジメント株式会社 | 太陽電池セル及びその製造方法 |

| KR20190015262A (ko) * | 2016-05-31 | 2019-02-13 | 레이저 시스템즈 앤드 솔루션즈 오브 유럽 | 디이프 접합 전자 소자 및 그의 제조 공정 |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3737504B2 (ja) * | 2004-03-31 | 2006-01-18 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| FR2870988B1 (fr) * | 2004-06-01 | 2006-08-11 | Michel Bruel | Procede de realisation d'une structure multi-couches comportant, en profondeur, une couche de separation |

| JP2006066686A (ja) * | 2004-08-27 | 2006-03-09 | Matsushita Electric Ind Co Ltd | 不純物導入方法および不純物導入装置 |

| US7091097B1 (en) * | 2004-09-03 | 2006-08-15 | Advanced Micro Devices, Inc. | End-of-range defect minimization in semiconductor device |

| US7615502B2 (en) * | 2005-12-16 | 2009-11-10 | Sandisk 3D Llc | Laser anneal of vertically oriented semiconductor structures while maintaining a dopant profile |

| KR100732630B1 (ko) * | 2006-02-01 | 2007-06-27 | 삼성전자주식회사 | 불순물 도핑 영역을 포함하는 반도체 소자 및 그 형성 방법 |

| US7692275B2 (en) | 2007-02-26 | 2010-04-06 | International Business Machines Corporation | Structure and method for device-specific fill for improved anneal uniformity |

| US20090096066A1 (en) * | 2007-10-10 | 2009-04-16 | Anderson Brent A | Structure and Method for Device-Specific Fill for Improved Anneal Uniformity |

| US7759773B2 (en) * | 2007-02-26 | 2010-07-20 | International Business Machines Corporation | Semiconductor wafer structure with balanced reflectance and absorption characteristics for rapid thermal anneal uniformity |

| US7745909B2 (en) * | 2007-02-26 | 2010-06-29 | International Business Machines Corporation | Localized temperature control during rapid thermal anneal |

| US7679166B2 (en) * | 2007-02-26 | 2010-03-16 | International Business Machines Corporation | Localized temperature control during rapid thermal anneal |

| US8138066B2 (en) | 2008-10-01 | 2012-03-20 | International Business Machines Corporation | Dislocation engineering using a scanned laser |

| CN102421947B (zh) | 2009-03-09 | 2016-09-28 | 1366科技公司 | 从已熔化材料制造薄半导体本体的方法和装置 |

| GB201112610D0 (en) * | 2011-07-22 | 2011-09-07 | Rec Wafer Norway As | Heating a furnace for the growth of semiconductor material |

| US9597744B2 (en) * | 2013-11-11 | 2017-03-21 | Siemens Energy, Inc. | Method for utilizing a braze material with carbon structures |

| DE102016114264A1 (de) * | 2016-08-02 | 2018-02-08 | Infineon Technologies Ag | Herstellungsverfahren einschliesslich einer aktivierung von dotierstoffen und halbleitervorrichtungen mit steilen übergängen |

| CN108807276A (zh) * | 2017-05-05 | 2018-11-13 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| CN112885715A (zh) * | 2021-01-08 | 2021-06-01 | 中国科学院微电子研究所 | 一种半导体器件的制造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4535220A (en) * | 1981-11-10 | 1985-08-13 | The Secretary Of State For Defence In Her Britannic Majesty's Government Of The United Kingdom Of Great Britain And Northern Ireland | Integrated circuits |

| JPH01256124A (ja) * | 1988-04-05 | 1989-10-12 | Ricoh Co Ltd | Mos型半導体装置の製造方法 |

| US5950078A (en) * | 1997-09-19 | 1999-09-07 | Sharp Laboratories Of America, Inc. | Rapid thermal annealing with absorptive layers for thin film transistors on transparent substrates |

| US5953615A (en) * | 1999-01-27 | 1999-09-14 | Advance Micro Devices | Pre-amorphization process for source/drain junction |

| US6777317B2 (en) * | 2001-08-29 | 2004-08-17 | Ultratech Stepper, Inc. | Method for semiconductor gate doping |

-

2002

- 2002-11-20 KR KR10-2004-7008218A patent/KR20040054811A/ko not_active Application Discontinuation

- 2002-11-20 EP EP02781567A patent/EP1459366A2/en not_active Withdrawn

- 2002-11-20 AU AU2002348835A patent/AU2002348835A1/en not_active Abandoned

- 2002-11-20 JP JP2003548292A patent/JP2005510871A/ja active Pending

- 2002-11-20 WO PCT/IB2002/004881 patent/WO2003046967A2/en active Application Filing

- 2002-11-20 US US10/497,263 patent/US6982212B2/en not_active Expired - Fee Related

- 2002-11-26 TW TW091134323A patent/TWI268576B/zh not_active IP Right Cessation

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009529245A (ja) * | 2006-03-08 | 2009-08-13 | アプライド マテリアルズ インコーポレイテッド | 基板に形成された熱処理構造用の方法および装置 |

| JP2014060423A (ja) * | 2006-03-08 | 2014-04-03 | Applied Materials Inc | 基板に形成された熱処理構造用の方法および装置 |

| US10141191B2 (en) | 2006-03-08 | 2018-11-27 | Applied Materials, Inc. | Method of thermal processing structures formed on a substrate |

| US10840100B2 (en) | 2006-03-08 | 2020-11-17 | Applied Materials, Inc. | Method of thermal processing structures formed on a substrate |

| JP2013128030A (ja) * | 2011-12-19 | 2013-06-27 | Sanken Electric Co Ltd | 半導体装置の製造方法、半導体装置 |

| KR20190015262A (ko) * | 2016-05-31 | 2019-02-13 | 레이저 시스템즈 앤드 솔루션즈 오브 유럽 | 디이프 접합 전자 소자 및 그의 제조 공정 |

| JP2019523986A (ja) * | 2016-05-31 | 2019-08-29 | レーザー システムズ アンド ソリューションズ オブ ヨーロッパ | 深い接合の電子装置及びその製造方法 |

| KR102478873B1 (ko) | 2016-05-31 | 2022-12-19 | 레이저 시스템즈 앤드 솔루션즈 오브 유럽 | 디이프 접합 전자 소자 및 그의 제조 공정 |

| WO2018037751A1 (ja) * | 2016-08-25 | 2018-03-01 | パナソニックIpマネジメント株式会社 | 太陽電池セル及びその製造方法 |

| JP2018032786A (ja) * | 2016-08-25 | 2018-03-01 | パナソニックIpマネジメント株式会社 | 太陽電池セル及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1459366A2 (en) | 2004-09-22 |

| TW200409293A (en) | 2004-06-01 |

| KR20040054811A (ko) | 2004-06-25 |

| WO2003046967A2 (en) | 2003-06-05 |

| AU2002348835A1 (en) | 2003-06-10 |

| US20050003638A1 (en) | 2005-01-06 |

| WO2003046967A3 (en) | 2003-10-16 |

| TWI268576B (en) | 2006-12-11 |

| US6982212B2 (en) | 2006-01-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6982212B2 (en) | Method of manufacturing a semiconductor device | |

| JP2005510871A5 (ja) | ||

| US6380044B1 (en) | High-speed semiconductor transistor and selective absorption process forming same | |

| US6365476B1 (en) | Laser thermal process for fabricating field-effect transistors | |

| US6936505B2 (en) | Method of forming a shallow junction | |

| US7825016B2 (en) | Method of producing a semiconductor element | |

| KR100511765B1 (ko) | 소형 집적회로의 제조방법 | |

| KR100879494B1 (ko) | 반도체 게이트의 도핑 방법 | |

| US6645838B1 (en) | Selective absorption process for forming an activated doped region in a semiconductor | |

| JPH0669149A (ja) | 半導体装置の製造方法 | |

| US6555439B1 (en) | Partial recrystallization of source/drain region before laser thermal annealing | |

| US20020192914A1 (en) | CMOS device fabrication utilizing selective laser anneal to form raised source/drain areas | |

| US20070281472A1 (en) | Method of increasing transistor performance by dopant activation after silicidation | |

| US7112499B2 (en) | Dual step source/drain extension junction anneal to reduce the junction depth: multiple-pulse low energy laser anneal coupled with rapid thermal anneal | |

| US20070232033A1 (en) | Method for forming ultra-shallow high quality junctions by a combination of solid phase epitaxy and laser annealing | |

| US7615458B2 (en) | Activation of CMOS source/drain extensions by ultra-high temperature anneals | |

| JP2008510300A (ja) | 極浅接合の形成方法 | |

| CN1316569C (zh) | 低温的掺杂后活化工艺 | |

| US6952269B2 (en) | Apparatus and method for adiabatically heating a semiconductor surface | |

| JP2005101196A (ja) | 半導体集積回路装置の製造方法 | |

| Schmidt et al. | Materials processing | |

| US7091097B1 (en) | End-of-range defect minimization in semiconductor device | |

| JP2002246329A (ja) | 半導体基板の極浅pn接合の形成方法 | |

| JPH0677155A (ja) | 半導体基板の熱処理方法 | |

| KR100680436B1 (ko) | 반도체 소자의 트랜지스터 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051118 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051118 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20080612 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080718 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080805 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081017 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090327 |