JP2005294501A - コネクタ端子を有する電子回路ユニットおよび回路基板 - Google Patents

コネクタ端子を有する電子回路ユニットおよび回路基板 Download PDFInfo

- Publication number

- JP2005294501A JP2005294501A JP2004106890A JP2004106890A JP2005294501A JP 2005294501 A JP2005294501 A JP 2005294501A JP 2004106890 A JP2004106890 A JP 2004106890A JP 2004106890 A JP2004106890 A JP 2004106890A JP 2005294501 A JP2005294501 A JP 2005294501A

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- noise

- frame ground

- connector terminals

- connector terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Shielding Devices Or Components To Electric Or Magnetic Fields (AREA)

- Structure Of Printed Boards (AREA)

Abstract

【課題】 コネクタ端子部の共通フレームグランドを介して、ノイズが他の信号に、または、他の信号のフレームグランドに伝導すること防止する。

【解決手段】 回路素子群が搭載される回路基板10と、外部との接続を行うための、複数のコネクタ端子31−37と、回路基板10に設けられるフレームグランド30とを有する。フレームグランド30は、複数の分離領域31−37に分離された状態で、回路基板10の縁部に沿って配置される。そして、複数の分離領域31−37は、複数のコネクタ端子41−47に対応して、分散して配置される。

【選択図】図1

【解決手段】 回路素子群が搭載される回路基板10と、外部との接続を行うための、複数のコネクタ端子31−37と、回路基板10に設けられるフレームグランド30とを有する。フレームグランド30は、複数の分離領域31−37に分離された状態で、回路基板10の縁部に沿って配置される。そして、複数の分離領域31−37は、複数のコネクタ端子41−47に対応して、分散して配置される。

【選択図】図1

Description

本発明は、コネクタ端子を有する電子回路ユニットおよびそれに用いられる回路基板に係り、特に、それらのノイズを低減する技術に関する。

近年、電子回路基板からの電気的なノイズを低減することが求められている。そのために、電子回路自体にノイズ対策を施した電子回路基板が提案されている。例えば、高周波ノイズを低減するものとして、パワーICにおいて、小信号用の接地とその他の信号用の接地とを区別するという技術が開示されている(特許文献1)。

また、電子回路部品の動作時に電源層とアース層との間で電圧変動が生じることにより放射されるノイズ低減を図るものとして、電源層として、第1、第2の電源分離パターンと、第1、第2のアース層領域とを設け、第1の電源分離パターンの端部と第1のアース分離パターンとを接続する状態でバイパスコンデンサが、また、第2の電源分離パターンの端部と第2のアース分離パターンとを接続する状態でバイパスコンデンサが設けられ、バイパスコンデンサのそれぞれが、第1、第2電源分離パターンの端部に沿って略一定の間隔で配置されている構造としたものが開示されている(特許文献2)。

さらに、電子装置のケーブルから輻射する不要輻射ノイズを低減するものとして、フレームグランドに接地する接地板にケーブルを固定することによって接地するものが開示されている(特許文献3)。

ところで、電子機器において問題となるのは、当該機器内部でのノイズの問題に限られない。すなわち、当該電子機器から他の機器に対してノイズを伝えてしまい、他の機器にノイズの影響を与えてしまうという問題がある。この問題が生ずる原因の1つは、コネクタ端子部の共通フレームグランドを介して、ノイズが伝導すること、または、ノイズが放射されることにある。

しかし、従来、この問題についての対策は採られていない。前述した特許文献1では、電子回路基板に搭載される内部回路における設置の問題を扱っている。また、特許文献2では、回路基板における電源層とアース層との間での電圧変動の影響を除去するという問題を扱っている。従って、いずれも、コネクタ端子部の共通フレームグランドを介したノイズを漏洩するための技術を示すものではない。

一方、特許文献3では、ケーブルから輻射するノイズを低減するものである。しかし、ケーブルを接地板に接触させて、フレームグランドに接触させるに過ぎない。これによっても、もちろんある程度のノイズの漏洩を防ぐことができる。

しかし、近年、外部に漏洩する電磁ノイズをできる限り低減することが求められており、この特許文献3の対策では十分ではない。もちろん、ノイズを低減させることは技術的に不可能ではない。しかし、コストをかけずにノイズを低減することは必ずしも容易ではない。

本発明は、コネクタ端子を介して外部に漏洩されるノイズを低減する技術を提供することを目的とする。

本発明は、コネクタ端子部のフレームグランドを介して、ノイズが他の信号に、または、他の信号のフレームグランドに伝導することを防止する技術を提供することを目的とする。

本発明の第1の態様によれば、回路素子群が搭載され、電子機器の筐体に収容される電子回路ユニットにおいて、

前記回路素子群が搭載される回路基板と、

外部との接続を行うための、複数のコネクタ端子と、

前記回路基板に設けられるフレームグランドと、を有し、

前記フレームグランドは、複数の分離領域に分離された状態で、前記回路基板の縁部に沿って配置され、かつ、前記複数の分離領域は、複数のコネクタ端子に対応して、分散して配置されることを特徴とする電子回路ユニットが提供される。

前記回路素子群が搭載される回路基板と、

外部との接続を行うための、複数のコネクタ端子と、

前記回路基板に設けられるフレームグランドと、を有し、

前記フレームグランドは、複数の分離領域に分離された状態で、前記回路基板の縁部に沿って配置され、かつ、前記複数の分離領域は、複数のコネクタ端子に対応して、分散して配置されることを特徴とする電子回路ユニットが提供される。

また、本発明の他の態様によれば、回路素子群およびコネクタ端子を搭載するための回路基板において、

フレームグランドを有し、

前記フレームグランドは、複数の分離領域に分離された状態で、当該回路基板の縁部に沿って配置され、かつ、前記複数の分離領域は、複数のコネクタ端子に対応して、分散して配置されること

を特徴とする回路基板が提供される。

フレームグランドを有し、

前記フレームグランドは、複数の分離領域に分離された状態で、当該回路基板の縁部に沿って配置され、かつ、前記複数の分離領域は、複数のコネクタ端子に対応して、分散して配置されること

を特徴とする回路基板が提供される。

本発明によれば、コネクタ端子部のフレームグランドを介して、ノイズが他の信号に、または、他の信号のフレームグランドに伝導することを防止することができる。

以下、本発明の実施形態について図面を参照して説明する。

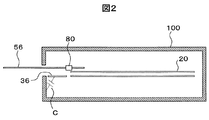

図1は、本発明の第1の実施形態における回路基板の構成を示す平面図である。また、図2に、図1に示す回路基板に他の回路部品等搭載して、電子回路ユニットとして、筐体に収容した状態を示す。

図1に示す本発明の一実施形態に係る回路基板10は、絶縁層11を有し、図2に示す筐体100に収容される。絶縁層11は、例えば、ポリイミド、ガラスエポキシ樹脂等により構成される。一般的には複数層が積層され、各層に、銅等の金属により構成される導体配線が配置される。また、回路基板10には、コネクタ端子群40が設けられる。

コネクタ端子群40には、AC入力用の電源用コネクタ端子41、接点出力用コネクタ端子42、ライン用コネクタ端子43、電話用コネクタ端子44、LAN用コネクタ端子46等の複数のコネクタ端子41−47が含まれる。コネクタ端子41には、電源線51が、また、他のコネクタ端子42−47には、それぞれ信号線52−57が接続される。

回路基板10には、導体層として、1乃至複数層の電源/グランドパターン20と、フレームグランド30とが、予め定められたパターンにより設けられる。また、この他に、図示していないが、信号伝送のための配線パターンが異なる絶縁層上に設けられる。この回路基板10に、図示していない各種回路素子が搭載され、また、コネクタ端子群40が配置されている。

フレームグランド30は、絶縁層11の縁部、すなわち、回路基板10が筐体100に収容された際に、コネクタ端子群30と近接する部分に、コネクタ端子群30の配列に対応して配置される。また、フレームグランド30は、間隙部S1からS6を挟んで、複数の分離領域31−37に分離されて設けられる。本実施形態の場合、コネクタ端子群40を構成する各コネクタ端子41−47に対応して分散配置される。具体的には、一対一対応に設けられる。このフレームグランド30は、電源/グランドパターン20と同様の導体により、同様の製造プロセス、例えば、フォトエッチングプロセス等を経て設けることができる。

なお、分離領域31−37の全部または一部については、分離せずに設け、実装時に、導体を切削して間隙部S1からS6を設けることにより、分離するようにしてもよい。また、予め設けた各間隙部S1−S6において、分離領域31−37の隣接する領域について、それぞれ、導電性のフィルム、導体片等の短絡部材により接続して、電気的に一体化しておく。その上で、必要に応じて短絡部材を剥離する等により除去して、間隙部による分離を有効とする構成としてもよい。

各分離領域31−37の大きさは、そもそも、グランドとして機能するために、ある程度の面積が必要である。一方、それらが配置される領域等の事情により、その大きさには制約がある。例えば、それぞれが対応するコネクタ端子41−47の大きさ、コネクタ端子配列密度、間隙部S1−S6の間隔等に応じて大きさが制限される。

ここで、間隙部幅、すなわち、間隙部Sを挟む導体間の距離について検討する。間隙部幅は、低減すべきノイズの大きさに応じて定まる。例えば、VCCI(情報処理等電波自主規制協議会)のクラスB規制値では、次のようになる。

150kHzから30MHzの範囲でのノイズである伝導ノイズについては、

伝導ノイズ:(46dBμV〜67dBμV)

(200μV)〜(2.2mV)

となる。そして、この場合には、間隙部幅、すなわち、分離領域31−37の隣接する領域間の間隔は、2から3mm程度であればよい。

伝導ノイズ:(46dBμV〜67dBμV)

(200μV)〜(2.2mV)

となる。そして、この場合には、間隙部幅、すなわち、分離領域31−37の隣接する領域間の間隔は、2から3mm程度であればよい。

また、30MHzから1GHzの範囲での電波ノイズ(放射ノイズ)については、

電波ノイズ:40〜47dBμV/m

(100μV/m)〜(220μV/m)

となる。そして、この場合には、間隙部幅は、1から2mm程度であればよい。

電波ノイズ:40〜47dBμV/m

(100μV/m)〜(220μV/m)

となる。そして、この場合には、間隙部幅は、1から2mm程度であればよい。

一方、間隙部S1−S6のそれぞれの幅は、広いほどノイズの低減性能が向上する。例えば、ノイズレベルが前述した規制値を10%程度超えるような場合、当該部位における間隙部幅を10%広くすることにより、規制値に抑え込めるようにすることができる。

上述した回路基板は、コネクタ端子群30を取り付け、かつ、図示していない回路素子群を搭載して、筺体100に収容する。図2においては、筺体100を分離領域36において、切断した状態を示す。図2では、コネクタ端子の構造部についての図示は省略して、信号線56のみを示している。

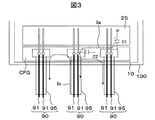

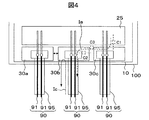

次に、本発明によるノイズ抑止の原理について、図3および図4を参照して説明する。図3に、フレームグランドを共通フレームグランドとした場合を示す。また、図4に、フレームグランドに、本発明を適用して複数の分離領域に分離したものを用いた場合を示す。いずれの場合も、信号グランドのP部に、局所的にノイズ電圧が発生した場合を例として説明する。なお、説明の便宜のため、図1に示す回路基板より簡単な回路構成としてある。

(信号グランドノイズ電流が他の信号線に伝導する場合)

図3に示す共通フレームグランドを用いた回路では、信号グランド25のP部に局所的に発生したノイズ電圧が、ノイズ電流Iaとして、容量C1、C2を通って、信号ケーブル90の信号線91に伝導する。その結果、このノイズ電流に起因して、外部に放射ノイズを発生させ、EMI特性を低下させる。ここで、C1は、信号グランド25と共通フレームグランドCFGとの間の浮遊容量である。また、C2は、共通フレームグランドCFGと信号線91との間の浮遊容量である。

(信号グランドノイズ電流が他の信号線に伝導する場合)

図3に示す共通フレームグランドを用いた回路では、信号グランド25のP部に局所的に発生したノイズ電圧が、ノイズ電流Iaとして、容量C1、C2を通って、信号ケーブル90の信号線91に伝導する。その結果、このノイズ電流に起因して、外部に放射ノイズを発生させ、EMI特性を低下させる。ここで、C1は、信号グランド25と共通フレームグランドCFGとの間の浮遊容量である。また、C2は、共通フレームグランドCFGと信号線91との間の浮遊容量である。

信号グランドのような平板導体の場合、ノイズの平行平板共振によって、強度が局部的大きくなる部分(例えば、P部)が発生する。このようなノイズは、数百メガヘルツと高周波のため、容量C1、C2を通りやすく、外部に伝導しやすい。フレームグランドが共通の場合に、このノイズがすべての信号にのる可能性がある。この場合、ほとんどすべての信号についてフィルタを入れることによって対処することも考えられるが、ノイズ対策が複雑となる。

なお、局部的ノイズとしては、他にLSIの電源電流ノイズ等が考えられる。

これに対して、本発明を適用して、フレームグランドを複数の分離領域30aから30cに分離した場合、図4に示すように、各分離領域30aと30bとの間、30bと30cとの間が、直流的には非導通となる。一方、高周波的にも、浮遊容量C3を小さくすることができることから、ここを通るノイズ電流を小さくすることができる。その結果、ノイズが他の部分に拡散することを防止することができるため、一部の信号についてフィルタを入れるだけで対処することが可能となる。従って、ノイズ対策が非常に簡便なものとなる。

(外部信号のフレームグランドノイズ電流が他の信号のケーブルフレームグランド95または他の信号ラインに伝導する場合)

他の信号のケーブルフレームグランド95または他の信号ラインに伝導したノイズ電流Icは、伝導ノイズまたは放射ノイズとなり、EMI特性を低下させる。フレームグランドが共通の場合、このノイズがすべての信号にのる可能性がある。そのため、すべての信号についてフィルタを入れるなどの対策が必要となる。

(外部信号のフレームグランドノイズ電流が他の信号のケーブルフレームグランド95または他の信号ラインに伝導する場合)

他の信号のケーブルフレームグランド95または他の信号ラインに伝導したノイズ電流Icは、伝導ノイズまたは放射ノイズとなり、EMI特性を低下させる。フレームグランドが共通の場合、このノイズがすべての信号にのる可能性がある。そのため、すべての信号についてフィルタを入れるなどの対策が必要となる。

しかし、本発明の場合、フレームグランンドが複数に分離されているため、前述した理由から、ノイズ電流Icがフレームグランド30bから他のフレームグランド(例えば、30a)に流れることがなくなる。そのため、すべてのフレームグランドにノイズがのるという事態になることが避けられる。そのため、一部の信号についてのみノイズ対策をすれば足り、対策が簡便になる。

なお、以上に述べた本発明が解決しようとする課題は、フレームグランドが筐体に対して浮いている場合でも、また、筐体と接続されている場合でも、同じである。

次に、本発明の他の実施形態について図5を参照して説明する。図5に示す実施形態は、分離領域の一つである分離領域38を、複数(図5の例では2個)コネクタ端子46、47に対応させたものである。この実施形態の場合でも、前述した実施形態と同様に、間隙部幅を決定することができる。そして、同様の原理により、ノイズ電流の漏洩を低減することができる。

10…回路基板、11…絶縁層、20…電源/グランドパターン、25…信号グランド、30…フレームグランド、31−37…分離領域、40…コネクタ端子群、41−47…コネクタ端子、51…電源線、52−57…信号線、100…筐体。

Claims (6)

- 回路素子群が搭載され、電子機器の筐体に収容される電子回路ユニットにおいて、

前記回路素子群が搭載される回路基板と、

外部との接続を行うための、複数のコネクタ端子と、

前記回路基板に設けられるフレームグランドと、を有し、

前記フレームグランドは、複数の分離領域に分離された状態で、前記回路基板の縁部に沿って配置され、かつ、前記複数の分離領域は、複数のコネクタ端子に対応して、分散して配置されること

を特徴とする電子回路ユニット。 - 請求項1に記載の電子回路ユニットにおいて、

前記分離領域は、前記筐体の接地点に対して浮いた状態におかれることを特徴とする電子回路ユニット。 - 請求項1および2のいずれか一項に記載の電子回路ユニットにおいて、

前記分離領域のいずれかは、前記複数のコネクタ端子のうち、2以上のコネクタ端子に対応して配置されることを特徴とする電子回路ユニット。 - 回路素子群およびコネクタ端子を搭載するための回路基板において、

フレームグランドを有し、

前記フレームグランドは、複数の分離領域に分離された状態で、当該回路基板の縁部に沿って配置され、かつ、前記複数の分離領域は、複数のコネクタ端子に対応して、分散して配置されること

を特徴とする回路基板。 - 請求項4に記載の回路基板において、

前記各分離領域は、接地点に対する導通しない状態に形成されることを特徴とする回路基板。 - 請求項4および5のいずれか一項に記載の回路基板において、

前記分離領域のいずれかは、前記複数のコネクタ端子のうち、2以上のコネクタ端子に対応して配置されることを特徴とする回路基板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004106890A JP2005294501A (ja) | 2004-03-31 | 2004-03-31 | コネクタ端子を有する電子回路ユニットおよび回路基板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004106890A JP2005294501A (ja) | 2004-03-31 | 2004-03-31 | コネクタ端子を有する電子回路ユニットおよび回路基板 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294501A true JP2005294501A (ja) | 2005-10-20 |

Family

ID=35327100

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004106890A Pending JP2005294501A (ja) | 2004-03-31 | 2004-03-31 | コネクタ端子を有する電子回路ユニットおよび回路基板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294501A (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0927692A (ja) * | 1995-07-12 | 1997-01-28 | Oki Inf Syst | インタフェース構造 |

| JPH11259172A (ja) * | 1998-03-06 | 1999-09-24 | Canon Inc | 電子機器 |

| JP2001148277A (ja) * | 1999-11-22 | 2001-05-29 | Sharp Corp | 雷サージ電圧吸収回路を備えた電源回路 |

| JP2003283177A (ja) * | 2002-03-27 | 2003-10-03 | Yaskawa Electric Corp | 電子装置の放射ノイズ低減装置 |

-

2004

- 2004-03-31 JP JP2004106890A patent/JP2005294501A/ja active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0927692A (ja) * | 1995-07-12 | 1997-01-28 | Oki Inf Syst | インタフェース構造 |

| JPH11259172A (ja) * | 1998-03-06 | 1999-09-24 | Canon Inc | 電子機器 |

| JP2001148277A (ja) * | 1999-11-22 | 2001-05-29 | Sharp Corp | 雷サージ電圧吸収回路を備えた電源回路 |

| JP2003283177A (ja) * | 2002-03-27 | 2003-10-03 | Yaskawa Electric Corp | 電子装置の放射ノイズ低減装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5488540A (en) | Printed circuit board for reducing noise | |

| CA2146139C (en) | Electromagnetic radiation reduction technique using grounded conductive traces circumscribing internal planes of printed circuit boards | |

| KR101999509B1 (ko) | 회로 기판 | |

| JP2000286587A (ja) | 外部ケーブル接続用コネクタ部の電磁シールド構造 | |

| JP5147501B2 (ja) | 車載電子装置 | |

| KR20200014231A (ko) | 회로 기판 및 이를 포함하는 전자 기기 | |

| WO2012039120A4 (en) | Printed circuit board | |

| JP6843312B1 (ja) | 回路基板及び電子機器 | |

| US7939766B2 (en) | Apparatus for electromagentically shielding a portion of a circuit board | |

| JP2005294511A (ja) | コネクタ端子を有する電子回路ユニットおよび回路基板 | |

| JPH09232014A (ja) | インタフェースケーブル接続用コネクタ | |

| US8208271B2 (en) | Printed board and image formation apparatus | |

| JP5320801B2 (ja) | 電子機器及びそのノイズ遮蔽方法 | |

| JP2005294501A (ja) | コネクタ端子を有する電子回路ユニットおよび回路基板 | |

| JP2005294502A (ja) | コネクタ端子を有する電子回路ユニットおよび回路基板 | |

| KR100512738B1 (ko) | 인쇄회로기판 및 이를 사용하는 전자기기 | |

| JP2008172280A (ja) | コネクタ端子を有する電子回路ユニットおよび回路基板 | |

| JP3678658B2 (ja) | Emi対策用電源ケーブルコネクタ | |

| JPH11284291A (ja) | 回路基板およびこの回路基板を搭載した液晶表示装置 | |

| US20130265675A1 (en) | Digital protective relay | |

| JPH0515317B2 (ja) | ||

| JP2006261470A (ja) | 多層プリント回路基板 | |

| JP5398888B2 (ja) | 電子機器 | |

| JP5183390B2 (ja) | 電子機器 | |

| JP2001326468A (ja) | 多層プリント配線板及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060922 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061003 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070213 |