JP2005294418A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2005294418A JP2005294418A JP2004105182A JP2004105182A JP2005294418A JP 2005294418 A JP2005294418 A JP 2005294418A JP 2004105182 A JP2004105182 A JP 2004105182A JP 2004105182 A JP2004105182 A JP 2004105182A JP 2005294418 A JP2005294418 A JP 2005294418A

- Authority

- JP

- Japan

- Prior art keywords

- impurity

- region

- semiconductor device

- capacitor

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Liquid Crystal (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Abstract

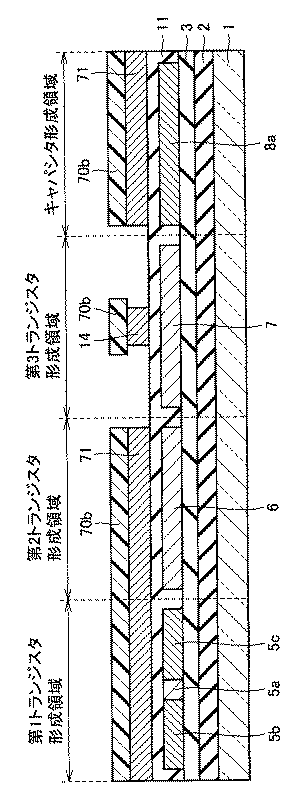

【解決手段】 本発明の半導体装置100は、n型TFT30とキャパシタ60とを備えた半導体装置であって、n型TFT30はソース領域30aおよびドレイン領域30bを有している。ソース領域30aおよびドレイン領域30bの各々は、n型TFT30のゲート電極12の真下に形成された第1不純物領域5b,5cと、第1不純物領域5b,5cの不純物濃度よりも高い不純物濃度を有する第2不純物領域5f,5gとを有している。第1不純物領域5b,5cの不純物濃度とキャパシタ60の一方電極8aの不純物濃度とが同じである。

【選択図】 図1

Description

図1は、本発明の実施の形態1における半導体装置の構成を示す断面図である。

μmである。第3の不純物領域5d,5eの各々の不純物濃度は第1不純物領域5b,5cの各々の不純物濃度よりも高く、第2の不純物領域5g,5fの各々の不純物濃度は第3不純物領域5d,5eの各々の不純物濃度よりも高い。第1不純物領域5b,5cの各々はゲート電極12の真下に形成されている。すなわち、チャネル形成領域5aと、第1不純物領域5b,5cの各々とをゲート絶縁膜となるSiO2膜11を介して覆うように、n型TFT30のゲート電極12が形成されている。なお、第1不純物領域5b,5cの不純物濃度は1017原子/cm3以上1019原子/cm3以下であることが好ましい。

その後、アッシングと薬液処理によりレジスト70aを除去する。

図11は、本発明の実施の形態2における半導体装置の構成を示す断面図である。

本実施例においては、まず、図1に示す実施の形態1の半導体装置100を製造した。半導体装置100におけるn型TFT30のチャネル幅を10μmとし、チャネル長は5μmとした。また、第1不純物領域5b,5cのチャネル長方向の長さを1μmとし、第3不純物領域5d,5eのチャネル長方向の長さを0.5μmとした。また、ゲート電極12のチャネル長方向の長さを7μmとした。

2.2×10-4Aとなっている。このことから、本発明のn型TFT30のオン電流はLDD構造のTFTのオン電流とほぼ同様の値となっていることが分かる。

本実施例においては、第1不純物領域5b,5cおよび下部電極8aの不純物濃度をそれぞれ5×1017原子/cm3,1×1018原子/cm3,2×1018原子/cm3と変化させて図1に示す実施の形態1の半導体装置100を製造した。そして、それぞれの半導体装置100についてキャパシタ60のフラットバンド電圧を測定した。この結果を表2に示す。なお、表2のフラットバンド電圧は、下部電極8aの電位に対する上部電極15の電位で示されている。

本実施例においては、第1不純物領域5b,5cおよび下部電極8aの不純物濃度をそれぞれ5×1016原子/cm3、1×1017原子/cm3、5×1017原子/cm3と変化させて図1に示す実施の形態1の半導体装置100を製造した。そして、それぞれの半導体装置100のn型TFT30について、実施例1と同様の方法により耐圧を測定した。この結果を表3に示す。

Claims (11)

- トランジスタとキャパシタとを備えた半導体装置であって、

前記トランジスタはソース領域およびドレイン領域を有し、

前記ソース領域および前記ドレイン領域の各々は、前記トランジスタのゲート電極の真下に形成された前記第1不純物領域と、前記第1不純物領域の不純物濃度よりも高い不純物濃度を有する第2不純物領域とを有し、

前記第1不純物領域の不純物濃度と前記キャパシタの一方電極の不純物濃度とが同じであることを特徴とする、半導体装置。 - 前記トランジスタは第3不純物領域をさらに有し、

前記第3の不純物領域は前記第1不純物領域と前記第2不純物領域との間に形成されており、

前記第3不純物領域の不純物濃度は、前記第1不純物領域の不純物濃度よりも高く、前記第2の不純物領域の不純物濃度よりも低いことを特徴とする、請求項1に記載の半導体装置。 - 前記第1不純物領域の不純物濃度と同じ不純物濃度である前記一方電極の電位よりも前記キャパシタの他方電極の電位の方が常に高いことを特徴とする、請求項1または2に記載の半導体装置。

- 前記キャパシタの前記一方電極または他方電極と画素電極とは電気的に接続されていることを特徴とする、請求項1〜3のいずれかに記載の半導体装置。

- 前記トランジスタはnチャネル型トランジスタであることを特徴とする、請求項1〜4のいずれかに記載の半導体装置。

- 前記第1不純物領域の不純物濃度は1017原子/cm3以上1019原子/cm3以下であることを特徴とする、請求項1〜5のいずれかに記載の半導体装置。

- 第1トランジスタとキャパシタとを備えた半導体装置の製造方法であって、

第1トランジスタ形成領域とキャパシタ形成領域とを有する半導体膜を基板上に形成する工程と、

第1不純物濃度を有する1対の第1不純物領域を前記半導体膜の前記第1トランジスタ形成領域に形成する工程と、

前記1対の第1不純物領域の間に挟まれるチャネル形成領域と、前記1対の第1不純物領域の各々の一部とを第1絶縁膜を介して覆うように、前記第1トランジスタの第1ゲート電極を前記半導体膜上に形成する工程と、

前記第1不純物領域よりも不純物濃度の高い第2不純物濃度を有する1対の第2不純物領域を前記第1ゲート電極の真下を除く第1不純物領域内に形成する工程とを備え、

前記1対の第1不純物領域を形成する工程と同一の工程により、前記第1不純物濃度を有する前記キャパシタの一方電極が前記半導体膜に形成されることを特徴とする、半導体装置の製造方法。 - 前記第1不純物領域よりも不純物濃度が高く、前記第2不純物領域よりも不純物濃度が低い第3不純物濃度を有する1対の第3不純物領域を前記第1不純物領域と前記第2不純物領域との間に形成する工程をさらに備えることを特徴とする、請求項7に記載の半導体装置の製造方法。

- 前記第1ゲート電極を形成する工程は、

前記半導体膜の前記第1トランジスタ形成領域上に前記第1絶縁膜を介して第1導電膜を形成する工程と、

前記チャネル形成領域と、前記1対の第1不純物領域の各々の一部とを覆うように、第1レジストを前記第1導電膜上に形成する工程と、

前記第1レジストをマスクとして、前記第1レジストよりも線幅が細くなるように前記第1導電膜をエッチングする工程とを含み、

前記第1レジストをマスクとして不純物を注入することにより前記第2不純物濃度を有する前記1対の第2不純物領域が前記第1不純物領域内に形成され、

前記第1のゲート電極をマスクとして不純物を注入することにより前記1対の第3不純物領域が形成されることを特徴とする、請求項8に記載の半導体装置の製造方法。 - 第2トランジスタを形成する工程をさらに備え、

前記第2トランジスタを形成する工程は、

前記第1導電膜を形成する工程と同一の工程により、前記第2トランジスタ形成領域をさらに有する前記半導体膜の前記第2トランジスタ形成領域上に第2絶縁膜を介して第2導電膜を形成する工程と、

第1レジストを形成する工程と同一の工程により、第2レジストを前記第2導電膜上に形成する工程と、

前記第1導電膜をエッチングする工程と同一の工程により、前記第2レジストをマスクとして、前記第2レジストよりも線幅が細くなるように前記第2導電膜をエッチングする工程と、

前記1対の第2不純物領域を形成する工程と同一の工程により、前記第2レジストをマスクとして不純物を注入することにより第4不純物濃度を有する1対の第4不純物領域を前記半導体層の前記第2トランジスタ形成領域に形成する工程と、

前記1対の第3不純物領域を形成する工程と同一の工程により、前記第2導電層をマスクとして不純物を注入することにより第5の不純物濃度を有する1対の第5不純物領域を形成する工程とを含むことを特徴とする、請求項9に記載の半導体装置の製造方法。 - 前記第1ゲート電極を形成する工程と同一の工程により、前記キャパシタの他方電極が形成されることを特徴とする、請求項7〜10のいずれかに記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105182A JP2005294418A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105182A JP2005294418A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置およびその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294418A true JP2005294418A (ja) | 2005-10-20 |

Family

ID=35327036

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004105182A Pending JP2005294418A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294418A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008015454A (ja) * | 2006-06-30 | 2008-01-24 | Lg Phillips Lcd Co Ltd | 液晶表示装置及びその製造方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001024196A (ja) * | 1999-07-05 | 2001-01-26 | Semiconductor Energy Lab Co Ltd | 電気光学装置の作製方法 |

| JP2002006340A (ja) * | 2000-06-26 | 2002-01-09 | Seiko Epson Corp | 液晶装置およびその製造方法ならびに電子機器 |

| JP2003149675A (ja) * | 2001-11-15 | 2003-05-21 | Hitachi Ltd | 液晶表示装置 |

-

2004

- 2004-03-31 JP JP2004105182A patent/JP2005294418A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001024196A (ja) * | 1999-07-05 | 2001-01-26 | Semiconductor Energy Lab Co Ltd | 電気光学装置の作製方法 |

| JP2002006340A (ja) * | 2000-06-26 | 2002-01-09 | Seiko Epson Corp | 液晶装置およびその製造方法ならびに電子機器 |

| JP2003149675A (ja) * | 2001-11-15 | 2003-05-21 | Hitachi Ltd | 液晶表示装置 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008015454A (ja) * | 2006-06-30 | 2008-01-24 | Lg Phillips Lcd Co Ltd | 液晶表示装置及びその製造方法 |

| US8269907B2 (en) | 2006-06-30 | 2012-09-18 | Lg Display Co., Ltd. | Liquid crystal display device and method for fabricating the same |

| KR101250789B1 (ko) * | 2006-06-30 | 2013-04-08 | 엘지디스플레이 주식회사 | 액정표시장치의 제조방법 |

| US8665386B2 (en) | 2006-06-30 | 2014-03-04 | Lg Display Co., Ltd. | Liquid crystal display device and method for fabricating the same |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2666103B2 (ja) | 薄膜半導体装置 | |

| US10468533B2 (en) | Semiconductor device and method for manufacturing same | |

| CN101924111B (zh) | 半导体器件和制造半导体器件的方法 | |

| US7700995B2 (en) | Semiconductor device and display device | |

| JP2009290211A (ja) | 半導体素子及びその製造方法 | |

| CN1909249B (zh) | 具有薄膜晶体管的半导体器件及其制造方法 | |

| CN100495730C (zh) | 半导体器件以及图像显示装置 | |

| JP3296975B2 (ja) | 薄膜トランジスタ及びその製造方法 | |

| JPH10256554A (ja) | 薄膜トランジスタ及びその製造方法 | |

| JP2005228819A (ja) | 半導体装置 | |

| US8513766B2 (en) | Semiconductor device having a drain-gate isolation portion | |

| JP2004040108A (ja) | Ldd構造を有する薄膜トランジスタとその製造方法 | |

| JP2005311037A (ja) | 半導体装置およびその製造方法 | |

| JP2005333107A (ja) | 半導体装置、画像表示装置および半導体装置の製造方法 | |

| JPH098314A (ja) | 薄膜トランジスタ | |

| JPH05275701A (ja) | 薄膜トランジスタ | |

| US20100207120A1 (en) | Production method of semiconductor device and semiconductor device | |

| JP2005294418A (ja) | 半導体装置およびその製造方法 | |

| TW200417035A (en) | TFT structure with LDD region and manufacturing process of the same | |

| JP5414712B2 (ja) | 半導体装置 | |

| JP3398665B2 (ja) | 薄膜トランジスタの製造方法 | |

| JP4342191B2 (ja) | 薄膜トランジスタを備えた装置及びその製造方法 | |

| US8124979B2 (en) | Thin film transistor and method of manufacturing the same | |

| JP2014033136A (ja) | 表示装置およびその製造方法 | |

| KR101385471B1 (ko) | 박막 트랜지스터 및 그 제조 방법과, 그를 이용한 액정표시 장치 및 유기 발광 다이오드 표시 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061005 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090903 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090908 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091106 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100330 |