JP2005294326A - 光起電力素子及びその製造方法 - Google Patents

光起電力素子及びその製造方法 Download PDFInfo

- Publication number

- JP2005294326A JP2005294326A JP2004103385A JP2004103385A JP2005294326A JP 2005294326 A JP2005294326 A JP 2005294326A JP 2004103385 A JP2004103385 A JP 2004103385A JP 2004103385 A JP2004103385 A JP 2004103385A JP 2005294326 A JP2005294326 A JP 2005294326A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- sccm

- conversion efficiency

- photoelectric conversion

- photovoltaic element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/545—Microcrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/546—Polycrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/548—Amorphous silicon PV cells

Landscapes

- Photovoltaic Devices (AREA)

Abstract

【課題】 非晶質シリコンを用いた光起電力素子の光劣化後の光電変換効率を向上させる。

【解決手段】 Siを主構成元素とする多結晶、微結晶または非晶質半導体をi層に含むpin接合を少なくとも一組有する光起電力素子において、該光起電力素子の初期光電変換効率をダイオードリーク電流により2%以上9%以下低下させたことを特徴とする。

【選択図】 図6−1

【解決手段】 Siを主構成元素とする多結晶、微結晶または非晶質半導体をi層に含むpin接合を少なくとも一組有する光起電力素子において、該光起電力素子の初期光電変換効率をダイオードリーク電流により2%以上9%以下低下させたことを特徴とする。

【選択図】 図6−1

Description

本発明は、主として多結晶、微結晶または非晶質半導体を光活性層に用いた光起電力素子の信頼性と変換効率の向上に関する。

従来、光起電力素子には単結晶、多結晶を用いた系が用いられてきた。特に、単結晶シリコンでは変換効率が20%を超えるものも登場し、太陽光発電システムが一般住宅にも普及し始めている。しかしながら、太陽電池市場の拡大に伴い、生産コスト低減の面から非晶質を用いた光起電力素子への期待が高まり種々の作製方法が検討されてきた。

半導体装置に使われる非晶質シリコン、微結晶シリコン、あるいは多結晶シリコンの堆積方法としては、シランSiH4またはジシランSi2H6を成膜ガスとするRFプラズマCVD法やマイクロ波プラズマCVD法、などが用いられてきた。実験的にはこの他にも光CVD法、ECRCVD法、水素原子存在下でのシリコンの真空蒸着法などがある。このような非晶質シリコン、微結晶シリコンの作製法でもっとも普及しているのはプラズマCVD法である。シランSiH4、ジシランSi2H6、四フッ化珪素SiF4を材料ガスとして用い、必要に応じて水素ガスで希釈を行い、13.56MHzの高周波でプラズマを発生させ、プラズマにより成膜ガスを分解して反応性のある活性種をつくり、基板上に膜を堆積させる。また、成膜ガスに、ホスフィン(PH3),ジボラン(B2H6)、BF3などのドーピングガスを混ぜれば、n型半導体、p型半導体が形成できる。

さらに、シャントパスによる特性低下を防止するため、金属層(裏面電極)と半導体層の間に導電性を示す透光性の材料による層、即ち透明導電性層を設けることが行なわれている。

非晶質シリコン光起電力素子の場合、光を照射すると変換効率が悪くなってしまう。光を照射すると、生成された光キャリアの再結合中心となるシリコンダングリングボンドが増加してしまう。そのため、太陽光の下に長く置くと光起電力素子の変換効率が低下してしまう。これに対して、光劣化の少ない系として微結晶シリコンの開発が進められてきた。しかし、アモルファス微結晶中のアモルファス相の光劣化など問題も抱えている。

光起電力素子の場合、信頼性の観点から光劣化以外にpn間のシャント抵抗が問題となる。特に、シャント抵抗が大きく下がると、光電変換効率が低下し、また実用上光起電力素子の耐電圧が低下するという問題がある。特許文献1にあるようにシャント抵抗は1kΩ・cm2から500kΩ・cm2で高ければ高いほど信頼性は向上し光電変換効率が良いとされている。また、特許文献2にみられる光起電力素子も2kΩ・cm2から200kΩ・cm2なる値を代表値としてあげている。また、シャントに関連して特許文献3では光起電力素子内部のピンホールに注目している。ピンホールの直径d[μm]とその密度N個/cm2との関係がd2×N≦1.5×104であるように規定している。

非晶質シリコンの場合、光劣化は、光生成キャリアが、半導体膜中で再結合することにより、ダングリングボンドを生成すると考えられ、そのメカニズムについては諸説唱えられている。また、光劣化のない系として微結晶シリコンを用いることも大いに検討されている。完全な非晶質でなく、非晶質相と微結晶相の両者を含むことを特徴とする微結晶シリコンの開発も行われている。微結晶シリコンでは、バンドギャップが1.1eV程度であり、非晶質シリコンのバンドギャップ約1.7eVよりも小さい。そのため、光起電力素子において、i層を二層以上組み合わせて作製するスタック型光起電力素子のボトムまたはミドル用の光起電力素子として微結晶シリコンは期待されている。

しかし、微結晶シリコンは、結晶相と非晶質相の混合であるから、光が照射されたとき生成されたキャリアは、結晶相中を走行するときの移動度に比べ、非晶質相を走行するときの移動度が光劣化により悪化することが問題となっている。微結晶シリコンでは、結晶粒の界面もしくは結晶粒の周りの非晶質領域で光劣化が生じていると考えられる。そのため、非晶質シリコンの場合と同様に光劣化の低減対策をとる必要がある。

非晶質シリコンの光劣化は、ステブラーロンスキー効果と言われる光誘起の可逆現象である。光起電力素子の短絡電流は、電子−正孔対の生成効率、ドリフト移動度、キャリアの寿命で決まるが、光照射によってキャリアの寿命が、大きく減少することがわかっている。これらは、微結晶シリコン内の非晶質領域にも当てはまり非晶質シリコンと同様の特性の光劣化現象が起こる。

現象論的には、ステブラーロンスキー効果の原因となる準安定ダングリングボンドは、光によって励起された電子−正孔対の直接的および間接的な非輻射再結合あるいはどちらか一方のキャリアのトラッピングによって誘起される。本発明では、ステブラロンスキー効果を抑制し、非晶質シリコン、微結晶シリコン、多結晶シリコンの光劣化後の光電変換効率を向上させることを目的とする。

本発明は上記目的を達成するために、光劣化現象とリーク電流に着目して鋭意検討した結果完成に至ったものであり、その骨子とするところは、Siを主構成元素とする多結晶、微結晶または非晶質半導体をi層に含むpin接合を少なくとも一組有する光起電力素子において、該光起電力素子の初期光電変換効率をダイオードリーク電流により2%以上9%以下低下させたことを特徴とする光起電力素子である。

また、本発明は、Siを主構成元素とする多結晶、微結晶または非晶質半導体をi層に含むpin接合を有する光起電力素子を酸性水溶液中に浸漬し該光起電力素子のp層側に電圧を印加する工程において、前記光起電力素子のダイオードリーク電流による初期光電変換効率の低下率が2%以上9%以下になるように条件を制御することを特徴とする光起電力素子の製造方法である。なお、前記制御は、前記印加電圧の波形を変化させることにより行なうことが好ましい。

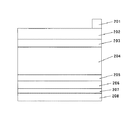

一般的な光起電力素子は図2のように集電電極201、透明電極202、p型半導体層203、i型半導体層204、n型半導体層205、透明導電層206、裏面電極207、導電性基板208からなっている。図2のような構成をとる場合、透明導電層206は多重干渉効果により反射率を高めるほかに、半導体層の短絡箇所に過剰な電流が流れるのを防止し、金属層(裏面電極207)を覆って半導体層との反応を防止するといった光起電力素子の信頼性を高める効果がある。しかし、半導体層の成膜時にごみや基板形状などが原因で生ずるピンホールや欠陥による多数の透明電極−裏面電極間の短絡については、透明導電層206の介在だけでは該短絡を防止する信頼性を十分確保できるとはいえず、光起電力素子の性能の低下を十分に防止するのは難しい。

こうしたことから、成膜後すでに存在する短絡を除去、あるいは短絡箇所近傍の部材を高抵抗化し光起電力素子の性能を回復する処理が施される。以降この処理をシャントパッシベーションと呼ぶ。シャントパッシベーションの条件を適正化することにより、光起電力素子のリーク電流を変えシャント抵抗を変化させた光起電力素子を作製することが出来る。

光起電力素子のpn同士を短絡すると、再結合電流が減少し、光劣化も低減することが一般に知られている。本発明は、この現象に着目し、シャント電流を積極的に利用する事によって光劣化を抑止する事を検討した。その結果、従来はできる限り小さく押さえていたシャント電流を敢えて特定の範囲内の電流量流すことによって、光起電力素子の再結合電流を減らすことで光劣化を抑制し劣化後の光電変換効率を向上させよういうことが本発明の狙いである。

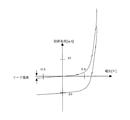

PIN型光起電力素子の場合、図1のような模式図で表されるように、ダイオードと並列抵抗で表記できる。このとき並列抵抗を挿入することにより、光によって励起された電子−正孔対は並列抵抗を介して消費され、光劣化は低減される。

しかし、並列抵抗を入れることにより、光起電力素子(ダイオード)の初期の光電変換効率は低下する。そこで、光劣化後の光電変換効率が最大になるように並列抵抗の値を変化させる必要がある。本発明では、光起電力素子のシャントパッシベーションの条件を制御する事により、ダイオードリーク電流を敢えて多めに生じさせること(並列抵抗の値を下げる)により、光劣化を抑制し光劣化後の変換効率の向上を図ったものである。

本発明によれば、光起電力素子のシャント抵抗を制御し、ダイオードリーク電流による光電変換効率の低下率を2%以上9%以下としたことにより、非晶質シリコンを用いた光起電力素子の光劣化後の光電変換効率を向上させることができる。また、耐電圧の高い光起電力素子を作製でき信頼性を向上させることができる。

図2は、本発明の概念を詳しく説明するための、光起電力素子の断面図の一例である。図2において、208は導電性基板、207は裏面電極、206は透明導電層、205はn型半導体層、204はi型半導体層、203はp型半導体層、202は透明電極である。201は発生した光電流を取り出す集電電極である。さらに、図2は基板208と逆側から光を入射する構成であるが、基板側から光を入射する構成の光起電力素子では、基板を除いて図2とは逆の順番に各層を積層することで対応できる

以下、本発明の光起電力素子の各層について形成する順に詳しく説明する。

以下、本発明の光起電力素子の各層について形成する順に詳しく説明する。

(導電性基板)

本発明に用いられる導電性基板208は、たとえば、NiCr,ステンレス,Al,Cr,Mo,Au,Nb,Ta,V,Ti,Pt,Pbなどの金属またはこれらの合金からなるものである。また、導電性基板208の厚さは、製造上および取り扱い上における機械的強度などの点から、通常は10μm以上必要である。導電性基板の研磨処理には、化学エッチングまたは切削加工により、鋭角を持ったジグザグ状に金属基板の表面を加工する。化学研磨法、電解研磨法、などの化学的表面加工法、およびダイヤモンド、カーボランダム、アランダムなどの微粒子研磨剤を用いる機械的研磨法により、凹凸を制御しながら金属基板の表面を加工する。金属表面を研磨したあと、エッチングすることにより、多重凸面上の尖端をなくす。

本発明に用いられる導電性基板208は、たとえば、NiCr,ステンレス,Al,Cr,Mo,Au,Nb,Ta,V,Ti,Pt,Pbなどの金属またはこれらの合金からなるものである。また、導電性基板208の厚さは、製造上および取り扱い上における機械的強度などの点から、通常は10μm以上必要である。導電性基板の研磨処理には、化学エッチングまたは切削加工により、鋭角を持ったジグザグ状に金属基板の表面を加工する。化学研磨法、電解研磨法、などの化学的表面加工法、およびダイヤモンド、カーボランダム、アランダムなどの微粒子研磨剤を用いる機械的研磨法により、凹凸を制御しながら金属基板の表面を加工する。金属表面を研磨したあと、エッチングすることにより、多重凸面上の尖端をなくす。

(裏面電極層)

本発明に用いられる裏面電極207は光入射方向に対し半導体層の裏面に配される電極である。裏面電極の材料としては、金、銀、銅、アルミニウム、ニッケル、鉄、クロム、モリブデン、タングステン、チタン、コバルト、タンタル、ニオブ、ジルコニウム等の金属またはステンレス等の合金が挙げられる。なかでもアルミニウム、銅、銀、金などの反射率の高い金属が特に好ましい。反射率の高い金属を用いる場合には、裏面電極に半導体層で吸収しきれなかった光を再び半導体層に反射する光反射層の役割を兼ねさせる事ができる。

本発明に用いられる裏面電極207は光入射方向に対し半導体層の裏面に配される電極である。裏面電極の材料としては、金、銀、銅、アルミニウム、ニッケル、鉄、クロム、モリブデン、タングステン、チタン、コバルト、タンタル、ニオブ、ジルコニウム等の金属またはステンレス等の合金が挙げられる。なかでもアルミニウム、銅、銀、金などの反射率の高い金属が特に好ましい。反射率の高い金属を用いる場合には、裏面電極に半導体層で吸収しきれなかった光を再び半導体層に反射する光反射層の役割を兼ねさせる事ができる。

(透明導電層)

透明導電層206は、主に以下のような目的で、裏面電極層207と半導体層の間に配置される。まず、光起電力素子の裏面での乱反射を向上させ、薄膜による多重干渉によって光を光起電力素子内に閉じ込めて、半導体層内の光路長を延ばし、光起電力素子の短絡電流(Jsc)を増大させる。次に、裏面電極層の金属が、半導体層に拡散するかあるいはマイグレーションを起こして、光起電力素子がシャントすることを防止する。また、透明導電層に若干の抵抗値をもたせることで、半導体層を挟んで設けられた裏面電極層207と透明電極202との間に半導体層のピンホール等の欠陥で発生するショートを防止することである。

透明導電層206は、主に以下のような目的で、裏面電極層207と半導体層の間に配置される。まず、光起電力素子の裏面での乱反射を向上させ、薄膜による多重干渉によって光を光起電力素子内に閉じ込めて、半導体層内の光路長を延ばし、光起電力素子の短絡電流(Jsc)を増大させる。次に、裏面電極層の金属が、半導体層に拡散するかあるいはマイグレーションを起こして、光起電力素子がシャントすることを防止する。また、透明導電層に若干の抵抗値をもたせることで、半導体層を挟んで設けられた裏面電極層207と透明電極202との間に半導体層のピンホール等の欠陥で発生するショートを防止することである。

透明導電層206は半導体層の吸収可能な波長領域において高い透過率を有することと、適度の抵抗率が要求される。好ましくは、650nm以上の透過率が、80%以上、より好ましくは、85%以上、最適には90%以上であることが望ましい。

(半導体層)

本発明に用いられる半導体層の材料としては、Si、C、Ge等のIV族元素を用いたもの、あるいはSiGe、SiC、SiSn等のIV族合金を用いたものが用いられる。

本発明に用いられる半導体層の材料としては、Si、C、Ge等のIV族元素を用いたもの、あるいはSiGe、SiC、SiSn等のIV族合金を用いたものが用いられる。

また、以上の半導体材料の中で、本発明の光起電力素子に特に好適に用いられる半導体材料としては、a−Si:H(水素化非晶質シリコンの略記)、μc−Si(微結晶シリコンの略記)、多結晶シリコン、a−Si:F、a−Si:H:F、a−SiGe:H、a−SiGe:F、a−SiGe:H:F、a−SiC:H、a−SiC:F、a−SiC:H:F等のIV族及びIV族合金系非単結晶半導体材料が挙げられる。

また、半導体層は価電子制御及び禁制帯幅制御を行うことができる。具体的には半導体層を形成する際に価電子制御剤又は禁制帯幅制御剤となる元素を含む原料化合物を単独で、又は前記堆積膜形成用原料ガス又は前記希釈ガスに混合して成膜空間内に導入してやれば良い。

また、半導体層は、価電子制御によって、少なくともその一部が、p型およびn型にドーピングされ、少なくとも一組のpin接合を形成する。そして、pin接合を複数積層することにより、いわゆるスタック型光起電力素子の構成になる。

また、半導体層の形成方法としては、マイクロ波プラズマCVD法、VHFプラズマCVD法、RFプラズマCVD法、光CVD法、熱CVD法、MOCVD法などの各種CVD法によって、あるいはEB蒸着、MBE、イオンプレーティング、イオンビーム法等の各種蒸着法、スパッタ法、スプレー法、印刷法などによって、形成される。工業的に採用されている方法としては、原料ガスをプラズマで分解し、基板上に堆積させるプラズマCVD法が好んで用いられる。また、反応装置としては、バッチ式の装置や連続成膜装置などが所望に応じて使用できる。

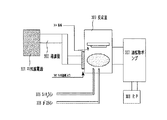

本発明では、i型半導体層としてシリコン、シリコンゲルマニウム、シリコンカーバイドなどを非晶質の状態、微結晶化または多結晶化させて用いている。微結晶層を成長させるための方法としては、大量の水素で原料ガスを希釈し、大パワーを入れて成膜する方法が用いられることが多い。作製装置の一例を図3に示す。301に示すマイクロ波電源から周波数2.45GHz、パワー20Wから2000Wのマイクロ波を導入する。マイクロ波の周波数は工業周波数である2.45GHzのほか、50MHzから1.5GHzも好適に用いられる。301のマイクロ波電源で発生したマイクロ波は、302に示す導波管を通じて309に示す反応室に導入される。原料ガスであるSiH4は305に示すラインから導入される。GeH4、CH4、H2などのガスを、306に示すガスラインから導入される。ガスは、ライン305および306から反応室309に導入される。反応室309の中には、SiH4を5sccmから200sccm、GeH4を5sccmから500sccm、CH4を5sccmから1000sccm、H2を100sccmから3000sccmなどの流量で導入される。マイクロ波導入口303から入射したマイクロ波によって、反応室309内のガスはプラズマ状態となり、304に示す基板上に、非晶質シリコン、微結晶シリコン、SiGe、SiCが形成できる。分解後のガスは307に示す油拡散ポンプによって排気され、反応室309内の圧力は、1.33Pa(10mTorr)から66.5Pa(500mTorr)に保たれる。また、マイクロ波プラズマCVDの他に、RFプラズマCVD法も用いられ、この場合反応室圧力は13.3Pa(100mTorr)から1330Pa(10Torr)で成膜を行う。

(透明電極)

透明電極202は光を透過する、光入射側の電極であるとともに、その膜厚を最適化する事によって反射防止膜としての役割も兼ねる。透明電極202は半導体層の吸収可能な波長領域において高い透過率を有することと、抵抗率が低いことが要求される。好ましくは、550nmにおける透過率が、80%以上、より好ましくは、85%以上であることが望ましい。また、抵抗率は好ましくは、5×10-3Ωcm以下、より好ましくは、1×10-3Ωcm以下であることが望ましい。その材料としては、In2O3、SnO2、ITO(In2O3+SnO2)、ZnO、CdO、Cd2SnO4、TiO2、Ta2O5、Bi2O3、MoO3、NaxWO3等の導電性酸化物あるいはこれらを混合したものが好適に用いられる。また、これらの化合物に、導電率を変化させる元素(ドーパント)を添加しても良い。

透明電極202は光を透過する、光入射側の電極であるとともに、その膜厚を最適化する事によって反射防止膜としての役割も兼ねる。透明電極202は半導体層の吸収可能な波長領域において高い透過率を有することと、抵抗率が低いことが要求される。好ましくは、550nmにおける透過率が、80%以上、より好ましくは、85%以上であることが望ましい。また、抵抗率は好ましくは、5×10-3Ωcm以下、より好ましくは、1×10-3Ωcm以下であることが望ましい。その材料としては、In2O3、SnO2、ITO(In2O3+SnO2)、ZnO、CdO、Cd2SnO4、TiO2、Ta2O5、Bi2O3、MoO3、NaxWO3等の導電性酸化物あるいはこれらを混合したものが好適に用いられる。また、これらの化合物に、導電率を変化させる元素(ドーパント)を添加しても良い。

導電率を変化させる元素(ドーパント)としては、例えば透明電極202がZnOの場合には、Al、In、B、Ga、Si、F等が、またIn2O3の場合には、Sn、F、Te、Ti、Sb、Pb等が、またSnO2の場合には、F、Sb、P、As、In、Tl、Te、W、Cl、Br、I等が好適に用いられる。

また、透明電極202の形成方法としては、スプレー法、CVD法、プラズマCVD法、電析法、真空蒸着法、イオン化蒸着法、スパッタリング法、スピンオン法、デップ法等が好適に用いられる。

例えばスパッタリング法により透明電極を作製する場合、スパッタターゲットとしてITO等を用いることができる。ITOターゲットにおいては、インジウム化合物と錫化合物、例えばインジウム塩化物と錫塩化物、あるいはインジウム、錫のアルコキシドを原料とし、化学蒸着法(CVD)により、酸化雰囲気中で気相反応させることによって、平均粒径0.1〜1μmと小さく、大きさの揃ったITOの微粒子を得ることができる。さらに粒径が小さいだけでなく分解、酸化反応、凝縮という工程を通るという特徴上、従来の液相法に比べて、錫原子はIn2O3微粒子中のインジウム原子と置換したり、格子間に侵入したりして存在することが多くなり、In2O3微粒子とSnO2微粒子が分相して存在することが少なくなると考えられる。

(シャントパッシベーション)

透明導電層は多重干渉効果により反射率を高めるほかに、半導体層の短絡箇所に過剰な電流が流れるのを防止し、金属層(裏面電極)を覆って半導体層との反応を防止するといった光起電力素子の信頼性を高める効果がある。しかし、半導体層の成膜時にごみや基板形状などが原因で生ずるピンホールや欠陥による多数の透明電極−裏面電極間の短絡については、透明導電層の介在だけでは該短絡を防止する信頼性を十分確保できるとはいえず、光起電力素子の性能の低下を十分に防止するのは難しい。こうしたことから、成膜後すでに存在する短絡を除去、あるいは短絡箇所近傍の部材を高抵抗化し光起電力素子の性能を回復する処理が施される。この処理はシャントパッシベーションと呼ばれている。

透明導電層は多重干渉効果により反射率を高めるほかに、半導体層の短絡箇所に過剰な電流が流れるのを防止し、金属層(裏面電極)を覆って半導体層との反応を防止するといった光起電力素子の信頼性を高める効果がある。しかし、半導体層の成膜時にごみや基板形状などが原因で生ずるピンホールや欠陥による多数の透明電極−裏面電極間の短絡については、透明導電層の介在だけでは該短絡を防止する信頼性を十分確保できるとはいえず、光起電力素子の性能の低下を十分に防止するのは難しい。こうしたことから、成膜後すでに存在する短絡を除去、あるいは短絡箇所近傍の部材を高抵抗化し光起電力素子の性能を回復する処理が施される。この処理はシャントパッシベーションと呼ばれている。

シャントパッシベーションの具体的な方法としては、米国特許第4,166,918号明細書には大面積光起電力素子の電気的短絡部の欠陥部を除去する方法が記載されている。この方法は降伏電圧以下の十分高い逆バイアス電圧を用いて光起電力素子の欠陥部を焼きとるものである。また特公昭62−59901号公報には半導体装置のピンホールをレーザーにより埋設する方法が記載されている。さらには、特公昭62−4869号公報には光起電力素子の非晶質膜を貫通して生じるピンホールに絶縁物を充填する方法が記載されている。また、米国特許第4,729,970号明細書には透明導電膜を含む電気バイアスのショート欠陥部に変換試薬を接触し、欠陥付近の導電膜の高抵抗化することにより電極と電気的に絶縁する方法が記載されている。

しかしながら、上記の方法はいずれも欠陥部以外の正常部にダメージを与える可能性があるという問題がある。特に上述した特公昭62−4869号公報の方法は、感光性絶縁物を塗布し透光性基板を介して光照射によりピンホールに絶縁物を充填する方法であるため、導電性基板を用いる場合には適応できないという問題がある。

光起電力素子の量産に好適なシャントパッシベーションとしては、米国特許第4,084,400号明細書に記載された、光起電力素子のショート欠陥部をH2SO4などの酸溶液中で電圧を印加して欠陥付近の導電膜を高抵抗化することにより電極と電気的に絶縁する方法が挙げられる。その際には、図4にみられるような装置において、シャントパッシベーションを行っている。浴槽402の中には例えば1wt%の硫酸水溶液を入れ、電極405を設けその上に磁石などで光起電力素子404をn側が電極405と接するように設置し、対向電極403を設ける。電極と対向電極に電圧を印加するために、パルス電源401が接続してある。

上記の光起電力素子404には、金属層としてテクスチャー構造のAgを100nm堆積した、5cm×5cmの鏡面研磨ステンレス板(SUS304)を基板とし、透明導電層ZnOを1μm形成した。さらにグロー放電分解法にて、SiH4,PH3を原料ガスとしてn型a−Si層を20nm、SiH4を原料ガスとしてi型a−Si層を400nm、SiH4,BF3,H2を原料ガスとしてp型微結晶(μc)Si層を10nm堆積し薄膜半導体接合とした。その上に透明電極として抵抗加熱蒸着法により酸化インジウム錫膜(ITO膜)を70nm堆積し、さらにAgペーストで幅300μmの集電電極を形成して光起電力素子を得た。また、透明層にSn/(Sn+Zn)=14%のZTO膜を用いた。

この試料を、1wt%の硫酸水溶液を主成分とする電解液にてシャントパッシベーションし、短絡箇所を除去した。次に全ての試料を光の当たらない状態で湿度85%、雰囲気温度85℃中で逆電圧0.85Vを印加(高湿逆バイアス試験)し、時間に伴うRshDk(光の当たらない状態での漏れ抵抗)の変化を測定、比較評価した。RshDkが0.01kΩcm2以下に低下すると、低照度光の下で開放電圧が出なくなり、光起電力素子としての特性、信頼性に問題がでてくる。従って高湿逆バイアス試験ではRshDk≧0.01kΩcm2を高湿逆バイアス試験合格基準とする。

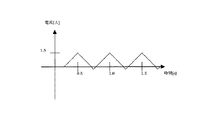

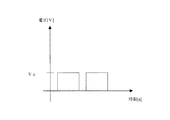

シャントパッシベーション時に電流は図5に示すような波形を示した。p層側(対向電極403)に正の電圧を印加しこの時に流れる電流(逆方向電流)を計測した。最初に逆方向電流を徐々に増やし、一定時間保持した後、逆方向電流をゼロに近づける。印加電圧ゼロのとき、電流は順方向にオーバーシュートしてしまい、順方向電流領域ができる。しばらくすると、順方向電流はゼロとなり、印加電圧ゼロで、電流の方もゼロとなる。この手順を3回繰り返し、図5のような電流を光起電力素子に流れるよう電圧を印加した。このようにしてシャントパッシベーション処理を行った。

この時、逆方向電流最高値aの値を変化させる事により、順方向漏れ電流bを変化させる事が出来る。逆方向電流最高値aが大きければ、ピンホールや欠陥による多数の透明電極−裏面電極間の短絡の原因となるシャントパスを封じる事が出来る。しかし、順方向漏れ電流bが大きいと、理由は明らかではないがシャント抵抗が下がり、光電変換効率が低下する。本発明では、逆方向電流最高値、順方向漏れ電流、入力する電圧波形を変化させることにより、シャント抵抗を下げ、初期の光電変換効率の低下率が2%以上から9%以下となるように光起電力素子のリーク電流を増やすことにより、光電変換効率の劣化率を抑え、劣化後の光電変換効率を向上させている。

以下、本発明の実施例を説明するが、本発明はこれらの実施例に限定されるものではない。

(実施例1)

本実施例では、先ず、非晶質シリコンをi型層とするpin接合を有するシングル光起電力素子に対して順方向漏れ電流を異なる電流値にしてシャントパッシベーションを行った試料をいくつか作製し、順方向漏れ電流を変化させたときのシングル光起電力素子の特性を調べた。本実施例のシングル光起電力素子は以下のようにして作製した。

本実施例では、先ず、非晶質シリコンをi型層とするpin接合を有するシングル光起電力素子に対して順方向漏れ電流を異なる電流値にしてシャントパッシベーションを行った試料をいくつか作製し、順方向漏れ電流を変化させたときのシングル光起電力素子の特性を調べた。本実施例のシングル光起電力素子は以下のようにして作製した。

5cm×5cm×0.8mmのSUS304を支持体(導電性基板)として適用した。支持体に用いたSUS304は熱圧延後、酸洗を硝酸5vol%で行い、その後バフ研磨を行ったものである。支持体のSUS304の片側の表面はバフ研磨によって鏡面処理されており、その鏡面側に裏面電極として、アルミニウムを抵抗加熱によるEB蒸着法で20Å/sの堆積速さで厚さ1000Å堆積した。裏面電極の上の透明導電層は、酸化亜鉛をターゲットとするDCスパッタリング法により作製した。酸化亜鉛をスパッタする際には、Arガスを用い圧力1.06Pa(8mTorr)、直流電力2kWで行った。堆積前に15分間、シャッターを閉じ基板表面に酸化亜鉛が堆積しないようにして、放電させて酸化亜鉛ターゲット表面のクリーニングを行った。その後、シャッターを30分間開けて酸化亜鉛薄膜を形成した。

次に非晶質シリコンをi型層とするpin接合を作製した。通常のプラズマCVD法により、ガス流量Si2H6 1.0sccm,1%H2希釈のPH3 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.5W、内圧160Pa(1.2Torr)の条件で10分間堆積を行ない、n+型の非晶質シリコン(n+−a−Si:H)層を1000Å形成し、続けて真空を破らずに、ガス流量Si2H6 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.0W、内圧153Pa(1.15Torr)の条件で140分間堆積を行い、非ドープの非晶質シリコン(i−a−Si:H)層を8000Å形成し、さらに続けて真空を破らずに、ガス流量SiH4 0.1sccm,10%H2希釈のB2H6 0.2sccm,H2 74.5sccm、基板温度200℃、RFパワー33.0W、内圧266Pa(2.0Torr)の条件で5分間堆積を行ない、p+型の微結晶シリコン(p+−μc−Si:H)層を250Å形成した。

その後、スパッタ法によりITO層を700Å、Cr層を2000Å、Al層を10000Å堆積した。続いて、Al層,Cr層を通常のフォトリソグラフィー工程により所望の形状にエッチングして端子取り出し電極とした後、ITO層を通常のフォトリソグラフィー工程により所望の形状にエッチングし、キャリアの収聯電極を形成した。

以上のようにして作製したシングル光起電力素子に対してシャントパッシベーションを行った。その時の、順方向漏れ電流を0から10mA/cm2まで異なる電流値にしてシャントパッシベーションを行った試料をいくつか作製した。

順方向漏れ電流を変化させたときの非晶質シリコンをi層に用いたシングル光起電力素子の特性を表1に示す。

表1に示すように、順方向漏れ電流が大きくなればなるほど、シャント抵抗は下がり光電変換効率は小さくなっている。

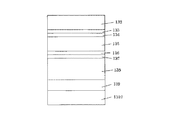

次に、上記のような特性をもったa−Siをi型層とするpin接合をトップセルに用いて、図6−1に示すようなスタック型光起電力素子を作製した。

図6−1のようにスタック型光起電力素子はAg/ZnOを形成した基板65上にボトムセル64、ミドルセル63、トップセル62、ITO61からなる。

このスタック型光起電力素子は、先ず、基板上にAg薄膜と酸化亜鉛薄膜を形成後、高周波プラズマCVD法によりn型半導体層を形成した。このとき、高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccm,H2で20ppmにまで希釈したPH3の混合ガス 0.5sccm、の条件で堆積を行なった。その後、図3に示すマイクロ波プラズマCVDチャンバーに入れi型半導体層を形成した。反応室309内に基板304を設置し、SiH4ライン305とガスライン306からSiH4とその他のガスを導入する。マイクロ波電源301から導波管302を介し、マイクロ波導入口303から反応室309内に導入する。この時の、マイクロ波パワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 100sccmを用いた。その後、高周波プラズマCVD法によって、p型半導体層を形成した。このとき、電源には、工業周波数13.56MHzを用い、電力500W、基板温度200℃、原料ガスとしてSiH4を20sccm、H2で60ppmにまで希釈したBF3の混合ガスを1.0sccm用い、圧力200Pa(1.5Torr)でp型半導体層を形成した。

以上のようにボトムpin層(ボトムセル64)を形成後、ミドルセル63を形成した。ミドルセルでは、n,pはボトムセルと同じ条件で作製した。図3に示すマイクロ波プラズマCVDチャンバーに入れi型半導体層を形成した。この時の、マイクロ波パワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 80sccmを用いた。

次に、非晶質シリコンをi型層とするトップセル62を作製した。通常のプラズマCVD法により、ガス流量Si2H6 1.0sccm,1%H2希釈のPH3 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.5W、内圧160Pa(1.2Torr)の条件で10分間堆積を行ない、n+型の非晶質シリコン(n+−a−Si:H)層を1000Å形成し、続けて真空を破らずに、ガス流量Si2H6 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.0W、内圧153Pa(1.15Torr)の条件で140分間堆積を行い、非ドープの非晶質シリコン(i−a−Si:H)層を8000Å形成し、さらに続けて真空を破らずに、ガス流量SiH4 0.1sccm,10%H2希釈のB2H6 0.2sccm,H2 74.5sccm、基板温度200℃、RFパワー33.0W、内圧266Pa(2.0Torr)の条件で5分間堆積を行ない、p+型の微結晶シリコン(p+−μc−Si:H)層を250Å形成した。

その後、スパッタ法によりITO層を700Å、Cr層を2000Å、Al層を10000Å堆積した。続いて、Al層,Cr層を通常のフォトリソグラフィー工程により所望の形状にエッチングして端子取り出し電極とした後、ITO層を通常のフォトリソグラフィー工程により所望の形状にエッチングし、キャリアの収聯電極を形成した。

以上のようにして作製したスタック型光起電力素子に対してシャントパッシベーションを行った。その時の、順方向漏れ電流を0から10mA/cm2まで異なる電流値にしてシャントパッシベーションを行った試料をいくつか作製した。

それらスタック型光起電力素子を光劣化試験にかけた。光劣化用には擬似太陽光発生装置(山下電装YSS−150)において1sun 100mW/cm2の光の下で、ステージ温度45℃で行った。そのときの光劣化特性の変化を表2−1に示す。

表2−1に示すように、a−Siシングル光起電力素子の順方向漏れ電流を増やす条件でシャントパッシベーションを行うと初期の光電変換効率は低下する。さらに、そのa−Siシングル光起電力素子のシャントパッシベーションをスタック型光起電力素子に行った場合においても順方向漏れ電流を大きくすると初期の光電変換効率は低下する。ここに示されているような光電変換効率の低下は、ダイオードリーク電流による低下であると考えられる。本願明細書及び特許請求の範囲では、このような光電変換効率の低下率を、初期光電変換効率のダイオードリーク電流による低下率と定義する。

また、光電変換効率の光劣化率は順方向漏れ電流を大きくするにつれて改善されている。これは、表1にあるように順方向漏れ電流を増やすにつれてa−Siシングル光起電力素子のシャント抵抗が下がり、光起電力素子のダイオードリーク電流が増え光活性なキャリアが再結合し、光劣化が改善されたためと考えられる。

また、光電変換効率の光劣化率は順方向漏れ電流を大きくするにつれて改善されている。これは、表1にあるように順方向漏れ電流を増やすにつれてa−Siシングル光起電力素子のシャント抵抗が下がり、光起電力素子のダイオードリーク電流が増え光活性なキャリアが再結合し、光劣化が改善されたためと考えられる。

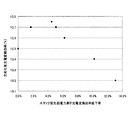

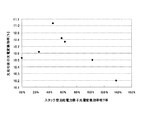

表2−1に示した結果をグラフにしたものが図6−2と図6−3である。図6−2に示すように、初期の光電変換効率の低下率が2%以上9%以下のa−Siシングル光起電力素子を用いたスタック型光起電力素子では、初期光電変換効率が最も高い12.31%のもの(順方向漏れ電流がゼロのもの)以上の光劣化後の光電変換効率を得ることができる。また、図6−3に示すように、スタックにした時の初期光電変換効率の低下率も9%以内であれば、スタック型光起電力素子の光劣化後光電変換効率は初期光電変換効率が最も高い12.31%のもの(順方向漏れ電流がゼロのもの)と同等以上であった。特に、シングル光起電力素子のダイオードリーク電流による光電変換効率の低下率が2%以上9%以下での効率が非常に良くなっている。

さらに、スタック型光起電力素子において、トップセルのa−Siのi層形成時の基板温度を300℃から350℃に変化させ、スタック型光起電力素子を作製した。

それらスタック型光起電力素子について同様に光劣化試験を行なった。その結果が表2−2である。また、表2−2の結果をグラフにしたものが図6−3、図6−4である。

表2−2においても、順方向漏れ電流を増やすにつれてa−Siシングル光起電力素子の光電変換効率は低下し、順方向漏れ電流が10mA/cm2のものは順方向漏れ電流ゼロのものに比べ18.1%も光電変換効率が低下した。また、スタックにした時の初期光電変換効率も順方向漏れ電流を増やすにつれ低下する。しかし、初期の光電変換効率の低下率が2%以上9%以下のa−Siシングル光起電力素子を用いたスタック型光起電力素子では、初期光電変換効率が最も高い12.50%のもの(順方向漏れ電流がゼロのもの)以上の光劣化後の光電変換効率を得ることができる。また、スタックにした時の初期光電変換効率の低下率も9%以内であれば、スタック型光起電力素子の光劣化後光電変換効率は初期光電変換効率が最も高い12.50%のもの(順方向漏れ電流がゼロのもの)と同等以上であり、順方向漏れ電流をある程度増やしたほうが効率が良くなっている。

(実施例2)

本実施例のスタック型光起電力素子は以下のようにして作製した。

本実施例のスタック型光起電力素子は以下のようにして作製した。

幅50cmの長尺状SUS430BAを基板として用い、酸洗を硝酸5vol%で行い、その後バフ研磨を行ったものをコイル状に巻いて使用した。支持体のSUS430BAの片側の表面はバフ研磨によって鏡面処理されており、その鏡面側に裏面電極として、アルミニウムをDCスパッタリング法で20Å/sの堆積速さで厚さ1000Å堆積した。裏面電極の上の透明導電層は、酸化亜鉛をターゲットとするDCスパッタリング法により作製した。酸化亜鉛のスパッタする際には、Arガスを用い圧力1.06Pa(8mTorr)、直流電力2kWで行った。堆積前に15分間、シャッターを閉じ基板表面に酸化亜鉛が堆積しないようにして、放電させて酸化亜鉛ターゲット表面のクリーニングを行った。その後、シャッターを30分間開けて酸化亜鉛薄膜を形成した。

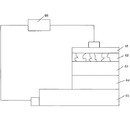

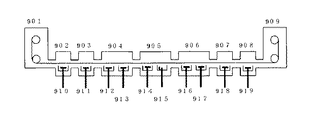

酸化亜鉛薄膜形成後、支持体を図7に示すロールツーロール式pin光起電力素子作製装置(高周波プラズマCVDチャンバー)に入れた。図中、70はロールの送り出しチャンバー、77は巻き取りチャンバーである。

先ず、n層チャンバー71において高周波プラズマCVD法によりn型半導体層を形成した。このとき、高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccm,H2で20ppmにまで希釈したPH3の混合ガス 0.5sccm、の条件で堆積を行なった。その後、ni層チャンバー72において高周波プラズマCVD法でniバッファー層を形成した。このとき、高周波電力2000W、圧力266Pa(2Torr)、材料ガス流量SiH4 100sccm,Si2H6 30sccm,H2 300sccmを用いた。その後、i層チャンバー73,74においてi型半導体層を形成した。この時の、VHFパワー1kW、作製温度250℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 100sccmを用いた。

その後、pi層チャンバー75においてpiバッファー層を形成した。このとき高周波電力2000W、圧力266Pa(2Torr)、材料ガス流量SiH4 100sccm,Si2H6 30sccm,H2 500sccmを用いた。その後、p層チャンバー76において高周波プラズマCVD法によって、p型半導体層を形成した。このとき、電源には、工業周波数13.56MHzを用い、電力500W、基板温度200℃、原料ガスとしてSiH4を20sccm、H2で60ppmにまで希釈したBF3の混合ガスを1.0sccm用い、圧力200Pa(1.5Torr)でp型半導体層を形成した。

以上のようにボトムpin層(ボトムセル)を形成後、ミドルセルを形成した。ミドルセルでは、n,pはボトムセルと同じ条件で作製した。図7に示す高周波プラズマCVDチャンバーに入れミドルセルの半導体層を形成した。この時の、VHFパワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 80sccmを用いた。

次に、非晶質シリコンをi型層とするトップセルを作製した。通常のプラズマCVD法により、ガス流量Si2H6 1.0sccm,1%H2希釈のPH3 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.5W、内圧160Pa(1.2Torr)の条件で10分間堆積を行ない、n+型の非晶質シリコン(n+−a−Si:H)層を1000Å形成し、続けて真空を破らずに、ガス流量Si2H6 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.0W、内圧153Pa(1.15Torr)の条件で140分間堆積を行ない、非ドープの非晶質シリコン(i−a−Si:H)層を8000Å形成し、さらに続けて真空を破らずに、ガス流量SiH4 0.1sccm,10%H2希釈のB2H6 0.2sccm,H2 74.5sccm、基板温度200℃、RFパワー33.0W、内圧266Pa(2.0Torr)の条件で5分間堆積を行ない、p+型の微結晶シリコン(p+−μc−Si:H)層を250Å形成した。

その後、スパッタ法によりITO層を700Å堆積した後、長尺の支持基体を50cmごとに切断した。続いて、切断した支持基体にAgペーストを用いてワイヤーグリッドをITO表面に張った。通常のフォトリソグラフィー工程により所望の形状にエッチングしてワイヤグリッド端部に電流取出し用電極タブを端子取り出し電極を形成した。

以上のようにして作製したスタック型光起電力素子に対してシャントパッシベーションを行った。シャントパッシベーションの際に、表3のように逆方向電流最高値aを変化させた。

それらのサンプルを湿度 80%、1sun 100mW/cm2の光照射下、温度25℃の下で光劣化試験を行なった。この時の光劣化特性の変化を表3に示す。

表3のように、逆方向電流が大きいほどシャントパッシベーションの効果は大きすぎ、初期効率は向上するが、シャント抵抗が上がったために光劣化率は悪化している。ボトムのi層形成時の基板温度の同じもの同士で比較すると、シャント抵抗が小さいほうが劣化後の光電変換効率は良くなっている。シャント抵抗が小さいほうが、光活性なキャリアがダイオードリーク電流により再結合したためと考えられる。特に、初期の光電変換効率の低下率が2%以上9%以下のスタック型光起電力素子では、初期光電変換効率が最も高いもの(逆方向電流最高値が0.5mA/cm2のもの)以上の光劣化後の光電変換効率を得ることができる。

(実施例3)

本実施例のスタック型光起電力素子は以下のようにして作製した。

本実施例のスタック型光起電力素子は以下のようにして作製した。

幅50cmの長尺状SUS430BAを基板として用い、酸洗を硝酸5vol%で行い、その後バフ研磨を行ったものをコイル状に巻いて使用した。支持体のSUS430BAの片側の表面はバフ研磨によって鏡面処理されており、その鏡面側に裏面電極として、アルミニウムをDCスパッタリング法で20Å/sの堆積速さで厚さ1000Å堆積した。裏面電極の上の透明導電層は、酸化亜鉛をターゲットとするDCスパッタリング法および電析法により作製した。電析法では、図9に示す電析装置を用いて酸化亜鉛を堆積した。図9中で910から919は亜鉛電極に電圧を印加する導入部であり、902から908は電析浴であり、硝酸亜鉛水溶液で満たされている。堆積する際には、硝酸亜鉛水溶液にデキストリンを0.1g/L加え酸化亜鉛薄膜を形成した。

酸化亜鉛薄膜形成後、支持体を図7に示すロールツーロール式pin光起電力素子作製装置に入れ、先ず、高周波プラズマCVD法によりn型半導体層を形成した。このとき、高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccm,H2で20ppmにまで希釈したPH3の混合ガス 0.5sccm、の条件で堆積を行なった。その後、i型半導体層を形成した。この時の、マイクロ波パワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 100sccmを用いた。

その後、高周波プラズマCVD法によって、p型半導体層を形成した。このとき、電源には、工業周波数13.56MHzを用い、電力500W、基板温度200℃、原料ガスとしてSiH4を20sccm、H2で60ppmにまで希釈したBF3の混合ガスを1.0sccm用い、圧力200Pa(1.5Torr)でp型半導体層を形成した。

以上のようにボトムpin層(ボトムセル)を形成後、ミドルセルを形成した。ミドルセルでは、n,pはボトムセルと同じ条件で作製した。図7に示すVHFプラズマCVDチャンバーに入れミドルセルの半導体層を形成した。この時の、VHFパワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 80sccmを用いた。

次に、非晶質シリコンをi型層とするトップセルを作製した。通常のプラズマCVD法により、ガス流量Si2H6 1.0sccm,1%H2希釈のPH3 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.5W、内圧160Pa(1.2Torr)の条件で10分間堆積を行ない、n+型の非晶質シリコン(n+−a−Si:H)層を1000Å形成し、続けて真空を破らずに、ガス流量Si2H6 1.0sccm,H2 48.0sccm、基板温度300℃、RFパワー1.0W、内圧153Pa(1.15Torr)の条件で140分間堆積を行ない、非ドープの非晶質シリコン(i−a−Si:H)層を8000Å形成し、さらに続けて真空を破らずに、ガス流量SiH4 0.1sccm,10%H2希釈のB2H6 0.2sccm,H2 74.5sccm、基板温度200℃、RFパワー33.0W、内圧266Pa(2.0Torr)の条件で5分間堆積を行ない、p+型の微結晶シリコン(p+−μc−Si:H)層を250Å形成した。

その後、スパッタ法によりITO層を700Å堆積した後、長尺の支持基体を50cmごとに切断した。続いて、切断した支持基体にAgペーストを用いてワイヤーグリッドをITO表面に張った。通常のフォトリソグラフィー工程により所望の形状にエッチングしてワイヤグリッド端部に電流取出し用電極タブを端子取り出し電極を形成した。

以上のようにして作製したスタック型光起電力素子に対してシャントパッシベーションを行った。その光起電力素子のIVカーブを図8に示す。図8のようになっており、マイナス電圧を印加するとダイオードリーク電流を生じた。表4のようにシャントパッシベーションの時に加える逆方向電流最高値の保持時間を変化させ初期光電変換効率と光劣化後の光電変換効率を種々の光起電力素子によって測定した。

表4のように、逆方向電流最高値の保持時間を減らすとシャントパッシベーションの効果が弱くなり、リーク電流が大きくなって光劣化率は向上している。光劣化後の光電変換効率は、ダイオードリーク電流による光電変換効率の低下率が2%以上9%以下で光劣化後非常に高い光電変換効率を示している。

(実施例4)

本実施例のシングル光起電力素子は以下のようにして作製した。

本実施例のシングル光起電力素子は以下のようにして作製した。

幅50cmの長尺状SUS430BAを基板として用い、酸洗を硝酸5vol%で行い、その後バフ研磨を行ったものをコイル状に巻いて使用した。支持体のSUS430BAの片側の表面はバフ研磨によって鏡面処理されており、その鏡面側に裏面電極として、アルミニウムをDCスパッタリング法で20Å/sの堆積速さで厚さ1000Å堆積した。裏面電極の上の透明導電層は、酸化亜鉛をターゲットとするDCスパッタリング法により作製した。酸化亜鉛のスパッタする際には、Arガスを用い圧力1.06Pa(8mTorr)、直流電力2kWで行った。堆積前に15分間、シャッターを閉じ基板表面に酸化亜鉛が堆積しないようにして、放電させて酸化亜鉛ターゲット表面のクリーニングを行った。その後、シャッターを30分間開けて酸化亜鉛薄膜を形成した。

酸化亜鉛薄膜形成後、支持体を図7に示すロールツーロール式pin光起電力素子作製装置に入れ、先ず、高周波プラズマCVD法によりn型半導体層を形成した。このとき、高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccm,H2で20ppmにまで希釈したPH3の混合ガス 0.5sccm、の条件で堆積を行なった。その後、非晶質Siのi型半導体層を形成した。この時のVHFパワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 50sccmを用いた。

その後、高周波プラズマCVD法によって、p型半導体層を形成した。このとき、電源には、工業周波数13.56MHzを用い、電力500W、基板温度200℃、原料ガスとしてSiH4を20sccm、H2で60ppmにまで希釈したBF3の混合ガスを1.0sccm用い、圧力200Pa(1.5Torr)でp型半導体層を形成した。以上のようにpin層を形成した。

その後、スパッタ法によりITO層を700Å堆積した後、長尺の支持基体を50cmごとに切断した。続いて、切断した支持基体にAgペーストを用いてワイヤーグリッドをITO表面に張った。通常のフォトリソグラフィー工程により所望の形状にエッチングしてワイヤグリッド端部に電流取出し用電極タブを端子取り出し電極を形成した。

以上のようにして作製したシングル光起電力素子に対して、図10に示すような波形の電圧を印加した。

逆方向に電圧を印加(P層側にプラス)し、電圧をゼロに戻しても、オーバーシュートが起こり、順方向に電流が流れてしまい、光起電力素子中にピンホールを生じてしまう。光起電力素子に生じたピンホールはSEMにより観察した。三角波の回数とピンホールの数との相関を示したものが表5である。非晶質シリコン内部の、異なる直径diのピンホールがNiの密度で存在する場合のΣdi2×Niを計算した。その値は、パルス数によって異なっており、表5のようになった。

表5のように、パルス数を増やすとピンホールの数が増え、ダイオードリーク電流が流れるための経路が増え、そのため光劣化の劣化率が改善される。特に、ダイオードリーク電流による光電変換効率の低下率が2%以上から9%以下では光劣化後の変換効率が、ピンホールが少なく初期光電変換効率が高いものより向上している。

(実施例5)

本実施例のシングル光起電力素子は以下のようにして作製した。

本実施例のシングル光起電力素子は以下のようにして作製した。

5cmφ厚さ0.8mmの円板状のSUS304を支持体として適用した本発明に基づく実施例を示す。支持体に用いたSUS304は熱圧延後、酸洗を硝酸5vol%で行い、その後バフ研磨を行ったものである。支持体のSUS304の片側の表面はバフ研磨によって鏡面処理されており、その鏡面側に裏面電極として、アルミニウムを抵抗加熱によるEB蒸着法で20Å/sの堆積速さで厚さ1000Å堆積した。裏面電極の上の透明導電層は、酸化亜鉛をターゲットとするDCスパッタリング法により作製した。酸化亜鉛のスパッタする際には、Arガスを用い圧力1.06Pa(8mTorr)、直流電力2kWで行った。堆積前に15分間、シャッターを閉じ基板表面に酸化亜鉛が堆積しないようにして、放電させて酸化亜鉛ターゲット表面のクリーニングを行った。その後、シャッターを30分間開けて酸化亜鉛薄膜を形成した。

酸化亜鉛薄膜形成後、高周波プラズマCVD法によりn型半導体層を形成した。このとき、高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccm,H2で20ppmにまで希釈したPH3の混合ガス 0.5sccm、の条件で堆積を行なった。その後、図3に示すマイクロ波プラズマCVDチャンバーに入れi型半導体層を形成した。この時の、マイクロ波パワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 100sccmを用いた。

その後、高周波プラズマCVD法によって、p型半導体層を形成した。このとき、電源には、工業周波数13.56MHzを用い、電力500W、基板温度200℃、原料ガスとしてSiH4を20sccm、H2で60ppmにまで希釈したBF3の混合ガスを1.0sccm用い、圧力200Pa(1.5Torr)でp型半導体層を形成した。

その後、スパッタ法によりITO層を700Å、Cr層を2000Å、Al層を10000Å堆積した。続いて、Al層,Cr層を通常のフォトリソグラフィー工程により所望の形状にエッチングして端子取り出し電極とした後、ITO層を通常のフォトリソグラフィー工程により所望の形状にエッチングし、キャリアの収聯電極を形成した。

以上のようにして作製したシングル光起電力素子に対してシャントパッシベーションを行った。その後、図11に示すような0.5wt%の硝酸水溶液中で光起電力素子に電圧を印加した。図11で光起電力素子115はアルミ板114の上に固定し、対向電極113を設け、電源111により電圧をかけた。本実施例では、硫酸雰囲気で30ppmであった。また、この雰囲気は塩酸液または硝酸液でも良く、光起電力素子全体に電圧が印加できるような系であればよい。この光起電力素子に図12に示すような電圧を印加した。図12のような矩形波を印加すると矩形波の立下り部分で、光起電力素子には順方向電流が流れ、シャント抵抗が下がってしまう。矩形波の電圧を表6のように変化させたときの光起電力素子のシャント抵抗を観察した。さらに、それらの光起電力素子に対して、−25V印加して光起電力素子の特性に異常が出ないかどうか試験を行った。

その結果、表6に示すようにVaを高くしたほうが、耐電圧試験でも結果がよく生存率も100%であった。また、シャント抵抗が低いほうが半導体層の破壊がしにくく耐電圧試験の結果がよく、実用上の信頼性が高いことがわかった。また、ダイオードリーク電流による光電変換効率の低下率が2%以上9%以下で良好な結果を得た。

(実施例6)

本実施例では図13に示すような光起電力素子を作成した。この光起電力素子は、導電性基板1310、裏面電極139、透明導電層138、n層137、niバッファー層136、i層135、piバッファー層134、p層133、透明電極132から構成される。

本実施例では図13に示すような光起電力素子を作成した。この光起電力素子は、導電性基板1310、裏面電極139、透明導電層138、n層137、niバッファー層136、i層135、piバッファー層134、p層133、透明電極132から構成される。

導電性基板(支持体)1310には、5cm×5cm×0.8mmのSUS304を用いた。この支持体に用いたSUS304は熱圧延後、酸洗を硝酸5vol%で行い、その後バフ研磨を行ったものである。支持体のSUS304の片側の表面はバフ研磨によって鏡面処理されており、その鏡面側に裏面電極として、アルミニウムを抵抗加熱によるEB蒸着法で20Å/sの堆積速さで厚さ1000Å堆積した。裏面電極の上の透明導電層は、酸化亜鉛をターゲットとするDCスパッタリング法により作製した。酸化亜鉛のスパッタする際には、Arガスを用い圧力1.06Pa(8mTorr)、直流電力2kWで行った。堆積前に15分間、シャッターを閉じ基板表面に酸化亜鉛が堆積しないようにして、放電させて酸化亜鉛ターゲット表面のクリーニングを行った。その後、シャッターを30分間開けて酸化亜鉛薄膜を形成した。

酸化亜鉛薄膜形成後、高周波プラズマCVD法によりn型半導体層を形成した。このとき、高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccm,H2で20ppmにまで希釈したPH3の混合ガス 0.5sccm、の条件で堆積を行なった。その後、高周波プラズマCVD法により、niバッファーとして高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm、Si2H6 30sccmで、放電時間と温度を表7のように変化させて堆積した。その後、図3に示すマイクロ波プラズマCVDチャンバーに入れi型半導体層を形成した。この時の、マイクロ波パワー1kW、作製温度300℃、圧力74.5Pa(560mTorr)、原料ガスにはSiH4 5sccmおよびH2 100sccmを用いた。

その後、高周波プラズマCVD法により、piバッファーとして高周波電力200W、圧力266Pa(2Torr)、材料ガス流量SiH4 200sccm,Si2H6 30sccmを用い、20秒間堆積した。その後、高周波プラズマCVD法によって、p型半導体層を形成した。このとき、電源には、工業周波数13.56MHzを用い、電力500W、基板温度200℃、原料ガスとしてSiH4を20sccm、H2で60ppmにまで希釈したBF3の混合ガスを1.0sccm用い、圧力200Pa(1.5Torr)でp型半導体層を形成した。

以上のようにして、図13のような光起電力素子を作成した。

図13のniバッファー層136の作製時の放電時間と基板温度を表7のように変えるとシャント抵抗が変化し、シャント抵抗が低くなると光劣化率は向上している。特にリーク電流による光電変換効率の低下率が2%以上9%以下のものは、光劣化後の光電変換効率がシャントの少ないものよりも向上しており、光劣化後に高い光電変換効率を示している。

61 ITO

62 トップセル

63 ミドルセル

64 ボトムセル

65 基板

66 負荷

70 送り出しチャンバー

71 n層チャンバー

72 ni層チャンバー

73 i層チャンバー

74 i層チャンバー

75 pi層チャンバー

76 p層チャンバー

77 巻き取りチャンバー

111 電源

112 液槽

113 対向電極

114 アルミ板

115 光起電力素子

132 透明電極

133 p層

134 piバッファー層

135 i層

136 niバッファー層

137 n層

138 透明導電層

139 裏面電極

1310 導電性基板

201 集電電極

202 透明電極

203 p型半導体層

204 i型半導体層

205 n型半導体層

206 透明導電層

207 裏面電極

208 導電性基板

301 マイクロ波電源

302 導波管

303 マイクロ波導入口

304 基板

305 SiH4ライン

306 ガスライン

307 油拡散ポンプ

308 RP

309 反応室

401 パルス電源

402 液槽

403 対向電極

404 光起電力素子

405 電極

62 トップセル

63 ミドルセル

64 ボトムセル

65 基板

66 負荷

70 送り出しチャンバー

71 n層チャンバー

72 ni層チャンバー

73 i層チャンバー

74 i層チャンバー

75 pi層チャンバー

76 p層チャンバー

77 巻き取りチャンバー

111 電源

112 液槽

113 対向電極

114 アルミ板

115 光起電力素子

132 透明電極

133 p層

134 piバッファー層

135 i層

136 niバッファー層

137 n層

138 透明導電層

139 裏面電極

1310 導電性基板

201 集電電極

202 透明電極

203 p型半導体層

204 i型半導体層

205 n型半導体層

206 透明導電層

207 裏面電極

208 導電性基板

301 マイクロ波電源

302 導波管

303 マイクロ波導入口

304 基板

305 SiH4ライン

306 ガスライン

307 油拡散ポンプ

308 RP

309 反応室

401 パルス電源

402 液槽

403 対向電極

404 光起電力素子

405 電極

Claims (3)

- Siを主構成元素とする多結晶、微結晶または非晶質半導体をi層に含むpin接合を少なくとも一組有する光起電力素子において、該光起電力素子の初期光電変換効率をダイオードリーク電流により2%以上9%以下低下させたことを特徴とする光起電力素子。

- Siを主構成元素とする多結晶、微結晶または非晶質半導体をi層に含むpin接合を有する光起電力素子を酸性水溶液中に浸漬し該光起電力素子のp層側に電圧を印加する工程において、前記光起電力素子のダイオードリーク電流による初期光電変換効率の低下率が2%以上9%以下になるように条件を制御することを特徴とする光起電力素子の製造方法。

- 前記制御は、前記印加電圧の波形を変化させることにより行なうことを特徴とする請求項2に記載の光起電力素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103385A JP2005294326A (ja) | 2004-03-31 | 2004-03-31 | 光起電力素子及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103385A JP2005294326A (ja) | 2004-03-31 | 2004-03-31 | 光起電力素子及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294326A true JP2005294326A (ja) | 2005-10-20 |

Family

ID=35326964

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004103385A Withdrawn JP2005294326A (ja) | 2004-03-31 | 2004-03-31 | 光起電力素子及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294326A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012504350A (ja) * | 2008-09-29 | 2012-02-16 | シンシリコン・コーポレーション | 一体的に統合されたソーラーモジュール |

| JP2012523125A (ja) * | 2009-06-10 | 2012-09-27 | シンシリコン・コーポレーション | 光起電モジュール、及び、タンデム型半導体層スタックを有する光起電モジュールを製造する方法 |

| JP2022521593A (ja) * | 2019-02-21 | 2022-04-11 | ニヴァロックス-ファー ソシエテ アノニム | 黒色光起電力デバイス |

| CN115411153A (zh) * | 2021-05-26 | 2022-11-29 | 黄剑鸣 | 提高hit异质结太阳能电池转换效率的方法 |

-

2004

- 2004-03-31 JP JP2004103385A patent/JP2005294326A/ja not_active Withdrawn

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012504350A (ja) * | 2008-09-29 | 2012-02-16 | シンシリコン・コーポレーション | 一体的に統合されたソーラーモジュール |

| JP2012523125A (ja) * | 2009-06-10 | 2012-09-27 | シンシリコン・コーポレーション | 光起電モジュール、及び、タンデム型半導体層スタックを有する光起電モジュールを製造する方法 |

| JP2022521593A (ja) * | 2019-02-21 | 2022-04-11 | ニヴァロックス-ファー ソシエテ アノニム | 黒色光起電力デバイス |

| JP7270754B2 (ja) | 2019-02-21 | 2023-05-10 | ニヴァロックス-ファー ソシエテ アノニム | 黒色光起電力デバイス |

| CN115411153A (zh) * | 2021-05-26 | 2022-11-29 | 黄剑鸣 | 提高hit异质结太阳能电池转换效率的方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3754815B2 (ja) | 光起電力素子、光電変換素子、光起電力素子の製造方法及び光電変換素子の製造方法 | |

| KR100237661B1 (ko) | 이면 반사층 및 그 형성방법과 이면 반사층을 이용한 광기전력 소자 및 그 제조방법 | |

| JP3029178B2 (ja) | 薄膜半導体太陽電池の製造方法 | |

| JP4241446B2 (ja) | 積層型光起電力素子 | |

| JP4208281B2 (ja) | 積層型光起電力素子 | |

| EP2624307B1 (en) | Method for manufacturing photoelectric conversion device | |

| US20160329443A1 (en) | Solar cell with a low-resistivity transparent conductive oxide layer | |

| EP2889916B1 (en) | Solar cell and method for manufacturing the same | |

| JP2009033208A (ja) | 積層型光起電力素子の製造方法 | |

| US20140238476A1 (en) | Photoelectric conversion device and manufacturing method thereof, and photoelectric conversion module | |

| JP2000219512A (ja) | 酸化亜鉛薄膜の製造方法、それを用いた光起電力素子の製造方法、及び光起電力素子 | |

| JP2001267611A (ja) | 薄膜太陽電池及びその製造方法 | |

| WO2012020682A1 (ja) | 結晶シリコン系太陽電池 | |

| JP2004335823A (ja) | 光起電力素子及び光起電力素子の形成方法 | |

| JP2011003750A (ja) | 結晶シリコン系太陽電池 | |

| JP5307688B2 (ja) | 結晶シリコン系太陽電池 | |

| JPH05110125A (ja) | 光起電力素子 | |

| JP3679595B2 (ja) | 光起電力素子及びその製造方法 | |

| JPH10178195A (ja) | 光起電力素子 | |

| JP2005294326A (ja) | 光起電力素子及びその製造方法 | |

| JP2004119491A (ja) | 薄膜太陽電池の製造方法およびその方法で製造された薄膜太陽電池 | |

| JP2846508B2 (ja) | 光起電力素子 | |

| JP2011077454A (ja) | 結晶シリコン系太陽電池とその製造方法 | |

| JP2004363544A (ja) | 酸化亜鉛膜及びそれを用いた光起電力素子、酸化亜鉛膜の形成方法 | |

| TW201201396A (en) | Method for manufacturing a solar panel |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Application deemed to be withdrawn because no request for examination was validly filed |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20070605 |