JP2005293918A - マイクロスイッチング素子およびマイクロスイッチング素子製造方法 - Google Patents

マイクロスイッチング素子およびマイクロスイッチング素子製造方法 Download PDFInfo

- Publication number

- JP2005293918A JP2005293918A JP2004104378A JP2004104378A JP2005293918A JP 2005293918 A JP2005293918 A JP 2005293918A JP 2004104378 A JP2004104378 A JP 2004104378A JP 2004104378 A JP2004104378 A JP 2004104378A JP 2005293918 A JP2005293918 A JP 2005293918A

- Authority

- JP

- Japan

- Prior art keywords

- base substrate

- fixed

- electrode

- movable

- contact portion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01H—ELECTRIC SWITCHES; RELAYS; SELECTORS; EMERGENCY PROTECTIVE DEVICES

- H01H59/00—Electrostatic relays; Electro-adhesion relays

- H01H59/0009—Electrostatic relays; Electro-adhesion relays making use of micromechanics

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01H—ELECTRIC SWITCHES; RELAYS; SELECTORS; EMERGENCY PROTECTIVE DEVICES

- H01H11/00—Apparatus or processes specially adapted for the manufacture of electric switches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01H—ELECTRIC SWITCHES; RELAYS; SELECTORS; EMERGENCY PROTECTIVE DEVICES

- H01H1/00—Contacts

- H01H1/0036—Switches making use of microelectromechanical systems [MEMS]

- H01H2001/0084—Switches making use of microelectromechanical systems [MEMS] with perpendicular movement of the movable contact relative to the substrate

Landscapes

- Micromachines (AREA)

- Manufacture Of Switches (AREA)

Abstract

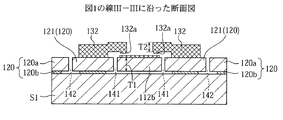

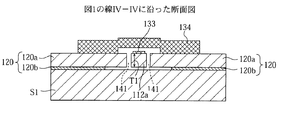

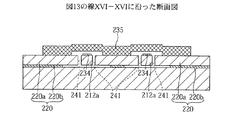

【解決手段】 本発明のマイクロスイッチング素子X1は、ベース基板と、当該ベース基板に接合しているアンカー部111およびアンカー部111から延出してベース基板に対向する延出部112を有する可動部110と、延出部112におけるベース基板とは反対の側に設けられた可動コンタクト部131と、可動コンタクト部131に対向する接触部を各々が有し且つベース基板に対して各々が固定されている一対の固定コンタクト電極132と、を備える。

【選択図】 図1

Description

前記ベース基板に接合しているアンカー部、および、当該アンカー部から延出して前記ベース基板に対向する延出部、を有する可動部と、

前記延出部における前記ベース基板とは反対の側に設けられた可動コンタクト部と、

前記可動コンタクト部に対向する第1接触部を有し且つ前記ベース基板に対して固定されている第1固定コンタクト電極と、

前記可動コンタクト部に対向する第2接触部を有し且つ前記ベース基板に対して固定されている第2固定コンタクト電極と、を備えるマイクロスイッチング素子。

(付記2)前記可動部における前記ベース基板とは反対の側に設けられた第1駆動電極と、当該第1駆動電極に対向する部位を有し且つ前記ベース基板に対して固定されている第2駆動電極と、を更に備える付記1に記載のマイクロスイッチング素子。

(付記3)ベース基板と、

前記ベース基板に接合しているアンカー部、および、当該アンカー部から延出して前記ベース基板に対向する延出部、を有する可動部と、

前記ベース基板に接合している固定部と、

前記延出部における前記ベース基板とは反対の側に設けられた可動コンタクト部と、

前記可動コンタクト部に対向する第1接触部を有し且つ前記固定部に接合している第1固定コンタクト電極と、

前記可動コンタクト部に対向する第2接触部を有し且つ前記固定部に接合している第2固定コンタクト電極と、を備えるマイクロスイッチング素子。

(付記4)前記固定部は、前記可動部から離隔している、付記3に記載のマイクロスイッチング素子。

(付記5)前記固定部は、前記可動部の周囲を囲む、付記3または4に記載のマイクロスイッチング素子。

(付記6)前記固定部は、相互に離隔して各々が前記ベース基板に接合している複数の固定アイランド部を含む、付記3から5のいずれか一つに記載のマイクロスイッチング素子。

(付記7)前記可動部における前記ベース基板とは反対の側に設けられた第1駆動電極と、当該第1駆動電極に対向する部位を有し且つ前記固定部に接合している第2駆動電極と、を更に備える付記3から6のいずれか一つに記載のマイクロスイッチング素子。

(付記8)前記可動部における前記ベース基板とは反対の側に設けられた第1駆動電極と、当該第1駆動電極上に配された圧電膜と、当該圧電膜上に配された第2駆動電極と、を更に備える付記1および3から6のいずれか一つに記載のマイクロスイッチング素子。

(付記9)前記延出部は単結晶シリコンよりなる、付記1から8のいずれか一つに記載のマイクロスイッチング素子。

(付記10)前記第1固定コンタクト電極および/または前記第2固定コンタクト電極の厚さは5μm以上である、付記1から9のいずれか一つに記載のマイクロスイッチング素子。

(付記11)前記延出部の厚さは5μm以上である、付記1から10のいずれか一つに記載のマイクロスイッチング素子。

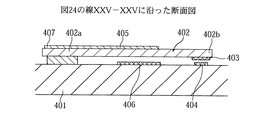

(付記12)ベース基板と、当該ベース基板に接合しているアンカー部および当該アンカー部から延出して前記ベース基板に対向する延出部を有する可動部と、前記ベース基板に接合している固定部と、前記延出部における前記ベース基板とは反対の側に設けられた可動コンタクト部と、当該可動コンタクト部に対向する第1接触部を有し且つ前記固定部に接合している第1固定コンタクト電極と、前記可動コンタクト部に対向する第2接触部を有し且つ前記固定部に接合している第2固定コンタクト電極と、を備えるマイクロスイッチング素子を、第1層と、第2層と、これらの間に介在する中間層とからなる積層構造を有する材料基板に対して加工を施すことによって製造するための方法であって、

前記第1層において前記延出部へと加工される第1部位上に可動コンタクト部を形成する第1電極形成工程と、

前記第1部位、当該第1部位に連続し且つ前記第1層において前記アンカー部へと加工される第2部位、および前記第1層において前記固定部へと加工される第3部位、をマスクするマスクパターンを介して、前記第1層に対して前記中間層に至るまで異方性エッチング処理を施す第1エッチング工程と、

前記第3部位における第1接合領域を露出させるための第1開口部、および、前記第3部位における第2接合領域を露出させるための第2開口部、を有する犠牲層を形成する犠牲層形成工程と、

前記犠牲層を介して前記可動コンタクト部に対向する第1接触部を有し且つ前記第1接合領域にて前記第3部位に接合する第1固定コンタクト電極、および、前記犠牲層を介して前記可動コンタクト部に対向する第2接触部を有し且つ前記第2接合領域にて前記第3部位に接合する第2固定コンタクト電極、を形成する第2電極形成工程と、

前記犠牲層を除去する犠牲層除去工程と、

前記ベース基板および前記第1部位の間に介在する中間層をエッチング除去する第2エッチング工程と、を含むマイクロスイッチング素子製造方法。

(付記13)前記第1電極形成工程では、前記第1部位上に更に第1駆動電極を形成し、前記犠牲層形成工程で形成される前記犠牲層は、更に、前記第3部位における第3接合領域を露出させるための第3開口部を有し、前記第2電極形成工程では、更に、前記犠牲層を介して前記第1駆動電極に対向する部位を有し且つ前記第3接合領域にて前記第3部位に接合する第2駆動電極を形成する、付記12に記載のマイクロスイッチング素子製造方法。

S1,S2,401 基板

110,150,210,402 可動部

111,151,211 アンカー部

112,152,212 延出部

120,220 固定部

131,231,403 可動コンタクト部

132,232,233,404 固定コンタクト電極

133,234 第1駆動電極

134,345 第2駆動電極

141,142,241,242 スリット

104,107 犠牲層

105,108 マスク

340 圧電駆動部

Claims (10)

- ベース基板と、

前記ベース基板に接合しているアンカー部、および、当該アンカー部から延出して前記ベース基板に対向する延出部、を有する可動部と、

前記延出部における前記ベース基板とは反対の側に設けられた可動コンタクト部と、

前記可動コンタクト部に対向する第1接触部を有し且つ前記ベース基板に対して固定されている第1固定コンタクト電極と、

前記可動コンタクト部に対向する第2接触部を有し且つ前記ベース基板に対して固定されている第2固定コンタクト電極と、を備えるマイクロスイッチング素子。 - ベース基板と、

前記ベース基板に接合しているアンカー部、および、当該アンカー部から延出して前記ベース基板に対向する延出部、を有する可動部と、

前記ベース基板に接合している固定部と、

前記延出部における前記ベース基板とは反対の側に設けられた可動コンタクト部と、

前記可動コンタクト部に対向する第1接触部を有し且つ前記固定部に接合している第1固定コンタクト電極と、

前記可動コンタクト部に対向する第2接触部を有し且つ前記固定部に接合している第2固定コンタクト電極と、を備えるマイクロスイッチング素子。 - 前記固定部は、前記可動部から離隔している、請求項2に記載のマイクロスイッチング素子。

- 前記固定部は、前記可動部の周囲を囲む、請求項2または3に記載のマイクロスイッチング素子。

- 前記固定部は、相互に離隔して各々が前記ベース基板に接合している複数の固定アイランド部を含む、請求項2から4のいずれか一つに記載のマイクロスイッチング素子。

- 前記可動部における前記ベース基板とは反対の側に設けられた第1駆動電極と、当該第1駆動電極に対向する部位を有し且つ前記固定部に接合している第2駆動電極と、を更に備える請求項2から5のいずれか一つに記載のマイクロスイッチング素子。

- 前記可動部における前記ベース基板とは反対の側に設けられた第1駆動電極と、当該第1駆動電極上に配された圧電膜と、当該圧電膜上に配された第2駆動電極と、を更に備える請求項1から5のいずれか一つに記載のマイクロスイッチング素子。

- 前記延出部は単結晶シリコンよりなる、請求項1から7のいずれか一つに記載のマイクロスイッチング素子。

- ベース基板と、当該ベース基板に接合しているアンカー部および当該アンカー部から延出して前記ベース基板に対向する延出部を有する可動部と、前記ベース基板に接合している固定部と、前記延出部における前記ベース基板とは反対の側に設けられた可動コンタクト部と、当該可動コンタクト部に対向する第1接触部を有し且つ前記固定部に接合している第1固定コンタクト電極と、前記可動コンタクト部に対向する第2接触部を有し且つ前記固定部に接合している第2固定コンタクト電極と、を備えるマイクロスイッチング素子を、第1層と、第2層と、これらの間に介在する中間層とからなる積層構造を有する材料基板に対して加工を施すことによって製造するための方法であって、

前記第1層において前記延出部へと加工される第1部位上に可動コンタクト部を形成する第1電極形成工程と、

前記第1部位、当該第1部位に連続し且つ前記第1層において前記アンカー部へと加工される第2部位、および前記第1層において前記固定部へと加工される第3部位、をマスクするマスクパターンを介して、前記第1層に対して前記中間層に至るまで異方性エッチング処理を施す第1エッチング工程と、

前記第3部位における第1接合領域を露出させるための第1開口部、および、前記第3部位における第2接合領域を露出させるための第2開口部、を有する犠牲層を形成する犠牲層形成工程と、

前記犠牲層を介して前記可動コンタクト部に対向する第1接触部を有し且つ前記第1接合領域にて前記第3部位に接合する第1固定コンタクト電極、および、前記犠牲層を介して前記可動コンタクト部に対向する第2接触部を有し且つ前記第2接合領域にて前記第3部位に接合する第2固定コンタクト電極、を形成する第2電極形成工程と、

前記犠牲層を除去する犠牲層除去工程と、

前記ベース基板および前記第1部位の間に介在する中間層をエッチング除去する第2エッチング工程と、を含むマイクロスイッチング素子製造方法。 - 前記第1電極形成工程では、前記第1部位上に更に第1駆動電極を形成し、前記犠牲層形成工程で形成される前記犠牲層は、更に、前記第3部位における第3接合領域を露出させるための第3開口部を有し、前記第2電極形成工程では、更に、前記犠牲層を介して前記第1駆動電極に対向する部位を有し且つ前記第3接合領域にて前記第3部位に接合する第2駆動電極を形成する、請求項10に記載のマイクロスイッチング素子製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104378A JP4414263B2 (ja) | 2004-03-31 | 2004-03-31 | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

| US10/710,589 US7515023B2 (en) | 2004-03-31 | 2004-07-22 | Micro-switching device and method of manufacturing micro-switching device |

| TW093121862A TWI253751B (en) | 2004-03-31 | 2004-07-22 | Micro-switching device and method of manufacturing micro-switching device |

| KR1020040063139A KR100619488B1 (ko) | 2004-03-31 | 2004-08-11 | 마이크로 스위칭 소자 및 마이크로 스위칭 소자 제조 방법 |

| CNB2004100575151A CN100411189C (zh) | 2004-03-31 | 2004-08-12 | 微型开关器件和制造微型开关器件的方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104378A JP4414263B2 (ja) | 2004-03-31 | 2004-03-31 | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293918A true JP2005293918A (ja) | 2005-10-20 |

| JP4414263B2 JP4414263B2 (ja) | 2010-02-10 |

Family

ID=35050087

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004104378A Expired - Fee Related JP4414263B2 (ja) | 2004-03-31 | 2004-03-31 | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7515023B2 (ja) |

| JP (1) | JP4414263B2 (ja) |

| KR (1) | KR100619488B1 (ja) |

| CN (1) | CN100411189C (ja) |

| TW (1) | TWI253751B (ja) |

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007152501A (ja) * | 2005-12-06 | 2007-06-21 | Seiko Epson Corp | Mems振動子及びその製造方法 |

| JP2007207487A (ja) * | 2006-01-31 | 2007-08-16 | Fujitsu Ltd | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

| JP2008034154A (ja) * | 2006-07-27 | 2008-02-14 | Fujitsu Media Device Kk | スイッチ |

| JP2008177043A (ja) * | 2007-01-18 | 2008-07-31 | Fujitsu Ltd | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

| JP2009252672A (ja) * | 2008-04-10 | 2009-10-29 | Fujitsu Ltd | スイッチング素子製造方法およびスイッチング素子 |

| JP2009252671A (ja) * | 2008-04-10 | 2009-10-29 | Fujitsu Ltd | スイッチング装置、スイッチング素子、および通信機器 |

| JP2009277617A (ja) * | 2008-05-19 | 2009-11-26 | Nippon Telegr & Teleph Corp <Ntt> | 微細電子機械スイッチおよびその製造方法 |

| KR100945623B1 (ko) * | 2006-12-07 | 2010-03-04 | 후지쯔 가부시끼가이샤 | 마이크로 스위칭 소자 |

| JP2010225513A (ja) * | 2009-03-25 | 2010-10-07 | Fujitsu Ltd | 電気部品およびその製造方法、並びにマイクロスイッチデバイス |

| JP2011119126A (ja) * | 2009-12-03 | 2011-06-16 | Fujitsu Ltd | 電子デバイス |

| US7965159B2 (en) | 2006-12-07 | 2011-06-21 | Fujitsu Limited | Micro-switching device and manufacturing method for the same |

| JP2011189477A (ja) * | 2010-03-16 | 2011-09-29 | Disco Corp | マイクロマシンデバイスの製造方法 |

| JP2012169461A (ja) * | 2011-02-15 | 2012-09-06 | Toyota Motor Corp | 半導体装置 |

| US8293557B2 (en) | 2010-03-12 | 2012-10-23 | Fujitsu Limited | Manufacturing method of MEMS device, and substrate used therefor |

| JP2013143231A (ja) * | 2012-01-10 | 2013-07-22 | Fujitsu Ltd | 高周波マイクロスイッチ |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100485787B1 (ko) * | 2002-08-20 | 2005-04-28 | 삼성전자주식회사 | 마이크로 스위치 |

| US7820470B2 (en) * | 2005-07-15 | 2010-10-26 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of micro-electro-mechanical device |

| US8043950B2 (en) * | 2005-10-26 | 2011-10-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7978034B2 (en) * | 2006-06-15 | 2011-07-12 | Panasonic Corporation | Electromechanical element and electronic equipment using the same |

| US7746539B2 (en) * | 2008-06-25 | 2010-06-29 | Qualcomm Mems Technologies, Inc. | Method for packing a display device and the device obtained thereof |

| US7545252B1 (en) | 2008-07-24 | 2009-06-09 | International Business Machines Corporation | Phase change MEMS switch |

| JP5803615B2 (ja) * | 2011-11-29 | 2015-11-04 | 富士通株式会社 | 電子デバイスとその製造方法 |

| JP2016059191A (ja) * | 2014-09-11 | 2016-04-21 | ソニー株式会社 | 静電型デバイス |

| WO2018002595A1 (en) * | 2016-06-30 | 2018-01-04 | Cirrus Logic International Semiconductor Limited | Mems device and process |

| DE102017215236A1 (de) * | 2017-08-31 | 2019-02-28 | Siemens Aktiengesellschaft | MEMS-Schalter und Verfahren zur Herstellung eines MEMS-Schalters |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5578976A (en) * | 1995-06-22 | 1996-11-26 | Rockwell International Corporation | Micro electromechanical RF switch |

| US6307452B1 (en) | 1999-09-16 | 2001-10-23 | Motorola, Inc. | Folded spring based micro electromechanical (MEM) RF switch |

| US6466102B1 (en) * | 1999-10-05 | 2002-10-15 | National Research Council Of Canada | High isolation micro mechanical switch |

| DE10004393C1 (de) * | 2000-02-02 | 2002-02-14 | Infineon Technologies Ag | Mikrorelais |

| JP3538109B2 (ja) * | 2000-03-16 | 2004-06-14 | 日本電気株式会社 | マイクロマシンスイッチ |

| EP1535296A4 (en) * | 2002-06-14 | 2007-04-04 | Ibm | MICROELECTROMECHANICAL SWITCH HAVING DEFORMABLE ELASTOMERIC CONDUCTIVE ELEMENT |

| CN2554790Y (zh) * | 2002-07-03 | 2003-06-04 | 信息产业部电子第十三研究所 | 自适应触点的微机械继电器 |

| KR100485787B1 (ko) * | 2002-08-20 | 2005-04-28 | 삼성전자주식회사 | 마이크로 스위치 |

| CN1405592A (zh) * | 2002-11-01 | 2003-03-26 | 中国科学院上海微系统与信息技术研究所 | 一种利用<110>硅片制作的微机械光开关 |

-

2004

- 2004-03-31 JP JP2004104378A patent/JP4414263B2/ja not_active Expired - Fee Related

- 2004-07-22 US US10/710,589 patent/US7515023B2/en not_active Expired - Fee Related

- 2004-07-22 TW TW093121862A patent/TWI253751B/zh not_active IP Right Cessation

- 2004-08-11 KR KR1020040063139A patent/KR100619488B1/ko not_active Expired - Fee Related

- 2004-08-12 CN CNB2004100575151A patent/CN100411189C/zh not_active Expired - Fee Related

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007152501A (ja) * | 2005-12-06 | 2007-06-21 | Seiko Epson Corp | Mems振動子及びその製造方法 |

| JP2007207487A (ja) * | 2006-01-31 | 2007-08-16 | Fujitsu Ltd | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

| US8106730B2 (en) | 2006-01-31 | 2012-01-31 | Fujitsu Limited | Microswitching device and method of manufacturing the same |

| JP2008034154A (ja) * | 2006-07-27 | 2008-02-14 | Fujitsu Media Device Kk | スイッチ |

| US7965159B2 (en) | 2006-12-07 | 2011-06-21 | Fujitsu Limited | Micro-switching device and manufacturing method for the same |

| KR100945623B1 (ko) * | 2006-12-07 | 2010-03-04 | 후지쯔 가부시끼가이샤 | 마이크로 스위칭 소자 |

| US7755460B2 (en) | 2006-12-07 | 2010-07-13 | Fujitsu Limited | Micro-switching device |

| JP2008177043A (ja) * | 2007-01-18 | 2008-07-31 | Fujitsu Ltd | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 |

| US7755459B2 (en) | 2007-01-18 | 2010-07-13 | Fujitsu Limited | Micro-switching device and method of manufacturing the same |

| JP2009252672A (ja) * | 2008-04-10 | 2009-10-29 | Fujitsu Ltd | スイッチング素子製造方法およびスイッチング素子 |

| JP2009252671A (ja) * | 2008-04-10 | 2009-10-29 | Fujitsu Ltd | スイッチング装置、スイッチング素子、および通信機器 |

| JP2009277617A (ja) * | 2008-05-19 | 2009-11-26 | Nippon Telegr & Teleph Corp <Ntt> | 微細電子機械スイッチおよびその製造方法 |

| JP2010225513A (ja) * | 2009-03-25 | 2010-10-07 | Fujitsu Ltd | 電気部品およびその製造方法、並びにマイクロスイッチデバイス |

| JP2011119126A (ja) * | 2009-12-03 | 2011-06-16 | Fujitsu Ltd | 電子デバイス |

| US8519284B2 (en) | 2009-12-03 | 2013-08-27 | Fujitsu Limited | Electronic device |

| US8293557B2 (en) | 2010-03-12 | 2012-10-23 | Fujitsu Limited | Manufacturing method of MEMS device, and substrate used therefor |

| JP2011189477A (ja) * | 2010-03-16 | 2011-09-29 | Disco Corp | マイクロマシンデバイスの製造方法 |

| JP2012169461A (ja) * | 2011-02-15 | 2012-09-06 | Toyota Motor Corp | 半導体装置 |

| JP2013143231A (ja) * | 2012-01-10 | 2013-07-22 | Fujitsu Ltd | 高周波マイクロスイッチ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100411189C (zh) | 2008-08-13 |

| TWI253751B (en) | 2006-04-21 |

| US20050225921A1 (en) | 2005-10-13 |

| TW200532908A (en) | 2005-10-01 |

| JP4414263B2 (ja) | 2010-02-10 |

| KR20050096803A (ko) | 2005-10-06 |

| KR100619488B1 (ko) | 2006-09-08 |

| US7515023B2 (en) | 2009-04-07 |

| CN1677686A (zh) | 2005-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4414263B2 (ja) | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 | |

| JP4417861B2 (ja) | マイクロスイッチング素子 | |

| JP4447940B2 (ja) | マイクロスイッチング素子製造方法およびマイクロスイッチング素子 | |

| JP4879760B2 (ja) | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 | |

| KR100945623B1 (ko) | 마이크로 스위칭 소자 | |

| US7851976B2 (en) | Micro movable device and method of making the same using wet etching | |

| JP2007535797A (ja) | マイクロマシン技術(mems)スイッチ用のビーム | |

| CN101224865A (zh) | 微开关器件及其制造方法 | |

| JP4932506B2 (ja) | マイクロスイッチング素子 | |

| JP4628275B2 (ja) | マイクロスイッチング素子およびマイクロスイッチング素子製造方法 | |

| JP2007196303A (ja) | マイクロ構造体製造方法およびマイクロ構造体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061211 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090330 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090428 |

|

| RD13 | Notification of appointment of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7433 Effective date: 20090512 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20090512 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090626 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090908 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091028 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091117 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091119 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121127 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4414263 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121127 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121127 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121127 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131127 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |