JP2005293477A - メモリコントローラ - Google Patents

メモリコントローラ Download PDFInfo

- Publication number

- JP2005293477A JP2005293477A JP2004111091A JP2004111091A JP2005293477A JP 2005293477 A JP2005293477 A JP 2005293477A JP 2004111091 A JP2004111091 A JP 2004111091A JP 2004111091 A JP2004111091 A JP 2004111091A JP 2005293477 A JP2005293477 A JP 2005293477A

- Authority

- JP

- Japan

- Prior art keywords

- data

- state machine

- selector

- signal

- address

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1689—Synchronisation and timing concerns

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Microcomputers (AREA)

- Memory System (AREA)

Abstract

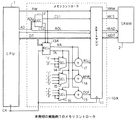

【解決手段】 CPU1からデータ信号DTとして与えられる選択情報と加算情報をレジスタ13Aで保持し、選択信号SLとしてセレクタ14〜16に共通に与えると共に、加算値VAとして加算器17〜19へ共通に与える。各セレクタ14〜16では、選択信号SLに従って複数の入力データの中から、それぞれ1つのデータが選択される。各セレクタ14〜16から出力されたデータは、それぞれ加算器17〜19において加算値VAが加算され、その加算結果の値が、それぞれアドレスセットアップ値ASU、アサートパルス幅APW、及びデータオフ値DOFのパラメータとしてステートマシン11に与えられる。

【選択図】 図1

Description

図2(a)に示すように、メモリコントローラ10は、動作タイミングが異なるCPU1とSRAM2等のメモリの間で読み書き動作のタイミング制御を行うもので、主要構成要素であるステートマシン11に加えて、デコーダ12、レジスタ13、及びセレクタ14〜16を備えている。

電源投入時の初期設定により、CPU1によってSRAM2の種別等が読み出され、このSRAM2に応じたアドレスセットアップ値ASU、アサートパルス幅APW、及びデータオフ値DOFの組み合わせを選択するための選択情報が、このCPU1からレジスタ13に書き込まれる。ここでは、レジスタ13に“1”が書き込まれたとする。これにより、セレクタ14で入力データ“1”が選択され、アドレスセットアップ値ASUとしてステートマシン11に与えられる。セレクタ15では、入力データ“2”が選択され、アサートパルス幅APWとしてステートマシン11に与えられる。更に、セレクタ16では、入力データ“2”が選択され、データオフ値DOFとしてステートマシン11に与えられる。

電源投入時の初期設定により、CPU1によってSRAM2の種別等が読み出され、このSRAM2に応じたアドレスセットアップ値ASU、アサートパルス幅APW、及びデータオフ値DOFのパラメータを設定するためのデータが、このCPU1からレジスタ13に書き込まれる。ここでは、レジスタ13Aに選択情報として“1”が書き込まれ、加算情報として“2”が書き込まれたとする。これにより、レジスタ13Aから出力される選択信号SLによって、セレクタ14で入力データ“1”が選択され、加算値VAに従って加算器17で“2”が加算され、アドレスセットアップ値ASUとして“3”がステートマシン11に与えられる。セレクタ15では、入力データ“2”が選択され、加算器18で“2”が加算され、アサートパルス幅APWとして“4”がステートマシン11に与えられる。更に、セレクタ16では、入力データ“2”が選択され、加算器19で“2”が加算され、データオフ値DOFとして“4”がステートマシン11に与えられる。

電源投入時の初期設定により、CPU1によってSRAM2の種別等が読み出され、このSRAM2に応じたアドレスセットアップ値ASU、アサートパルス幅APW、及びデータオフ値DOFの組み合わせを選択するための第1及び第2の選択情報と遅延情報が、このCPU1からレジスタ13に書き込まれる。ここでは、レジスタ13Bに第1の選択情報、即ち選択信号SLとして“1”が書き込まれ、加算情報、即ち加算値VAとして“2”が書き込まれ、第2の選択情報、即ち選択信号SLBとして“3”が書き込まれたとする。

2 SRAM

10A,10B メモリコントローラ

11 ステートマシン

12 デコーダ

13A,13B レジスタ

14〜16,20,22〜24 セレクタ

17〜19,21 加算器

25〜27 判定部

Claims (3)

- 中央処理装置と記憶装置の間で転送される制御信号、アドレス信号及びデータ信号のタイミングを与えられたパラメータに従って制御するステートマシンと、

前記中央処理装置から与えられた選択情報と加算情報を保持するレジスタと、

前記選択情報に従って複数のデータの中から該当するデータを選択するセレクタと、

前記セレクタで選択されたデータに前記加算情報を加算してその加算結果を前記パラメータとして前記ステートマシンに与える加算器とを、

備えたことを特徴とするメモリコントローラ。 - 中央処理装置と記憶装置の間で転送される制御信号、アドレス信号及びデータ信号のタイミングを与えられた複数のパラメータに従って制御するステートマシンと、

前記中央処理装置から与えられた第1及び第2の選択情報と加算情報を保持するレジスタと、

前記複数のパラメータに対応して設けられ、前記第1の選択情報に従ってそれぞれ複数のデータの中から該当するデータを選択する複数のセレクタと、

前記複数のセレクタの内で前記第2の選択情報に該当するセレクタで選択されたデータには前記加算情報を加算してその加算結果を前記パラメータとして前記ステートマシンへ与え、該第2の選択情報に該当しないセレクタで選択されたデータはそのままパラメータとして該ステートマシンへ与えるパラメータ変更手段とを、

備えたことを特徴とするメモリコントローラ。 - 前記パラメータは、

前記記憶装置に対するチップ選択信号が出力されてから該記憶装置の記憶領域を指定するメモリアドレスが確定して出力されるまでのクロック数を設定するアドレスセットアップ値と、

前記メモリアドレスが出力されている期間のクロック数を設定するアサートパルス幅と、

前記メモリアドレスの出力の停止から前記メモリに対するデータバス上のデータ信号が停止されるまでのクロック数を設定するデータオフ値とを、

含むことを特徴とする請求項1または2記載のメモリコントローラ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111091A JP2005293477A (ja) | 2004-04-05 | 2004-04-05 | メモリコントローラ |

| US11/079,210 US20050223160A1 (en) | 2004-04-05 | 2005-03-15 | Memory controller |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004111091A JP2005293477A (ja) | 2004-04-05 | 2004-04-05 | メモリコントローラ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005293477A true JP2005293477A (ja) | 2005-10-20 |

Family

ID=35055714

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004111091A Pending JP2005293477A (ja) | 2004-04-05 | 2004-04-05 | メモリコントローラ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20050223160A1 (ja) |

| JP (1) | JP2005293477A (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102018124375A1 (de) * | 2017-11-21 | 2019-05-23 | Samsung Electronics Co., Ltd. | Betriebsverfahren eines signalempfängers, pulsbreitensteuerungund elektronische vorrichtung mit denselben |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6272609B1 (en) * | 1998-07-31 | 2001-08-07 | Micron Electronics, Inc. | Pipelined memory controller |

| US7325024B2 (en) * | 2003-12-04 | 2008-01-29 | Intel Corporation | Adder circuit with sense-amplifier multiplexer front-end |

-

2004

- 2004-04-05 JP JP2004111091A patent/JP2005293477A/ja active Pending

-

2005

- 2005-03-15 US US11/079,210 patent/US20050223160A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20050223160A1 (en) | 2005-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102810082B (zh) | 带有动态端口的优先级分配能力的存储器控制器 | |

| KR20170109026A (ko) | 명령어 시프터 감소를 위한 방법들 및 장치들 | |

| US6597615B2 (en) | Refresh control for semiconductor memory device | |

| JP2002133862A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2003242799A5 (ja) | ||

| US6501699B2 (en) | Refresh control for semiconductor memory device | |

| JP2008009817A (ja) | 半導体装置及びデータ転送方法 | |

| US7876641B2 (en) | Semiconductor integrated circuit | |

| JP2005293477A (ja) | メモリコントローラ | |

| JP2006313090A (ja) | 半導体集積回路及びそのバーインテスト方法 | |

| JP4945125B2 (ja) | メモリ制御装置 | |

| JP5398664B2 (ja) | 半導体メモリ | |

| JP4790540B2 (ja) | 半導体装置 | |

| US9053776B2 (en) | Setting information storage circuit and integrated circuit chip including the same | |

| JP3642420B2 (ja) | 半導体装置 | |

| JP2009230434A (ja) | リセット回路 | |

| US7755969B2 (en) | Address receiving circuit for a semiconductor apparatus | |

| JP4549073B2 (ja) | メモリ制御回路 | |

| JP2005107648A (ja) | メモリ制御装置 | |

| JP4774119B2 (ja) | 半導体集積回路および制御信号分配方法 | |

| JP2007122250A (ja) | メモリインターフェース回路 | |

| JPH1153256A (ja) | 半導体記憶装置 | |

| JP2015156549A (ja) | 駆動能力制御回路および駆動能力制御方法 | |

| JP2005301897A (ja) | データ通信装置 | |

| JP2012216188A (ja) | 記憶制御装置、記憶制御方法及び記憶制御プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060825 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20081126 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20090302 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090810 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090818 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091215 |