JP2005250683A - マイクロコンピュータ - Google Patents

マイクロコンピュータ Download PDFInfo

- Publication number

- JP2005250683A JP2005250683A JP2004057919A JP2004057919A JP2005250683A JP 2005250683 A JP2005250683 A JP 2005250683A JP 2004057919 A JP2004057919 A JP 2004057919A JP 2004057919 A JP2004057919 A JP 2004057919A JP 2005250683 A JP2005250683 A JP 2005250683A

- Authority

- JP

- Japan

- Prior art keywords

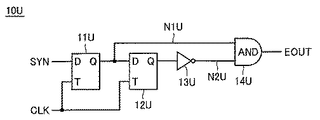

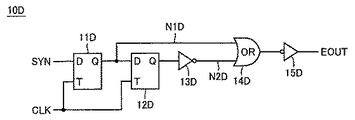

- signal

- circuit

- data

- transfer

- enable signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

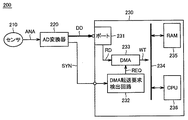

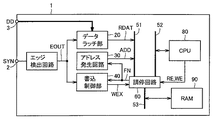

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/28—Handling requests for interconnection or transfer for access to input/output bus using burst mode transfer, e.g. direct memory access DMA, cycle steal

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Bus Control (AREA)

- Microcomputers (AREA)

- Memory System (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004057919A JP2005250683A (ja) | 2004-03-02 | 2004-03-02 | マイクロコンピュータ |

| US11/069,013 US7177966B2 (en) | 2004-03-02 | 2005-03-02 | Microcomputer minimizing influence of bus contention |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004057919A JP2005250683A (ja) | 2004-03-02 | 2004-03-02 | マイクロコンピュータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005250683A true JP2005250683A (ja) | 2005-09-15 |

| JP2005250683A5 JP2005250683A5 (enExample) | 2007-04-05 |

Family

ID=34909070

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004057919A Pending JP2005250683A (ja) | 2004-03-02 | 2004-03-02 | マイクロコンピュータ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7177966B2 (enExample) |

| JP (1) | JP2005250683A (enExample) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4896450B2 (ja) | 2005-06-30 | 2012-03-14 | 株式会社東芝 | 記憶装置 |

| JP4908017B2 (ja) * | 2006-02-28 | 2012-04-04 | 富士通株式会社 | Dmaデータ転送装置及びdmaデータ転送方法 |

| US20080075057A1 (en) * | 2006-09-25 | 2008-03-27 | Mediatek Inc. | Frequency correction burst detection |

| EP2455830A1 (de) * | 2010-11-23 | 2012-05-23 | Siemens Aktiengesellschaft | Verfahren zur Erfassung von Eingangssignaländerungen |

| KR20220149220A (ko) | 2021-04-30 | 2022-11-08 | 삼성전자주식회사 | 메모리 장치 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4106983A (en) * | 1976-01-15 | 1978-08-15 | Westinghouse Electric Corp. | Thermocouple hot junction receptacle for a nuclear reactor |

| JPS5296836A (en) * | 1976-02-10 | 1977-08-15 | Toshiba Corp | Multiplex data processing system |

| JPS6016664B2 (ja) * | 1977-10-28 | 1985-04-26 | 豊田工機株式会社 | デ−タ転送装置 |

| US4868784A (en) * | 1982-02-22 | 1989-09-19 | Texas Instruments Incorporated | Microcomputer with a multi-channel serial port having a single port address |

| US4959782A (en) * | 1986-10-29 | 1990-09-25 | United Technologies Corporation | Access arbitration for an input-output controller |

| JPH0645252B2 (ja) * | 1987-08-12 | 1994-06-15 | 株式会社日立製作所 | ラスタスキヤン式プリンタ制御装置 |

| JPS6476254A (en) | 1987-09-18 | 1989-03-22 | Fujitsu Ltd | Device for arbitrating bus |

| JPH01291354A (ja) | 1988-05-19 | 1989-11-22 | Fujitsu Kiden Ltd | データ転送制御装置 |

| JPH01320564A (ja) * | 1988-06-23 | 1989-12-26 | Hitachi Ltd | 並列処理装置 |

| JP2617621B2 (ja) | 1990-12-19 | 1997-06-04 | 富士通株式会社 | 低速/高速インタフェース回路 |

| JP3661235B2 (ja) * | 1995-08-28 | 2005-06-15 | 株式会社日立製作所 | 共有メモリシステム、並列型処理装置並びにメモリlsi |

| US5923654A (en) * | 1996-04-25 | 1999-07-13 | Compaq Computer Corp. | Network switch that includes a plurality of shared packet buffers |

| JPH103447A (ja) * | 1996-06-18 | 1998-01-06 | Matsushita Electric Ind Co Ltd | バスブリッジ装置 |

| JP2001209609A (ja) | 2000-01-25 | 2001-08-03 | Hitachi Ltd | マイクロコンピュータシステム |

| JP4047498B2 (ja) | 1999-08-25 | 2008-02-13 | 株式会社東芝 | データ処理装置 |

| JP3843667B2 (ja) * | 1999-10-15 | 2006-11-08 | セイコーエプソン株式会社 | データ転送制御装置及び電子機器 |

| US6981073B2 (en) * | 2001-07-31 | 2005-12-27 | Wis Technologies, Inc. | Multiple channel data bus control for video processing |

| JP2003067324A (ja) | 2001-08-29 | 2003-03-07 | Oki Electric Ind Co Ltd | インタフェース回路 |

-

2004

- 2004-03-02 JP JP2004057919A patent/JP2005250683A/ja active Pending

-

2005

- 2005-03-02 US US11/069,013 patent/US7177966B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20050198420A1 (en) | 2005-09-08 |

| US7177966B2 (en) | 2007-02-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7500028B2 (en) | DMA controller providing for ring buffer and rectangular block transfers | |

| JP2007525766A (ja) | マルチポートメモリシステムにおける衝突検出 | |

| US6754786B2 (en) | Memory control circuit and method for arbitrating memory bus | |

| CN111949069B (zh) | 用于异步数据传送的电路 | |

| US6272583B1 (en) | Microprocessor having built-in DRAM and internal data transfer paths wider and faster than independent external transfer paths | |

| US6782433B2 (en) | Data transfer apparatus | |

| US4853848A (en) | Block access system using cache memory | |

| JP2005250683A (ja) | マイクロコンピュータ | |

| US5467454A (en) | Bus use request adjusting apparatus allowing changing priority levels | |

| US6973520B2 (en) | System and method for providing improved bus utilization via target directed completion | |

| US6691182B2 (en) | DMA controller in which bus access ratio can be set | |

| JPH11232214A (ja) | 情報処理装置用プロセッサおよびその制御方法 | |

| US20070038795A1 (en) | Asynchronous bus interface and processing method thereof | |

| US6105082A (en) | Data processor used in a data transfer system which includes a detection circuit for detecting whether processor uses bus in a forthcoming cycle | |

| JPH10307787A (ja) | バッファメモリ装置 | |

| JP2005321933A (ja) | データ入出力装置およびデータ入出力方法 | |

| US6505274B2 (en) | Processor and system for controlling shared access to a memory | |

| JP2007052685A (ja) | マイクロコントローラ | |

| JP2002278918A (ja) | Dma装置 | |

| US20050060453A1 (en) | Instruction supply control unit and semiconductor device | |

| JP4478592B2 (ja) | メモリ回路 | |

| JP2006059303A (ja) | コンピュータシステム | |

| US20020069311A1 (en) | Bus control device | |

| JPH11273380A (ja) | Lsi動作モード設定信号取り込み方法およびモード信号取り込み機能つきlsi | |

| JP2008165485A (ja) | 半導体装置及びバッファ制御回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100202 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100302 |