JP2004235360A - 積層型薄膜コンデンサ - Google Patents

積層型薄膜コンデンサ Download PDFInfo

- Publication number

- JP2004235360A JP2004235360A JP2003021103A JP2003021103A JP2004235360A JP 2004235360 A JP2004235360 A JP 2004235360A JP 2003021103 A JP2003021103 A JP 2003021103A JP 2003021103 A JP2003021103 A JP 2003021103A JP 2004235360 A JP2004235360 A JP 2004235360A

- Authority

- JP

- Japan

- Prior art keywords

- electrode layer

- thin film

- electrode

- polarity

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Ceramic Capacitors (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Abstract

【解決手段】支持基板上に設けられた、少なくとも複数の電極層2、4と複数の誘電体層3と外部との接続に用いる外部端子5、6で構成される積層型薄膜コンデンサにおいて、各電極層2(4)の外周辺が、他の同一極性の電極層2a、2b、2c(4a、4b)の外周辺と交差しないように、電極層を変位させた。

【選択図】図1

Description

【発明の属する技術分野】

本発明は、積層型薄膜コンデンサ、即ち、支持基板上に第1の一方極性の電極層、第1の薄膜誘電体層、第1の他方極性の電極層、第2の薄膜誘電体層、第2の一方極性の電極層、第3の薄膜誘電体層、第2の他方極性の電極層、第4の薄膜誘電体層・・の順に積層した積層型薄膜コンデンサに関するものである。

【0002】

【従来の技術】

近年においては、電子機器の小型化に伴い、電子機器内に設置される電子部品にも小型化の要求があり、コンデンサとしては、積層セラミックコンデンサなどを用いて既にハンドリング可能な大きさ程度まで、小型化が実現されている。

【0003】

一方、電子機器の小型化にも使いやすい大きさという点から、下限に達しつつあり、今後は、軽量化、薄型化、高機能化の要求が強くなると予想される。

【0004】

電子部品の薄型化に適したコンデンサとして、薄膜コンデンサがある。誘電体層の厚みを1μm以下に薄膜化したものが既に開示されている(例えば、特許文献1参照)。また、小型、大容量を得る目的で複数の電極層と複数の薄膜誘電体層とを積層させた積層型の薄膜コンデンサもいくつか開示されている(例えば、特許文献2,3参照)。

【0005】

また、積層セラミックコンデンサの分野で開示事例があり、電極面積を素子中央付近から段階的に変化させて、電気的歪みによる誘電体クラックの発生を抑制することを目的としている(例えば、特許文献4参照)。

【0006】

【特許文献1】

特開昭60−94716号公報

【特許文献2】

特開平7−169648号公報

【特許文献3】

特開平11−214245号公報

【特許文献4】

特開2000−124057号公報

【0007】

【発明が解決しようとする課題】

単に薄膜誘電体層の厚みを薄くし、積層するだけでは、実用に耐えうる薄膜コンデンサを作製することはできない。特に、コンデンサとしての信頼性の観点から充分な絶縁性を確保することは、重要な問題である。

【0008】

薄膜コンデンサはその構造上、支持基板を用いて、この支持基板上に電極層、薄膜誘電体層を交互に被着形成するものであり、薄膜誘電体層の下層にある電極層を被覆する必要がある。

【0009】

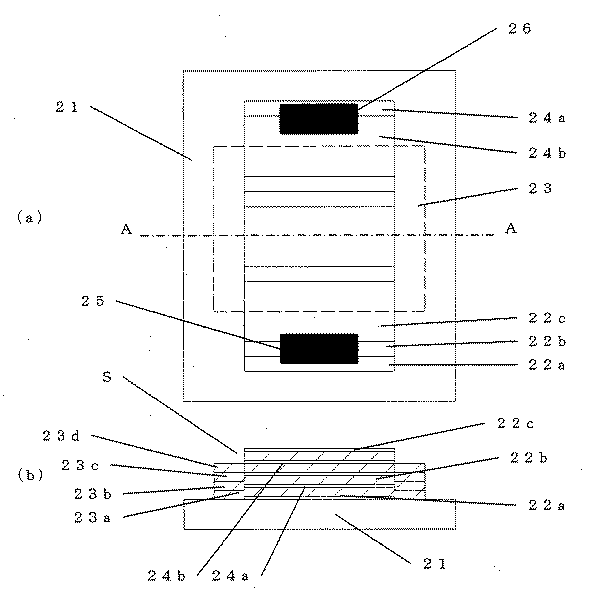

図6(a)(b)は、従来の積層型薄膜コンデンサの一例である。図6(a)は平面図であり、(b)はその断面図である。

【0010】

支持基板21上には、第1の一方極性の電極層22a、第1の薄膜誘電体層23a、第1の他方極性の電極層24a、第2の薄膜誘電体層23b、第2の一方極性の電極層22b、第3の薄膜誘電体層23c、第2の他方極性の電極層24b、第4の薄膜誘電体層23d、第3の一方極性の電極層22cが順に積層した積層型薄膜コンデンサである。即ち、一方極性の電極層(総じて22という)と、他方極性の電極層(総じて24という)とによって、4つの薄膜誘電体層(総じて23という)が挟持されて、4つの容量領域が積層されている。図6では、一方極性の電極層22の端部は、薄膜誘電体層23よりも図の下側に延出して、延出端部で形成される段差部には外部端子25が設けられている。また、他方極性の電極層24の端部は、薄膜誘電体層23よりも図の上側に延出して、延出端部で形成される段差部に外部端子26が設けられている。

【0011】

このような積層型薄膜コンデンサでは、特に、下層に位置する電極層、例えば22aの延出部以外を薄膜誘電体層23aで被覆するため、その境界部分に段差部Sが存在し、この段差部Sの処理をどのようにするかが絶縁性、信頼性を確保する観点から重要な問題の一つである。

【0012】

また、電極層22、24の充分な厚みの薄膜誘電体層23で被覆しないと、異なる極性の電極層とのショート不良や絶縁性劣化を引き起こし、薄膜コンデンサの信頼性が損なわれる。

【0013】

特に、積層数が増えるにつれて、電極層22、24の有無による段差部Sが顕著となり、電極層22、24の段差部S側の端部を被覆するための薄膜誘電体層23厚みの確保が困難になり、充分な絶縁性、信頼性が確保されない問題がある。

【0014】

本発明は、積層数によらず、電極層の有無による段差に起因する絶縁性、信頼性の低下を抑制した積層型の薄膜コンデンサを提供することを目的とする。

【0015】

【課題を解決するための手段】

本発明の薄膜コンデンサは、支持基板上に、一方極性の電極層と他方極性の電極層との間に薄膜誘電体層を挟持した複数の容量領域を積層するとともに、同一極性の電極層どうしを接続する外部端子を備える積層型薄膜コンデンサにおいて、

前記各電極層は、その外周辺が同一極性の他の電極層の外周辺と互いに交差することがない。

また、前記各電極層の一部は、薄膜誘電体層から延出するとともに、該延出部を有し、該各電極の延出部に跨がって前記外部端子が設けられている。

さらに、前記複数の同一極性を有する電極層のうち上側に位置する電極層は、平面上、下側に位置する電極層の配置領域内に形成されている。

さらに、前記複数の同一極性を有する電極層のうち上側に位置する電極層は、平面上、下側に位置する電極層の配置領域を包含して形成されている。

さらに、薄膜誘電体層の厚みが各電極層の厚みの3倍以上あることが望ましい。

【0016】

【作用】

本発明の薄膜コンデンサの電極層は、その外周辺が同一極性の他の電極層の外周辺と互いに交差することなく変位されて形成されている。このため、容量領域の積層数が増加しても電極層の有無による段差が最大で電極厚みの2倍となり、どの電極層においても薄膜誘電体層の被覆性は変わらず、充分な絶縁性、信頼性が確保することができる。

【0017】

また、複数の同一極性を有する電極層において、上層の電極層は下層の電極層の内側領域に、また、下層の電極層を包含するように配置されているので、より充分な絶縁性、信頼性が確保することができる。さらに、薄膜誘電体層の厚みが下層に位置する電極層の厚みの3倍以上あれば、より充分な絶縁性、信頼性が確保することができる。

【0018】

【発明の実施の形態】

以下、本発明の積層型薄膜コンデンサを図面に基づいて詳説する。

【0019】

図1は、保護膜を省略した4つの容量領域を積層した積層型薄膜コンデンサを示し、図1(a)はその平面図であり、図1(b)は、(a)のA−A線断面図である。

【0020】

本発明の積層型薄膜コンデンサは、支持基板1上に、第1の一方極性の電極層2a、第1の薄膜誘電体層3a、第1の他方極性の電極層4a、第2の薄膜誘電体層3b、第2の一方極性の電極層2b、第3の薄膜誘電体層3c、第2の他方極性の電極層4b、第4の薄膜誘電体層3d、第3の一方極性の電極層2cが順に積層した積層型薄膜コンデンサである。即ち、一方極性の電極層(総じて2という)と、他方極性の電極層(総じて4という)とによって、4つの薄膜誘電体層(総じて3という)が挟持されて、4つの容量領域が積層されている。

また、一方極性の電極層2の端部は、薄膜誘電体層3よりも図の下側に延出して、延出端部で形成される段差部には、各電極層2a〜2cに跨がって外部端子5が設けられている。また、他方極性の電極層4の端部は、薄膜誘電体層3よりも図の上側に延出して、延出端部で形成される段差部には、各電極層4a、4bに跨がって外部端子6が設けられている。

【0021】

しかも、各電極層2、4の左右側においては、上層側の一方極性の電極層2は、下層に位置する電極層2の内部領域に形成され、上層側の他方極性の電極層4は、下層に位置する電極層4の内部領域に形成されている。例えば、図2の電極パターン図から明らかのように、第1の一方極性の電極層2aは、その形状は第2の一方極性の電極層2bよりも大きく設定されている(図2(a))。また、第2の一方極性の電極層2bは、その形状は第3の一方極性の電極層2cよりも大きく設定されている(図2(c))。そして、第2の一方極性の電極層2bは、薄膜誘電体層3から延出するものの、全体が第1の一方極性の電極層2aの配置領域内に形成される(図2(a)と図2(c)参照)。また、図2(e)である第3の一方極性の電極層2cは、薄膜誘電体層3から延出するものの全体が第2の一方極性の電極層2bの配置領域内に形成される(図2(c)と図2(e)参照)。

【0022】

また、他方極性の電極4は、一方極性の電極層2が薄膜誘電体層3から延出する方向が相違するものの、同様にして形成されている。第1の他方極性の電極層4aは、その形状は第2の他方極性の電極層4bよりも大きく設定されている(図2(b))。そして、図2(d)である第2の他方極性の電極層4bは、薄膜誘電体層3から延出するものの全体が第1の他方極性の電極層4aの配置領域内に形成される(図2(b)と図2(d)参照)。尚、図2(f)には、第1乃至第4の薄膜誘電体層3a〜3dのパターンを示している。また、図2(g)は、3つの一方極性の電極層2a〜2cが薄膜誘電体層3から延出する端部に跨がって形成される外部端子5及び2つの他方極性の電極層3が薄膜誘電体層3から延出する端部に跨がって形成される外部端子6の電極パターンを示している。

【0023】

即ち、電極層2、4に着目すると、各電極層2、4は、その外周辺が同一極性の他の電極層2、4の外周辺と互いに交差(一致することも含む)することなく変位されて配置されている。これに対して、従来では、同一極性の電極層を形成する際に、成膜用マスクを一方方向にずらして形成するようにしたことにより、例えば、各電極層22、24の外周辺の左右側の辺が一致しており、電極層22、24の左右境界部分で段切れが発生してしまうのに対して、本実施例では、薄膜誘電体層3の外周領域では、各電極層2、4の各端部に応じた全体として緩やかな段差部となっている。

【0024】

尚、図1(a)の平面図では、薄膜誘電体層3を破線で示しているが、この薄膜誘電体層は各層3a〜3dまで同一の形状となっている。また、外部と接続する外部端子5、6は平面図において黒色で示した。

【0025】

図1(a)の平面図に示すように、積層型薄膜コンデンサは、電極層2、4で同一極性の電極2外周辺が、他の同一極性の電極2の外周辺と交差しないように変位して配置されており、図1(b)の断面図から電極層2、4のすべて端部において、薄膜誘電体層3の被覆状態、積層数に関わらず、同じ被覆状態、即ち、緩やかな段差状となる。

【0026】

これにより、薄膜誘電体層3の積層数が増加しても、薄膜誘電体層3中で段差による段切れが発生することなく、コンデンサとしての絶縁性が悪くなることはなく、また、信頼性においても絶縁劣化しにくい構造となる。ここで、薄膜誘電体層3の厚みを電極層2、4の厚みに比較して、3倍以上にすることにより、この段差部分で段切れが全く発生せず、コンデンサとしての絶縁性が悪くなることは皆無となる。

【0027】

図3は、本発明の積層型薄膜コンデンサの他の実施例を示すものであり、保護膜を省略した概略図であり、(a)は平面図であり、(b)はA−A線断面図である。

【0028】

この実施例では、図1では、積層構造の上層に位置する電極層は、下層に位置する同一極性の電極層の配置領域内に形成されていたのに対して、逆の積層構造となっている。尚、電極層、薄膜誘電体層の符合を図1と同一符合を付す。

【0029】

支持基板1側から最下層に位置する第1の一方極性の電極層2aは、その形状は第2の一方極性の電極層2bよりも小さく設定されている。また、第2の一方極性の電極層2bは、その形状は第3の一方極性の電極層2cよりもさらに小さく設定されている。そして、第2の一方極性の電極層2bは、薄膜誘電体層3から延出するものの全体が第1の一方極性の電極層2aの配置領域を完全に包含するように形成される。また、第3の一方極性の電極層2cは、薄膜誘電体層3から延出するものの全体が第2の一方極性の電極層2bの配置領域を完全に包含するよう形成される。

【0030】

また、他方極性の電極4は、一方極性の電極層2が薄膜誘電体層3から延出する方向が相違するものの、同様にして形成されている。

【0031】

尚、図1の積層型薄膜コンデンサも、図3に示す積層型薄膜コンデンサも、各電極層2、4の延出端部に設ける外部端子5、6として、各電極層2、4の延出端部側の薄膜誘電体層3の境界部分で薄膜誘電体層3の厚み及び積層数による段差が発生する。しかし、外部端子5、6を各電極層2、4の端部に跨がって形成し、場合よっては、外部端子5、6の厚みを厚くしたり、薄膜技法で下地導体膜を形成し、ハンダなどのバンプ部材を形成することにより、高い信頼性の外部端子5、6を得ることができる。

【0032】

図4は、さらに別の積層型薄膜コンデンサの概略図を示す。この実施例では、一方極性の電極層12、他方極性の電極層13の配置領域内の複数箇所に外部端子15、16が形成される低インダクタンスの積層型薄膜コンデンサである。図4では、合計4つの外部端子15、16が2行2列に配置されている。図4(a)は、支持基板、保護膜を省略した状態の平面である。また、図4(b)は各薄膜誘電体層13のパターンを示し、薄膜誘電体層13の外部端子15、16形成領域に対応するように貫通孔13a、13bが形成されている。また、図4(c)は各薄膜誘電体層13の貫通孔に形成され、且つ各一方極性の電極層12と外部端子15とを接続し、また、各他方極性の電極層14と外部端子16とを接続する端子下地層15a、16aのパターンを示す。

【0033】

また、図4(d)、(f)、(h)は、それぞれ第1の一方極性の電極層12a、第2の一方極性の電極層12b、第3の一方極性の電極層12cの電極パターン図である。図4(d)、(f)、(h)において、電極パターンの右上及び左下の比較的大きな円は、他方極性の電極層14どうしを接続する導体と短絡しないように形成された貫通孔Xであり、電極パターンの左上及び右下の小さな円は、一方極性の電極層12どうしが接続する導体部位Yを示しており、上述の端子下地層15aの形成位置に対応する。

【0034】

さらに、図4(e)、(g)は、それぞれ第1の他方極性の電極層14a、第2の他方極性の電極層14bの電極パターン図である。図4(e)、(g)において、電極パターンの左上及び右下の比較的大きな円は、一方極性の電極層12どうしを接続する導体と短絡しないように形成された貫通孔Wであり、上述の導体部位Yに対して一回りを大きくなっている。また、電極パターンの右上及び左下の小さな円は、他方極性の電極層14どうしが接続する導体部位Zを示しおり、上述の貫通孔X内に相当し、同時に、上述の端子下地層16aの形成位置に対応する。

【0035】

ここで、各電極層12、14の外周形状は、支持基板から上層に向かって、電極厚みの20倍以上の変位を持って小さくなるように形成している。このようにすれば、同一極性の電極層2、4どうしは勿論のこと、全ての電極層2、4について、外周辺が交差することがなく、薄膜誘電体層3と各電極層2、4の境界部分で緩やかな階段状の段差部とすることができる。

【0036】

尚、図4の積層型薄膜コンデンサは、外部端子15、16として、2列に千鳥状に2端子づつ形成しているが、各列に外部端子15、16を4端子づつ交互に形成し、しかも、1列目と2列目の同一極性の外部端子を千鳥状に配置してもよい。尚、列の数も、その列の中の外部端子数も、容量領域で発生する容量値、インダクタンス成分を考慮して、任意数だけ形成してもよい。その一例として、2列×8端子の16端子を有する積層型薄膜コンデンサを図5に示す。尚、図5においては、図4と同一符号を付している。

【0037】

以上、本発明の積層型薄膜コンデンサの構造において、3層の一方極性の電極層2、2層の他方極性の電極層4、4層の薄膜誘電体層が4層の例を示したが、構造から明らかなように、積層数に制限されるものではない。

【0038】

外部との接続に用いる端子部5、6は形状としては、図示したバンプ形状が望ましいが、特に限定されるものではない。図示したバンプ形状の場合、その形成位置は、同じ極性の電極層同士を接続していれば、外部端子5、6を電極層2、4に複数形成しても構わない。尚、外部端子5、6は、回路基板などの実装時に発生する熱応力による容量領域へのダメージを考慮すると、薄膜誘電体層3の上方に形成しない方が望ましい。

【0039】

また、本発明の理解を助けるため、図では、支持基板を、また、保護膜を省略した。支持基板は、最下層の電極層2a(12a)及びその上に形成される第1の薄膜誘電体層3a(13)が形成できる大きさを有しておればよい。また、保護膜は、外部端子5、6を露出して、最上層に位置する例えば電極層2c(12c)及びその下層に位置する薄膜誘電体層3d(13)を被覆するように形成されている。保護膜の信頼性確保のためには、SiOx、SiNxなど透湿係数の低い無機系の膜が望ましく、ベンゾシクロブテン(BCB樹脂)やポリイミド樹脂などの有機系の膜でもよい。また、より信頼性を確保する為に、複数を組み合わせても良い。

【0040】

【実施例】

図4に示す積層型薄膜コンデンサで、外部端子15、16が合計2列×8端子の16端子を有する積層型薄膜コンデンサを作成した。電極層12、14、端子の端子下地層15a、16aの形成はDCスパッタ装置を用い、薄膜誘電体層13の形成はRFスパッタ装置を用いた。

【0041】

先ず、厚さ0.25mmのサファイア単結晶基板上に、チタン酸化物からなる密着層を形成し、その上に80nmのPt電極層を形成した。フォトリソグラフィの技術を用いて、第1の一方極性の電極層12aをパターンに加工した。

【0042】

加工された電極層12aの上に、250nmのBa0.5Sr0.5TiO3からなる薄膜誘電体層13を形成した。電極層同様、フォトリソグラフィの技術を用いて、第1の他方極性の電極層14aをパターンに加工した。

【0043】

さらに第2の薄膜誘電体層13b、第2の一方極性の電極層12b、第3の薄膜誘電体層13c、第2の他方極性の電極層14b、第4の薄膜誘電体層13d、第3の一方極性の電極層12cを順次、形成、パターン加工を繰り返し、薄膜誘電体層4層、電極層5層の薄膜コンデンサを形成した。このとき、下層に位置する電極層12aから上層に向かって、加工精度を考慮し、各電極層12、14の外周形状が10μmづつ小さくなるように設定した。

【0044】

次に、端子部を形成するための下地層を1.0μmのNi層と0.1μmのAu層とで形成し、フォトリソグラフィの技術を用いてパターンに加工した。この後、光感光性BCBを塗布し、露光、現像を行い、端子部を形成するための下地層の一部が露出するように開口部を有する保護膜を形成した。さらに、スクリーン印刷技術を用いて、保護膜の開口部に市販のはんだペーストを転写、リフローを行い、はんだバンプを形成し、本発明の積層型の薄膜コンデンサを得た。これを本発明の試料とする。

【0045】

同様の手法を用いて、各電極層の外周形状が同一の従来の積層型の薄膜コンデンサを得た。これを比較試料例とする。

【0046】

各試料例に対して、高温負荷試験を行った結果を表1にまとめる。高温負荷試験は、125℃/3.75V/1,000時間/24個で行った。絶縁抵抗は、室温/2.5V/60秒印加の条件で測定した。

【0047】

【表1】

【0048】

静電容量に関しては、いずれの試料においても、試験前後において大きな変化はなかった。比較試料例の方が少し容量が大きいが、これは、電極層間の対向面積の差に起因している。

【0049】

試験前の絶縁抵抗において、本発明の試料例の方が比較試料例よりも、少し絶縁抵抗が大きい。また、試験後の絶縁抵抗においてその差が顕著となり、本発明試料例の方が優れていることがわかる。

【0050】

表1から明らかなように、本発明の薄膜コンデンサは従来品と比べて初期の絶縁抵抗が高く、絶縁抵抗の劣化も抑えられていることがわかる。

【0051】

【発明の効果】

本発明の積層型薄膜コンデンサは、電極層の端部の外周辺が、他の同一極性の電極層の外周辺と交差しないように変位して形成している。このため、積層数が増加しても電極層の有無による段差が最大で電極厚みの2倍となり、電極層への薄膜誘電体層の被覆性は変わらず、充分な絶縁性、信頼性が確保することができる。また、複数の同一極性を有する電極層において、上層の電極層は下層の電極層の内側にあるので、電極層端部を被覆した薄膜誘電体層上に電極層が形成される部位が少なくなり、より充分な絶縁性、信頼性が確保することができる。

【図面の簡単な説明】

【図1】(a)は、本発明の積層型薄膜コンデンサの平面図であり、(b)は(a)のA−A線に沿う断面図である。

【図2】(a)〜(e)は図1の積層型薄膜コンデンサを各電極層のパターン図であり、(f)は薄膜誘電体層のパターン図であり、(g)は外部端子のパターン図である。

【図3】(a)は、本発明の他の積層型薄膜コンデンサの平面図であり、(b)は(a)のA−A線に沿う断面図である。

【図4】本発明の別の積層型薄膜コンデンサを示すものであり、(a)はその全体の平面図であり、(b)は薄膜誘電体層のパターン図であり、(c)は外部端子の下地層のパターン図であり、(d)〜(h)は、各電極層のパターン図である。

【図5】本発明の別の積層型薄膜コンデンサを示すものであり、(a)はその全体の平面図であり、(b)は薄膜誘電体層のパターン図であり、(c)は外部端子の下地層のパターン図であり、(d)〜(h)は、各電極層のパターン図である。

【図6】従来の積層型薄膜コンデンサを示し、(a)は、その平面図であり、(b)は(a)のA−A線に沿う断面図である。

【符号の説明】

2、2a〜2c、12、12a〜12c・・・一方極性の電極層

4、4a、4b、14、14a、14b・・・一方極性の電極層

3、3a〜3d、13、13a〜13d・・・薄膜誘電体層

Claims (5)

- 支持基板上に、一方極性の電極層と他方極性の電極層との間に薄膜誘電体層を挟持した複数の容量領域を積層するとともに、同一極性の電極層どうしを接続する外部端子を備える積層型薄膜コンデンサにおいて、

前記各電極層は、その外周辺が同一極性の他の電極層の外周辺と互いに交差することがないことを特徴とする積層型薄膜コンデンサ。 - 前記各電極層の一部は、薄膜誘電体層から延出するとともに、該延出部を有し、該各電極の延出部に跨がって前記外部端子が設けられていることを特徴とする請求項1記載の積層型薄膜コンデンサ。

- 前記複数の同一極性を有する電極層のうち上側に位置する電極層は、平面上、下側に位置する電極層の配置領域内に形成されていることを特徴とする請求項1記載の積層型薄膜コンデンサ。

- 前記複数の同一極性を有する電極層のうち上側に位置する電極層は、平面上、下側に位置する電極層の配置領域を包含して形成されていることを特徴とする請求項1記載の積層型薄膜コンデンサ。

- 薄膜誘電体層の厚みが各電極層の厚みの3倍以上あることを特徴とする請求項1または2のいずれか記載の薄膜コンデンサ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003021103A JP4331950B2 (ja) | 2003-01-29 | 2003-01-29 | 積層型薄膜コンデンサ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003021103A JP4331950B2 (ja) | 2003-01-29 | 2003-01-29 | 積層型薄膜コンデンサ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004235360A true JP2004235360A (ja) | 2004-08-19 |

| JP4331950B2 JP4331950B2 (ja) | 2009-09-16 |

Family

ID=32950536

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003021103A Expired - Fee Related JP4331950B2 (ja) | 2003-01-29 | 2003-01-29 | 積層型薄膜コンデンサ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4331950B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009078225A1 (ja) * | 2007-12-14 | 2009-06-25 | Murata Manufacturing Co., Ltd. | 薄膜積層キャパシタの製造方法 |

| JP2010232445A (ja) * | 2009-03-27 | 2010-10-14 | Tdk Corp | 薄膜デバイス |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5591112A (en) * | 1978-12-28 | 1980-07-10 | Fujitsu Ltd | Multilayer thin film capacitor |

| JPS6372108A (ja) * | 1983-12-19 | 1988-04-01 | スペクトラム コントロール インコーポレーテッド | コンデンサを製造するための高速度製造方法 |

| JPH07142287A (ja) * | 1993-11-18 | 1995-06-02 | Asahi Glass Co Ltd | 積層薄膜コンデンサおよびその製造方法 |

| JPH0878283A (ja) * | 1994-09-06 | 1996-03-22 | Toshiba Corp | 薄膜キャパシタ |

| JPH10501658A (ja) * | 1995-03-27 | 1998-02-10 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 複数の電子多層構成部品の製造方法 |

| JP2001185443A (ja) * | 1999-12-22 | 2001-07-06 | Hitachi Ltd | 薄膜コンデンサ |

| JP2003234245A (ja) * | 2002-02-06 | 2003-08-22 | Sony Corp | 多層キャパシタ及びその製造方法 |

-

2003

- 2003-01-29 JP JP2003021103A patent/JP4331950B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5591112A (en) * | 1978-12-28 | 1980-07-10 | Fujitsu Ltd | Multilayer thin film capacitor |

| JPS6372108A (ja) * | 1983-12-19 | 1988-04-01 | スペクトラム コントロール インコーポレーテッド | コンデンサを製造するための高速度製造方法 |

| JPH07142287A (ja) * | 1993-11-18 | 1995-06-02 | Asahi Glass Co Ltd | 積層薄膜コンデンサおよびその製造方法 |

| JPH0878283A (ja) * | 1994-09-06 | 1996-03-22 | Toshiba Corp | 薄膜キャパシタ |

| JPH10501658A (ja) * | 1995-03-27 | 1998-02-10 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 複数の電子多層構成部品の製造方法 |

| JP2001185443A (ja) * | 1999-12-22 | 2001-07-06 | Hitachi Ltd | 薄膜コンデンサ |

| JP2003234245A (ja) * | 2002-02-06 | 2003-08-22 | Sony Corp | 多層キャパシタ及びその製造方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009078225A1 (ja) * | 2007-12-14 | 2009-06-25 | Murata Manufacturing Co., Ltd. | 薄膜積層キャパシタの製造方法 |

| JP4930602B2 (ja) * | 2007-12-14 | 2012-05-16 | 株式会社村田製作所 | 薄膜積層キャパシタの製造方法 |

| US8343361B2 (en) | 2007-12-14 | 2013-01-01 | Murata Manufacturing Co., Ltd. | Method for producing a thin film laminated capacitor |

| JP2010232445A (ja) * | 2009-03-27 | 2010-10-14 | Tdk Corp | 薄膜デバイス |

| US8218287B2 (en) | 2009-03-27 | 2012-07-10 | Tdk Corporation | Thin-film device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4331950B2 (ja) | 2009-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10468187B2 (en) | Thin-film ceramic capacitor having capacitance forming portions separated by separation slit | |

| JP6927544B2 (ja) | 薄膜キャパシター及びその製造方法 | |

| JP5924461B1 (ja) | 複合電子部品 | |

| US20170142838A1 (en) | Laminated thin film capacitor | |

| WO2022004014A1 (ja) | 薄膜キャパシタ及びこれを備える電子回路基板 | |

| US10720280B2 (en) | Thin-film ceramic capacitor having capacitance forming portions separated by separation slit | |

| US8760843B2 (en) | Capacitive device and method for fabricating the same | |

| JP4684856B2 (ja) | 電子部品 | |

| JP2004095638A (ja) | 薄膜デカップリングキャパシタとその製造方法 | |

| US10278290B2 (en) | Electronic component embedded substrate | |

| JP2008027982A (ja) | Lc複合部品 | |

| JP2006066831A (ja) | 積層セラミックコンデンサ | |

| JP4331950B2 (ja) | 積層型薄膜コンデンサ | |

| JP5061895B2 (ja) | キャパシタ及びそれを内蔵した配線基板 | |

| JP4574383B2 (ja) | 薄膜コンデンサおよび配線基板 | |

| JP2004259891A (ja) | 積層型薄膜コンデンサ | |

| CN101026155A (zh) | 薄膜器件 | |

| US11271074B2 (en) | Capacitor and method for manufacturing the same | |

| JPH05347227A (ja) | 積層薄膜コンデンサ | |

| JP6904085B2 (ja) | 電子部品内蔵基板 | |

| WO2024101272A1 (ja) | 集積化受動部品、及び集積化受動部品の製造方法 | |

| US10847317B2 (en) | Electronic component | |

| US10418179B2 (en) | Multilayer thin-film capacitor | |

| JP4044878B2 (ja) | 積層型薄膜コンデンサ | |

| JP3645808B2 (ja) | 薄膜電子部品およびその製法並びに基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050712 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080205 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080407 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080527 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080728 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090526 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090619 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120626 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120626 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130626 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |